Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# EiceDRIVER™ SIL

High Voltage IGBT Driver for Automotive Applications

# 1EDI2001AS

Single Channel Isolated Driver for Inverter Systems AD Step

# Datasheet

Hardware Description Rev. 3.1, 2015-07-30

Edition 2015-07-30

Published by Infineon Technologies AG 81726 Munich, Germany © 2015 Infineon Technologies AG All Rights Reserved.

#### **Legal Disclaimer**

The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics. With respect to any examples or hints given herein, any typical values stated herein and/or any information regarding the application of the device, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation, warranties of non-infringement of intellectual property rights of any third party.

### Information

For further information on technology, delivery terms and conditions and prices, please contact the nearest Infineon Technologies Office (www.infineon.com).

## Warnings

Due to technical requirements, components may contain dangerous substances. For information on the types in question, please contact the nearest Infineon Technologies Office.

Infineon Technologies components may be used in life-support devices or systems only with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

| Revision History |                                                                                                                                                |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Page or Item     | Subjects (major changes since previous revision)                                                                                               |  |  |

| Rev 2.2, 2014-07 | 7-25                                                                                                                                           |  |  |

| Page 11          | Updated SP Number                                                                                                                              |  |  |

| Page 28          | Added note: "the contents of a frame"                                                                                                          |  |  |

| Page 28          | Added note: "in case of permanent"                                                                                                             |  |  |

| Page 42          | Added note: "the Pulse suppressor"                                                                                                             |  |  |

| Page 49          | Corrected Table 2-14                                                                                                                           |  |  |

| Page 51          | Updated Chapter 2.4.10.1.9                                                                                                                     |  |  |

| Page 51          | Updated Chapter 2.4.10.1.11 .                                                                                                                  |  |  |

| Page 76          | Update PID value.                                                                                                                              |  |  |

| Page 79          | Updated reset value of register PSTAT2.                                                                                                        |  |  |

| Page 93          | Update SID value.                                                                                                                              |  |  |

| Page 94          | Correct SSTAT definition of bits 15 and 14 to rh.                                                                                              |  |  |

| Page 106         | Updated definition of bit field <b>DSATBT</b> .                                                                                                |  |  |

| Page 107         | Updated definition of bit field OCPBT.                                                                                                         |  |  |

| Page 116         | Updated Table 5-1                                                                                                                              |  |  |

| Page 118         | Updated Figure 5-1                                                                                                                             |  |  |

| Page 119         | Corrected Table 5-2                                                                                                                            |  |  |

| Page 120         | Updated footnote <sup>2)</sup> in <b>Table 5-3</b> .                                                                                           |  |  |

| Page 120         | Updated value R <sub>thjcbot</sub> in <b>Table 5-4</b>                                                                                         |  |  |

| Page 121         | Updated parameters V <sub>UVLO2</sub> and V <sub>OVLO2</sub> in <b>Table 5-5</b> .                                                             |  |  |

| Page 122         | Updated parameter f <sub>clk1</sub> in <b>Table 5-6</b>                                                                                        |  |  |

| Page 123         | Updated parameters R <sub>PDIN1</sub> and I <sub>INPR1</sub> in <b>Table 5-7</b>                                                               |  |  |

| Page 125         | Updated parameters R <sub>PDIN2</sub> and updated parameter R <sub>PDOSD2</sub> in <b>Table 5-13</b>                                           |  |  |

| Page 127         | Updated parameters V <sub>GPON0</sub> , V <sub>GPON1</sub> V <sub>GPON2</sub> , t <sub>PDISTO</sub> , V <sub>GPOF15</sub> in <b>Table 5-17</b> |  |  |

| Page 129         | Updated parameters R <sub>PUDESAT2</sub> , V <sub>DESAT0</sub> in <b>Table 5-18</b>                                                            |  |  |

| Page 129         | Updated parameter R <sub>PUOCP2</sub> in <b>Table 5-19</b>                                                                                     |  |  |

| Page 131         | Updated parameter t <sub>DEAD</sub> , t <sub>OFFDESAT2</sub> in <b>Table 5-21</b>                                                              |  |  |

| Page 132         | Updated parameter t <sub>FSCLK</sub> , removed parameter t <sub>SCLKp</sub> <b>Table 5-22</b>                                                  |  |  |

#### **Trademarks of Infineon Technologies AG**

AURIX<sup>™</sup>, C166<sup>™</sup>, CanPAK<sup>™</sup>, CIPOS<sup>™</sup>, CIPURSE<sup>™</sup>, EconoPACK<sup>™</sup>, CoolMOS<sup>™</sup>, CoolSET<sup>™</sup>, CORECONTROL<sup>™</sup>, CROSSAVE<sup>™</sup>, DAVE<sup>™</sup>, EasyPIM<sup>™</sup>, EconoBRIDGE<sup>™</sup>, EconoDUAL<sup>™</sup>, EconoPIM<sup>™</sup>, EiceDRIVER<sup>™</sup>, eupec<sup>™</sup>, FCOS<sup>™</sup>, HITFET<sup>™</sup>, HybridPACK<sup>™</sup>, I<sup>2</sup>RF<sup>™</sup>, ISOFACE<sup>™</sup>, IsoPACK<sup>™</sup>, MIPAQ<sup>™</sup>, ModSTACK<sup>™</sup>, my-d<sup>™</sup>, NovalithIC<sup>™</sup>, OptiMOS<sup>™</sup>, ORIGA<sup>™</sup>, PRIMARION<sup>™</sup>, PrimePACK<sup>™</sup>, PrimeSTACK<sup>™</sup>, PRO-SIL<sup>™</sup>, PROFET<sup>™</sup>, RASIC<sup>™</sup>, ReverSave<sup>™</sup>, SatRIC<sup>™</sup>, SIEGET<sup>™</sup>, SINDRION<sup>™</sup>, SIPMOS<sup>™</sup>, SmartLEWIS<sup>™</sup>, SOLID FLASH<sup>™</sup>, TEMPFET<sup>™</sup>, thinQ!<sup>™</sup>, TRENCHSTOP<sup>™</sup>, TriCore<sup>™</sup>.

## **Other Trademarks**

Advance Design System  $^{\text{TM}}$  (ADS) of Agilent Technologies, AMBA  $^{\text{TM}}$ , ARM  $^{\text{TM}}$ , MULTI-ICE  $^{\text{TM}}$ , KEIL  $^{\text{TM}}$ , PRIMECELL  $^{\text{TM}}$ , REALVIEW  $^{\text{TM}}$ , THUMB  $^{\text{TM}}$ ,  $\mu$ Vision  $^{\text{TM}}$  of ARM Limited, UK. AUTOSAR  $^{\text{TM}}$  is licensed by AUTOSAR

development partnership. Bluetooth™ of Bluetooth SIG Inc. CAT-iq™ of DECT Forum. COLOSSUS™, FirstGPS™ of Trimble Navigation Ltd. EMV™ of EMVCo, LLC (Visa Holdings Inc.). EPCOS™ of Epcos AG. FLEXGO™ of Microsoft Corporation. FlexRay™ is licensed by FlexRay Consortium. HYPERTERMINAL™ of Hilgraeve Incorporated. IEC™ of Commission Electrotechnique Internationale. IrDA™ of Infrared Data Association Corporation. ISO™ of INTERNATIONAL ORGANIZATION FOR STANDARDIZATION. MATLAB™ of MathWorks, Inc. MAXIM™ of Maxim Integrated Products, Inc. MICROTEC™, NUCLEUS™ of Mentor Graphics Corporation. Mifare™ of NXP. MIPI™ of MIPI Alliance, Inc. MIPS™ of MIPS Technologies, Inc., USA. muRata™ of MURATA MANUFACTURING CO., MICROWAVE OFFICE™ (MWO) of Applied Wave Research Inc., OmniVision™ of OmniVision Technologies, Inc. Openwave™ Openwave Systems Inc. RED HAT™ Red Hat, Inc. RFMD™ RF Micro Devices, Inc. SIRIUS™ of Sirius Satellite Radio Inc. SOLARIS™ of Sun Microsystems, Inc. SPANSION™ of Spansion LLC Ltd. Symbian™ of Symbian Software Limited. TAIYO YUDEN™ of Taiyo Yuden Co. TEAKLITE™ of CEVA, Inc. TEKTRONIX™ of Tektronix Inc. TOKO™ of TOKO KABUSHIKI KAISHA TA. UNIX™ of X/Open Company Limited. VERILOG™, PALLADIUM™ of Cadence Design Systems, Inc. VLYNQ™ of Texas Instruments Incorporated. VXWORKS™, WIND RIVER™ of WIND RIVER SYSTEMS, INC. ZETEX™ of Diodes Zetex Limited.

Last Trademarks Update 2011-02-24

## **Table of Contents**

# **Table of Contents**

|           | T. 1. 10                                          | _   |

|-----------|---------------------------------------------------|-----|

|           | Table of Contents                                 |     |

|           | List of Figures                                   |     |

|           | List of Tables                                    | . 9 |

| I         | Product Definition                                | 11  |

| 1.1       | Overview                                          | 11  |

| 1.2       | Feature Overview                                  | 11  |

| 1.3       | Target Applications                               | 12  |

| 2         | Functional Description                            | 13  |

| 2.1       | Introduction                                      | 13  |

| 2.2       | Pin Configuration and Functionality               | 14  |

| 2.2.1     | Pin Configuration                                 |     |

| 2.2.2     | Pin Functionality                                 |     |

| 2.2.2.1   | Primary Side                                      |     |

| 2.2.2.2   | Secondary Side                                    |     |

| 2.2.2.3   | Pull Devices                                      |     |

| 2.3       | Block Diagram                                     |     |

|           | Functional Block Description                      |     |

| 2.4.1     | Power Supplies                                    |     |

| 2.4.2     | Clock Domains                                     |     |

| 2.4.3     | PWM Input Stage                                   |     |

| 2.4.4     | SPI Interface                                     |     |

| 2.4.4.1   | Overview                                          |     |

| 2.4.4.2   | General Operation                                 | 24  |

| 2.4.4.3   | Definitions                                       | 26  |

| 2.4.4.4   | SPI Data Integrity Support                        | 28  |

| 2.4.4.4.1 | Parity Bit                                        | 28  |

| 2.4.4.4.2 | SPI Error                                         | 28  |

| 2.4.4.5   | Protocol Description                              | 29  |

| 2.4.4.5.1 | Command Catalog                                   | 29  |

| 2.4.4.5.2 | Word Convention                                   | 29  |

| 2.4.4.5.3 | ENTER_CMODE Command                               | 30  |

| 2.4.4.5.4 | ENTER_VMODE Command                               | 30  |

| 2.4.4.5.5 | EXIT_CMODE Command                                | 30  |

| 2.4.4.5.6 | NOP Command                                       | 31  |

| 2.4.4.5.7 | READ Command                                      |     |

| 2.4.4.5.8 | WRITEH                                            |     |

| 2.4.4.5.9 | WRITEL                                            |     |

| 2.4.5     | Operating Modes                                   |     |

| 2.4.5.1   | General Operation                                 |     |

| 2.4.5.2   | Definitions                                       |     |

| 2.4.5.2.1 | Events and State Transitions                      |     |

| 2.4.5.2.2 | Emergency Turn-Off Sequence                       |     |

| 2.4.5.2.3 | Ready, Disabled, Enabled and Active State         |     |

| 2.4.5.3   | Operation Modes Description                       |     |

| 2.4.5.4   | Activating the device after reset                 |     |

| 2.4.5.5   | Activating the device after an Event Class A or B |     |

| 2.4.5.6   | Debug Mode                                        | 38  |

# **Table of Contents**

| 2.4.6      | Driver Functionality                                | 39 |

|------------|-----------------------------------------------------|----|

| 2.4.6.1    | Overview                                            | 39 |

| 2.4.6.2    | Switching Sequence Description                      | 43 |

| 2.4.6.3    | Disabling the output stage                          | 45 |

| 2.4.6.4    | Passive Clamping                                    | 45 |

| 2.4.7      | Fault Notifications                                 | 46 |

| 2.4.8      | EN Signal Pin                                       | 46 |

| 2.4.9      | Reset Events                                        |    |

| 2.4.10     | Operation in Configuration Mode                     | 49 |

| 2.4.10.1   | Static Configuration Parameters                     |    |

| 2.4.10.1.1 | 9                                                   |    |

| 2.4.10.1.2 | 3                                                   |    |

| 2.4.10.1.3 | O BL I                                              |    |

| 2.4.10.1.4 |                                                     |    |

| 2.4.10.1.5 | · ·                                                 |    |

| 2.4.10.1.6 | F 3 F                                               |    |

| 2.4.10.1.7 |                                                     |    |

| 2.4.10.1.8 | g                                                   |    |

| 2.4.10.1.9 | 3 · ··· · · · · · · · · · · · · · · · ·             |    |

| 2.4.10.1.1 |                                                     |    |

| 2.4.10.1.1 | ŭ                                                   |    |

| 2.4.10.1.1 |                                                     |    |

| 2.4.10.1.1 |                                                     |    |

| 2.4.10.2   | Dynamic Configuration                               |    |

| 2.4.10.3   | Delay Calibration                                   | 52 |

| 3          | Protection and Diagnostics                          | 53 |

| 3.1        | Supervision Overview                                | 53 |

| 3.2        | Protection Functions: Category A                    | 55 |

| 3.2.1      | Desaturation Protection                             | 55 |

| 3.2.2      | Overcurrent Protection                              | 57 |

| 3.2.3      | External Enable                                     | 59 |

| 3.2.4      | Output Stage Monitoring                             | 60 |

| 3.3        | Protection Functions: Category B                    | 61 |

| 3.3.1      | Power Supply Voltage Monitoring                     | 61 |

| 3.3.2      | Internal Supervision                                | 62 |

| 3.3.2.1    | Lifesign watchdog                                   | 63 |

| 3.3.2.2    | Oscillator Monitoring                               |    |

| 3.3.2.3    | Memory Supervision                                  | 63 |

|            | Protection Functions: Category C                    |    |

| 3.4.1      | Shoot Through Protection function                   |    |

| 3.4.2      | Gate Monitoring                                     |    |

| 3.4.3      | Temperature Monitoring                              |    |

| 3.4.4      | SPI Error Detection                                 |    |

| 3.4.5      | Active Short Circuit Support                        |    |

|            | Protection Functions: Category D                    |    |

| 3.5.1      | Operation in Verification Mode and Weak Active Mode |    |

| 3.5.2      | Weak Turn On                                        |    |

| 3.5.3      | DESAT Supervision Level 1                           |    |

| 3.5.4      | DESAT Supervision Level 2                           |    |

| 3.5.5      | DESAT Supervision Level 3                           |    |

| 3.5.6      | OCP Supervision Level 1                             | 71 |

## **Table of Contents**

| 3.5.7<br>3.5.8<br>3.5.9 | OCP Supervision Level 3       72         Power Supply Monitoring Supervision       72         Internal Clock Supervision       73 |

|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------|

| <b>4</b> 4.1 4.2 4.3    | Register Description74Primary Register Description76Secondary Registers Description93Read / Write Address Ranges114               |

| 5                       | Specification                                                                                                                     |

| 5.1                     | Typical Application Circuit                                                                                                       |

| 5.2                     | Absolute Maximum Ratings                                                                                                          |

| 5.3                     | Operating range 120                                                                                                               |

| 5.4                     | Thermal Characteristics                                                                                                           |

| 5.5                     | Electrical Characteristics                                                                                                        |

| 5.5.1                   | Power Supply                                                                                                                      |

| 5.5.2                   | Internal Oscillators                                                                                                              |

| 5.5.3                   | Primary I/O Electrical Characteristics                                                                                            |

| 5.5.4                   | Secondary I/O Electrical Characteristics                                                                                          |

| 5.5.5                   | Switching Characteristics                                                                                                         |

| 5.5.6                   | Desaturation Protection                                                                                                           |

| 5.5.7                   | Overcurrent Protection                                                                                                            |

| 5.5.8                   | Over temperature Warning                                                                                                          |

| 5.5.9                   | Error Detection Timing                                                                                                            |

| 5.5.10                  | SPI Interface                                                                                                                     |

| 5.5.11                  | Insulation Characteristics                                                                                                        |

| 6                       | Package Information                                                                                                               |

# EiceDRIVER™ SIL 1EDI2001AS

# **List of Figures**

# **List of Figures**

| Figure 2-1  | Pin Configuration                                   | 14  |

|-------------|-----------------------------------------------------|-----|

| igure 2-2   | Block Diagram                                       | 19  |

| igure 2-3   | PWM Input Stage                                     | 21  |

| igure 2-4   | STP: Inhibition Time Definition                     | 22  |

| igure 2-5   | STP: Example of Operation                           | 22  |

| igure 2-6   | SPI Regular Bus Topology                            | 24  |

| igure 2-7   | SPI Daisy Chain Bus Topology                        | 25  |

| igure 2-8   | Response Answer Principle - Daisy Chain Topology    | 27  |

| igure 2-9   | Response Answer Principle - Regular Topology        | 27  |

| igure 2-10  | SPI Commands Overview                               | 29  |

| igure 2-11  | Operating Modes State Diagram                       | 33  |

| igure 2-12  | Output Stage Diagram of Principle                   | 39  |

| Figure 2-13 | TTOFF: Principle of Operation                       | 41  |

| igure 2-14  | TTOFF: pulse suppressor aborting a turn-on sequence | 42  |

| Figure 2-15 | Idealized Switching Sequence                        | 44  |

| igure 2-16  | Output Stage Disable: Principle of Operation        | 45  |

| Figure 3-1  | DESAT Function: Diagram of Principle                | 55  |

| Figure 3-2  | DESAT Operation                                     |     |

| igure 3-3   | DESAT Operation with DESAT clamping enabled         | 57  |

| igure 3-4   | OCP Function: Principle of Operation                | 58  |

| igure 3-5   | Power Supply Supervision Function                   | 61  |

| igure 3-6   | Shoot Through Protection: Principle of Operation    |     |

| igure 3-7   | Gate Monitoring Function: Timing Definition         | 66  |

| igure 3-8   | ASC Strategy Support                                |     |

| igure 3-9   | Idealized Weak Turn-On Sequence                     |     |

| igure 5-1   | Typical Application Example 1                       |     |

| Figure 5-2  | SPI Interface Timing                                |     |

| igure 6-1   | Package Dimensions                                  |     |

| igure 6-2   | Recommended Footprint                               | 134 |

# **List of Tables**

# **List of Tables**

| Table 2-1  | Pin Configuration                                             | 14  |

|------------|---------------------------------------------------------------|-----|

| Table 2-2  | Internal pull devices                                         | 18  |

| Table 2-3  | SPI Command Catalog                                           | 29  |

| Table 2-4  | Word Convention                                               | 29  |

| Table 2-5  | ENTER_CMODE request and answer messages                       | 30  |

| Table 2-6  | ENTER_VMODE request and answer messages                       | 30  |

| Table 2-7  | EXIT_CMODE request and answer messages                        | 30  |

| Table 2-8  | NOP request and answer messages                               | 31  |

| Table 2-9  | READ request and answer messages                              | 31  |

| Table 2-10 | WRITEH request and answer messages                            | 31  |

| Table 2-11 | WRITEL request and answer messages                            | 32  |

| Table 2-12 | Failure Notification Clearing                                 | 46  |

| Table 2-13 | Reset Events Summary                                          |     |

| Table 2-14 | Pin behavior (primary side) in case of reset condition        |     |

| Table 2-15 | Pin behavior (secondary side) in case of reset condition      | 49  |

| Table 3-1  | Safety Related Functions                                      |     |

| Table 3-2  | DESAT Protection Overview                                     | 55  |

| Table 3-3  | OCP Function Overview                                         |     |

| Table 3-4  | External Enable Function Overview                             | 59  |

| Table 3-5  | Output Stage Monitoring Overview                              | 60  |

| Table 3-6  | Power Supply Voltage Monitoring Overview                      |     |

| Table 3-7  | System Supervision Overview                                   |     |

| Table 3-8  | STP Overview                                                  |     |

| Table 3-9  | Gate Monitoring Overview                                      |     |

| Table 3-10 | Temperature Monitoring Overview                               |     |

| Table 3-11 | SPI Error Detection Overview                                  |     |

| Table 3-12 | Active Short Circuit Support Overview                         |     |

| Table 3-13 | DESAT Supervision Level 1 Overview                            |     |

| Table 3-14 | DESAT Supervision Level 2 Overview                            |     |

| Table 3-15 | DESAT Supervision Level 3 Overview                            |     |

| Table 3-16 | OCP Supervision Level 1 Overview                              |     |

| Table 3-17 | OCP Supervision Level 3 Overview                              |     |

| Table 3-18 | Power Supply Monitoring Supervision Overview                  |     |

| Table 3-19 | Primary Clock Supervision Overview                            |     |

| Table 4-1  | Register Overview                                             |     |

| Table 4-2  | Bit Access Terminology                                        |     |

| Table 4-3  | Read Access Validity                                          |     |

| Table 4-4  | Write Access Validity                                         |     |

| Table 5-1  | Component Values                                              |     |

| Table 5-2  | Absolute Maximum Ratings                                      |     |

| Table 5-3  | Operating Conditions                                          |     |

| Table 5-4  | Thermal Characteristics                                       |     |

| Table 5-5  | Power Supplies Characteristics                                |     |

| Table 5-6  | Internal Oscillators                                          |     |

| Table 5-7  | Electrical Characteristics for Pins: INP, INSTP, EN           |     |

| Table 5-8  | Electrical Characteristics for Pins: NRST/RDY, SCLK, SDI, NCS |     |

| Table 5-9  | Electrical Characteristics for Pins: SDO                      |     |

| Table 5-10 | Electrical Characteristics for Pins: NFLTA, NFLTB             |     |

| Table 5-11 | Electrical Characteristics for Pins: GATE, DESAT              | 125 |

# **List of Tables**

| Table 5-12 | Electrical Characteristics for Pins: TON, TOFF                                 | 125 |

|------------|--------------------------------------------------------------------------------|-----|

| Table 5-13 | Electrical Characteristics for Pins: OSD, DEBUG                                | 125 |

| Table 5-14 | Electrical Characteristics for Pin: NUV2                                       | 126 |

| Table 5-15 | Electrical Characteristics for Pins: DACLP                                     | 126 |

| Table 5-16 | Electrical Characteristics for Pin: VREG                                       | 126 |

| Table 5-17 | Switching Characteristics                                                      | 127 |

| Table 5-18 | <b>DESAT</b> characteristics                                                   | 129 |

| Table 5-19 | OCP characteristics                                                            | 129 |

| Table 5-20 | Over temperature Warning Characteristics                                       | 130 |

| Table 5-21 | Error Detection Timing                                                         | 131 |

| Table 5-22 | SPI Interface Characteristics                                                  | 132 |

| Table 5-23 | Isolation Characteristics referring to DIN EN 60747-5-2 (VDE 0884 - 2):2003-01 | 133 |

| Table 5-24 | Isolation Characteristics referring to LII 1577                                | 133 |

#### 1EDI2001AS

# 1 Product Definition

### 1.1 Overview

The 1EDI2001AS is a high-voltage IGBT gate driver designed for automotive motor drives above 5 kW. The 1EDI2001AS is based on Infineon's Coreless Transformer (CLT) technology, providing galvanic insulation between low voltage and high voltage domains. The device has been designed to support 400 V, 600 V and 1200 V IGBT technologies.

On the high voltage side ("secondary" side), the 1EDI2001AS is dimensioned to drive an external booster stage. Short propagation delays and controlled internal tolerances lead to minimal distortion of the PWM signal.

A large panel of safety-related functions has been implemented in the 1EDI2001AS, in order to support functional safety requirements at system level (as per ISO 26262). Besides, those integrated features ease the implementation of Active Short Circuit (ASC) strategies.

The 1EDI2001AS can be used optimally with Infineon's 1EBN100XAE "EiceDRIVER™ Boost" booster stage family.

# 1.2 Feature Overview

The following features are supported by the 1EDI2001AS:

#### **Functional Features**

- Single Channel IGBT Driver.

- On-chip galvanic insulation (up to 6kV).

- Support of 600 V and 1200 V IGBT technologies.

- Low propagation delay and minimal PWM distortion.

- Support of 5 V logic levels (primary side).

- 16-bit Standard SPI interface (up to 2 MBaud) with daisy chain support (primary side).

- Enable input pin (primary side).

- Pseudo-differential inputs for critical signals (primary side).

- Power-On Reset pin (primary side).

- Debug mode.

- Pulse Suppressor.

| Product Name | Ordering Code | Package   |

|--------------|---------------|-----------|

| 1EDI2001AS   | SP001361862   | PG-DSO-36 |

**Product Definition**

- Fully Programmable Active Clamping Inhibit signal (secondary side).

- Optimal support of EiceBoost functions.

- 36-pin PG-DSO-36 green package.

- · Automotive qualified (as per AEC Q100).

#### Safety Relevant Features

- Desaturation monitoring.

- · Overcurrent protection.

- Fully programmable Two-Level Turn-Off.

- · Automatic Emergency Turn-Off in failure case.

- Automatic or externally triggered disabling of the output stage (tristate).

- Under- and over-voltage supervision of all the power supplies (both primary and secondary sides).

- NFLTA and NFLTB notification pins for fast system response time (primary side).

- · Safe internal state machine.

- · Weak Turn-On functionality.

- · Internal overtemperature sensor (secondary side).

- · Internal clock monitoring.

- Gate signal monitoring.

- Individual error and status flags readable via SPI.

- Support for Active Short Circuit strategies.

- · Full diagnosticability.

- · In-application testability of safety critical functions.

- Suitable for systems up to ASIL D requirements (as per ISO 26262).

# 1.3 Target Applications

- Inverters for automotive Hybrid Electric Vehicles (HEV) and Electric Vehicles (EV).

- High Voltage DC/DC converter.

- Industrial Drive.

# 2 Functional Description

## 2.1 Introduction

The 1EDI2001AS is an advanced single channel IGBT driver that can also be used for driving power MOS devices. The device has been developed in order to optimize the design of high performance safety relevant automotive systems.

The device is based on Infineon's Coreless Transformer Technology and consist of two chips separated by a galvanic isolation. The low voltage (primary) side can be connected to a standard 5 V logic. The high voltage (secondary) side is in the DC-link voltage domain.

Internally, the data transfers are ensured by two independent communication channels. One channel is dedicated to transferring the ON and OFF information of the PWM input signal only. This channel is unidirectional (from primary to secondary). Because this channel is dedicated to the PWM information, latency time and PWM distortion are minimized. The second channel is bidirectional and is used for all the other data transfers (e.g. status information, etc).

The 1EDI2001AS supports advanced functions in order to optimize the switching behavior of the IGBT. Furthermore, it supports several monitoring and protection functions, making it suitable for systems having to fulfill ASIL requirements (as per ISO 26262).

# 2.2 Pin Configuration and Functionality

# 2.2.1 Pin Configuration

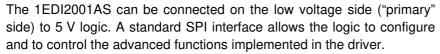

Figure 2-1 Pin Configuration

Table 2-1 Pin Configuration

| Pin<br>Number | Symbol | I/O    | Voltage Class | Function                              |

|---------------|--------|--------|---------------|---------------------------------------|

| 1,9,18        | VEE2   | Supply | Supply        | Negative Power Supply <sup>1)</sup> . |

| 2             | TON    | Output | 15V Secondary | Turn-On Output.                       |

| 3             | VCC2   | Supply | Supply        | Positive Power Supply.                |

| 4             | TOFF   | Output | 15V Secondary | Turn-Off Output.                      |

| 5             | DESAT  | Input  | 15V Secondary | Desaturation Protection Input.        |

| 6             | GATE   | Input  | 15V Secondary | Gate Monitoring Input.                |

| 7             | GND2   | Ground | Ground        | Ground.                               |

| 8             | IREF2  | Input  | 5V Secondary  | External Reference Input.             |

| 10            | VREG   | Output | 5V Secondary  | Reference Output Voltage.             |

| 11            | OCP    | Input  | 5V Secondary  | Over Current Protection.              |

| 12            | OCPG   | Ground | Ground        | Ground for the OCP function,          |

| 13            | DEBUG  | Input  | 5V Secondary  | Debug Input.                          |

Table 2-1 Pin Configuration (cont'd)

| Pin<br>Number | Symbol   | I/O          | Voltage Class | Function                                                                               |

|---------------|----------|--------------|---------------|----------------------------------------------------------------------------------------|

| 14            | DACLP    | Output       | 5V Secondary  | Active Clamping Disable Output.                                                        |

| -             |          | Output       |               | 1 0 1                                                                                  |

| 15            | OSD      | Input        | 5V Secondary  | Output Stage Disable Input.                                                            |

| 16            | Reserved | Reserved     | Reserved      | Reserved. This pin shall be connected to <b>GND2</b> .                                 |

| 17            | NUV2     | Output       | 5V Secondary  | V <sub>CC2</sub> not valid notification output.                                        |

| 19, 28, 36    | GND1     | Ground       | Ground        | Ground <sup>2)</sup> .                                                                 |

| 20            | Reserved | Reserved     | Reserved      | Reserved. This pin shall be connected to GND1.                                         |

| 21            | SCLK     | Input        | 5V Primary    | SPI Serial Clock Input.                                                                |

| 22            | SDI      | Input        | 5V Primary    | SPI Serial Data Input.                                                                 |

| 23            | NCS      | Input        | 5V Primary    | SPI Chip Select Input (low active).                                                    |

| 24            | SDO      | Output       | 5V Primary    | SPI Serial Data Output.                                                                |

| 25            | Reserved | Reserved     | Reserved      | Reserved. This pin shall be connected to GND1.                                         |

| 26            | NFLTB    | Output       | 5V Primary    | Fault B Output (low active, open drain).                                               |

| 27            | NFLTA    | Output       | 5V Primary    | Fault A Output (low active, open drain).                                               |

| 29            | NRST/RDY | Input/Output | 5V Primary    | Reset Input (low active, open drain). This signal notifies that the device is "ready". |

| 30            | EN       | Input        | 5V Primary    | Enable Input.                                                                          |

| 31            | REF0     | Ref. Ground  | Ground        | Reference Ground for signals INP, INSTP, EN.                                           |

| 32            | INP      | Input        | 5V Primary    | Positive PWM Input.                                                                    |

| 33            | INSTP    | Input        | 5V Primary    | Monitoring PWM Input.                                                                  |

| 34            | VCC1     | Supply Input | Supply        | Positive Power Supply.                                                                 |

| 35            | IREF1    | Input        | 5V Primary    | External Reference Input.                                                              |

<sup>1)</sup> All VEE2 pins must be connected together.

<sup>2)</sup> All GND1 pins must be connected together.

# 2.2.2 Pin Functionality

# 2.2.2.1 Primary Side

#### **GND1**

Ground connection for the primary side.

#### VCC<sub>1</sub>

5V power supply for the primary side (referring to GND1).

#### INP

Non-inverting PWM input of the driver. The internal structure of the pad makes the IC robust against glitches. An internal weak pull-down resistor to  $V_{REF0}$  drives this input to Low state in case the pin is floating.

#### **INSTP**

Monitoring PWM input for shoot through protection. The internal structure of the pad makes the IC robust against glitches. An internal weak pull-down resistor to  $V_{REF0}$  drives this input to Low state in case the pin is floating.

#### REF0

Reference Ground signal for the signals **INP**, **INSTP**, **EN**. This pin should be connected to the ground signal of the logic issuing those signals.

#### EN

Enable Input Signal. This signal allows the logic on the primary side to turn-off and deactivate the device. An internal weak pull-down resistor to  $V_{REF0}$  drives this input to Low state in case the pin is floating. This pin reacts on logic levels.

#### **NFLTA**

Open-Drain Output signal used to report major failure events (Event Class A). In case of an error event, **NFLTA** is driven to Low state. This pin shall be connected externally to  $V_{CC1}$  with a pull-up resistance.

## **NFLTB**

Open-Drain Output signal used to report major failure events (Event Class B). In case of an error event, **NFLTB** is driven to Low state. This pin shall be connected externally to  $V_{CC1}$  with a pull-up resistance.

## **SCLK**

Serial Clock Input for the SPI interface. An internal weak pull-up device to  $V_{CC1}$  drives this input to high state in case the pin is floating.

## **SDO**

Serial Data Output (push-pull) or the SPI interface.

#### **SDI**

Serial Data Input for the SPI interface. An internal weak pull-up device to  $V_{CC1}$  drives this input to high state in case the pin is floating.

#### NCS

Chip Select input for the SPI interface. This signal is low active. An internal weak pull-up device to  $V_{CC1}$  drives this input to High state in case the pin is floating.

#### IREF1

Reference input of the primary chip. This pin shall be connected to  $V_{\text{GND1}}$  via an external resistor.

## **NRST/RDY**

Open drain reset input. This signal is low-active. When a valid signal is received on this pin, the device is brought in its default state. This signal is also used as a "ready notification". A high level on this pin indicates that the primary chip is functional.

# 2.2.2.2 Secondary Side

#### VEE2

Negative power supply for the secondary side, referring to V<sub>GND2</sub>.

#### VCC<sub>2</sub>

Positive power supply for the secondary side, referring to V<sub>GND2</sub>.

#### GND<sub>2</sub>

Reference ground for the secondary side.

### **DESAT**

Desaturation Protection input pin. The function associated with this pin monitors the  $V_{CE}$  voltage of the IGBT. An internal pull-up resistor to  $V_{CC2}$  drives this signal to High level in case it is floating.

## **OCP**

Over Current Protection input pin. The function associated with this pin monitors the voltage across a sensing resistance located on the auxiliary path of a Current Sense IGBT. An internal weak pull-up resistor to the internal 5V reference drives this input to High state in case the pin is floating.

#### **OCPG**

Over Current Protection Ground.

## **TON**

Output pin for turning on the IGBT.

## **TOFF**

Output pin for turning off the IGBT.

# **GATE**

Input pin used to monitor the IGBT gate voltage.

### **OSD**

Output Stage Disable input. A High Level on this pin tristates the output stage. An internal weak pull-down resistor to  $V_{\text{GND2}}$  drives this input to Low state in case the pin is floating.

#### **DACLP**

Output pin used to disable the active clamping function of the booster.

#### **DEBUG**

Debug input pin. This pin is latched at power-up. When a High level is detected on this pin, the device enters a special mode where it can be operated without SPI interface. This feature is for development purpose only. This pin should normally be tied to  $V_{\text{GND2}}$ . An internal weak pull-down resistor to  $V_{\text{GND2}}$  drives this input to Low state in case the pin is floating.

#### IREF2

Reference input of the secondary chip. This pin shall be connected to  $V_{GND2}$  via an external resistor.

#### **VREG**

Reference Output voltage. This pin shall be connected to an external capacitance to V<sub>GND2</sub>.

#### NUV<sub>2</sub>

$V_{CC2}$  not valid notification signal (Open Drain). This signal drives a low level when  $V_{CC2}$  is not valid or when the internal 5V digital supply is not valid. When both supplies are valid, this pin is in high impedance state. This pin shall be connected externally to a 5V reference with a pull-up resistance.

#### 2.2.2.3 Pull Devices

Some of the pins are connected internally to pull-up or pull-down devices. This is summarized in Table 2-2.

Table 2-2 Internal pull devices

| Signal | Device                                |

|--------|---------------------------------------|

| INP    | Weak pull down to V <sub>REF0</sub>   |

| INSTP  | Weak pull down to V <sub>REF0</sub>   |

| EN     | Weak pull down to V <sub>REF0</sub>   |

| SCLK   | Weak pull up to V <sub>CC1</sub>      |

| SDI    | Weak pull up to V <sub>CC1</sub>      |

| NCS    | Weak pull up to V <sub>CC1</sub>      |

| DESAT  | Weak pull up to V <sub>CC2</sub>      |

| OSD    | Weak pull down to V <sub>GND2</sub>   |

| OCP    | Weak pull up to 5V internal reference |

| DEBUG  | Weak pull down to V <sub>GND2</sub>   |

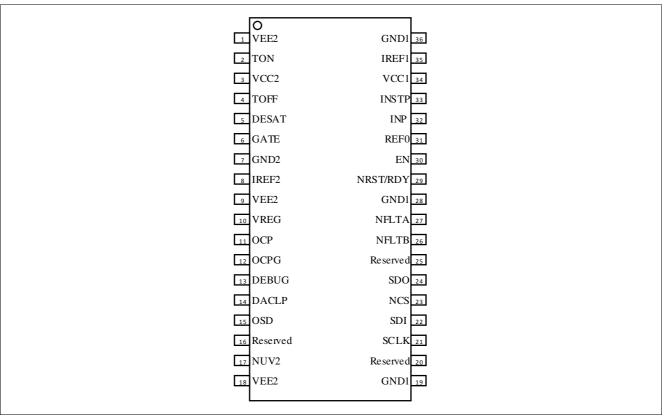

# 2.3 Block Diagram

Figure 2-2 Block Diagram

# 2.4 Functional Block Description

# 2.4.1 Power Supplies

On the primary side, the 1EDI2001AS needs a single 5 Vsupply source V<sub>CC1</sub> for proper operation. This makes the device compatible to most of the microcontrollers available for automotive applications.

On the secondary side, the 1EDI2001AS needs two power supplies for proper operation.

- The positive power supply V<sub>CC2</sub> is typically set to 15 V (referring to V<sub>GND2</sub>).

- The negative supply V<sub>EE2</sub> is typically set to -8 V (referring to V<sub>GND2</sub>).

Under- and over-voltage monitoring is performed continuously during operation of the device (see Chapter 3.3.1).

A 5V supply for the digital domain on the secondary side is generated internally (present at pin VREG).

#### 2.4.2 Clock Domains

The clock system of the 1EDI2001AS is based on three oscillators defining each a clock domain:

- · One RC oscillator (OSC1) for the primary chip.

- One RC oscillator (OSC2) for the secondary chip excepting the output stage.

- One Start-Stop oscillator (SSOSC2) for the output stage on the secondary side.

The two RC oscillators are running constantly. They are also monitored constantly, and large deviations from the nominal frequency are identified as a system failure (Event Class B, see **Chapter 3.3.2.2**).

The Start Stop oscillator is controlled by the PWM command.

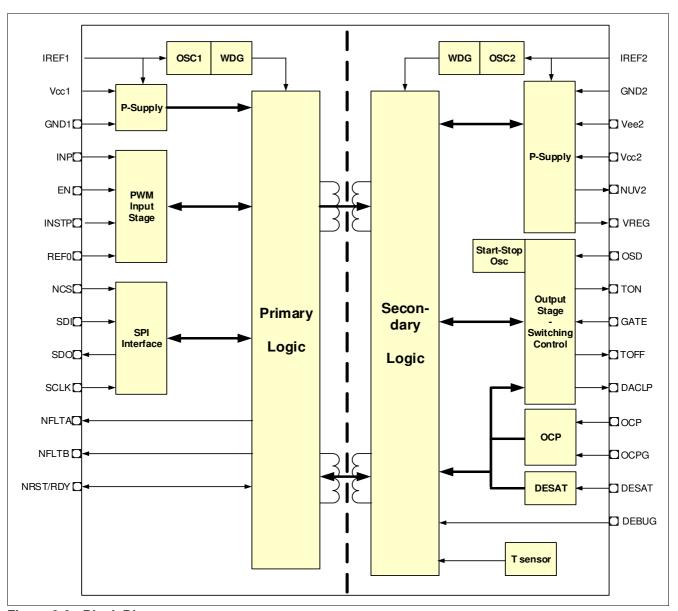

# 2.4.3 PWM Input Stage

The PWM input stage generates from the external signals **INP**, **INSTP** and **EN** the turn-on and turn-off commands to the secondary side. The general structure of the PWM input block is shown **Figure 2-3**.

Figure 2-3 PWM Input Stage

Signals INP, INSTP and EN are pseudo-differential, in the sense that they are not referenced to the common ground GND1 but to signal REF0. This is intended to make the device more robust against ground bouncing effects.

Note: Glitches shorter than  $t_{INPR1}$  occurring at signal INP are filtered internally.

Note: Pulses at INP below t<sub>INPPD</sub> might be distorted or suppressed.

The 1EDI2001AS supports non-inverted PWM signals only. When a High level on pin INP is detected while signals INSTP and ENare valid, a turn-on command is issued to the secondary chip. A Low level at pin INP issues a turn-off command to the secondary chip.

Signal **EN** can inhibit turn-on commands received at pin **INP**. A valid signal **EN** is required in order to have turn-on commands issued to the secondary chip. If an invalid signal is provided, the PWM input stage issues constantly turn-off commands to the secondary chip. The functionality of signal **EN** is detailed in **Chapter 2.4.8**.

Note: After an invalid-to valid-transition of signal **EN**, a minimum delay of t<sub>INPEN</sub> should be inserted before turning **INP** on.

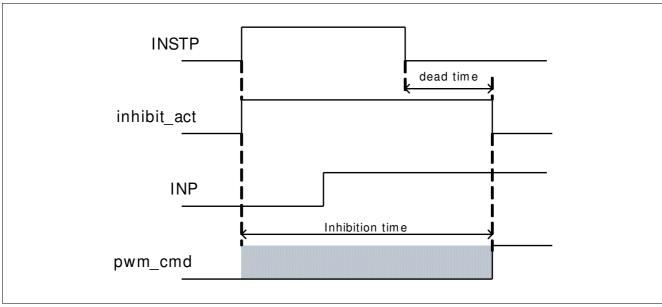

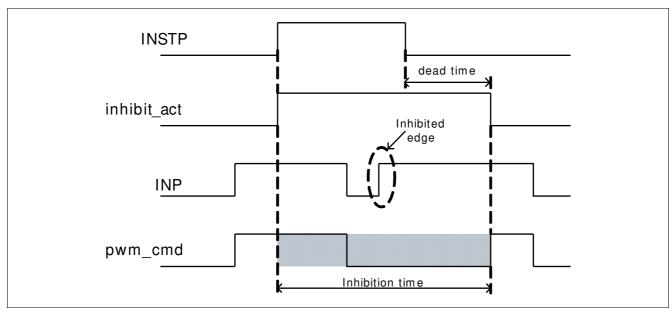

As shown in **Figure 2-4**, signal **INSTP** provides a Shoot-Through Protection (STP) to the system. When signal at pin **INSTP** is at High level, the internal signal <code>inhibit\_act</code> is activated. The inhibition time is defined as the pulse duration of signal inhibit\_act. It corresponds to the pulse duration of signal **INSTP** to which a minimum dead time is added. During the inhibition time, rising edges of signal **INP** are inhibited. Bit **PSTAT2.STP** is set for the duration of the inhibition time.

Figure 2-4 STP: Inhibition Time Definition

It shall be noted that during the inhibition time, signal pwm\_cmd is not forced to Low. It means that if the device is already turned-on when **INSTP** is High, it stays turned-on until the signal at pin **INP** goes Low. This is depicted in **Figure 2-5**.

Figure 2-5 STP: Example of Operation

When a condition occurs where a rising edge of signal INP is inhibited, an error notification is issued. See Chapter 3.4.1 for more details.

### 2.4.4 SPI Interface

This chapter describes the functionality of the SPI block.

#### 2.4.4.1 Overview

The standard SPI interface implemented on the 1EDI2001AS is compatible with most of the microcontrollers available for automotive and industrial applications. The following features are supported by the SPI interface:

- · Full-duplex bidirectional communication link.

- SPI Slave mode (only).

- 16-bit frame format.

- · Daisy chain capability.

- MSB first.

- Parity Check (optional) and Parity Bit generation (LSB).

The SPI interface of the 1EDI2001AS provides a standardized bidirectional communication interface to the main microcontroller. From the architectural point of view, it fulfills the following functions:

- Initialization of the device.

- Configuration of the device (static and runtime).

- Reading of the status of the device (static and runtime).

- Operation of the verification modes of the device.

The purpose of the SPI interface is to exchange data which have relaxed timing constraints compared to the PWM signals (from the point of view of the motor control algorithm). The IGBT switching behavior is for example controlled directly by the PWM input. Similarly, critical application failures requiring fast reaction are notified on the primary side via the feedback signals **NFLTA**, **NFLTB** and **NRST/RDY**.

In order to minimize the complexity of the end-application and to optimize the microcontroller's resources, the implemented interface has daisy chain capability. Several (typically 6) 1EDI2001AS devices can be combined into a single SPI bus.

# 2.4.4.2 General Operation

The SPI interface of the 1EDI2001AS supports full duplex operation. The interface relies on four communication signals:

- NCS: (Not) Chip Select.

- SCLK: Serial Clock.

- SDI: Serial Data In.

- SDO: Serial Data Out.

The SPI interface of the 1EDI2001AS supports slave operation only. An SPI master (typically, the main microcontroller) is connected to one or several 1EDI2001AS devices, forming an SPI bus. Several bus topologies are supported.

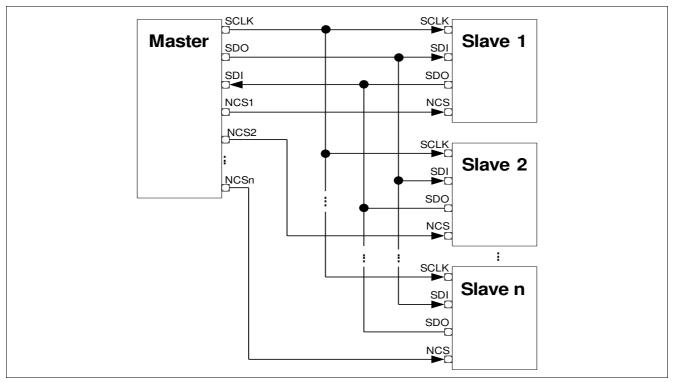

A regular SPI bus topology can be used where each of the slaves is controlled by an individual chip select signal (**Figure 2-6**). In this case, the number of slaves on the bus is only limited by the application's constraints.

Figure 2-6 SPI Regular Bus Topology

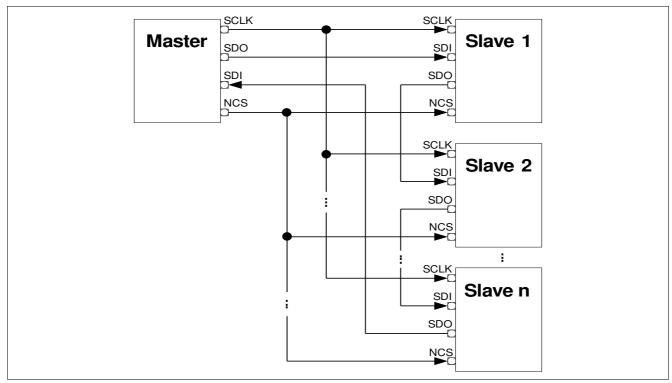

In order to simplify the layout of the PCB and to reduce the number of pins used on the microcontroller's side, a daisy chain topology can also be used. The chain's depth is not limited by the 1EDI2001AS itself. A possible topology is shown **Figure 2-7**.

Figure 2-7 SPI Daisy Chain Bus Topology

## **Physical Layer**

The SPI interface relies on two shift registers:

- A shift output register, reacting on the rising edges of SCLK.

- A shift input register, reacting on the falling edges of SCLK.

When signal NCS is inactive, the signals at pins SCLK and SDI are ignored. The output SDO is in tristate.

When NCS is activated, the shift output register is updated internally with the value requested by the previous SPI access.

At each rising edge of the **SCLK** signal (while **NCS** is active), the shift output register is serially shifted out by one bit on the **SDO** pin (MSB first). At each falling edge of the clock pulse, the data bit available at the input **SDI** is latched and serially shifted into the shift input register.

At the deactivation of NCS, the SPI logic checks how many rising and falling edges of the SCLK signal have been received. In case both counts differ and / or are not a multiple of 16, an SPI Error is generated. The SPI block then checks the validity of the received 16-bit word. In case of a non valid data, an SPI error is generated. In case no error is detected, the data is decoded by the internal logic.

The NCS signal is active low.

#### **Input Debouncing Filters**

The input stages of signals **SDI**, **SCLK**, and **NCS** include each a Debouncing Filter. The input signals are that way filtered from glitches and noise.

The input signals **SDI** and **SCLK** are analyzed at each edge of the internal clock derived from OSC1. If the same external signal value is sampled three times consecutively, the signal is considered as valid and is processed by the SPI logic. Otherwise, the transition is considered as a glitch and is discarded.