Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

## **CeraLink**<sup>™</sup>

Capacitors for fast-switching semiconductors

Series/Type: Low profile (LP) series

Ordering code: B58031\*

Date: 2017-02-15

Version: 5.0

© EPCOS AG 2016. Reproduction, publication and dissemination of this publication, enclosures hereto and the information contained therein without EPCOS' prior express consent is prohibited.

EPCOS AG is a TDK Group Company.

#### Capacitor for fast-switching semiconductors

Low profile (LP) series

## **Applications**

- · Power converters and inverters

- DC link/ snubber capacitor for power converters and inverters

#### **Features**

- High ripple current capability

- · High temperature robustness

- · Low equivalent serial inductance (ESL)

- Low equivalent serial resistance (ESR)

- Low power loss

- · Low dielectric absorption

- · Optimized for high frequencies up to several MHz

- · Increasing capacitance with DC bias up to operating voltage

- · High capacitance density

- · Minimized dielectric loss at high temperatures

- · Qualification based on AEC-Q200 rev. D

- Suitable for reflow soldering only

#### Construction

- RoHS-compatible PLZT ceramic (lead lanthanum zirconium titanate)

- · Copper inner electrodes

- · Silver outer electrodes

- · Silver coated copper-invar lead frame

#### General technical data

| Dissipation factor    | $	an \delta$          | < 0.02     |    |

|-----------------------|-----------------------|------------|----|

| Insulation resistance | R <sub>ins, typ</sub> | > 1        | GΩ |

| Operating device      | T <sub>device</sub>   | -40 +150   | °C |

| temperature           |                       |            |    |

| Weight of device      |                       | approx 1.3 | g  |

### Capacitor for fast-switching semiconductors

Low profile (LP) series

## Electrical specifications and ordering codes

| Lead    | V <sub>pk, max</sub> | V <sub>R</sub> | $V_{op}$ | C <sub>nom, typ</sub> | C <sub>eff, typ</sub> | C <sub>0</sub> | Ordering code   |

|---------|----------------------|----------------|----------|-----------------------|-----------------------|----------------|-----------------|

| type    | V                    | V              | V        | μF                    | μF                    | μF             |                 |

| L-style | 650                  | 500            | 400      | 1                     | 0.6                   | 0.35 ±20%      | B58031I5105M062 |

| J-style | 650                  | 500            | 400      | 1                     | 0.6                   | 0.35 ±20%      | B58031U5105M062 |

| L-style | 1000                 | 700            | 600      | 0.5                   | 0.25                  | 0.14 ±20%      | B58031I7504M062 |

| J-style | 1000                 | 700            | 600      | 0.5                   | 0.25                  | 0.14 ±20%      | B58031U7504M062 |

| L-style | 1300                 | 900            | 800      | 0.25                  | 0.13                  | 0.07 ±20%      | B58031I9254M062 |

| J-style | 1300                 | 900            | 800      | 0.25                  | 0.13                  | 0.07 ±20%      | B58031U9254M062 |

## **Typical values**

|                |       | ESR<br>0 V <sub>DC</sub> ,<br>0.5 V <sub>RMS</sub> ,<br>25 °C, 1 MHz | $\begin{array}{c} \textbf{ESR} \\ 0 \ V_{DC}, \\ 0.5 \ V_{RMS}, \\ 25 \ ^{\circ}\text{C}, 1 \ \text{kHz} \end{array}$ | ESL | I <sub>op</sub> <sup>1)</sup><br>100 kHz<br>T <sub>A</sub> = 85 °C | I <sub>op</sub> <sup>1)</sup><br>100 kHz<br>T <sub>A</sub> = 105 °C |

|----------------|-------|----------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|-----|--------------------------------------------------------------------|---------------------------------------------------------------------|

|                |       | mΩ                                                                   | Ω                                                                                                                     | nH  | A <sub>RMS</sub>                                                   | A <sub>RMS</sub>                                                    |

| V <sub>R</sub> | 500 V | 12                                                                   | 3                                                                                                                     | 2.5 | 11.4                                                               | 9.7                                                                 |

| V <sub>R</sub> | 700 V | 29                                                                   | 9                                                                                                                     | 2.5 | 7.1                                                                | 6.5                                                                 |

| V <sub>R</sub> | 900 V | 45                                                                   | 14                                                                                                                    | 2.5 | 5.1                                                                | 4.6                                                                 |

<sup>&</sup>lt;sup>1)</sup> Normal operating current without forced cooling at T<sub>device</sub> = 150 °C. Higher values permissible at reduced lifetime.

## **Packaging**

All types are delivered on 330-mm reel with 1000 pieces.

### Capacitor for fast-switching semiconductors

Low profile (LP) series

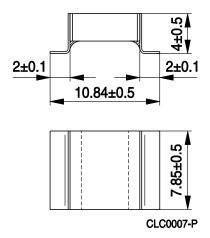

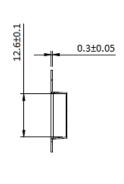

## **Dimensional drawings**

### L-style

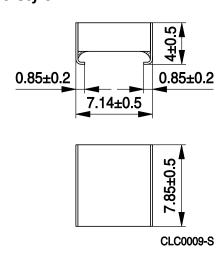

## J-style

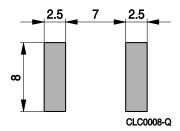

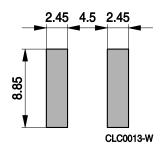

## Recommended solder pads

Dimensions in mm

### Capacitor for fast-switching semiconductors

Low profile (LP) series

## Polarity $V_R = 500 \text{ V}$

J-style L-style

## Polarity $V_R = 700 \text{ V}$

J-style L-style

## Polarity $V_R = 900 \text{ V}$

J-style

## **Marking of components**

Manufacturer's logo CeraLink™ type Nominal capacitance Rated voltage

## Capacitor for fast-switching semiconductors

Low profile (LP) series

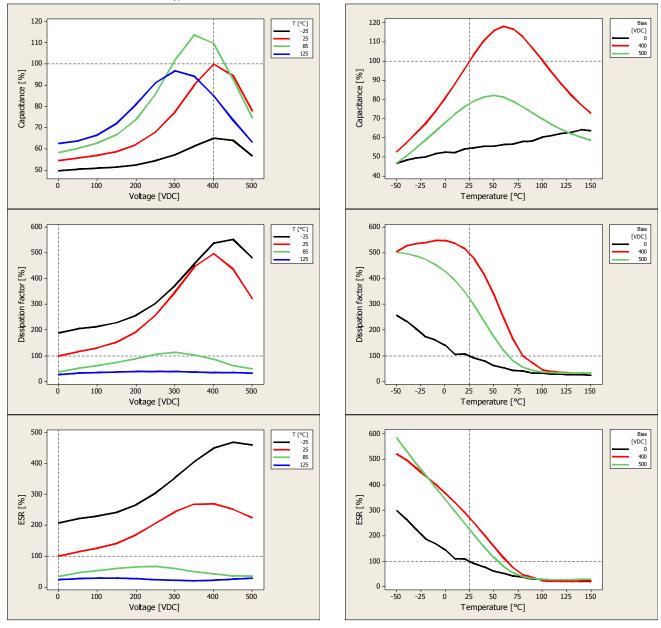

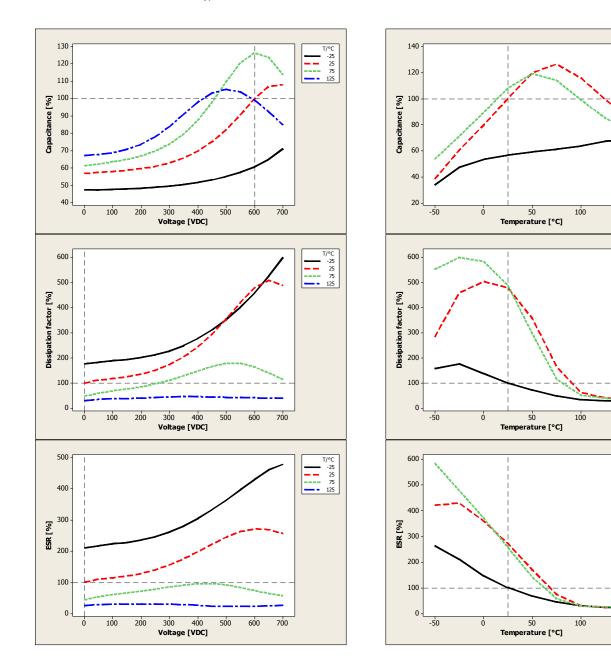

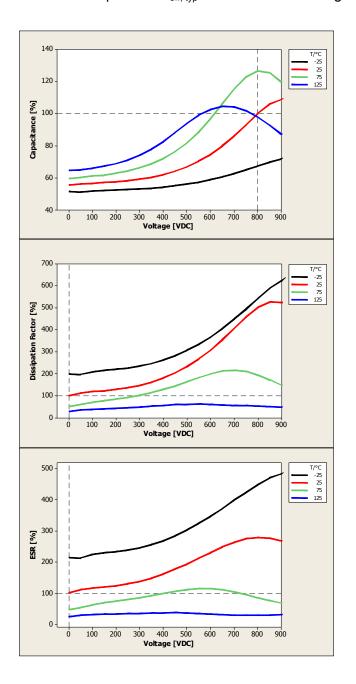

## Typical characteristics as a function of temperature and voltage $V_R = 500 \text{ V}$ ( $V_{AC} = 0.5 \text{ V}_{RMS}$ , frequency = 1 kHz)

All given temperatures are device temperatures.

The curves show the relative changes of the capacitance, dissipation factor and ESR. The 100% values correspond to  $C_{\text{eff,typ}}$  and tan  $\delta$  which are given on page 2 and 3 of this data sheet.

#### Capacitor for fast-switching semiconductors

Low profile (LP) series

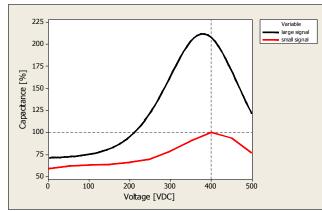

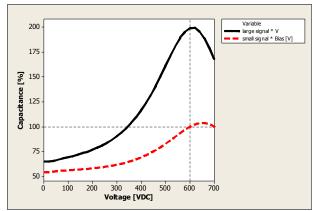

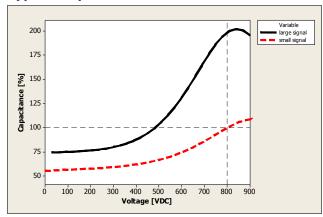

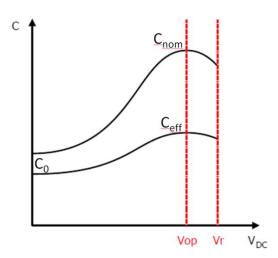

#### Typical capacitance values as a function of voltage $V_R = 500 \text{ V}$

Large signal capacitance:

Quasistatic (slow variation of the voltage), 25 °C

The nominal capacitance is defined as the large signal capacitance at  $V_{\text{op}}$ .

See glossary for further information.

Small signal capacitance:

0.5 V<sub>RMS</sub>, 1 kHz, 25 °C

The effective capacitance is defined as the small signal capacitance at  $V_{\text{op}}$ .

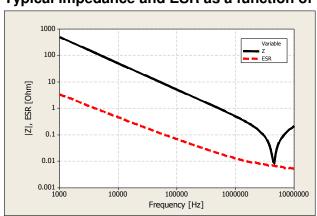

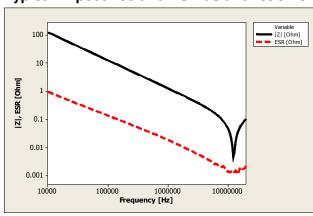

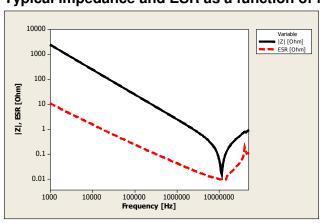

#### Typical impedance and ESR as a function of frequency $V_R = 500 \text{ V}$

$V_{DC} = 0 \text{ V}, V_{AC} = 0.5 \text{ V}_{RMS}, T_{device} = 25 \text{ °C}$

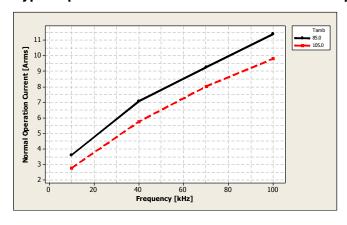

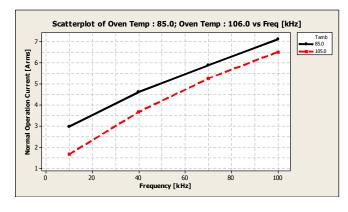

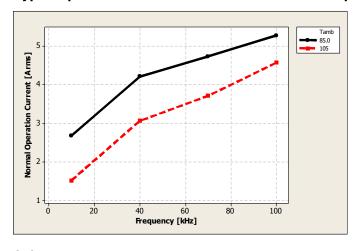

### Typical permissible current as a function of frequency $V_R = 500 \text{ V}$

Measurement performed at  $V_{\rm op}$ . The values correspond to a device temperature of 150 °C.

No forced cooling was used.

#### **Aging**

The capacitance has an aging behavior which shows a decrease of capacitance with time.

The typical aging rate is about 2.5% per logarithmic decade in hours.

## Capacitor for fast-switching semiconductors

Low profile (LP) series

150

150

150

Bias [VDC] 0 600

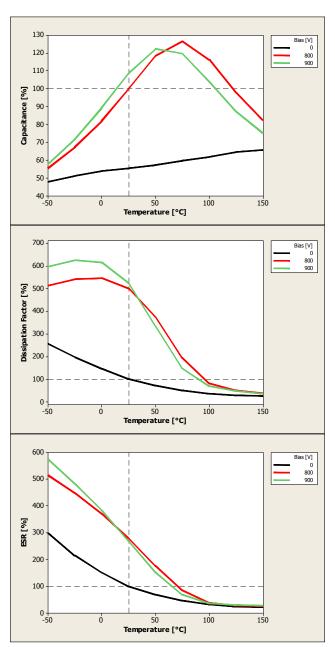

# Typical characteristics as a function of temperature and voltage $V_R = 700 \text{ V}$ ( $V_{AC} = 0.5 \text{ V}_{RMS}$ , frequency = 1 kHz)

All given temperatures are device temperatures.

The curves show the relative changes of the capacitance, dissipation factor and ESR. The 100% values correspond to  $C_{\text{eff, typ}}$  and tan  $\delta$  which are given on page 2 and 3 of this data sheet.

#### Capacitor for fast-switching semiconductors

Low profile (LP) series

#### Typical capacitance values as a function of voltage $V_R = 700 \text{ V}$

Large signal capacitance:

Quasistatic (slow variation of the voltage), 25 °C

The nominal capacitance is defined as the large signal capacitance at  $V_{\text{op}}.$

See glossary for further information.

Small signal capacitance:

0.5 V<sub>RMS</sub>, 1 kHz, 25 °C

The effective capacitance is defined as the small signal capacitance at  $V_{\text{op}}$ .

#### Typical impedance and ESR as a function of frequency $V_R = 700 \text{ V}$

$V_{DC} = 0 \text{ V}, V_{AC} = 0.5 \text{ V}_{RMS}, T_{device} = 25 \text{ °C}$

#### Typical permissible current as a function of frequency $V_R = 700 \text{ V}$

Measurement performed at  $V_{\text{op}}$ . The values correspond to a device temperature of 150 °C.

No forced cooling was used.

#### Aging

The capacitance has an aging behavior which shows a decrease of capacitance with time.

The typical aging rate is about 2.5% per logarithmic decade in hours.

## Capacitor for fast-switching semiconductors

Low profile (LP) series

# Typical characteristics as a function of temperature and voltage $V_R = 900 \text{ V}$ ( $V_{AC} = 0.5 \text{ V}_{RMS}$ , frequency = 1 kHz)

All given temperatures are device temperatures.

The curves show the relative changes of the capacitance, dissipation factor and ESR. The 100% values correspond to  $C_{\text{eff, typ}}$  and tan  $\delta$  which are given on page 2 and 3 of this data sheet.

#### Capacitor for fast-switching semiconductors

Low profile (LP) series

#### Typical capacitance values as a function of voltage $V_R = 900 \text{ V}$

Large signal capacitance:

Quasistatic (slow variation of the voltage), 25 °C The nominal capacitance is defined as the large signal capacitance at  $V_{\text{op}}$ .

See glossary for further information.

Small signal capacitance:

0.5 V<sub>RMS</sub>, 1 kHz, 25 °C

The effective capacitance is defined as the small signal capacitance at  $V_{\text{op}}$ .

#### Typical impedance and ESR as a function of frequency $V_R = 900 \text{ V}$

$V_{DC} = 0 \text{ V}, V_{AC} = 0.5 \text{ V}_{RMS}, T_{device} = 25 \text{ °C}$

#### Typical permissible current as a function of frequency $V_R = 900 \text{ V}$

Measurement performed at V<sub>op</sub>.

The values correspond to a device temperature of 150 °C.

No active cooling was used.

#### **Aging**

The capacitance has an aging behavior which shows a decrease of capacitance with time.

The typical aging rate is about 2.5% per logarithmic decade in hours.

#### Capacitor for fast-switching semiconductors

Low profile (LP) series

#### Reliability

A. Preconditioning:

- Reflow solder the capacitor on a PCB using the recommended soldering profile

- Check of external appearance

- Measurement of electrical parameters R<sub>ins</sub>, C<sub>0</sub>, tan δ

- $\circ$  Apply  $V_{pk,max}$  for 7 seconds and measure  $R_{ins}$  at room temperature: Isolation resistance (@  $V_{pk,max},$  7 s, 25 °C)

- Measure  $C_0$  and tan δ within 10 minutes to 1 hour afterwards: Initial capacitance (@ 0  $V_{DC}$ , 0.5  $V_{RMS}$ , 1 kHz, 25 °C) Dissipation factor (@ 0  $V_{DC}$ , 0.5  $V_{RMS}$ , 1 kHz, 25 °C)

- B. Performance of a specific reliability test.

- C. After performing a specific test:

- Check the external appearance again

- Repeat the measurement of the electrical parameters

- O Apply  $V_{pk,max}$  for 7 seconds and measure  $R_{ins}$  at room temperature: Isolation resistance (@  $V_{pk,max}$ , 7 s, 25 °C)  $R_{ins}$  > 10 MΩ

- o Measure C and tan δ: Change of initial capacitance (@ 0  $V_{DC}$ , 0.5  $V_{RMS}$ , 1 kHz, 25 °C) | Δ C / C<sub>0</sub> | < 15%

- o Dissipation factor (@ 0  $V_{DC}$ , 0.5  $V_{RMS}$ , 1 kHz, 25 °C) tan  $\delta$  < 0.05

| Test                                  | Standard                   | Test conditions                                                                       | Criteria                                                                                                                                                           |

|---------------------------------------|----------------------------|---------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| External appearance                   |                            | Visual inspection with magnifying glass                                               | No defects that might affect performance                                                                                                                           |

| High<br>temperature<br>operating life | MIL-STD-202,<br>method 108 | 150 °C, V <sub>R</sub> , 1000 hours                                                   | No mechanical damage $\mid \Delta \ C \ / \ C_0 \mid , \ tan \ \delta \ and \ R_{ins}$ within defined limits                                                       |

| Biased<br>humidity                    | MIL-STD-202,<br>method 103 | 85 °C, 85% rel. hum., V <sub>R</sub> , 1000 hours                                     | No mechanical damage $\mid \Delta \ C \ / \ C_0 \mid, \ \text{tan } \delta \ \text{and } R_{\text{ins}}$ within defined limits                                     |

| Temperature shock                     | IEC 60384-9,<br>4.8        | -55 °C to +150 °C<br>20 seconds transfer time<br>15 minutes dwell time<br>1000 cycles | No mechanical damage $\mid \Delta \; C \; / \; C_0 \mid \text{, tan } \delta \; \text{and } R_{\text{ins}}$ within defined limits                                  |

| Terminal strength test                | AEC-Q200-005               | Apply a force of 17.7 N for 60 seconds  Pushing force P.C.Board                       | No detaching of termination. No rupture of ceramic $\mid \Delta \; C \; / \; C_0 \mid , \; \text{tan } \delta \; \text{and } R_{\text{ins}}$ within defined limits |

## **Capacitor for fast-switching semiconductors**

## Low profile (LP) series

| Test                                     | Standard                                          | Test conditions                                                                                                                                                                                             | Criteria                                                                                                                                                     |

|------------------------------------------|---------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Tensile<br>strength test<br>(unsoldered) |                                                   | Apply a force of 10 N in the shown direction.  Ceramic body is clamped:                                                                                                                                     | No detaching of termination. No rupture of ceramic $\mid \Delta \ C \ / \ C_0 \mid, \ \text{tan } \delta \ \text{and } R_{\text{ins}}$ within defined limits |

| Board flex                               | AEC-Q200-005                                      | Bending of 2 mm for 60 seconds  Support  Solder Chip Printed circuit board before testing  45±2  Radius 340  Probe to exert bending force  Printed circuit board under test  Displacement  Dimensions in mm | No mechanical damage $\mid \Delta \ C \ / \ C_0 \mid, \ \text{tan } \delta \ \text{and } R_{\text{ins}}$ within defined limits                               |

| Vibration                                | MIL-STD-202,<br>method 204                        | 5 g/ 20 min, 12 cycles, 3 axis<br>10 Hz to 2000 Hz                                                                                                                                                          | No mechanical damage $\mid \Delta \; C \; / \; C_0 \mid , \; \text{tan } \delta \; \text{and } R_{\text{ins}}$ within defined limits                         |

| Mechanical<br>shock                      | MIL-STD-202,<br>method 213                        | Acceleration 400 m/s <sup>2</sup> Half sine pulse duration 6 milliseconds 4000 bumps                                                                                                                        | No mechanical damage $\mid \Delta \ C \ / \ C_0 \mid, \ \text{tan } \delta \ \text{and } R_{\text{ins}}$ within defined limits                               |

| Reflow test                              |                                                   | 3 times recommended reflow soldering profile                                                                                                                                                                | No mechanical damage Proper solder coating of contact areas   Δ C / C <sub>0</sub>  , tan δ and R <sub>ins</sub> within defined limits                       |

| Leaching test<br>(lead frame<br>only)    | MIL-STD-202,<br>method 210,<br>condition B        | Dip test of contact areas in solder bath (260 °C for 10 seconds)                                                                                                                                            | No damage of lead frame silver coating                                                                                                                       |

| Solderability<br>(lead frame<br>only)    | J-STD-002,<br>method A @<br>235 °C,<br>category 3 | Dip test of contact areas in solder bath (235 °C for 5 ± 0.5 seconds)                                                                                                                                       | > 95% wettability of lead frame                                                                                                                              |

| Resistance to solvent                    |                                                   | Dipping and cleaning with isopropanol                                                                                                                                                                       | Marking must be legible<br>  Δ C / C0  , tan δ and R <sub>ins</sub> within defined limits                                                                    |

| Geometry                                 |                                                   | Using a caliper                                                                                                                                                                                             | Within specified tolerance in the chapter construction                                                                                                       |

### Capacitor for fast-switching semiconductors

Low profile (LP) series

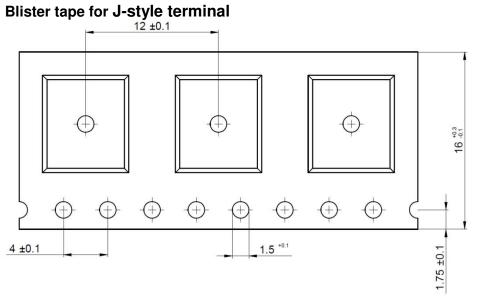

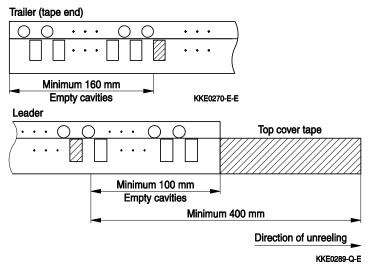

## **Packaging**

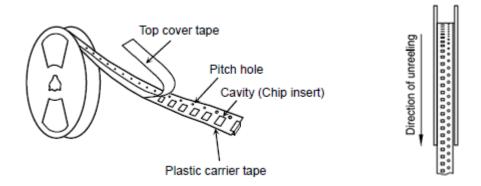

The CeraLink™ will be delivered in a blister tape (taping to IEC 60286-3).

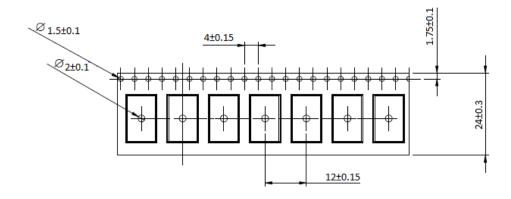

### Blister tape for L-style terminal

PPD MT IC

#### Capacitor for fast-switching semiconductors

Low profile (LP) series

#### Part orientation for L-style terminal

#### Part orientation for J-style terminal

#### **Taping information**

Trailer: There is a minimum of 160 mm of carrier tape with empty compartments and sealed by the cover tape.

Leader: There is a minimum of 400 mm of cover tape, which includes at least 100 mm of carrier tape with empty compartments.

Dimensions in mm

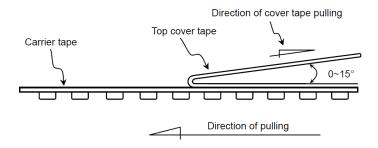

## Fixing peeling strength (top tape)

The peeling strength is 0.1 ... 1.3 N.

### Capacitor for fast-switching semiconductors

Low profile (LP) series

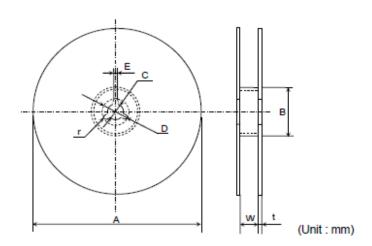

## Reel packing

|   | L-style terminal | J-style terminal |

|---|------------------|------------------|

| Α | 330 ±2           | 330 ±2           |

| В | 100 ±1           | 62 ±1            |

| С | 13 +0.5/ -0.2    | 12.8 +0.7        |

| D | 20.2 min.        | 19.1 min.        |

| E | 2.2 ±0.2         | 1.6 ±0.5         |

| W | 24.2 +2          | 16.4 +2          |

#### Dimensions in mm

## Capacitor for fast-switching semiconductors

Low profile (LP) series

## Recommended reflow soldering profile

| Profile feature                                                               |                                        | SAC, Sn95.5Ag3.8Cu0.7 @ N <sub>2</sub> atmosphere |

|-------------------------------------------------------------------------------|----------------------------------------|---------------------------------------------------|

| Preheat and soak                                                              |                                        |                                                   |

| - Temperature min                                                             | T <sub>smin</sub>                      | 150 °C                                            |

| - Temperature max                                                             | T <sub>smax</sub>                      | 200 °C                                            |

| - Time                                                                        | t <sub>smin</sub> to t <sub>smax</sub> | 60 120 seconds                                    |

| Average ramp-up rate                                                          | T <sub>L</sub> to T <sub>p</sub>       | 3 °C/ second max.                                 |

| Liquidus temperature                                                          | T <sub>L</sub>                         | 217 °C                                            |

| Time at liquidus temperature                                                  | t <sub>L</sub>                         | 60 150 seconds                                    |

| Peak package body temperature                                                 | T <sub>p</sub> <sup>1)</sup>           | 245 °C 260 °C max. <sup>2)</sup>                  |

| Time $(t_p)^{3)}$ within 5 °C of specified classification temperature $(T_c)$ |                                        | 30 seconds <sup>3)</sup>                          |

| Average ramp-down rate                                                        | T <sub>p</sub> to T <sub>L</sub>       | 6 °C/ second max.                                 |

| Time 25 °C to peak temperature                                                |                                        | maximum 8 minutes                                 |

- 1) Tolerance for peak profile temperature (T<sub>p</sub>) is defined as a supplier minimum and a user maximum.

- 2) Depending on package thickness. For details please refer to JEDEC J-STD-020D.

- 3) Tolerance for time at peak profile temperature (tp) is defined as a supplier minimum and a user maximum.

#### Notes:

All temperatures refer to topside of the package, measured on the package body surface.

Max. number of reflow cycles: 3

After the soldering process, the capacitance is lowered. Applying V<sub>R</sub> to the device will re-establish the capacitance.

The components are suitable for reflow soldering to JEDEC J-STD-020D.

#### Capacitor for fast-switching semiconductors

Low profile (LP) series

#### General technical information

#### Storage

- Only store CeraLink™ capacitors in their original packaging. Do not open the package prior to processing.

- Storage conditions in original packaging: temperature −25 °C to +45 °C, relative humidity ≤ 75% annual average, maximum 95%, dew precipitation is inadmissible.

- Do not store CeraLink<sup>™</sup> capacitors where they are exposed to heat or direct sunlight.

Otherwise the packaging material may be deformed or CeraLink<sup>™</sup> may stick together, causing problems during mounting.

- Avoid contamination of the CeraLink™ surface during storage, handling and processing.

- Avoid storing CeraLink<sup>™</sup> devices in harmful environments where they are exposed to corrosive gases (e.g. SOx, Cl).

- Use CeraLink<sup>™</sup> as soon as possible after opening factory seals such as polyvinyl-sealed packages.

- Solder CeraLink<sup>™</sup> components within 6 months after shipment from EPCOS.

#### Handling

- Do not drop CeraLink™ components or allow them to be chipped.

- Do not touch CeraLink™ with your bare hands gloves are recommended.

- Avoid contamination of the CeraLink™ surface during handling.

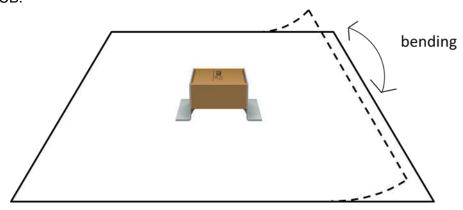

- The CeraLink™ was tested to withstand the board flex test defined in the AEC-Q200 rev. D, method 005.

- The CeraLink™ uses copper lead frames to prevent mechanical stress to the ceramic. Too

much bending causes open mode. Avoid high mechanical stress like twisting after soldering

on a PCB.

CeraLink™ \_\_\_\_\_B58031\*

#### Capacitor for fast-switching semiconductors

Low profile (LP) series

#### Mounting

- Do not subject CeraLink™ devices to mechanical stress when encapsulating them with sealing material or overmolding with plastic material. Encapsulation may lead to worse heat dissipation too. Please ask for further information.

- Do not scratch the electrodes before, during or after the mounting process.

- Make sure contacts and housings used for assembly with CeraLink™ components are clean before mounting.

- The surface temperature of an operating CeraLink™ can be higher than the ambient temperature. Ensure that adjacent components are placed at a sufficient distance from a CeraLink™ to allow proper cooling.

- Avoid contamination of the CeraLink™ surface during processing.

#### Soldering

- The use of mild, non-activated fluxes for soldering is recommended, as well as proper cleaning of the PCB.

- Complete removal of flux is recommended to avoid surface contamination that can result in an instable and/or high leakage current.

- Use resin-type or non-activated flux.

- Bear in mind that insufficient preheating may cause ceramic cracks.

- Rapid cooling by dipping in solvent is not recommended, otherwise a component may crack.

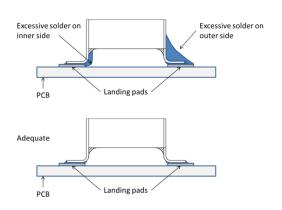

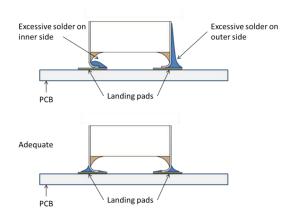

- Excessive usage of solder paste can reduce the mechanical robustness of the device, whereas insufficient solder may cause the CeraLink™ to detach from the PCB. Use an adequate amount of solder paste, but on the landing pads only.

- If an unsuitable cleaning fluid is used, flux residue or foreign particles may stick to the CeraLink™ surface and deteriorate its insulation resistance. Insufficient or improper cleaning of the CeraLink™ may cause damage to the component.

- Excessive washing like ultrasonic cleaning, can affect the connection between the ceramic chip and the outer electrode. To avoid this, we give the following recommendation:

- o Power: 20 W/I max.

- Frequency: 40 kHz max.

- Washing time: 5 minutes max.

#### Capacitor for fast-switching semiconductors

Low profile (LP) series

## **Glossary**

Initial capacitance C<sub>0</sub>: Is the value at the origin of the hysteresis without any applied direct

voltage.

Effective capacitance C<sub>eff</sub>:

Occurs at  $V_{op}$  and is measured with an applied ripple voltage of 0.5  $V_{\text{RMS}}$  and 1 kHz. The CeraLink  $^{\text{TM}}$  is designed to have its highest

capacitance value at the operating voltage  $V_{op}$ .

Nominal capacitance C<sub>nom</sub>: Is the value derived by the tangent of the mean hysteresis as the

derivation of the mean hysteresis is dQ/dV ~ C.

#### Capacitor for fast-switching semiconductors

Low profile (LP) series

#### Symbols and terms

AC Alternating current

C<sub>0</sub> Initial capacitance @ 0 V<sub>DC</sub>, 0.5 V<sub>RMS</sub>, 1 kHz, 25 °C

C<sub>eff,typ</sub> Typical effective capacitance @ V<sub>op</sub>, 0.5 V<sub>RMS</sub>, 1 kHz, 25 °C

$C_{\text{nom,typ}}$  Typical nominal capacitance @  $V_{\text{op}}$ , quasistatic, 25 °C. See glossary (page 20)

for definition of the nominal capacitance

DC Direct current

ESL Equivalent serial inductance

ESR Equivalent serial resistance

I<sub>op</sub> Operating ripple current, root mean square value of sinusoidal AC current

LP Low profile

PCB Printed circuit board

PLZT Lead lanthanum zirconium titanate

R<sub>ins</sub> Insulation resistance

$R_{ins, typ}$  Insulation resistance @  $V_{op}$ , t > 240 s, 25 °C SAC Tin silver copper alloy; lead-free solder paste

T<sub>A</sub> Ambient temperature

tan  $\delta$  Dissipation factor @ 0 V<sub>dc</sub>, 0.5 V<sub>rms</sub> 1 kHz, 25°C

$T_{device}$  Device temperature.  $T_{device} = T_A + \Delta T$  ( $\Delta T$  defines the self-heating of the device

due to applied current).

$V_{op}$  Operating voltage  $V_{B}$  Rated voltage

$V_{\text{RMS}}$  Root mean square value of sinusoidal AC voltage  $V_{\text{pk,max}}$  Maximum peak operating voltage @  $V_{\text{pk,max}}$ , 25 °C, 7 s

ΔT Increase of temperature during operation

#### Capacitor for fast-switching semiconductors

Low profile (LP) series

#### **Cautions and warnings**

#### General

Not for use in resonant circuits, where a voltage of alternating polarity occurs.

Not for AC applications. Consult your EPCOS representative for further details.

If used in snubber circuits, ensure that the sum of all voltages remains at the same polarity.

Some parts of this publication contain statements about the suitability of our CeraLink™ components for certain areas of application, including recommendations about incorporation/design-in of these products into customer applications. The statements are based on our knowledge of typical requirements often made of our CeraLink™ devices in the particular areas. We nevertheless expressly point out that such statements cannot be regarded as binding statements about the suitability of our CeraLink™ components for a particular customer application. As a rule, EPCOS is either unfamiliar with individual customer applications or less familiar with them than the customers themselves. For these reasons, it is always incumbent on the customer to check and decide whether the CeraLink™ devices with the properties described in the product specification are suitable for use in a particular customer application.

- Do not use EPCOS CeraLink™ components for purposes not identified in our specifications.

- Ensure the suitability of a CeraLink™ in particular by testing it for reliability during design-in. Always evaluate a CeraLink™ component under worst-case conditions.

- Pay special attention to the reliability of CeraLink™ devices intended for use in safety-critical applications (e.g. medical equipment, automotive, spacecraft, nuclear power plant).

#### Design notes

- Consider derating at higher operating temperatures. As a rule, lower temperatures and voltages increase the life time of CeraLink™ devices.

- If steep surge current edges are to be expected, make sure your design is as low-inductive as possible.

- In some cases the malfunctioning of passive electronic components or failure before the end of their service life cannot be completely ruled out in the current state of the art, even if they are operated as specified. In applications requiring a very high level of operational safety and especially when the malfunction or failure of a passive electronic component could endanger human life or health (e.g. in accident prevention, life-saving systems, or automotive battery line applications such as clamp 30), ensure by suitable design of the application or other measures (e.g. installation of protective circuitry, fuse or redundancy) that no injury or damage is sustained by third parties in the event of such a malfunction or failure.

- Specified values only apply to CeraLink™ components that have not been subject to prior electrical, mechanical or thermal damage. The use of CeraLink™ devices in line-to-ground applications is therefore not advisable, and it is only allowed together with safety countermeasures such as thermal fuses.

CeraLink™ \_\_\_\_\_B58031\*

#### Capacitor for fast-switching semiconductors

Low profile (LP) series

#### Operation

- Use CeraLink<sup>™</sup> only within the specified operating temperature range.

- Use CeraLink™ only within specified voltage and current ranges.

- The CeraLink has to be operated in a dry atmosphere, which must not contain any additional chemical vapors or substances.

- Environmental conditions must not harm the CeraLink™. Use the capacitors under normal atmospheric conditions only. A reduction of the oxygen partial pressure to below 1 mbar is not permissible.

- Prevent a CeraLink™ from contacting liquids and solvents.

- Avoid dewing and condensation.

- During operation, the CeraLink<sup>™</sup> can produce audible noise due to its piezoelectric characteristic.

- EPCOS CeraLink™ components are mainly designed for encased applications. Under all circumstances avoid exposure to:

- o direct sunlight

- o rain or condensation

- o steam, saline spray

- o corrosive gases

- o atmosphere with reduced oxygen content

This listing does not claim to be complete, but merely reflects the experience of EPCOS AG.

#### Display of ordering codes for EPCOS products

The ordering code for one and the same EPCOS product can be represented differently in data sheets, data books, other publications, on the EPCOS website, or in order-related documents such as shipping notes, order confirmations and product labels. The varying representations of the ordering codes are due to different processes employed and do not affect the specifications of the respective products. Detailed information can be found on the Internet under www.epcos.com/orderingcodes

#### Important notes

The following applies to all products named in this publication:

- 1. Some parts of this publication contain statements about the suitability of our products for certain areas of application. These statements are based on our knowledge of typical requirements that are often placed on our products in the areas of application concerned. We nevertheless expressly point out that such statements cannot be regarded as binding statements about the suitability of our products for a particular customer application. As a rule, EPCOS is either unfamiliar with individual customer applications or less familiar with them than the customers themselves. For these reasons, it is always ultimately incumbent on the customer to check and decide whether an EPCOS product with the properties described in the product specification is suitable for use in a particular customer application.

- 2. We also point out that in individual cases, a malfunction of electronic components or failure before the end of their usual service life cannot be completely ruled out in the current state of the art, even if they are operated as specified. In customer applications requiring a very high level of operational safety and especially in customer applications in which the malfunction or failure of an electronic component could endanger human life or health (e.g. in accident prevention or life-saving systems), it must therefore be ensured by means of suitable design of the customer application or other action taken by the customer (e.g. installation of protective circuitry or redundancy) that no injury or damage is sustained by third parties in the event of malfunction or failure of an electronic component.

- 3. The warnings, cautions and product-specific notes must be observed.

- 4. In order to satisfy certain technical requirements, some of the products described in this publication may contain substances subject to restrictions in certain jurisdictions (e.g. because they are classed as hazardous). Useful information on this will be found in our Material Data Sheets on the Internet (www.epcos.com/material). Should you have any more detailed questions, please contact our sales offices.

- 5. We constantly strive to improve our products. Consequently, the products described in this publication may change from time to time. The same is true of the corresponding product specifications. Please check therefore to what extent product descriptions and specifications contained in this publication are still applicable before or when you place an order. We also reserve the right to discontinue production and delivery of products. Consequently, we cannot guarantee that all products named in this publication will always be available. The aforementioned does not apply in the case of individual agreements deviating from the foregoing for customer-specific products.

- 6. Unless otherwise agreed in individual contracts, all orders are subject to the current version of the "General Terms of Delivery for Products and Services in the Electrical Industry" published by the German Electrical and Electronics Industry Association (ZVEI).

- 7. The trade names EPCOS, CeraDiode, CeraLink, CeraPad, CeraPlas, CSMP, CSSP, CTVS, DeltaCap, DigiSiMic, DSSP, ExoCore, FilterCap, FormFit, LeaXield, MAGicCharge, MiniBlue, MiniCell, MKD, MKK, MotorCap, PCC, PhaseCap, PhaseCube, PhaseMod, PhiCap, PQSine, SIFERRIT, SIFI, SIKOREL, SilverCap, SIMDAD, SiMic, SIMID, SineFormer, SIOV, SIP5D, SIP5K, TFAP, ThermoFuse, WindCap are trademarks registered or pending in Europe and in other countries. Further information will be found on the Internet at www.epcos.com/trademarks.