# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# PRODUCT MANUAL

# **Rabbit 2000<sup>®</sup> Microprocessor**

# **User's Manual**

019-0069 • 070831-P

#### Rabbit 2000 Microprocessor User's Manual

Part Number 019-0069 • 070831–P • Printed in U.S.A.

©2002–2007 Rabbit Semiconductor Inc. • All rights reserved.

No part of the contents of this manual may be reproduced or transmitted in any form or by any means without the express written permission of Rabbit Semiconductor.

Permission is granted to make one or more copies as long as the copyright page contained therein is included. These copies of the manuals may not be let or sold for any reason without the express written permission of Rabbit Semiconductor.

Rabbit Semiconductor reserves the right to make changes and improvements to its products without providing notice.

#### **Trademarks**

Rabbit and Dynamic C are registered trademarks of Rabbit Semiconductor Inc. Rabbit 2000 is a trademark of Rabbit Semiconductor Inc.

The latest revision of this manual is available on the Rabbit Semiconductor Web site, www.rabbit.com, for free, unregistered download.

#### Rabbit Semiconductor Inc.

www.rabbit.com

# TABLE OF CONTENTS

| Chapter 1. Introduction                                         | <b>1</b> |

|-----------------------------------------------------------------|----------|

| 1.1 Features and Specifications                                 |          |

| 1.2 Summary of Rabbit Advantages                                | 3        |

| Chapter 2. Rabbit Design Features                               | 7        |

| 2.1 The Rabbit 8-bit Processor vs. 16-bit and 32-bit Processors | 8        |

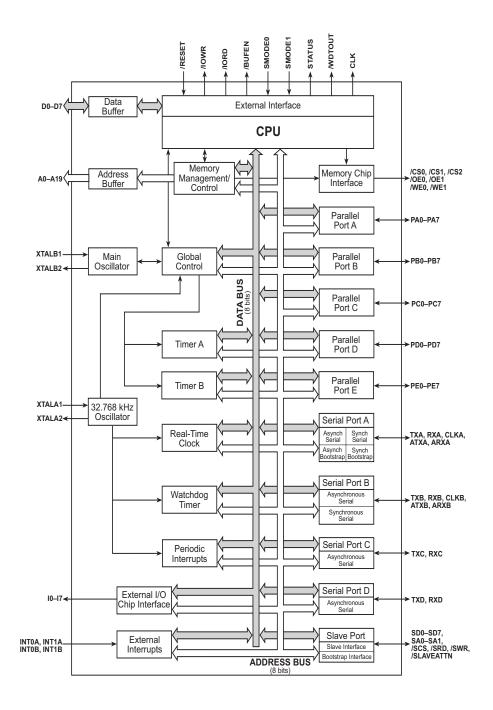

| 2.2 Overview of On-Chip Peripherals                             |          |

| 2.2.1 Serial Ports                                              | 8        |

| 2.2.2 System Clock                                              | 8        |

| 2.2.3 Time/Date Oscillator                                      | 9        |

| 2.2.4 Parallel I/O                                              | 9        |

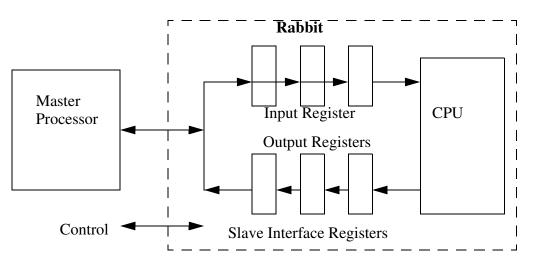

| 2.2.5 Slave Port                                                | 10       |

| 2.2.6 Timers                                                    | 10       |

| 2.3 Design Standards                                            | 12       |

| 2.3.1 Programming Port                                          |          |

| 2.3.2 Standard BIOS                                             |          |

| 2.4 Dynamic C Support for the Rabbit                            | 12       |

# Chapter 3. Details on Rabbit

| Microprocessor Features                                         | 13 |

|-----------------------------------------------------------------|----|

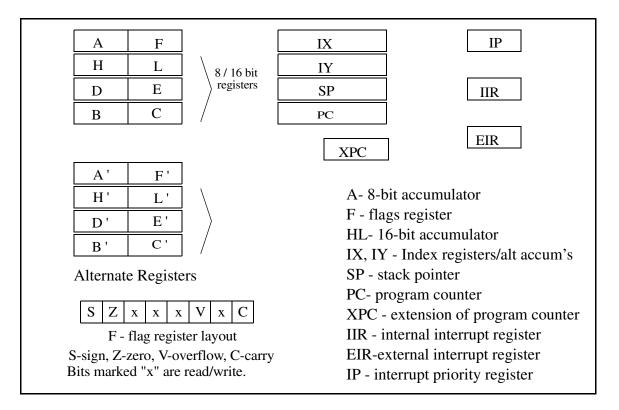

| 3.1 Processor Registers                                         |    |

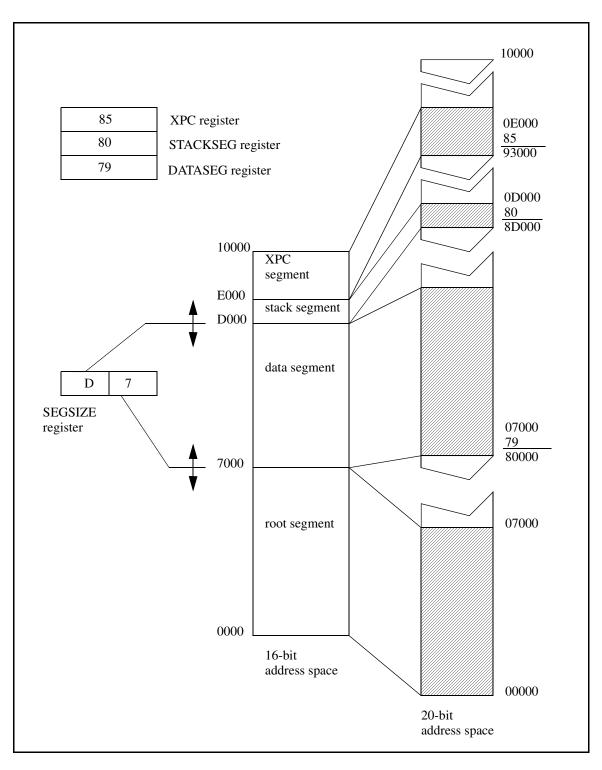

| 3.2 Memory Mapping                                              |    |

| 3.2.1 Extended Code Space                                       |    |

| 3.2.2 Extending Data Memory                                     |    |

| 3.2.3 Practical Memory Considerations                           |    |

| 3.3 Instruction Set Outline                                     |    |

| 3.3.1 Load Immediate Data To a Register                         |    |

| 3.3.2 Load or Store Data from or to a Constant Address          |    |

| 3.3.3 Load or Store Data Using an Index Register                |    |

| 3.3.4 Register to Register Move                                 | 25 |

| 3.3.5 Register Exchanges                                        | 25 |

| 3.3.6 Push and Pop Instructions                                 |    |

| 3.3.7 16-bit Arithmetic and Logical Ops                         | 26 |

| 3.3.8 Input/Output Instructions                                 | 29 |

| 3.4 How to Do It in Assembly Language—Tips and Tricks           |    |

| 3.4.1 Zero HL in 4 Clocks                                       |    |

| 3.4.2 Exchanges Not Directly Implemented                        |    |

| 3.4.3 Manipulation of Boolean Variables                         |    |

| 3.4.4 Comparisons of Integers                                   | 32 |

| 3.4.5 Atomic Moves from Memory to I/O Space                     |    |

| 3.5 Interrupt Structure                                         |    |

| 3.5.1 Interrupt Priority                                        | 35 |

| 3.5.2 Multiple External Interrupting Devices                    |    |

| 3.5.3 Privileged Instructions, Critical Sections and Semaphores |    |

| 3.5.4 Critical Sections                                         |    |

| 3.5.5 Semaphores Using Bit B,(HL)                               |    |

| 3.5.6 Computed Long Calls and Jumps                             |    |

| Chapter 4. Rabbit Capabilities                           | 41  |

|----------------------------------------------------------|-----|

|                                                          |     |

| 4.1.1 Pulse Width Modulation to Reduce Relay Power       |     |

|                                                          |     |

|                                                          |     |

|                                                          |     |

| 4.4.1 Slave Rabbit As A Protocol UART                    |     |

| Chapter 5. Pin Assignments and Functions                 | 49  |

| 5.1 Package Schematic and Pinout                         | 49  |

|                                                          |     |

| 5.3 Rabbit Pin Descriptions                              |     |

| 5.4 Bus Timing                                           |     |

|                                                          |     |

|                                                          |     |

|                                                          |     |

| 5.6.2 3.3 Volts                                          |     |

| 5.7 I/O Buffer Sourcing and Sinking Limit                | 64  |

| Chapter 6. Rabbit Internal I/O Registers                 | 65  |

|                                                          |     |

|                                                          |     |

| Chapter 7. Miscellaneous I/O Functions                   | 71  |

|                                                          |     |

|                                                          |     |

|                                                          |     |

|                                                          |     |

|                                                          |     |

| 7.6 Time/Date Clock (Real-Time Clock)                    | 78  |

| 7.7 Watchdog Timer                                       | 80  |

| 7.8 System Reset                                         |     |

| 7.9 Rabbit Interrupt Structure                           |     |

| 7.9.1 External Interrupts                                |     |

| 7.9.2 Interrupt Vectors: INT0 - EIR,0x00/INT1 - EIR,0x08 |     |

| 7.10 Bootstrap Operation                                 | 88  |

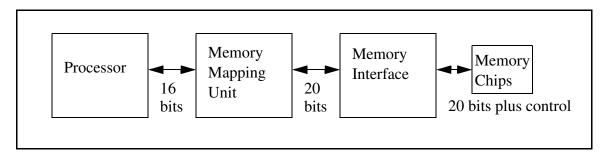

| Chapter 8. Memory Mapping and Interface                  | 91  |

|                                                          |     |

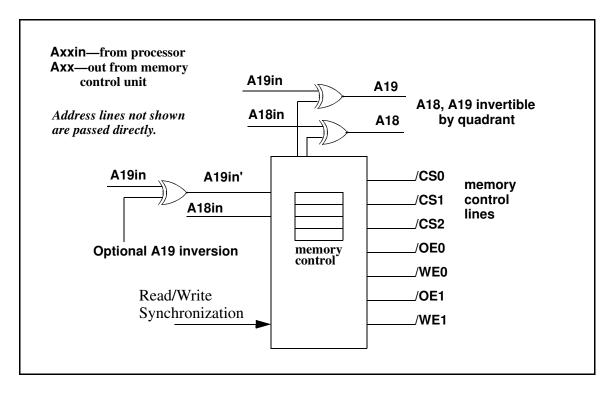

| 8.2 Memory Interface Unit                                | 93  |

|                                                          |     |

|                                                          |     |

|                                                          |     |

|                                                          |     |

|                                                          |     |

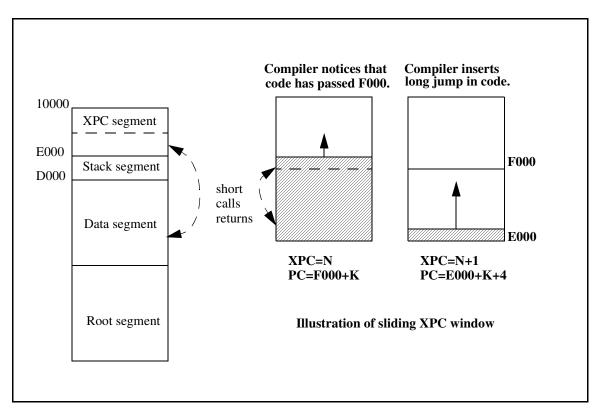

| 8.5 How Compiler Compiles to Memory                      | 97  |

| Chapter 9. Parallel Ports                                | 99  |

|                                                          |     |

|                                                          |     |

|                                                          |     |

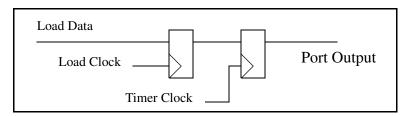

| Precisely Timed Output Pulses                            |     |

|                                                          |     |

|                                                          | 100 |

|                                                          |     |

#### Chapter 10. I/O Bank Control Registers

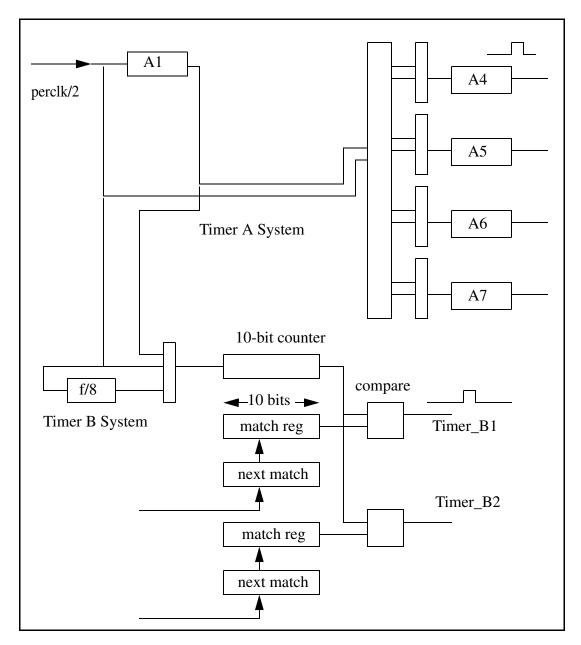

| Chapter 11. Timers                                                                                                                   | 111        |

|--------------------------------------------------------------------------------------------------------------------------------------|------------|

| 11.1 Timer A                                                                                                                         |            |

| 11.1.1 Timer A I/O Registers                                                                                                         |            |

| 11.1.2 Practical Use of Timer A                                                                                                      |            |

| 11.2 Timer B                                                                                                                         |            |

| 11.2.1 Using Timer B                                                                                                                 | 117        |

| Chapter 12. Rabbit Serial Ports                                                                                                      | 119        |

| 12.1 Serial Port Register Layout                                                                                                     | -          |

| 12.2 Serial Port Interrupt                                                                                                           |            |

| 12.3 Transmit Serial Data Timing                                                                                                     |            |

| 12.9 Transmit Serial Data Timing                                                                                                     |            |

| 12.5 Clocked Serial Ports                                                                                                            |            |

| 12.6 Clocked Serial Timing                                                                                                           |            |

| 12.6.1 Clocked Serial Timing With Internal Clock                                                                                     |            |

| 12.6.2 Clocked Serial Timing with External Clock                                                                                     |            |

| 12.7 Serial Port Software Suggestions                                                                                                | 129        |

| 12.7.1 Controlling an RS-485 Driver and Receiver                                                                                     | 131        |

| 12.7.2 Transmitting Dummy Characters                                                                                                 |            |

| 12.7.3 Transmitting and Detecting a Break                                                                                            |            |

| 12.7.4 Using A Serial Port to Generate a Periodic Interrupt<br>12.7.5 Extra Stop Bits, Sending Parity, 9th Bit Communication Schemes |            |

| 12.7.6 Supporting 9th Bit Communication Protocols                                                                                    |            |

| 12.7.7 Rabbit-Only Master/Slave Protocol                                                                                             | 135        |

| 12.7.8 Data Framing/Modbus                                                                                                           |            |

|                                                                                                                                      |            |

| Chapter 13. Rabbit Slave Port                                                                                                        | 137        |

| 13.1 Hardware Design of Slave Port Interconnection                                                                                   | 143        |

| 13.2 Slave Port Registers                                                                                                            |            |

| 13.3 Applications and Communications Protocols for Slaves                                                                            |            |

| 13.3.1 Slave Applications                                                                                                            |            |

| 13.3.2 Master-Slave Messaging Protocol                                                                                               | 146        |

| Chapter 14. Rabbit 2000 Clocks                                                                                                       | 149        |

| 14.1 Low-Power Design                                                                                                                | -          |

| 14.1 Low-Power Design                                                                                                                |            |

| 14.2 Clock Spectrum Spreader Module                                                                                                  | 130        |

| Chapter 15. AC Timing Specifications                                                                                                 | 151        |

|                                                                                                                                      | -          |

| 15.1 Memory Access and I/O Read/Write Times                                                                                          | 134<br>163 |

| 15.2 Current Consumption                                                                                                             | 102        |

| Chapter 16. Rabbit BIOS and Virtual Driver                                                                                           | 165        |

| 16.1 The BIOS                                                                                                                        |            |

| 16.1.1 BIOS Services                                                                                                                 |            |

| 16.1.2 BIOS Assumptions                                                                                                              |            |

| 16.2 Virtual Driver                                                                                                                  | 166        |

| 16.2.1 Periodic Interrupt                                                                                                            |            |

| 16.2.2 Watchdog Timer Support                                                                                                        | 166        |

| Chapter 17. Other Rabbit Software                                                                                                    | 169        |

| 17.1 Power Management Support                                                                                                        |            |

| 17.2 Reading and Writing I/O Registers                                                                                               |            |

| 17.2.1 Using Assembly Language                                                                                                       |            |

| 17.2.2 Using Library Functions                                                                                                       | 170        |

| 17.3 Shadow Registers                                                                                                                |            |

| 17.3.1 Updating Shadow Registers                                                                                                     | 171        |

| 17.3.2 Interrupt While Updating Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 17.3.3 Write-only Registers Without Shadow Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                 |

| 17.4 Timer and Clock Usage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 172                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                 |

| Chapter 18. Rabbit Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 175                                                                                                                                                                                                             |

| 18.1 Load Immediate Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                 |

| 18.2 Load & Store to Immediate Address                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                 |

| 18.3 8-bit Indexed Load and Store                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                 |

| 18.4 16-bit Indexed Loads and Stores                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                 |

| 18.5 16-bit Load and Store 20-bit Address                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                 |

| 18.6 Register to Register Moves                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                 |

| 18.7 Exchange Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                 |

| 18.8 Stack Manipulation Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                 |

| 18.9 16-bit Arithmetic and Logical Ops                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                 |

| 18.10 8-bit Arithmetic and Logical Ops                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                 |

| 18.11 8-bit Bit Set, Reset and Test                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                 |

| 18.12 8-bit Increment and Decrement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                 |

| 18.13 8-bit Fast A register Operations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                 |

| 18.14 8-bit Shifts and Rotates                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                 |

| 18.15 Instruction Prefixes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                 |

| 18.16 Block Move Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                 |

| 18.17 Control Instructions - Jumps and Calls                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                 |

| 18.18 Miscellaneous Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                 |

| 18.19 Privileged Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 186                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                 |

| Chapter 10 Differences Rephit vs. 790/7190 Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 197                                                                                                                                                                                                             |

| Chapter 19. Differences Rabbit vs. Z80/Z180 Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 187                                                                                                                                                                                                             |

| •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 187                                                                                                                                                                                                             |

| Chapter 20. Instructions in Alphabetical Order                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | -                                                                                                                                                                                                               |

| Chapter 19. Differences Rabbit vs. Z80/Z180 Instructions<br>Chapter 20. Instructions in Alphabetical Order<br>With Binary Encoding                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 187<br>189                                                                                                                                                                                                      |

| Chapter 20. Instructions in Alphabetical Order<br>With Binary Encoding                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | -                                                                                                                                                                                                               |

| Chapter 20. Instructions in Alphabetical Order<br>With Binary Encoding<br>Appendix A.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 189                                                                                                                                                                                                             |

| Chapter 20. Instructions in Alphabetical Order<br>With Binary Encoding<br>Appendix A.<br>The Rabbit Programming Port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 189<br>197                                                                                                                                                                                                      |

| Chapter 20. Instructions in Alphabetical Order<br>With Binary Encoding<br>Appendix A.<br>The Rabbit Programming Port<br>A.1 The Rabbit Programming Port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | <b>189</b><br><b>197</b><br>197                                                                                                                                                                                 |

| <ul> <li>Chapter 20. Instructions in Alphabetical Order<br/>With Binary Encoding</li> <li>Appendix A.<br/>The Rabbit Programming Port</li> <li>A.1 The Rabbit Programming Port</li> <li>A.2 Use of the Programming Port as a Diagnostic/Setup Port</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | <b>189</b><br><b>197</b><br>197<br>198                                                                                                                                                                          |

| <ul> <li>Chapter 20. Instructions in Alphabetical Order<br/>With Binary Encoding</li> <li>Appendix A.<br/>The Rabbit Programming Port         <ul> <li>A.1 The Rabbit Programming Port</li> <li>A.2 Use of the Programming Port as a Diagnostic/Setup Port</li> <li>A.3 Alternate Programming Port</li> </ul> </li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | <b>189</b><br><b>197</b><br>197<br>198<br>198                                                                                                                                                                   |

| Chapter 20. Instructions in Alphabetical Order<br>With Binary Encoding<br>Appendix A.<br>The Rabbit Programming Port<br>A.1 The Rabbit Programming Port<br>A.2 Use of the Programming Port as a Diagnostic/Setup Port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | <b>189</b><br><b>197</b><br>197<br>198<br>198                                                                                                                                                                   |

| <ul> <li>Chapter 20. Instructions in Alphabetical Order<br/>With Binary Encoding</li> <li>Appendix A.<br/>The Rabbit Programming Port         <ul> <li>A.1 The Rabbit Programming Port</li> <li>A.2 Use of the Programming Port as a Diagnostic/Setup Port</li> <li>A.3 Alternate Programming Port</li> <li>A.4 Suggested Rabbit Crystal Frequencies</li> </ul> </li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | <b>189</b><br><b>197</b><br>197<br>198<br>198<br>199                                                                                                                                                            |

| Chapter 20. Instructions in Alphabetical Order<br>With Binary Encoding<br>Appendix A.<br>The Rabbit Programming Port<br>A.1 The Rabbit Programming Port<br>A.2 Use of the Programming Port as a Diagnostic/Setup Port<br>A.3 Alternate Programming Port<br>A.4 Suggested Rabbit Crystal Frequencies<br>Appendix B. Rabbit 2000 Revisions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | <b>189</b><br><b>197</b><br>197<br>198<br>198<br>199<br><b>201</b>                                                                                                                                              |

| <ul> <li>Chapter 20. Instructions in Alphabetical Order<br/>With Binary Encoding</li> <li>Appendix A.<br/>The Rabbit Programming Port         <ul> <li>A.1 The Rabbit Programming Port</li> <li>A.2 Use of the Programming Port as a Diagnostic/Setup Port</li> <li>A.3 Alternate Programming Port</li> <li>A.4 Suggested Rabbit Crystal Frequencies</li> </ul> </li> <li>Appendix B. Rabbit 2000 Revisions         <ul> <li>B.1 Rabbit 2000 Revisions</li> </ul> </li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | <b>189</b><br><b>197</b><br>197<br>198<br>198<br>198<br>199<br><b>201</b><br>201                                                                                                                                |

| <ul> <li>Chapter 20. Instructions in Alphabetical Order<br/>With Binary Encoding</li> <li>Appendix A.<br/>The Rabbit Programming Port         <ul> <li>A.1 The Rabbit Programming Port</li> <li>A.2 Use of the Programming Port as a Diagnostic/Setup Port.</li> <li>A.3 Alternate Programming Port</li> <li>A.4 Suggested Rabbit Crystal Frequencies</li> </ul> </li> <li>Appendix B. Rabbit 2000 Revisions         <ul> <li>B.1 Rabbit 2000 Revisions.</li> <li>B.2 Discussion of Fixes and Improvements</li> </ul> </li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                         | <b>189</b><br><b>197</b><br>197<br>198<br>198<br>199<br><b>201</b><br>201<br>203                                                                                                                                |

| <ul> <li>Chapter 20. Instructions in Alphabetical Order<br/>With Binary Encoding</li> <li>Appendix A.<br/>The Rabbit Programming Port         <ul> <li>A.1 The Rabbit Programming Port</li> <li>A.2 Use of the Programming Port as a Diagnostic/Setup Port.</li> <li>A.3 Alternate Programming Port</li></ul></li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | <b>189</b><br><b>197</b><br>197<br>198<br>198<br>199<br><b>201</b><br>201<br>203<br>204                                                                                                                         |

| <ul> <li>Chapter 20. Instructions in Alphabetical Order<br/>With Binary Encoding</li> <li>Appendix A.<br/>The Rabbit Programming Port         <ul> <li>A.1 The Rabbit Programming Port</li> <li>A.2 Use of the Programming Port as a Diagnostic/Setup Port.</li> <li>A.3 Alternate Programming Port</li></ul></li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | <b>189</b><br><b>197</b><br>197<br>198<br>198<br>199<br><b>201</b><br>201<br>203<br>204<br>205                                                                                                                  |

| Chapter 20. Instructions in Alphabetical Order<br>With Binary Encoding<br>Appendix A.<br>The Rabbit Programming Port<br>A.1 The Rabbit Programming Port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | <b>189</b><br><b>197</b><br>197<br>198<br>198<br>199<br><b>201</b><br>201<br>203<br>204<br>205<br>207<br>209                                                                                                    |

| Chapter 20. Instructions in Alphabetical Order<br>With Binary Encoding<br>Appendix A.<br>The Rabbit Programming Port<br>A.1 The Rabbit Programming Port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | <b>189</b><br><b>197</b><br>197<br>198<br>198<br>199<br><b>201</b><br>201<br>203<br>204<br>205<br>207<br>209<br>211                                                                                             |

| Chapter 20. Instructions in Alphabetical Order<br>With Binary Encoding<br>Appendix A.<br>The Rabbit Programming Port<br>A.1 The Rabbit Programming Port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | <b>189</b><br><b>197</b><br>197<br>198<br>198<br>198<br>199<br><b>201</b><br>201<br>203<br>204<br>205<br>207<br>209<br>211<br>213                                                                               |

| Chapter 20. Instructions in Alphabetical Order<br>With Binary Encoding<br>Appendix A.<br>The Rabbit Programming Port<br>A.1 The Rabbit Programming Port<br>A.2 Use of the Programming Port as a Diagnostic/Setup Port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | <b>189</b><br><b>197</b><br>197<br>198<br>198<br>199<br><b>201</b><br>201<br>203<br>204<br>205<br>207<br>209<br>211<br>213<br>213                                                                               |

| Chapter 20. Instructions in Alphabetical Order<br>With Binary Encoding<br>Appendix A.<br>The Rabbit Programming Port<br>A.1 The Rabbit Programming Port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | <b>189</b><br><b>197</b><br>197<br>198<br>198<br>198<br>199<br><b>201</b><br>201<br>203<br>204<br>205<br>207<br>209<br>211<br>213<br>213<br>213                                                                 |

| Chapter 20. Instructions in Alphabetical Order<br>With Binary Encoding         Appendix A.         The Rabbit Programming Port         A.1 The Rabbit Programming Port         A.2 Use of the Programming Port as a Diagnostic/Setup Port.         A.3 Alternate Programming Port         A.4 Suggested Rabbit Crystal Frequencies         Appendix B. Rabbit 2000 Revisions         B.1 Rabbit 1000 Revisions.         B.2 Discussion of Fixes and Improvements         B.2.1 Rabbit Internal I/O Registers         B.2.2 Revision-Level ID Register         B.2.3 Serial Port Changes         B.2.4 Improved Battery-Backup Circuit         B.2.5 Added Support for Instruction/Data Split         B.2.6 Write Inhibit (WE0) After Reset         B.2.7 Chip Selects Inactive During Internal I/O         B.2.8 External Interrupt Input Bug Fix         B.2.9 IOI/IOE Prefix Bug Fix         B.2.10 DDCB/FDCB Instruction Page and Wait State Bug Fixes | <b>189</b><br><b>197</b><br>197<br>198<br>198<br>198<br><b>201</b><br>201<br>203<br>204<br>205<br>207<br>209<br>211<br>213<br>213<br>213<br>213<br>214                                                          |

| Chapter 20. Instructions in Alphabetical Order<br>With Binary Encoding         Appendix A.         The Rabbit Programming Port         A.1 The Rabbit Programming Port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 189         197         197         198         198         199         201         203         204         205         207         209         211         213         213         213         214             |

| Chapter 20. Instructions in Alphabetical Order<br>With Binary Encoding         Appendix A.         The Rabbit Programming Port         A.1 The Rabbit Programming Port         A.2 Use of the Programming Port as a Diagnostic/Setup Port.         A.3 Alternate Programming Port         A.4 Suggested Rabbit Crystal Frequencies         Appendix B. Rabbit 2000 Revisions         B.1 Rabbit 2000 Revisions         B.2 Discussion of Fixes and Improvements         B.2.1 Rabbit Internal I/O Registers         B.2.2 Revision-Level ID Register         B.2.3 Serial Port Changes         B.2.4 Improved Battery-Backup Circuit         B.2.5 Added Support for Instruction/Data Split         B.2.6 Write Inhibit (/WE0) After Reset         B.2.7 Chip Selects Inactive During Internal I/O         B.2.8 External Interrupt Input Bug Fix         B.2.9 IOI/IOE Prefix Bug Fix         B.2.10 DDCB/FDCB Instruction Page and Wait State Bug Fixes | 189         197         197         198         198         199         201         203         204         205         207         209         211         213         213         213         214         215 |

# **1. INTRODUCTION**

Rabbit Semiconductor was formed expressly to design a a better microprocessor for use in small and medium-scale controllers. The first product is the *Rabbit 2000* microprocessor. The Rabbit 2000 designers have had years of experience using Z80, Z180 and HD64180 microprocessors in small controllers. The Rabbit shares a similar architecture and a high degree of compatibility with these microprocessors, but it is a vast improvement.

The Rabbit has been designed in close cooperation with Z-World, Inc., a long-time manufacturer of low-cost single-board computers. Z-World and Rabbit Semiconductor products are supported by an innovative C-language development system (Dynamic C).

The Rabbit 2000 is easy to use. Hardware and software interfaces are as uncluttered and are as foolproof as possible. The Rabbit 2000 has outstanding computation speed for a microprocessor with an 8-bit bus. This is because the Z80-derived instruction set is very compact and the design of the memory interface allows maximum utilization of the memory bandwidth. The Rabbit races through instructions.

Traditional microprocessor hardware and software development is simplified for Rabbit users. In-circuit emulators are not needed and will not be missed by the Rabbit developer. Software development is accomplished by connecting a simple interface cable from a PC serial port to the Rabbit-based target system.

#### 1.1 Features and Specifications

- 100-pin PQFP package. Operating voltage 2.7 V to 5 V. Clock speed to 30 MHz. All specifications are given for both industrial and commercial temperature and voltage ranges. Rabbit microprocessors cost under \$10 in moderate quantities.

- Industrial specifications are for a voltage variation of 10% and a temperature range from -40°C to +85°C. Commercial specifications are for a voltage variation of 5% and a temperature range from 0°C to 70°C.

- 1-megabyte code space allows C programs with up to 50,000+ lines of code. The extended Z80-style instruction set is C-friendly, with short and fast instructions for most common C operations.

- Four levels of interrupt priority make a fast interrupt response practical for critical applications. The maximum time to the first instruction of an interrupt routine is about 1 µs at a clock speed of 25 MHz.