Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# 71M6541D/F/G and 71M6542F/G Energy Meter ICs

## **DATA SHEET**

#### **GENERAL DESCRIPTION**

The 71M6541D/71M6541F/71M6541G/71M6542G are Teridian™ 4th-generation single-phase metering SoCs with a 5MHz 8051-compatible MPU core, low-power RTC with digital temperature compensation, flash memory, and LCD driver. Our Single Converter Technology® with a 22-bit delta-sigma ADC, three or four analog inputs, digital temperature compensation, precision voltage reference, and a 32-bit computation engine (CE) supports a wide range of metering applications with very few external components.

The 71M6541/2 devices support optional interfaces to the Teridian 71M6x01 series of isolated sensors, which offer BOM cost reduction, immunity to magnetic tamper, and enhanced reliability. Other features include an SPI interface, advanced power management, ultra-low-power operation in active and battery modes, 3/5KB shared RAM and 32/64/128KB of flash memory that can be programmed in the field with code and/or data during meter operation and the ability to drive up to six LCD segments per SEG driver pin. High processing and sampling rates combined with differential inputs offer a powerful metering platform for residential meters.

A complete array of code development tools, demonstration code, and reference designs enable rapid development and certification of meters that meet all ANSI and IEC electricity metering standards worldwide.

Teridian is a trademark and Single Converter Technology is a registered trademark of Maxim Integrated Products, Inc.

MICROWIRE is a registered trademark of National Semiconductor Corp.

#### **FEATURES**

- 0.1% Accuracy Over 2000:1 Current Range

- Exceeds IEC 62053/ANSI C12.20 Standards

- Two Current Sensor Inputs with Selectable Differential Mode

- Selectable Gain of 1 or 8 for One Current Input to Support Shunts

- High-Speed Wh/VARh Pulse Outputs with Programmable Width

- 32KB Flash, 3KB RAM (71M6541D)

- 64KB Flash, 5KB RAM (71M6541F/42F)

- 128KB Flash, 5KB RAM (71M6541G/42G)

- Up to Four Pulse Outputs with Pulse Count

- Four-Quadrant Metering

- Digital Temperature Compensation:

- Metrology Compensation

- Accurate RTC for TOU Functions with Automatic Temperature Compensation for Crystal in All Power Modes

- Independent 32-Bit Compute Engine

- 46-64Hz Line Frequency Range with the Same Calibration

- Phase Compensation (±10°)

- Three Battery-Backup Modes:

- Brownout Mode (BRN)

- LCD Mode (LCD)

- Sleep Mode (SLP)

- Wake-Up on Pin Events and Wake-On Timer

- 1µA in Sleep Mode

- Flash Security

- In-System Program Update

- 8-Bit MPU (80515), Up to 5 MIPS

- Full-Speed MPU Clock in Brownout Mode

- LCD Driver:

- Up to 6 Commons/Up to 56 Pins

- 5V LCD Driver with DAC

- Up to 51 Multifunction DIO Pins

- Hardware Watchdog Timer (WDT)

- I<sup>2</sup>C/MICROWIRE® EEPROM Interface

- SPI Interface with Flash Program Capability

- Two UARTs for IR and AMR

- IR LED Driver with Modulation

- Industrial Temperature Range

- 64-Pin (71M6541D/F/G) and 100-pin (71M6542F/G) Lead(Pb)-Free LQFP Package

# **Table of Contents**

| 1 | Intro | oduction                                                          | 10 |

|---|-------|-------------------------------------------------------------------|----|

| 2 | Hard  | dware Descriptiond                                                | 11 |

|   | 2.1   | Hardware Overview                                                 | 11 |

|   | 2.2   | Analog Front End (AFE)                                            | 12 |

|   |       | 2.2.1 Signal Input Pins                                           | 14 |

|   |       | 2.2.2 Input Multiplexer                                           | 15 |

|   |       | 2.2.3 Delay Compensation                                          | 19 |

|   |       | 2.2.4 ADC Pre-Amplifier                                           | 20 |

|   |       | 2.2.5 A/D Converter (ADC)                                         | 20 |

|   |       | 2.2.6 FIR Filter                                                  | 20 |

|   |       | 2.2.7 Voltage References                                          | 20 |

|   |       | 2.2.8 71M6x01 Isolated Sensor Interface (Remote Sensor Interface) | 22 |

|   | 2.3   | Digital Computation Engine (CE)                                   |    |

|   |       | 2.3.1 CE Program Memory                                           |    |

|   |       | 2.3.2 CE Data Memory                                              |    |

|   |       | 2.3.3 CE Communication with the MPU                               |    |

|   |       | 2.3.4 Meter Equations                                             |    |

|   |       | 2.3.5 Real-Time Monitor (RTM)                                     |    |

|   |       | 2.3.6 Pulse Generators                                            |    |

|   |       | 2.3.7 CE Functional Overview                                      |    |

|   | 2.4   | 80515 MPU Core                                                    |    |

|   |       | 2.4.1 Memory Organization and Addressing                          |    |

|   |       | 2.4.2 Special Function Registers (SFRs)                           |    |

|   |       | 2.4.3 Generic 80515 Special Function Registers                    |    |

|   |       | 2.4.4 Instruction Set                                             |    |

|   |       | 2.4.5 UARTs                                                       |    |

|   |       | 2.4.6 Timers and Counters                                         |    |

|   |       | 2.4.7 WD Timer (Software Watchdog Timer)                          |    |

|   |       | 2.4.8 Interrupts                                                  |    |

|   | 2.5   | On-Chip Resources                                                 |    |

|   |       | 2.5.1 Physical Memory                                             |    |

|   |       | 2.5.2 Oscillator                                                  |    |

|   |       | 2.5.3 PLL and Internal Clocks                                     |    |

|   |       | 2.5.4 Real-Time Clock (RTC)                                       |    |

|   |       | 2.5.5 71M654x Temperature Sensor                                  |    |

|   |       | 2.5.6 71M654x Battery Monitor                                     |    |

|   |       | 2.5.7 UART and Optical Interface                                  |    |

|   |       | 2.5.8 Digital I/O and LCD Segment Drivers                         |    |

|   |       | 2.5.9 EEPROM Interface                                            |    |

|   |       | 2.5.10 SPI Slave Port                                             |    |

|   |       | 2.5.11 Hardware Watchdog Timer                                    |    |

|   |       | 2.5.12 Test Ports (TMUXOUT and TMUX2OUT Pins)                     |    |

| 3 | Fun   | ctional Description                                               |    |

| 9 | 3.1   | Theory of Operation                                               |    |

|   | 3.1   | Battery Modes                                                     |    |

|   | ٥.۷   | 3.2.1 BRN Mode                                                    |    |

|   |       | 3.2.2 LCD Mode                                                    |    |

|   |       |                                                                   |    |

|   |       | 3.2.3 SLP Mode                                                    | 84 |

|   | 3.3  | Fault and Reset Behavior                                   | 85  |

|---|------|------------------------------------------------------------|-----|

|   |      | 3.3.1 Events at Power-Down                                 | 85  |

|   |      | 3.3.2 IC Behavior at Low Battery Voltage                   | 86  |

|   |      | 3.3.3 Reset Sequence                                       | 86  |

|   |      | 3.3.4 Watchdog Timer Reset                                 | 86  |

|   | 3.4  | Wake Up Behavior                                           | 87  |

|   |      | 3.4.1 Wake on Hardware Events                              | 87  |

|   |      | 3.4.2 Wake on Timer                                        | 90  |

|   | 3.5  | Data Flow and MPU/CE Communication                         | 91  |

| 4 | Appl | lication Information                                       | 92  |

|   | 4.1  | Connecting 5 V Devices                                     | 92  |

|   | 4.2  | Direct Connection of Sensors                               | 92  |

|   | 4.3  | 71M6541D/F/G Using Local Sensors                           | 93  |

|   | 4.4  | 71M6541D/F/G Using 71M6x01and Current Shunts               |     |

|   | 4.5  | 71M6542F/G Using Local Sensors                             |     |

|   | 4.6  | 71M6542F/G Using 71M6x01 and Current Shunts                |     |

|   | 4.7  | Metrology Temperature Compensation                         |     |

|   |      | 4.7.1 Voltage Reference Precision                          |     |

|   |      | 4.7.2 Temperature Coefficients for the 71M654x             |     |

|   |      | 4.7.3 Temperature Compensation for VREF with Local Sensors |     |

|   |      | 4.7.4 Temperature Compensation for VREF with Remote Sensor |     |

|   | 4.8  | Connecting I <sup>2</sup> C EEPROMs                        |     |

|   | 4.9  | Connecting Three-Wire EEPROMs                              |     |

|   | 4.10 | UART0 (TX/RX)                                              |     |

|   |      | Optical Interface (UART1)                                  |     |

|   |      | Connecting the Reset Pin                                   |     |

|   |      | Connecting the Emulator Port Pins                          |     |

|   |      | Flash Programming                                          |     |

|   |      | 4.14.1 Flash Programming via the ICE Port                  |     |

|   |      | 4.14.2 Flash Programming via the SPI Port                  |     |

|   | 4.15 | MPU Firmware Library                                       |     |

|   |      | Crystal Oscillator                                         |     |

|   |      | Meter Calibration                                          |     |

| 5 |      | ware Interface                                             |     |

|   | 5.1  | I/O RAM Map –Functional Order                              |     |

|   | 5.2  | I/O RAM Map – Alphabetical Order                           |     |

|   | 5.3  | CE Interface Description                                   |     |

|   |      | 5.3.1 CE Program                                           |     |

|   |      | 5.3.2 CE Data Format                                       |     |

|   |      | 5.3.3 Constants                                            |     |

|   |      | 5.3.4 Environment                                          | 126 |

|   |      | 5.3.5 CE Calculations                                      |     |

|   |      | 5.3.6 CE Front End Data (Raw Data)                         |     |

|   |      | 5.3.7 FCE Status and Control                               |     |

|   |      | 5.3.8 CE Transfer Variables                                |     |

|   |      | 5.3.9 Pulse Generation                                     |     |

|   |      | 5.3.10 Other CE Parameters                                 |     |

|   |      | 5.3.11 CE Calibration Parameters                           |     |

|   |      | 5.3.12 CE Flow Diagrams                                    |     |

| 6 | Elec | trical Specifications                                      |     |

|     | 6.1 Absolute Maximum Ratings |                                 |                                         |     |  |  |  |

|-----|------------------------------|---------------------------------|-----------------------------------------|-----|--|--|--|

|     | 6.2                          | Recommended External Components |                                         |     |  |  |  |

|     | 6.3                          | Recom                           | mended Operating Conditions             | 139 |  |  |  |

|     | 6.4                          | Perforr                         | nance Specifications                    | 140 |  |  |  |

|     |                              | 6.4.1                           | Input Logic Levels                      | 140 |  |  |  |

|     |                              | 6.4.2                           | Output Logic Levels                     | 140 |  |  |  |

|     |                              | 6.4.3                           | Battery Monitor                         | 141 |  |  |  |

|     |                              | 6.4.4                           | Temperature Monitor                     | 141 |  |  |  |

|     |                              | 6.4.5                           | Supply Current                          | 142 |  |  |  |

|     |                              | 6.4.6                           | V3P3D Switch                            | 143 |  |  |  |

|     |                              | 6.4.7                           | Internal Power Fault Comparators        | 143 |  |  |  |

|     |                              | 6.4.8                           | 2.5 V Voltage Regulator – System Power  | 143 |  |  |  |

|     |                              | 6.4.9                           | 2.5 V Voltage Regulator – Battery Power | 144 |  |  |  |

|     |                              | 6.4.10                          | Crystal Oscillator                      | 144 |  |  |  |

|     |                              | 6.4.11                          | Phase-Locked Loop (PLL)                 | 144 |  |  |  |

|     |                              | 6.4.12                          | LCD Drivers                             | 145 |  |  |  |

|     |                              | 6.4.13                          | VLCD Generator                          | 146 |  |  |  |

|     |                              | 6.4.14                          | VREF                                    | 148 |  |  |  |

|     |                              | 6.4.15                          | ADC Converter                           | 149 |  |  |  |

|     |                              | 6.4.16                          | Pre-Amplifier for IAP-IAN               | 150 |  |  |  |

|     | 6.5                          | Timing                          | Specifications                          | 151 |  |  |  |

|     |                              | 6.5.1                           | Flash Memory                            | 151 |  |  |  |

|     |                              | 6.5.2                           | SPI Slave                               | 151 |  |  |  |

|     |                              | 6.5.3                           | EEPROM Interface                        | 151 |  |  |  |

|     |                              | 6.5.4                           | RESET Pin                               | 152 |  |  |  |

|     |                              | 6.5.5                           | RTC                                     | 152 |  |  |  |

|     | 6.6                          | Packag                          | ge Outline Drawings                     | 153 |  |  |  |

|     |                              |                                 | 64-Pin LQFP Outline Package Drawing     |     |  |  |  |

|     |                              |                                 | 100-Pin LQFP Package Outline Drawing    |     |  |  |  |

|     | 6.7                          |                                 | ge Markings                             |     |  |  |  |

|     | 6.8                          | •                               | Diagrams                                |     |  |  |  |

|     |                              |                                 | 71M6541D/F/G LQFP-64 Package Pinout     |     |  |  |  |

|     |                              |                                 | 71M6542F/G LQFP-100 Package Pinout      |     |  |  |  |

|     | 6.9                          |                                 | scriptions                              |     |  |  |  |

|     |                              |                                 | Power and Ground Pins.                  |     |  |  |  |

|     |                              |                                 | Analog Pins                             |     |  |  |  |

|     |                              |                                 | Digital Pins                            |     |  |  |  |

|     |                              |                                 | I/O Equivalent Circuits                 |     |  |  |  |

| 7   | Orde                         |                                 | formation                               |     |  |  |  |

|     | 7.1                          |                                 | 41D/F/G and 71M6542F/G                  |     |  |  |  |

| 8   | Rela                         |                                 | ormation                                |     |  |  |  |

| 9   |                              |                                 | ormation                                |     |  |  |  |

| App | endix A: Acronyms164         |                                 |                                         |     |  |  |  |

|     |                              |                                 | rision History                          |     |  |  |  |

# **Figures**

| Figure 2. 71M6541D/F/G AFE Block Diagram (Local Sensors)                                         | 12  |

|--------------------------------------------------------------------------------------------------|-----|

| Figure 3. 71M6541D/F/G AFE Block Diagram with 71M6x01                                            |     |

| Figure 4. 71M6542F/G AFE Block Diagram (Local Sensors)                                           | 13  |

| Figure 5. 71M6542F/G AFE Block Diagram with 71M6x01                                              | 14  |

| Figure 6: States in a Multiplexer Frame $(MUX\_DIV[3:0] = 3)$                                    | 17  |

| Figure 7: States in a Multiplexer Frame $(MUX\_DIV[3:0] = 4)$                                    |     |

| Figure 8: General Topology of a Chopped Amplifier                                                | 21  |

| Figure 9: CROSS Signal with CHOP_E = 00                                                          |     |

| Figure 10: RTM Timing                                                                            |     |

| Figure 11: Timing relationship between ADC MUX, CE, and RTM Serial Transfer                      |     |

| Figure 12. Pulse Generator FIFO Timing                                                           | 28  |

| Figure 13: Accumulation Interval                                                                 |     |

| Figure 14: Samples from Multiplexer Cycle (MUX_DIV[3:0] = 3)                                     | 30  |

| Figure 15: Samples from Multiplexer Cycle (MUX_DIV[3:0] = 4)                                     | 30  |

| Figure 16: Interrupt Structure                                                                   | 47  |

| Figure 17: Automatic Temperature Compensation                                                    | 54  |

| Figure 18: Optical Interface                                                                     |     |

| Figure 19: Optical Interface (UART1)                                                             | 59  |

| Figure 20: Connecting an External Load to DIO Pins                                               | 60  |

| Figure 21: LCD Waveforms                                                                         |     |

| Figure 22: 3-wire Interface. Write Command, HiZ=0                                                | 72  |

| Figure 23: 3-wire Interface. Write Command, HiZ=1                                                |     |

| Figure 24: 3-wire Interface. Read Command                                                        |     |

| Figure 25: 3-Wire Interface. Write Command when CNT=0                                            | 73  |

| Figure 26: 3-wire Interface. Write Command when HiZ=1 and WFR=1                                  | 73  |

| Figure 27: SPI Slave Port - Typical Multi-Byte Read and Write operations                         | 75  |

| Figure 28: Voltage, Current, Momentary and Accumulated Energy                                    | 80  |

| Figure 29: Operation Modes State Diagram                                                         | 81  |

| Figure 30: MPU/CE Data Flow                                                                      | 91  |

| Figure 31: Resistive Voltage Divider (Voltage Sensing)                                           | 92  |

| Figure 32. CT with Single-Ended Input Connection (Current Sensing)                               | 92  |

| Figure 33: CT with Differential Input Connection (Current Sensing)                               | 92  |

| Figure 34: Differential Resistive Shunt Connections (Current Sensing)                            |     |

| Figure 35. 71M6541D/F/G with Local Sensors                                                       | 93  |

| Figure 36: 71M6541D/F/G with 71M6x01 isolated Sensor                                             |     |

| Figure 39: I <sup>2</sup> C EEPROM Connection                                                    |     |

| Figure 40: Connections for UART0                                                                 | 101 |

| Figure 41: Connection for Optical Components                                                     |     |

| Figure 42: External Components for the RESET Pin: Push-Button (Left), Production Circuit (Right) |     |

| Figure 43: External Components for the Emulator Interface                                        | 103 |

| Figure 44: CE Data Flow: Multiplexer and ADC                                                     |     |

| Figure 45: CE Data Flow: Scaling, Gain Control, Intermediate Variables                           | 136 |

| Figure 46: CE Data Flow: Squaring and Summation Stages                                           |     |

| Figure 47: 64-pin LQFP Package Outline                                                           |     |

| Figure 48: 100-pin LQFP Package Outline                                                          |     |

| Figure 49. Package Markings (Examples)                                                           | 155 |

| Figure 50: Pinout for the 71M6541D/F/G (LQFP-64 Package)                                         |     |

| Figure 52: I/O Equivalent Circuits                                                               | 162 |

# **Tables** Table 9: CKMPU Clock Frequencies......31 Table 11: Internal Data Memory Map.......33 Table 26: The IENO Bit Functions (SFR 0xA8)......41 Table 27: The IENI Bit Functions (SFR 0xB8)......41 Table 28: The IEN2 Bit Functions (SFR 0x9A).......42 Table 45: I/O RAM Registers for RTC Interrupts .......55 Table 48: Data/Direction Registers for SEGDIO0 to SEGDIO14 (71M6541D/F/G).......61 Table 49: Data/Direction Registers for SEGDIO19 to SEGDIO27 (71M6541D/F/G).......62 Table 51: Data/Direction Registers for SEGDIO51 and SEGDIO55 (71M6541D/F/G).......62 Table 52: Data/Direction Registers for SEGDIO0 to SEGDIO15 (71M6542F/G) .......63

| Table 53: Data/Direction Registers for SEGDIO16 to SEGDIO31 (71M6542F/G)    | 64  |

|-----------------------------------------------------------------------------|-----|

| Table 54: Data/Direction Registers for SEGDIO32 to SEGDIO45 (71M6542F/G)    | 64  |

| Table 55: Data/Direction Registers for SEGDIO51 to SEGDIO55 (71M6542F/G)    | 64  |

| Table 56: LCD_VMODE[1:0] Configurations                                     | 65  |

| Table 57: LCD Configurations                                                |     |

| Table 58: 71M6541D/F/G LCD Data Registers for SEG46 to SEG50                | 69  |

| Table 59: 71M6542F/G LCD Data Registers for SEG46 to SEG50                  | 70  |

| Table 60: EECTRL Bits for 2-pin Interface                                   | 71  |

| Table 61: EECTRL Bits for the 3-wire Interface                              | 71  |

| Table 62: SPI Transaction Fields                                            | 74  |

| Table 63: SPI Command Sequences                                             | 75  |

| Table 64: SPI Registers                                                     |     |

| Table 65: TMUX[5:0] Selections                                              |     |

| Table 66: TMUX2[4:0] Selections                                             | 79  |

| Table 67: Available Circuit Functions                                       | 82  |

| Table 68: VSTAT[2:0] (SFR 0xF9[2:0])                                        | 85  |

| Table 69: Wake Enables and Flag Bits                                        |     |

| Table 70: Wake Bits                                                         |     |

| Table 71: Clear Events for WAKE flags                                       |     |

| Table 72: GAIN_ADJn Compensation Channels                                   |     |

| Table 73: GAIN_ADJn Compensation Channels                                   |     |

| Table 74: I/O RAM Map – Functional Order, Basic Configuration               |     |

| Table 75: I/O RAM Map – Functional Order                                    |     |

| Table 76: I/O RAM Map – Functional Order                                    |     |

| Table 77. Standard CE Codes                                                 |     |

| Table 78: CE EQU Equations and Element Input Mapping                        |     |

| Table 79: CE Raw Data Access Locations                                      |     |

| Table 80: CESTATUS Register                                                 |     |

| Table 81: CESTATUS (CE RAM 0x80) Bit Definitions                            |     |

| Table 82: CECONFIG Register                                                 |     |

| Table 83: CECONFIG (CE RAM 0x20) Bit Definitions                            |     |

| Table 84: Sag Threshold and Gain Adjust Control                             |     |

| Table 85: CE Transfer Variables (with Local Sensors)                        |     |

| Table 86: CE Transfer Variables (with Remote Sensor)                        |     |

| Table 87: CE Energy Measurement Variables (with Local Sensors)              |     |

| Table 88: CE Energy Measurement Variables (with Remote Sensor)              |     |

| Table 89: Other Transfer Variables                                          |     |

| Table 90: CE Pulse Generation Parameters                                    |     |

| Table 91: CE Parameters for Noise Suppression and Code Version              |     |

| Table 92: CE Calibration Parameters                                         |     |

| Table 93: Absolute Maximum Ratings                                          |     |

| Table 95: Recommended Operating Conditions                                  |     |

| Table 96: Input Logic Levels                                                |     |

| Table 97: Output Logic Levels                                               |     |

| Table 98: Battery Monitor Performance Specifications ( <i>TEMP_BAT</i> = 1) |     |

| ·                                                                           |     |

| Table 99. Temperature Monitor                                               |     |

|                                                                             |     |

| Table 101: V3P3D Switch Performance Specifications                          |     |

| Table 102: Internal Power Fault Comparator Specifications                   |     |

| Table 103: 2.5 V Voltage Regulator Performance Specifications               |     |

| Table 104: Low-Power Voltage Regulator Performance Specifications           |     |

| Table 105: Crystal Oscillator Performance Specifications                    |     |

| Table 106: PLL Performance Specifications                                   | 144 |

# 71M6541D/F/G and 71M6542F/G Data Sheet

| Table 107: LCD Driver Performance Specifications    | 145 |

|-----------------------------------------------------|-----|

| Table 108: LCD Driver Performance Specifications    | 146 |

| Table 109: VREF Performance Specifications          | 148 |

| Table 110. ADC Converter Performance Specifications | 149 |

| Table 111: Pre-Amplifier Performance Specifications | 150 |

| Table 112: Flash Memory Timing Specifications       | 151 |

| Table 113. SPI Slave Timing Specifications          | 151 |

| Table 114: EEPROM Interface Timing                  | 151 |

| Table 115: RESET Pin Timing                         | 152 |

| Table 116: RTC Range for Date                       | 152 |

| Table 117. 71M6541 Package Markings                 | 155 |

| Table 118. 71M6542 Package Markings                 |     |

| Table 119: Power and Ground Pins                    |     |

| Table 120: Analog Pins                              | 159 |

| Table 121: Digital Pins                             | 160 |

| Table 122. Ordering Information                     | 163 |

|                                                     |     |

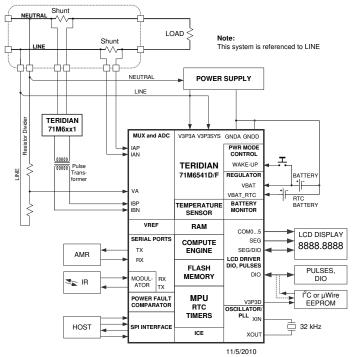

Figure 1: IC Functional Block Diagram

## 1 Introduction

This data sheet covers the 71M6541D (32KB), 71M6541F (64KB), 71M6541G (128KB), 71M6542F (64KB), and 71M6542G (128KB) fourth generation Teridian energy measurement SoCs. The term "71M654x" is used when discussing a device feature or behavior that is applicable to all four part numbers. The appropriate part number is indicated when a device feature or behavior is being discussed that applies only to a specific part number. This data sheet also covers basic details about the companion 71M6x01 isolated current sensor device. For more complete information on the 71M6x01 sensors, refer to the 71M6xxx Data Sheet.

This document covers the use of the 71M654x with locally connected sensors as well when it is used in conjunction with the 71M6x01 isolated current sensor. The 71M654x and 71M6x01 chipset make it possible to use one non-isolated and one isolated shunt current sensor to create single-phase and two-phase energy meters using inexpensive shunt resistors, while achieving unprecedented performance with this type of sensor technology. The 71M654x SoCs also support configurations involving one locally connected shunt and one locally connected Current Transformer (CT), or two CTs.

To facilitate document navigation, hyperlinks are often used to reference figures, tables and section headings that are located in other parts of the document. All hyperlinks in this document are highlighted in blue. Hyperlinks are used extensively to increase the level of detail and clarity provided within each section by referencing other relevant parts of the document. To further facilitate document navigation, this document is published as a PDF document with bookmarks enabled.

The reader is also encouraged to obtain and review the documents listed in 8 Related Information on page 163 of this document.

# 2 Hardware Description

#### 2.1 Hardware Overview

The Teridian 71M6541D/F/G and 71M6542F/G single-chip energy meter ICs integrate all primary functional blocks required to implement a solid-state residential electricity meter. Included on the chip are:

- An analog front end (AFE) featuring a 22-bit second-order sigma-delta ADC

- An independent 32-bit digital computation engine (CE) to implement DSP functions

- An 8051-compatible microprocessor (MPU) which executes one instruction per clock cycle (80515)

- A precision voltage reference (VREF)

- A temperature sensor for digital temperature compensation:

- Metrology digital temperature compensation (MPU)

- Automatic RTC digital temperature compensation operational in all power states

- LCD drivers

- RAM and Flash memory

- A real time clock (RTC)

- A variety of I/O pins

- A power failure interrupt

- · A zero-crossing interrupt

- Selectable current sensor interfaces for locally-connected sensors as well as isolated sensors (i.e., using the 71M6x01 companion IC with a shunt resistor sensor)

- Resistive Shunt and Current Transformers are supported

Resistive Shunts and Current Transformers (CT) current sensors are supported. Resistive shunt current sensors may be connected directly to the 71M654x device or isolated using a companion 71M6x01 isolator IC in order to implement a variety of single-phase / split-phase (71M6541D/F/G) or two-phase (71M6542F/G) metering configurations. An inexpensive, small size pulse transformer is used to isolate the 71M6x01 isolated sensor from the 71M654x. The 71M654x performs digital communications bi-directionally with the 71M6x01 and also provides power to the 71M6x01 through the isolating pulse transformer. Isolated (remote) shunt current sensors are connected to the differential input of the 71M6x01. Included on the 71M6x01 companion isolator chip are:

- Digital isolation communications interface

- An analog front end (AFE)

- A precision voltage reference (VREF)

- A temperature sensor (for digital temperature compensation)

- A fully differential shunt resistor sensor input

- A pre-amplifier to optimize shunt current sensor performance

- Isolated power circuitry obtains dc power from pulses sent by the 71M654x

In a typical application, the 32-bit compute engine (CE) of the 71M654x sequentially processes the samples from the voltage inputs on analog input pins and from the external 71M6x01 isolated sensors and performs calculations to measure active energy (Wh) and reactive energy (VARh), as well as A²h, and V²h for four-quadrant metering. These measurements are then accessed by the MPU, processed further and output using the peripheral devices available to the MPU.

In addition to advanced measurement functions, the clock function allows the 71M6541D/F/G and 71M6542F/G to record time-of-use (TOU) metering information for multi-rate applications and to time-stamp tamper or other events. Measurements can be displayed on 3.3 V LCDs commonly used in low-temperature environments. An on-chip charge pump is available to drive 5 V LCDs. Flexible mapping of LCD display segments facilitate integration of existing custom LCDs. Design trade-off between the number of LCD segments and DIO pins can be implemented in software to accommodate various requirements.

In addition to the temperature-trimmed ultra-precision voltage reference, the on-chip digital temperature compensation mechanism includes a temperature sensor and associated controls for correction of unwanted temperature effects on measurement and RTC accuracy, e.g., to meet the requirements of ANSI and IEC

standards. Temperature-dependent external components such as crystal oscillator, resistive shunts, current transformers (CTs) and their corresponding signal conditioning circuits can be characterized and their correction factors can be programmed to produce electricity meters with exceptional accuracy over the industrial temperature range.

One of the two internal UARTs is adapted to support an Infrared LED with internal drive and sense configuration and can also function as a standard UART. The optical output can be modulated at 38 kHz. This flexibility makes it possible to implement AMR meters with an IR interface. A block diagram of the IC is shown in Figure 1.

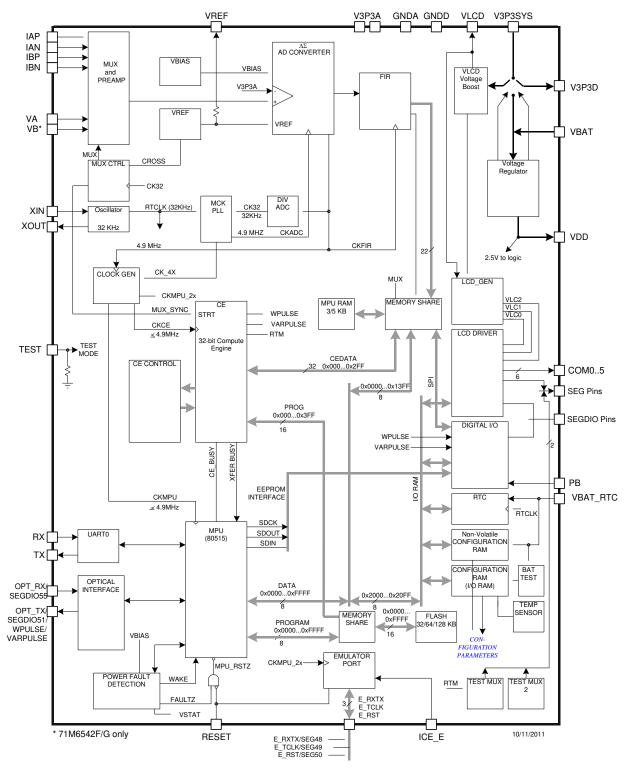

# 2.2 Analog Front End (AFE)

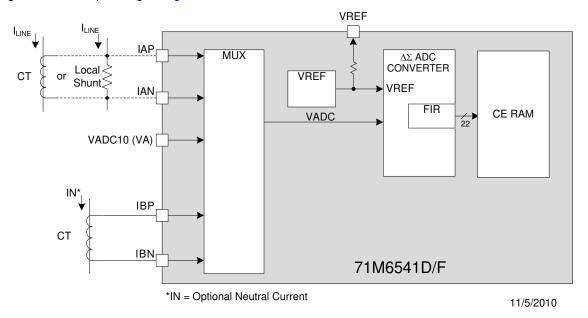

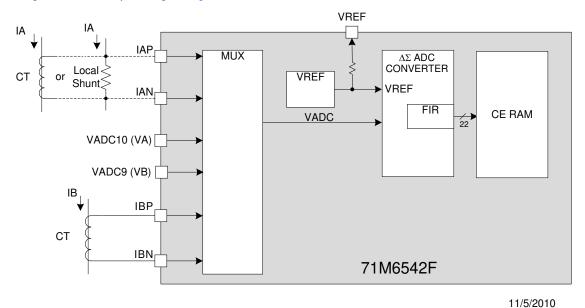

The AFE functions as a data acquisition system, controlled by the MPU. When used with locally connected sensors, as seen in Figure 2, the analog input signals (IAP-IAN, VA and IBP-IBN) are multiplexed to the ADC input and sampled by the ADC. The ADC output is decimated by the FIR filter and stored in CE RAM where it can be accessed and processed by the CE.

See Figure 6 for the multiplexer sequence corresponding to Figure 2. See Figure 35 for the meter configuration corresponding to Figure 2.

Figure 2. 71M6541D/F/G AFE Block Diagram (Local Sensors)

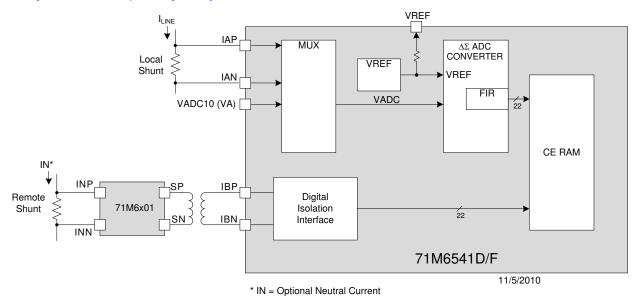

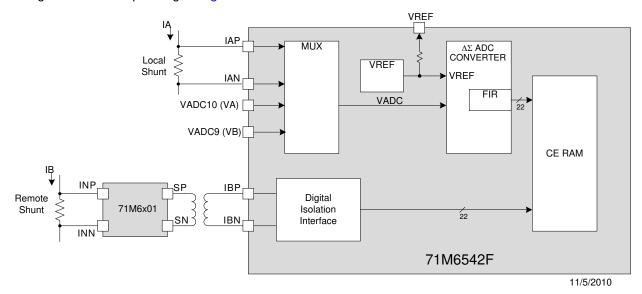

Figure 3 shows the 71M6541D/F/G multiplexer interface with one local and one remote resistive shunt sensor. As seen in Figure 3, when a remote isolated shunt sensor is connected via the 71M6x01, the samples associated with this current channel are not routed to the multiplexer, and are instead transferred digitally to the 71M6541D/F/G via the digital isolation interface and are directly stored in CE RAM.

See Figure 6 for the multiplexer timing sequence corresponding to Figure 3. See Figure 36 for the meter configurations corresponding to Figure 3.

Figure 3. 71M6541D/F/G AFE Block Diagram with 71M6x01

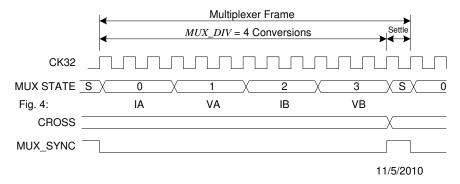

Figure 4 shows the 71M6542F/G AFE with locally connected sensors. The analog input signals (IAP-IAN, VA, IBP-IBN and VB) are multiplexed to the ADC input and sampled by the ADC. The ADC output is decimated by the FIR filter and stored in CE RAM where it can be accessed and processed by the CE.

See Figure 7 for the multiplexer timing sequence corresponding to Figure 4. See Figure 37 for the meter configuration corresponding to Figure 4.

Figure 4. 71M6542F/G AFE Block Diagram (Local Sensors)

Figure 5 shows the 71M6542F/G multiplexer interface with one local and one remote resistive shunt sensor. As seen in Figure 5, when a remote isolated shunt sensor is connected via the 71M6x01, the samples associated with this current channel are not routed to the multiplexer, and are instead transferred digitally to the 71M6542F/G via the digital isolation interface and are directly stored in CE RAM.

See Figure 6 for the multiplexer timing sequence corresponding to Figure 5. See Figure 38 for the meter configurations corresponding to Figure 5.

Figure 5. 71M6542F/G AFE Block Diagram with 71M6x01

## 2.2.1 Signal Input Pins

The 71M6541D/F/G features five ADC inputs. The 71M6542F/G features six ADC inputs.

IAP-IAN and IBP-IBN are intended for use as current sensor inputs. These four current sensor inputs can be configured as four single-ended inputs, or can be paired to form two differential inputs. For best performance, it is recommended to configure the current sensor inputs as differential inputs (i.e., IAP-IAN and IBP-IBN). The first differential input (IAP-IAN) features a pre-amplifier with a selectable gain of 1 or 8, and is intended for direct connection to a shunt resistor sensor, and can also be used with a Current Transformer (CT). The remaining differential pair (i.e., IBP-IBN) may be used with CTs, or may be enabled to interface to a remote 71M6x01 isolated current sensor providing isolation for a shunt resistor sensor using a low cost pulse transformer.

The remaining input in the 71M6541D/F/G (VA) is single-ended, and is intended for sensing the line voltage in a single-phase meter application using Equation 0 or 1 (see 2.3.4 Meter Equations on page 25). The 71M6542F/G features an additional single-ended voltage sensing input (VB) to support bi-phase applications using Equation 2. These single-ended inputs are referenced to the V3P3A pin.

All analog signal input pins measure voltage. In the case of shunt current sensors, currents are sensed as a voltage drop in the shunt resistor sensor. Referring to Figure 3, shunt sensors can be connected directly to the 71M654x (referred to as a 'local' shunt sensor) or connected via an isolated 71M6x01 (referred to as a 'remote' shunt sensor). In the case of Current Transformers (CT), the current is measured as a voltage across a burden resistor that is connected to the secondary winding of the CT. Meanwhile, line voltages are sensed through resistive voltage dividers. The VA and VB pins (VB is available in the 71M6542F/G only) are single-ended and their common return is the V3P3A pin.

Pins IAP-IAN can be programmed individually to be differential or single-ended as determined by the *DIFFA\_E* (*I/O RAM 0x210C[4]*) control bit. However, for most applications, IAP-IAN are configured as a differential input to work with a shunt or CT directly interfaced to the IAP-IAN differential input with the appropriate external signal conditioning components (see 4.2 Direct Connection of Sensors on page 92).

The performance of the IAP-IAN pins can be enhanced by enabling a pre-amplifier with a fixed gain of 8, using the I/O RAM control bit  $PRE\_E$  (I/O RAM 0x2704[5]). When  $PRE\_E = 1$ , IAP-IAN become the inputs to the 8x pre-amplifier, and the output of this amplifier is supplied to the multiplexer. The 8x amplification is useful when current sensors with low sensitivity, such as shunt resistors, are used. With  $PRE\_E$  set, the IAP-IAN input signal amplitude is restricted to 31.25 mV peak.

For the 71M654x application utilizing two shunt resistor sensors (Figure 3), the IAP-IAN pins are configured for differential mode to interface to a local shunt by setting the *DIFFA\_E* control bit. Meanwhile, the IBP-IBN pins are re-configured as digital balanced pair to communicate with a Teridian 71M6x01 Isolated Sensor interface by setting the *RMT\_E* control bit (*I/O RAM 0x2709[3]*). The 71M6x01 communicates with the 71M654x using a bi-directional digital data stream through an isolating low-cost pulse transformer. The 71M654x also supplies power to the 71M6x01 through the isolating transformer. This type of interface is further described at the end of this chapter (see 2.2.8 71M6x01 Isolated Sensor Interface (Remote Sensor Interface)).

For use with Current Transformers (CTs), as shown in Figure 2, the *RMT\_E* control bit is reset, so that the IBP-IBN pins are configured as local analog inputs. The IAP-IAN pins cannot be configured as a remote sensor interface.

#### 2.2.2 Input Multiplexer

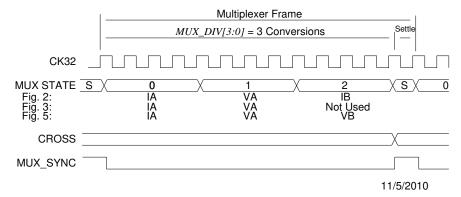

When operating with local sensors, the input multiplexer sequentially applies the input signals from the analog input pins to the input of the ADC (see Figure 2 and Figure 4). One complete sampling sequence is called a multiplexer frame. The multiplexer of the 71M6541D/F/G can select up to three input signals (IAP-IAN, VA, and IBP-IBN) per multiplexer frame as controlled by the I/O RAM control field  $MUX\_DIV[3:0]$  (I/O RAM 0x2100[7:4]) (see Figure 6). The multiplexer of the 71M6542F/G adds the VB signal to achieve a total of four inputs (see Figure 7). The multiplexer always starts at state 1 and proceeds until as many states as determined by  $MUX\_DIV[3:0]$  have been converted.

The 71M6541D/F/G and 71M6542F/G each require a unique CE code that is written for the specific application. Moreover, each CE code requires specific AFE and MUX settings in order to function properly. Table 1 provides the CE code and settings corresponding to the local sensor configurations shown in Figure 2 and Figure 4. Table 2 provides the CE code and settings corresponding to the local/remote sensor configuration utilizing the 71M6x01 as shown in Figure 3 and Figure 5.

| I/O RAM              | I/O RAM   | 71M6541D/F/G     | 71M6542F/G<br>(hex) |                  |  |

|----------------------|-----------|------------------|---------------------|------------------|--|

| Mnemonic             | Location  | (hex)            | Eq. 0 or 1          | Eq. 2            |  |

| FIR_LEN[1:0]         | 210C[2:1] | 1                | 1                   | 2                |  |

| ADC_DIV              | 2200[5]   | 1                | 1                   | 0                |  |

| PLL_FAST             | 2200[4]   | 1                | 1                   | 1                |  |

| MUX_DIV[3:0]         | 2100[7:4] | 3                | 3                   | 4                |  |

| MUX0_SEL[3:0]        | 2105[3:0] | 0                | 0                   | 0                |  |

| MUX1_SEL[3:0]        | 2105[7:4] | Α                | Α                   | Α                |  |

| MUX2_SEL[3:0]        | 2104[3:0] | 2                | 2                   | 2                |  |

| MUX3_SEL[3:0]        | 2104[7:4] | 1                | 1                   | 9                |  |

| RMT_E                | 2709[3]   | 0                | 0                   | 0                |  |

| DIFFA_E              | 210C[4]   | 1                | 1                   | 1                |  |

| DIFFB_E              | 210C[5]   | 1                | 1                   | 1                |  |

| EQU[2:0]             | 2106[7:5] | 0 or 1           | 0 or 1              | 2                |  |

| CE Code              |           | CE41A01          | CE41A01             | CE41A04          |  |

| Equations            |           | 0 or 1           | 0 or 1              | 2                |  |

|                      |           | 1 Shunt and 1 CT | 1 Shunt and 1 CT    | 1 Shunt and 1 CT |  |

| Current Sensor Types |           | or               | or                  | or               |  |

|                      |           | 2 CTs            | 2 CTs               | 2 CTs            |  |

| Applicable Figure    |           | Figure 2         | Figure 4            | Figure 4         |  |

Table 1. Required CE Code and Settings for Local Sensors

#### Notes:

Teridian updates the CE code periodically. Please contact your local Teridian representative to obtain the latest CE code and the associated settings. The configuration presented in this table is set by the MPU demonstration code during initialization.

| I/O RAM              | I/O RAM   | 71M6541D/F/G   | 71M6542F/G                                 |

|----------------------|-----------|----------------|--------------------------------------------|

| Mnemonic             | Location  | (hex)          | (hex)                                      |

| FIR_LEN[1:0]         | 210C[2:1] | 1              | 1                                          |

| ADC_DIV              | 2200[5]   | 1              | 1                                          |

| PLL_FAST             | 2200[4]   | 1              | 1                                          |

| MUX_DIV[3:0]         | 2100[7:4] | 3              | 3                                          |

| <i>MUX0_SEL[3:0]</i> | 2105[3:0] | 0              | 0                                          |

| <i>MUX1_SEL[3:0]</i> | 2105[7:4] | Α              | Α                                          |

| $MUX2\_SEL[3:0]^{I}$ | 2104[3:0] | 1              | 9                                          |

| $MUX3\_SEL[3:0]^{I}$ | 2104[7:4] | 1              | 1                                          |

| $RMT\_E$             | 2709[3]   | 1              | 1                                          |

| DIFFA_E              | 210C[4]   | 1              | 1                                          |

| $DIFFB\_E$           | 210C[5]   | 0              | 0                                          |

| EQU[2:0]             | 2106[7:5] | 0 or 1         | 0, 1 or 2                                  |

| CE Code              |           |                | 016201 <sup>2</sup><br>016601 <sup>3</sup> |

| Equations            |           | 0, 1           | 0, 1 and 2                                 |

|                      |           | 1 Local Shunt  | 1 Local Shunt                              |

| Current Sensor Type  |           | and            | and                                        |

|                      |           | 1 Remote Shunt | 1 Remote Shunt                             |

| Applicable Figure    |           | Figure 3       | Figure 5                                   |

| Notes:               |           |                |                                            |

Table 2. Required CE Code and Settings for 71M6x01 isolated Sensor

#### Notes:

- Although not used, set to 1 (the sample data is ignored by the CE) 1.

- 71M654x with 71M6201 remote sensor (200 Amps)

- 71M654x with 71M6601 remote sensor (60 Amps)

Teridian updates the CE code periodically. Please contact your local Teridian representative to obtain the latest CE code and the associated settings. The configuration presented in this table is set by the MPU demonstration code during initialization.

Using settings for the I/O RAM Mnemonics listed in Table 1 and Table 2 that do not match those required by the corresponding CE code being used results in undesirable side effects and must not be selected by the MPU. Consult your local Teridian representative to obtain the correct CE code and AFE / MUX settings corresponding to the application.

For a basic single-phase application, the IAP-IAN current input is configured for differential mode, whereas the VA pin is single-ended and is typically connected to the phase voltage via a resistor divider. The IBP-IBN differential input may be optionally used to sense the Neutral current. This configuration implies that the multiplexer applies a total of three inputs to the ADC. For this configuration, the multiplexer sequence is as shown in Figure 6. In this configuration IAP-IAN, IBP-IBN and VA are sampled, the extra conversion time slot (i.e., slot 2) is the optional Neutral current, and the physical current sensor for the Neutral current measurement may be omitted if not required.

For a standard single-phase application with tamper sensor in the neutral path, two current inputs can be configured for differential mode, using the pin pairs IAP-IAN and IBP-IBN. This means that the multiplexer applies a total of three inputs to the ADC. In this application, the system design may use two locally connected current sensors via IAP-IAN and IBP-IBN, as shown in Figure 2, and configured as differential inputs. Alternately, the IAP-IAN pin pair is configured as a differential input and connected to a local current shunt, and IBP-IBN is configured to connect to an isolated 71M6x01 isolated sensor (i.e.,  $RMT_E = 1$ ), as shown in Figure 3. The VA pin is typically connected to the phase voltage via resistor dividers. For this configuration, the multiplexer frame is also as shown in Figure 6 and time slot 2 is unused and ignored by the CE, as the samples corresponding to the remote sensor (IBP-IBN) do not pass through the multiplexer and are stored directly in CE RAM. The remote current sensor channel is sampled during the second half of the multiplexer frame and its timing relationship to the VA voltage is precisely known so that delay compensation can be properly applied.

The 71M6542F adds the ability to sample a second phase voltage (applied at the VB pin), which makes it suitable for meters with two voltage and two current sensors, such as meters implementing Equation 2 for dual-phase operation (P = VA\*IA+VB\*IB). Figure 7 shows the multiplexer sequence when four inputs are

processed with locally connected sensors, as shown in Figure 3. When using one local and one remote sensor (Figure 5), the multiplexer sequence is also as shown in Figure 7.

For both multiplexer sequences shown in Figure 6 and Figure 7, the frame duration is 13 CK32 cycles (where CK32 = 32768 Hz), therefore, the resulting sample rate is 32768 Hz / 13 = 2520.6 Hz.

Table 3 summarizes the various AFE input configurations.

Figure 6: States in a Multiplexer Frame  $(MUX\_DIV[3:0] = 3)$

Figure 7: States in a Multiplexer Frame  $(MUX\_DIV[3:0] = 4)$

Table 3: ADC Input Configuration

| Pin | ADC<br>Channel | Required<br>Setting            | Comment                                                                                                                                                                                                                                                |

|-----|----------------|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IAP | ADC0           |                                | Differential mode must be selected with $DIFFA\_E = 1$ (I/O $RAM\ 0x210C[4]$ ). The ADC results are stored in CE RAM                                                                                                                                   |

| IAN | ADC1           | $DIFFA\_E = 1$                 | location $ADCO$ ( $CE$ $RAM$ $0x0$ ), and $ADCI$ ( $CE$ $RAM$ $0xI$ ) is not disturbed.                                                                                                                                                                |

| IBP | ADC2           |                                | For locally connected sensors (Figure 2 and Figure 4), the differential input must be enabled by setting <i>DIFFB_E</i> ( <i>I/O RAM 0x210C[5]</i> .                                                                                                   |

| IBN | ADC3           | $DIFFB\_E = 1$ or $RMT\_E = 1$ | For the remote connected sensor (Figure 3 and Figure 5) with a remote shunt sensor, $RMT_E$ (I/O RAM 0x2709[3]) must be set.  In both cases, the ADC results are stored in RAM location $ADC2$ (CE RAM 0x2), and $ADC3$ (CE RAM 0x3) is not disturbed. |

| VA  | ADC10          |                                | Single-ended mode only. The ADC result is stored in RAM location <i>ADC10</i> ( <i>CE RAM 0xA</i> ).                                                                                                                                                   |

| VB  | ADC9           |                                | Single-ended mode only (71M6542F only). The ADC result is stored in RAM location <i>ADC9</i> ( <i>CE RAM 0x9</i> ).                                                                                                                                    |

Multiplexer advance, FIR initiation and chopping of the ADC reference voltage (using the internal CROSS signal, see 2.2.7 Voltage References) are controlled by the internal MUX\_CTRL circuit. Additionally, MUX\_CTRL launches each pass of the CE through its code. Conceptually, MUX\_CTRL is clocked by CK32, the 32768 Hz clock from the PLL block. The behavior of the MUX\_CTRL circuit is governed by:

- CHOP\_E[1:0] (I/O RAM 0x2106[3:2])

- MUX\_DIV[3:0] (I/O RAM 0x2100[7:4])

- FIR\_LEN[1:0] (I/O RAM 0x210C[2:1])

- ADC\_DIV (I/O RAM 0x2200[5])

The duration of each multiplexer state depends on the number of ADC samples processed by the FIR as determined by the FIR\_LEN[1:0] (I/O RAM 0x210C[2:1] control field. Each multiplexer state starts on the rising edge of CK32, the 32-kHz clock.

It is recommended that  $MUX\_DIV[3:0]$  (I/O RAM 0x2200[2:0]) be set to zero while changing the ADC configuration. Although not required, it minimizes system transients that might be caused by momentary shorts between the ADC inputs, especially when changing the  $DIFFn\_E$  control bits (I/O RAM 0x210C[5:4]). After the configuration bits are set, MUX DIV[3:0] should be set to the required value.

Additionally, the ADC can be configured to operate at  $\frac{1}{2}$  rate (32768\*75=2.46MHz). In this mode, the bias current to the ADC amplifiers is reduced and overall system power is reduced. The  $ADC_DIV(I/ORAMOx2200[5])$  bit selects full speed or half speed. At half speed, if  $FIR_LEN[1:0]$  is set to 01 (288), each conversion requires 4 XTAL cycles, resulting in a 2520Hz sample rate when  $MUX_DIV[3:0] = 3$ . Note that in order to work with these power-reducing settings, a corresponding CE code is required.

The duration of each time slot in CK32 cycles depends on FIR\_LEN[1:0], ADC\_DIV and PLL\_FAST:

```

Time Slot Duration (PLL\_FAST = 1) = (FIR\_LEN[1:0]+1) * (ADC\_DIV+1)

```

Time Slot Duration  $(PLL\_FAST = 0) = 3*(FIR\_LEN[1:0]+1)*(ADC\_DIV+1)$

The duration of a multiplexer frame in CK32 cycles is:

```

MUX Frame Duration = 3-2*PLL_FAST + Time Slot Duration * MUX_DIV[3:0]

```

The duration of a multiplexer frame in CK FIR cycles is:

MUX frame duration (CK\_FIR cycles) =

```

[3-2*PLL FAST + Time Slot Duration * MUX DIV] * (48+PLL FAST*102)

```

The ADC conversion sequence is programmable through the  $MUXx\_SEL$  control fields (I/O RAM 0x2100 to 0x2105). As stated above, there are three ADC time slots in the 71M6541D/F/G and four ADC time slots in the 71M6542F/G, as set by  $MUX\_DIV[3:0]$  (I/O RAM 0x2100[7:4]). In the expression  $MUXx\_SEL[3:0] = n$ , 'x' refers to the multiplexer frame time slot number and n refers to the desired ADC input number or ADC handle (i.e., ADC0 to ADC10, or simply 0 to 10 decimal). Thus, there are a total of 11 valid ADC handles in the 71M654x devices. For example, if  $MUX0\_SEL[3:0] = 0$ , then ADC0, corresponding to the sample from the IAP-IAN input (configured as a differential input), is positioned in the multiplexer frame during time slot 0. See Table 1 and Table 2 for the appropriate  $MUXx\_SEL[3:0]$  settings and other settings applicable to a particular CE code.

Note that when the remote sensor interface is enabled, and even though the samples corresponding to the remote sensor current (IBP-IBN) do not pass through the multiplexer, the  $MUX2\_SEL[3:0]$  and  $MUX3\_SEL[3:0]$  control fields must be written with a valid ADC handle that is not being used. Typically, ADC1 is used for this purpose (see Table 2). In this manner, the ADC1 handle, which is not used in the 71M6541D/F/G or 71M6542F/G, is used as a place holder in the multiplexer frame, in order to generate the correct multiplexer frame sequence and the correct sample rate. The resulting sample data stored in CERAMOxI is undefined and is ignored by the CE code. Meanwhile, the digital isolation interface takes care of automatically storing the samples for the remote interface current (IBP-IBN) in CERAMOxI.

Delay compensation and other functions in the CE code require the settings for  $MUX\_DIV[3:0]$ ,  $MUXx\_SEL[3:0]$ ,  $RMT\_E$ ,  $FIR\_LEN[1:0]$ ,  $ADC\_DIV$  and  $PLL\_FAST$  to be fixed for a given CE code. Refer to Table 1 and Table 2 for the settings that are applicable to the 71M6541D/F/G and 71M6542F/G.

Table 4 summarizes the I/O RAM registers used for configuring the multiplexer, signals pins, and ADC. All listed registers are 0 after reset and wake from battery modes, and are readable and writable.

| Name              | Location                                                                                        | Description                                                                                                                                         |  |  |

|-------------------|-------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| MUX0_SEL[3:0]     | 2105[3:0]                                                                                       | Selects the ADC input converted during time slot 0.                                                                                                 |  |  |

| MUX1_SEL[3:0]     | 2105[7:4]                                                                                       | Selects the ADC input converted during time slot 1.                                                                                                 |  |  |

| MUX2_SEL[3:0]     | 2104[3:0]                                                                                       | Selects the ADC input converted during time slot 2.                                                                                                 |  |  |

| MUX3_SEL[3:0]     | 2104[7:4]                                                                                       | Selects the ADC input converted during time slot 3.                                                                                                 |  |  |

| MUX4_SEL[3:0]     | 2103[3:0]                                                                                       | Selects the ADC input converted during time slot 4.                                                                                                 |  |  |

| MUX5_SEL[3:0]     | 2103[7:4]                                                                                       | Selects the ADC input converted during time slot 5.                                                                                                 |  |  |

| MUX6_SEL[3:0]     | 2102[3:0]                                                                                       | Selects the ADC input converted during time slot 6.                                                                                                 |  |  |

| MUX7_SEL[3:0]     | 2102[7:0]                                                                                       | Selects the ADC input converted during time slot 7.                                                                                                 |  |  |

| MUX8_SEL[3:0]     | 2101[3:0]                                                                                       | Selects the ADC input converted during time slot 8.                                                                                                 |  |  |

| MUX9_SEL[3:0]     | 2101[7:0]                                                                                       | Selects the ADC input converted during time slot 9.                                                                                                 |  |  |

| MUX10_SEL[3:0]    | 2100[3:0]                                                                                       | Selects the ADC input converted during time slot 10.                                                                                                |  |  |

| ADC_DIV           | 2200[5]                                                                                         | Controls the rate of the ADC and FIR clocks.                                                                                                        |  |  |

| MUX_DIV[3:0]      | 2100[7:4]                                                                                       | The number of ADC time slots in each multiplexer frame (maximum = 11).                                                                              |  |  |

| PLL_FAST          | 2200[4]                                                                                         | Controls the speed of the PLL and MCK.                                                                                                              |  |  |

| FIR_LEN[1:0]      | 210C[1]                                                                                         | Determines the number of ADC cycles in the ADC decimation FIR filter.                                                                               |  |  |

| DIFFA_E           | 210C[4]                                                                                         | Enables the differential configuration for analog input pins IAP-IAN.                                                                               |  |  |

| DIFFB_E           | 210C[5]                                                                                         | Enables the differential configuration for analog input pins IBP-IBN.                                                                               |  |  |

| RMT_E             | 2709[3]                                                                                         | Enables the remote sensor interface transforming pins IBP-IBN into a digital balanced differential pair for communications with the 71M6x01 sensor. |  |  |

| PRE_E             | 2704[5]                                                                                         | Enables the 8x pre-amplifier.                                                                                                                       |  |  |

| Refer to Table 76 | Refer to Table 76 starting on page 111 for more complete details about these I/O RAM locations. |                                                                                                                                                     |  |  |

Table 4: Multiplexer and ADC Configuration Bits

## 2.2.3 Delay Compensation

When measuring the energy of a phase (i.e., Wh and VARh) in a service, the voltage and current for that phase must be sampled at the same instant. Otherwise, the phase difference,  $\Phi$ , introduces errors.

$$\phi = \frac{t_{delay}}{T} \cdot 360^{\circ} = t_{delay} \cdot f \cdot 360^{\circ}$$

Where f is the frequency of the input signal, T = 1/f and  $t_{delay}$  is the sampling delay between current and voltage.

Traditionally, sampling is accomplished by using two A/D converters per phase (one for voltage and the other one for current) controlled to sample simultaneously. Maxim's Teridian Single-Converter Technology, however, exploits the 32-bit signal processing capability of its CE to implement "constant delay" all-pass filters. The all-pass filter corrects for the conversion time difference between the voltage and the corresponding current samples that are obtained with a single multiplexed A/D converter.

The "constant delay" all-pass filter provides a broad-band delay  $360^{\circ} - \theta$ , which is precisely matched to the difference in sample time between the voltage and the current of a given phase. This digital filter does not affect the amplitude of the signal, but provides a precisely controlled phase response.

The recommended ADC multiplexer sequence samples the current first, immediately followed by sampling of the corresponding phase voltage, thus the voltage is delayed by a phase angle  $\Phi$  relative to

the current. The delay compensation implemented in the CE aligns the voltage samples with their corresponding current samples by first delaying the current samples by one full sample interval (i.e.,  $360^{\circ}$ ), then routing the voltage samples through the all-pass filter, thus delaying the voltage samples by  $360^{\circ}$  -  $\theta$ , resulting in the residual phase error between the current and its corresponding voltage of  $\theta - \Phi$ . The residual phase error is negligible, and is typically less than  $\pm 1.5$  milli-degrees at 100Hz, thus it does not contribute to errors in the energy measurements.

When using remote sensors, the CE performs the same delay compensation described above to align each voltage sample with its corresponding current sample. Even though the remote current samples do not pass through the 71M654x multiplexer, their timing relationship to their corresponding voltages is fixed and precisely known, provided that the  $MUXn\_SEL[3:0]$  slot assignment fields are programmed as shown in Table 1 and Table 2.

#### 2.2.4 ADC Pre-Amplifier

The ADC pre-amplifier is a low-noise differential amplifier with a fixed gain of 8 available only on the IAP-IAN sensor input pins. A gain of 8 is enabled by setting  $PRE\_E = 1$  (I/O RAM 0x2704[5]). When disabled, the supply current of the pre-amplifier is <10 nA and the gain is unity. With proper settings of the  $PRE\_E$  and  $DIFFA\_E$  (I/O RAM 0x210C[4]) bits, the pre-amplifier can be used whether differential mode is selected or not. For best performance, the differential mode is recommended. In order to save power, the bias current of the pre-amplifier and ADC is adjusted according to the  $ADC\_DIV$  control bit (I/O RAM 0x2200[5]).

#### 2.2.5 A/D Converter (ADC)

A single  $2^{nd}$  order delta-sigma A/D converter digitizes the voltage and current inputs to the device. The resolution of the ADC, including the sign bit, is 21 bits ( $FIR\_LEN[1:0] = 1$ , I/O RAM 0x210C[2:1]), or 22 bits ( $FIR\_LEN[1:0] = 2$ ). The ADC is clocked by CKADC.

Initiation of each ADC conversion is controlled by MUX\_CTRL internal circuit as described above. At the end of each ADC conversion, the FIR filter output data is stored into the CE RAM location determined by the multiplexer selection. FIR data is stored LSB justified, but shifted left 9 bits.

#### 2.2.6 FIR Filter

The finite impulse response filter is an integral part of the ADC and it is optimized for use with the multiplexer. The purpose of the FIR filter is to decimate the ADC output to the desired resolution. At the end of each ADC conversion, the output data is stored into the fixed CE RAM location determined by the multiplexer selection as shown in Table 1 and Table 2.

#### 2.2.7 Voltage References

A bandgap circuit provides the reference voltage to the ADC. The amplifier within the reference is chopper stabilized, i.e., the chopper circuit can be enabled or disabled by the MPU using the I/O RAM control field  $CHOP\_E[1:0]$  (I/O RAM 0x2106[3:2]). The two bits in the  $CHOP\_E[1:0]$  field enable the MPU to operate the chopper circuit in regular or inverted operation, or in toggling modes (recommended). When the chopper circuit is toggled in between multiplexer cycles, dc offsets on VREF are automatically be averaged out, therefore the chopper circuit should always be configured for one of the toggling modes.

Since the VREF band-gap amplifier is chopper-stabilized, the dc offset voltage, which is the most significant long-term drift mechanism in the voltage references (VREF), is automatically removed by the chopper circuit. Both the 71M654x and the 71M6x01 feature chopper circuits for their respective VREF voltage reference.

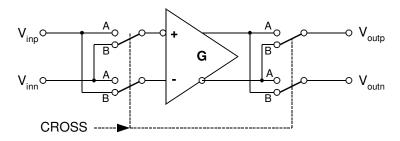

The general topology of a chopped amplifier is shown in Figure 8. The CROSS signal is an internal onchip signal and is not accessible on any pin or register.

Figure 8: General Topology of a Chopped Amplifier

It is assumed that an offset voltage Voff appears at the positive amplifier input. With all switches, as controlled by CROSS (an internal signal), in the A position, the output voltage is:

$$Voutp - Voutn = G (Vinp + Voff - Vinn) = G (Vinp - Vinn) + G Voff$$

With all switches set to the B position by applying the inverted CROSS signal, the output voltage is:

$$Voutn - Voutp = G (Vinn - Vinp + Voff) = G (Vinn - Vinp) + G Voff, or Voutp - Voutn = G (Vinp - Vinn) - G Voff$$

Thus, when CROSS is toggled, e.g., after each multiplexer cycle, the offset alternately appears on the output as positive and negative, which results in the offset effectively being eliminated, regardless of its polarity or magnitude.

When CROSS is high, the connection of the amplifier input devices is reversed. This preserves the overall polarity of that amplifier gain; it inverts its input offset. By alternately reversing the connection, the amplifier's offset is averaged to zero. This removes the most significant long-term drift mechanism in the voltage reference. The CHOP\_E[1:0] (I/O RAM 0x2106[3:2]) control field controls the behavior of CROSS. The CROSS signal reverses the amplifier connection in the voltage reference in order to negate the effects of its offset. On the first CK32 rising edge after the last multiplexer state of its sequence, the multiplexer waits one additional CK32 cycle before beginning a new frame. At the beginning of this cycle, the value of CROSS is updated according to the CHOP\_E[1:0] field. The extra CK32 cycle allows time for the chopped VREF to settle. During this cycle, MUXSYNC is held high. The leading edge of MUXSYNC initiates a pass through the CE program sequence. The beginning of the sequence is the serial readout of the four RTM words.

$CHOP\_E[1:0]$  has four states: positive, reverse, and two toggle states. In the positive state,  $CHOP\_E[1:0]$  = 01, CROSS is held low. In the reverse state,  $CHOP\_E[1:0]$  = 10, CROSS is held high.

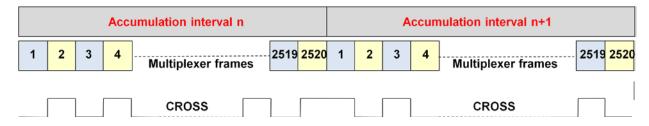

Figure 9: CROSS Signal with  $CHOP_E = 00$

Figure 9 shows CROSS over two accumulation intervals when  $CHOP\_E[1:0] = 00$ : At the end of the first interval, CROSS is high, at the end of the second interval, CROSS is low. Operation with  $CHOP\_E[1:0] = 00$  does not require control of the chopping mechanism by the MPU.

In the second toggle state,  $CHOP\_E[1:0] = 11$ , CROSS does not toggle at the end of the last multiplexer cycle in an accumulation interval.

A second, low-power voltage reference is used in the LCD system and for the comparators that support transitions to and from the battery modes.

#### 2.2.8 71M6x01 Isolated Sensor Interface (Remote Sensor Interface)

## 2.2.8.1 General Description

Non-isolating sensors, such as shunt resistors, can be connected to the inputs of the 71M654x via a combination of a pulse transformer and a 71M6x01 IC (a top-level block diagram of this sensor interface is shown in Figure 36). The 71M6x01 receives power directly from the 71M654x via a pulse transformer and does not require a dedicated power supply circuit. The 71M6x01 establishes 2-way communication with the 71M654x, supplying current samples and auxiliary information such as sensor temperature via a serial data stream.

One 71M6x01 Isolated Sensor can be supported by the 71M6541D/F/G and 71M6542F/G. When remote interface IBP-IBN is enabled, the two analog current inputs pins IBP and IBN become a digital balanced differential interface to the remote sensor. See Table 3 for details.

Each 71M6x01 Isolated Sensor consists of the following building blocks:

- Power supply for power pulses received from the 71M654x

- Digital communications interface

- Shunt signal pre-amplifier

- Delta-Sigma ADC Converter with precision bandgap reference (chopping amplifier)

- Temperature sensor

- Fuse system containing part-specific information

During an ordinary multiplexer cycle, the 71M654x internally determines which other channels are enabled with  $MUX\_DIV[3:0]$  (I/O RAM 0x2100[7:4]). At the same time, it decimates the modulator output from the 71M6x01 Isolated Sensors. Each result is written to CE RAM during one of its CE access time slots. See Table 3 for the CE RAM locations of the sampled signals.

#### 2.2.8.2 Communication between 71M654x and 71M6x01 Isolated Sensor

The ADC of the 71M6x01 derives its timing from the power pulses generated by the 71M654x and as a result, operates its ADC slaved to the frequency of the power pulses. The generation of power pulses, as well as the communication protocol between the 71M654x and 71M6x01 Isolated Sensor is automatic and transparent to the user. Details are not covered in this data sheet.

#### 2.2.8.3 Control of the 71M6x01 Isolated Sensor

The 71M654x can read or write certain types of information from each 71M6x01 isolated sensor.

The data to be read is selected by a combination of the RCMD[4:0] and TMUXRn[2:0]. To perform a read transaction from one of the 71M6x01 devices, the MPU first writes the TMUXRn[2:0] field (where n=2,4,6, located at I/O RAM 0x270A[2:0], 0x270A[6:4] and 0x2709[2:0], respectively). Next, the MPU writes RCMD[4:0] (SFR 0xFC[4:0]) with the desired command and phase selection. When the RCMD[4:2] bits have cleared to zero, the transaction has been completed and the requested data is available in  $RMT_RD[15:0]$  (I/O RAM 0x2602[7:0] is the MSB and 0x2603[7:0] is the LSB). The read parity error bit,  $PERR_RD$  (SFR 0xFC[6]) is also updated during the transaction. If the MPU writes to RCMD[4:0] before a previously initiated read transaction is completed, the command is ignored. Therefore, the MPU must wait for RCMD[4:2]=0 before proceeding to issue the next remote sensor read command.

The *RCMD[4:0]* field is divided into two sub-fields, *COMMAND=RCMD[4:2]* and *PHASE=RCMD[1:0]*, as shown in Table 5.

|     | Command<br>RCMD[4:2] |    | Selector<br>MD[1:0] | Associated TMUXRn Control Field |

|-----|----------------------|----|---------------------|---------------------------------|

| 000 | Invalid              | 00 | Invalid             |                                 |

| 001 | Command 1            | 01 | IBP-IBN             | TMUXRB [2:0]                    |