Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

### **Energy Meter ICs**

### **General Description**

The 71M6545T/71M6545HT metrology processors are based on Maxim Integrated's 4th-generation metering architecture supporting the 71M6xxx series of isolated current sensing products that offer drastic reduction in component count, immunity to magnetic tampering, and unparalleled reliability. The 71M6545T/71M6545HT integrate our Single Converter Technology® with a 22-bit delta sigma ADC, a customizable 32-bit computation engine (CE) for core metrology functions, as well as a user-programmable 8051-compatible application processor (MPU) core with 64KB flash and 5KB RAM.

An external host processor can access metrology functions directly through the SPI interface, or alternatively through the embedded MPU core in applications requiring metrology data capture, storage, and preprocessing within the metrology subsystem. In addition, the devices integrate an RTC, DIO, and UART. A complete array of ICE and development tools, programming libraries, and reference designs enable rapid development and certification of meters that meet all ANSI and IEC electricity metering standards worldwide.

The 71M6545T/71M6545HT operate over the industrial temperature range and come in a 64-pin lead(Pb)-free package.

### **Applications**

Three-Phase Residential, Commercial, and Industrial Energy Meters

<u>Ordering Information</u> and <u>Typical Operating Circuit</u> appear at end of data sheet.

Single Converter Technology is a registered trademark of Maxim Integrated Products, Inc.

MICROWIRE is a registered trademark of National Semiconductor Corp.

### **Benefits and Features**

- SoC Integration and Unique Isolation Technique Reduces BOM Cost Without Sacrificing Performance

- 0.1% Typical Accuracy Over 2000:1 Current Range

- Exceeds IEC 62053/ANSI C12.20 Standards

- Four-Quadrant Metering

- 46-64Hz Line Frequency Range with the Same Calibration

- Phase Compensation (±10°)

- Independent 32-Bit Compute Engine

- 64KB Flash, 5KB RAM

- · Built-In Flash Security

- SPI Interface to Host with Flash Program Capability

- Up to Four Pulse Outputs with Pulse Count

- 8-Bit MPU (80515), Up to 5 MIPS (Optional Use)

- Full-Speed MPU Clock in Brownout Mode

- Up to 29 Multifunction DIO Pins

- Hardware Watchdog Timer (WDT)

- UART for AMR or Other Communication Duties

- I<sup>2</sup>C/MICROWIRE® EEPROM Interface

- Innovative Isolation Technology (Requires Companion 71M6xxx Sensor, also from Maxim Integrated) Eliminates Current Transformers

- Four Current Sensor Inputs with Selectable Differential Mode

- Selectable Gain of 1 or 8 for One Current Input to Support Neutral Current Shunt

- High-Speed Wh/VARh Pulse Outputs with Programmable Width

- Digital Temperature Compensation Improves System Performance

- Metrology Compensation

- Accurate RTC for TOU Functions with Automatic Temperature Compensation for Crystal in All Power Modes

- Power Management Extends Battery Life During Power Outages

- · Two Battery-Backup Modes

- Brownout Mode (BRN)

- Sleep Mode (SLP)

- Wake-Up on Pin Events and Wake-On Timer

- 1µA in Sleep Mode

### **TABLE OF CONTENTS**

| General Description                 |    |

|-------------------------------------|----|

| Applications                        |    |

| Benefits and Features               |    |

| Absolute Maximum Ratings            |    |

| Electrical Characteristics          |    |

| Recommended External Components     |    |

| Pin Configuration                   |    |

| Pin Descriptions                    |    |

| Block Diagram                       |    |

| Hardware Description                |    |

| Analog Front-End (AFE)              |    |

| Signal Input Pins                   |    |

| Input Multiplexer                   |    |

| Delay Compensation                  |    |

| ADC Preamplifier                    |    |

| Analog-to-Digital Converter (ADC)   |    |

| FIR Filter                          |    |

| Voltage References                  |    |

| Isolated Sensor Interface           |    |

| Digital Computation Engine (CE)     |    |

| Meter Equations                     |    |

| Real-Time Monitor                   |    |

| Pulse Generators                    |    |

| XPULSE and YPULSE                   |    |

| VPULSE and WPULSE                   |    |

| 80515 MPU Core                      |    |

| Memory Organization and Addressing  |    |

| Program Memory                      |    |

| MPU External Data Memory (XRAM)     |    |

| MOVX Addressing                     |    |

| Dual Data Pointer                   |    |

| Internal Data Memory Map and Access |    |

| Special Function Registers          |    |

| Timers and Counters                 |    |

| Interrupts                          |    |

| Interrupt Overview                  |    |

| External MPU Interrupts             |    |

| On-Chin Resources                   | 30 |

| TABLE OF CONTENTS (continued)             |    |

|-------------------------------------------|----|

| Flash Memory                              | 30 |

| MPU/CE RAM                                |    |

| I/O RAM                                   |    |

| Crystal Oscillator                        |    |

| PLL                                       |    |

| Real-Time Clock (RTC)                     |    |

| RTC Trimming                              |    |

| RTC Interrupts                            |    |

| Temperature Sensor                        |    |

| Battery Monitor                           |    |

| Digital I/O                               |    |

| EEPROM Interface                          |    |

| Two-Pin EEPROM Interface                  |    |

| Three-Wire EEPROM Interface               |    |

| UART                                      |    |

| SPI Slave Port                            |    |

| SPI Safe Mode                             |    |

| SPI Flash Mode (SFM)                      |    |

| Hardware Watchdog Timer                   |    |

| Test Ports                                |    |

| Functional Description                    | 35 |

| Theory of Operation                       |    |

| Battery Modes                             |    |

| Brownout Mode                             |    |

| Sleep Mode                                |    |

| Applications Information                  | 36 |

| Connecting 5V Devices                     |    |

| Direct Connection of Sensors              |    |

| Using the 71M6545T/HT with Local Sensors  |    |

| Using the 71M6545T/HT with Remote Sensors |    |

| Metrology Temperature Compensation        |    |

| Connecting I <sup>2</sup> C EEPROMs       |    |

| Connecting Three-Wire EEPROMs             |    |

| UART                                      |    |

| Reset                                     |    |

| Emulator Port Pins                        |    |

| MPU Firmware Library                      |    |

| Motor Calibration                         | 42 |

# Energy Meter ICs

| TABLE OF CONTENTS (continued) |

|-------------------------------|

| Firmware Interface            |

| Overview: Functional Order    |

| I/O RAM Map: Details          |

| Reading the Info Page         |

| CE Interface Description      |

| CE Program                    |

| CE Data Format                |

| Constants                     |

| Environment55                 |

| CE Calculations               |

| CE Input Data                 |

| Status and Control            |

| Transfer Variables            |

| Pulse Generation              |

| CE Flow Diagrams              |

| Ordering Information          |

| Package Information           |

| Typical Operating Circuit     |

| Revision History              |

# Energy Meter ICs

| LIST OF FIGURES                                                                                   |    |

|---------------------------------------------------------------------------------------------------|----|

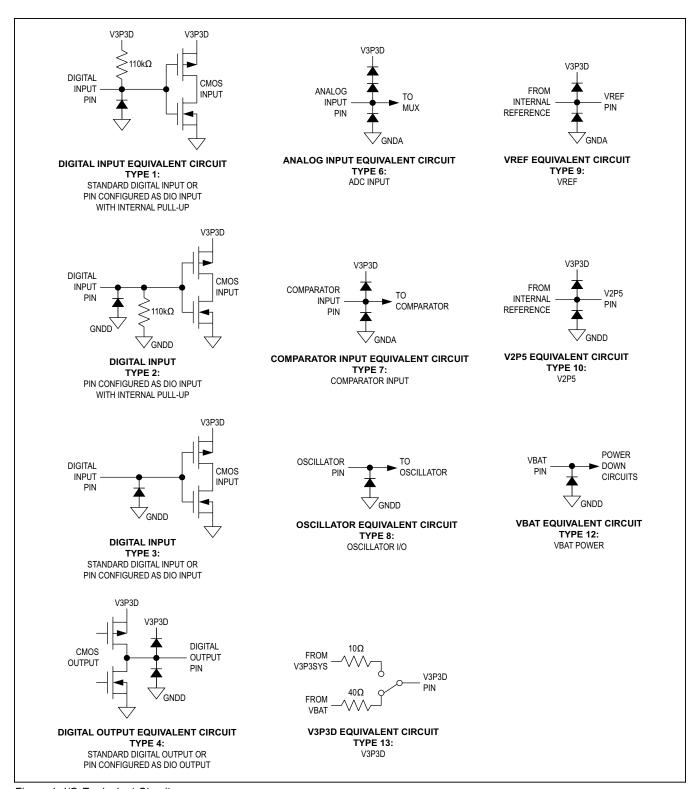

| Figure 1. I/O Equivalent Circuits                                                                 | 16 |

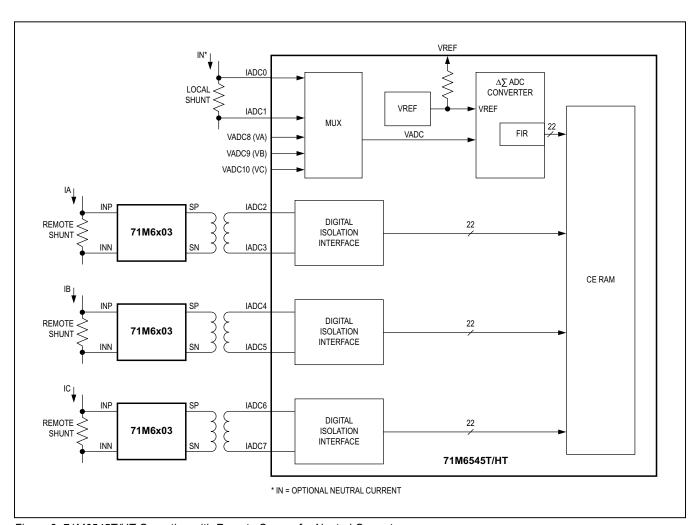

| Figure 2. 71M6545T/HT Operating with Local Sensors                                                | 19 |

| Figure 3. 71M6545T/HT Operating with Remote Sensor for Neutral Current                            | 20 |

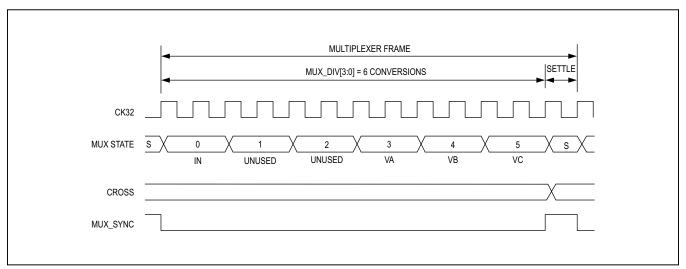

| Figure 4. Multiplexer Sequence with Neutral Channel and Remote Sensors                            | 22 |

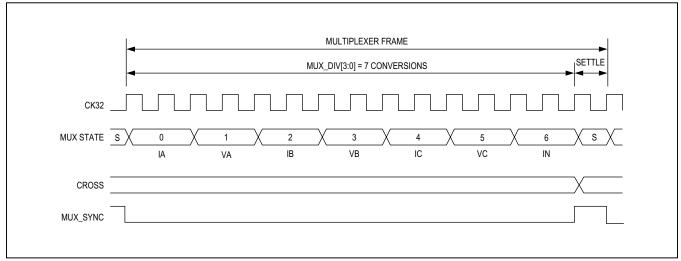

| Figure 5. Multiplexer Sequence with Neutral Channel and Current Transformers                      | 22 |

| Figure 6. Waveforms Comparing Voltage, Current, Energy per Interval, and Accumulated Energy       | 36 |

| Figure 7. Typical Voltage Sense Circuit Using Resistive Divider                                   | 38 |

| Figure 8. Typical Current-Sense Circuit Using Current Transformer in a Single-Ended Configuration | 38 |

| Figure 9. Typical Current-Sense Circuit Using Current Transformer in a Differential Configuration | 38 |

| Figure 10. Typical Current-Sense Circuit Using Shunt in a Differential Configuration              | 38 |

| Figure 11. 71M6545T/HT Typical Operating Circuit Using Locally Connected Sensors                  | 39 |

| Figure 12. 71M6545T/HT Typical Operating Circuit Using Remote Neutral Current Sensor              | 40 |

| Figure 13. Typical I <sup>2</sup> C Operating Circuit                                             | 41 |

| Figure 14. Typical UART Operating Circuit                                                         | 41 |

| Figure 15. Typical Reset Circuits                                                                 | 41 |

| Figure 16. Typical Emulator Connections                                                           | 41 |

| Figure 17. CE Data Flow—Multiplexer and ADC                                                       | 63 |

| Figure 18. CE Data Flow—Offset, Gain, and Phase Compensation                                      | 63 |

| Figure 19. CE Data Flow—Squaring and Summation                                                    | 64 |

# Energy Meter ICs

| LIST OF TABLES                                         |    |

|--------------------------------------------------------|----|

| Table 1. ADC Input Configuration                       | 23 |

| Table 2. Inputs Selected in Multiplexer Cycles         | 25 |

| Table 3. CKMPU Clock Frequencies                       | 26 |

| Table 4. Memory Map                                    | 26 |

| Table 5. Internal Data Memory Map                      | 27 |

| Table 6. Special Function Register Map                 | 28 |

| Table 7. Generic 80515 SFRs: Location and Reset Values | 28 |

| Table 8. Timers/Counters Mode Description              | 29 |

| Table 9. External MPU Interrupts                       | 30 |

| Table 10. Test Ports                                   | 34 |

| Table 11. Info Page Trim Fuses                         | 43 |

| Table 12. I/O RAM Locations in Numerical Order         | 44 |

| Table 13. I/O RAM Locations in Alphabetical Order      | 47 |

| Table 14. Power Equations                              | 57 |

| Table 15. CE Raw Data Access Locations                 | 57 |

| Table 16. CE Status Register                           | 58 |

| Table 17. CE Configuration Register                    | 58 |

| Table 18. Sag Threshold and Gain Adjustment Registers  | 59 |

| Table 19. CE Transfer Registers                        | 59 |

| Table 20. CE Pulse Generation Parameters               | 60 |

| Table 21. Other CE Parameters                          | 61 |

| Table 22. CE Calibration Parameters                    | 62 |

## **Absolute Maximum Ratings**

| (All voltages referenced to GNDA.)                                   | DIO Pins                                                        |

|----------------------------------------------------------------------|-----------------------------------------------------------------|

| Supplies and Ground Pins                                             | Configured as Digital Inputs10mA to +10mA, -0.5V to +6.0V       |

| V <sub>V3P3SYS</sub> , V <sub>V3P3A</sub> 0.5V to +4.6V              | Configured as Digital Outputs10mA to +10mA, -0.5V to            |

| V <sub>BAT</sub> , V <sub>BAT_RTC</sub> 0.5V to +4.6V                | $(V_{V3P3D} + 0.5V)$                                            |

| GNDD0.1V to +0.1V                                                    | Digital Pins                                                    |

| Analog Output Pins                                                   | Inputs (PB, RESET, RX, ICE_E, TEST)10mA to +10mA,               |

| V <sub>REF</sub> 10mA to +10mA, -0.5V to (V <sub>V3P3A</sub> + 0.5V) | -0.5V to +6.0V                                                  |

| V <sub>DD</sub> 10mA to +10mA, -0.5V to +3.0V                        | Outputs (TX)10mA to +10mA, -0.5V to (V <sub>V3P3D</sub> + 0.5V) |

| V <sub>V3P3D</sub> 10mA to +10mA, -0.5V to +4.6V                     | Temperature                                                     |

| Analog Input Pins                                                    | Operating Junction Temperature (peak, 100ms)+140°C              |

| IADC0-7, VADC8-1010mA to +10mA, -0.5V to                             | Operating Junction Temperature (continuous)+125°C               |

| $(V_{V3P3A} + 0.5V)$                                                 | Storage Temperature45°C to +140°C                               |

| XIN, XOUT10mA to +10mA, -0.5V to +3.0V                               | Lead Temperature (soldering, 10s)+300°C                         |

|                                                                      | Soldering Temperature (reflow)+260°C                            |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **Electrical Characteristics**

(Limits are production tested at  $T_A$  = +25°C. Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization.)

| PARAMETER                                                          | CONDITIONS                   | MIN - | TYP MAX | UNITS |

|--------------------------------------------------------------------|------------------------------|-------|---------|-------|

| RECOMMENDED OPERATING                                              | CONDITIONS                   |       |         |       |

| V <sub>V3P3SYS</sub> and V <sub>V3P3A</sub> Supply Voltage         | Precision metering operation | 3.0   | 3.6     | V     |

| V                                                                  | PLL_FAST = 1                 | 2.65  | 3.8     | V     |

| $V_{BAT}$                                                          | PLL_FAST = 0                 | 2.40  | 3.8     |       |

| V <sub>BAT_RTC</sub>                                               |                              | 2.0   | 3.8     | V     |

| Operating Temperature                                              |                              | -40   | +85     | °C    |

| INPUT LOGIC LEVELS                                                 |                              |       |         |       |

| Digital High-Level Input Voltage (V <sub>IH</sub> )                |                              | 2     |         | ٧     |

| Digital Low-Level Input Voltage (V <sub>IL</sub> )                 |                              |       | 0.8     | ٧     |

| Input Pullup Current, (I <sub>IL</sub> ) E_<br>RTXT, E_RST, E_TCLK |                              | 10    | 100     | μΑ    |

| Input Pullup Current, (I <sub>IL</sub> ) OPT_<br>RX, OPT_TX        |                              | 10    | 100     | μA    |

| Input Pullup Current, (I <sub>IL</sub> ) SPI_<br>CSZ (SEGDIO36)    |                              | 10    | 100     | μA    |

| Input Pullup Current, (I <sub>IL</sub> ) Other Digital Inputs      |                              | -1    | +1      | μA    |

| Input Pulldown Current (I <sub>IH</sub> ), ICE_E, RESET, TEST      |                              | 10    | 100     | μΑ    |

| Input Pulldown Current, (I <sub>IH</sub> )<br>Other Digital Inputs |                              | -1    | +1      | μA    |

(Limits are production tested at  $T_A$  = +25°C. Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization.)

| PARAMETER                                                   | CONDITIONS                                                  | MIN T                                 | YP MAX                                                                  | UNITS |

|-------------------------------------------------------------|-------------------------------------------------------------|---------------------------------------|-------------------------------------------------------------------------|-------|

| OUTPUT LOGIC LEVELS                                         | ·                                                           |                                       |                                                                         |       |

| Digital High-Level Output                                   | I <sub>LOAD</sub> = 1mA                                     | V <sub>V3P3D</sub> - 0.4              |                                                                         | V     |

| Voltage (V <sub>OH</sub> )                                  | I <sub>LOAD</sub> = 15mA (Note 1)                           | V <sub>V3P3D</sub> - 0.8              |                                                                         | V     |

| Digital Low-Level Output                                    | I <sub>LOAD</sub> = 1mA                                     | 0                                     | 0.4                                                                     | V     |

| Voltage (V <sub>OL</sub> )                                  | I <sub>LOAD</sub> = 15mA (Note 1)                           | 0                                     | 0.8                                                                     | V     |

| <b>BATTERY MONITOR</b> Battery Voltage Equation: 3.3        | + (BSENSE - BNOM3P3) x 0.0252 + STEMP x 2.79                | 9E-5 V                                |                                                                         |       |

|                                                             | V <sub>BAT</sub> = 2.0V                                     | -3.5                                  | +3.5                                                                    | - %   |

| Magaziramant Errar                                          | V <sub>BAT</sub> = 2.5V                                     | -3.5                                  | +3.5                                                                    |       |

| Measurement Error                                           | V <sub>BAT</sub> = 3.0V                                     | -3.0                                  | +3.0                                                                    |       |

|                                                             | V <sub>BAT</sub> = 3.8V                                     | -3.0                                  | +3.0                                                                    |       |

| Input Impedance                                             |                                                             | 260                                   |                                                                         | kΩ    |

| Passivation Current                                         | I <sub>BAT</sub> (BCURR = 1) – I <sub>BAT</sub> (BCURR = 0) | 50 1                                  | 00 165                                                                  | μA    |

| TEMPERATURE MONITOR                                         |                                                             |                                       |                                                                         |       |

| Temperature Measurement Equation                            |                                                             | - 0.0023 ><br>[(STEMP <sub>T85P</sub> | EMP x 0.085<br>x STEMP x<br>- STEMP <sub>T22P</sub> )/<br>2P) - 12.857] | °C    |

|                                                             | T <sub>A</sub> = +85°C                                      | -3.2                                  | +3.2                                                                    |       |

| Temperature Error                                           | T <sub>A</sub> = 0°C to +70°C                               | -2.65                                 | +2.65                                                                   | °C    |

| (Note 1)                                                    | T <sub>A</sub> = -20°C                                      | -3.4                                  | +3.4                                                                    |       |

|                                                             | T <sub>A</sub> = -40°C                                      | -3.8                                  | +3.8                                                                    |       |

| V <sub>BAT_RTC</sub> Charge per<br>Measurement              |                                                             |                                       | 2                                                                       | μC    |

| Duration of Temperature<br>Measurement after TEMP_<br>START |                                                             | :                                     | 22 40                                                                   | ms    |

(Limits are production tested at  $T_A$  = +25°C. Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization.)

| PARAMETER                                        |                                       | CONDITIONS                                                  | MIN  | TYP  | MAX   | UNITS  |

|--------------------------------------------------|---------------------------------------|-------------------------------------------------------------|------|------|-------|--------|

| SUPPLY CURRENT                                   |                                       |                                                             | •    |      |       |        |

|                                                  |                                       | P3SYS = 3.3V; MPU_DIV = 3 (614kHz<br>LL_FAST = 1; PRE_E = 0 |      | 5.5  | 6.7   |        |

| V <sub>V3P3A</sub> + V <sub>V3P3SYS</sub> Supply | PLL_FAST = 0                          | )                                                           |      | 2.6  | 3.5   | mA     |

| Current (Note 1)                                 | PRE_E = 1                             |                                                             |      | 5.7  | 6.9   |        |

|                                                  | PLL_FAST = 0                          | ), PRE_E=1                                                  |      | 2.6  | 3.6   |        |

| Dynamic Current                                  |                                       |                                                             |      | 0.4  | 0.6   | mA/MHz |

|                                                  | Mission mode                          |                                                             | -300 |      | +300  | nA     |

| V <sub>BAT</sub> Current                         | Brownout mod                          | e                                                           |      | 2.4  | 3.2   | mA     |

|                                                  | Sleep mode                            |                                                             | -300 |      | +300  | nA     |

|                                                  | Brownout mod                          | e                                                           |      | 400  | 650   | nA     |

| V <sub>BAT_RTC</sub> Current                     | Sleep mode, T                         | - <sub>A</sub> ≤ 25°C                                       |      | 0.7  | 1.7   | μA     |

|                                                  | Sleep mode, T                         | A = 85°C (Note 1)                                           |      | 1.5  | 3.2   | μA     |

| Flash Write Current                              | Maximum flash                         | n write rate                                                |      | 7.1  | 9.3   | mA     |

| V <sub>V3P3D</sub> SWITCH                        |                                       |                                                             |      |      |       | ,      |

| On Desistance                                    | V <sub>V3P3SYS</sub> to \             | / <sub>V3P3D</sub> , I <sub>V3P3D</sub> ≤ 1mA               |      |      | 11    | Ω      |

| On-Resistance                                    | V <sub>BAT</sub> to V <sub>V3P3</sub> | <sub>BD</sub> , I <sub>V3P3D</sub> ≤ 1mA                    |      |      | 11    |        |

| Гон                                              |                                       |                                                             |      |      |       | mA     |

| INTERNAL POWER FAULT CO                          | MPARATOR                              |                                                             |      |      |       | ,      |

| D                                                | 100mV overdr                          | ive, falling                                                | 20   |      | 200   |        |

| Response Time                                    | 100mV overdr                          | ive, rising                                                 |      |      | 200   | μs     |

| Falling Threshold, 3.0V<br>Comparator            |                                       |                                                             | 2.83 | 2.93 | 3.03  | V      |

| Falling Threshold, 2.8V<br>Comparator            |                                       |                                                             | 2.71 | 2.81 | 2.91  | V      |

| Difference between 3.0V and 2.8V comparators     |                                       |                                                             | 47   | 136  | 220   | mV     |

| Falling Threshold, 2.25V<br>Comparator           |                                       |                                                             | 2.14 | 2.33 | 2.51  | V      |

| Falling Threshold, 2.0V<br>Comparator            |                                       |                                                             | 1.90 | 2.07 | 2.23  | V      |

| Difference between 2.25V and 2.0V Comparators    |                                       |                                                             | 0.15 | 0.25 | 0.365 | V      |

|                                                  |                                       | 3.0V comparator                                             | 13   | 45   | 81    |        |

| Lhyatarasia                                      | T - 122°C                             | 2.8V comparator                                             | 17   | 42   | 79    | mV     |

| Hysteresis                                       | T <sub>A</sub> = +22°C                | 2.25V comparator                                            | 7    | 33   | 71    |        |

|                                                  |                                       | 2.0V comparator                                             | 4    | 28   | 83    |        |

(Limits are production tested at  $T_A$  = +25°C. Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization.)

| PARAMETER                                                                          | CONDITIONS                                                                      | MIN                                                                         | TYP                                  | MAX    | UNITS   |

|------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|-----------------------------------------------------------------------------|--------------------------------------|--------|---------|

| 2.5V REGULATOR                                                                     |                                                                                 |                                                                             |                                      |        |         |

| V <sub>V2P5</sub> Output Voltage                                                   | V <sub>V3P3</sub> = 3.0V to 3.8V, I <sub>LOAD</sub> = 0mA                       | 2.55                                                                        | 2.65                                 | 2.75   | V       |

| V <sub>V2P5</sub> Load Regulation                                                  | V <sub>BAT</sub> = 3.3V, V <sub>V3P3</sub> = 0V, I <sub>LOAD</sub> = 0mA to 1mA |                                                                             |                                      | 40     | mV      |

| December 1 Vallage                                                                 | I <sub>LOAD</sub> = 5mA                                                         |                                                                             |                                      | 440    | mV      |

| Dropout Voltage                                                                    | I <sub>LOAD</sub> = 0mA                                                         |                                                                             | 200                                  |        |         |

| PSSR                                                                               | I <sub>LOAD</sub> = 0mA                                                         |                                                                             | 5                                    |        | mV/V    |

| CRYSTAL OSCILLATOR                                                                 |                                                                                 |                                                                             |                                      |        |         |

| Maximum Output Power to Crystal                                                    |                                                                                 |                                                                             |                                      | 1      | μW      |

| PLL                                                                                |                                                                                 |                                                                             |                                      |        |         |

|                                                                                    | Power-up                                                                        |                                                                             | 3                                    |        |         |

| PLL Settling Time                                                                  | PLL_FAST transition, low to high                                                |                                                                             | 3                                    |        | me      |

| FLL Settling Time                                                                  | PLL_FAST transition, high to low                                                |                                                                             | 3                                    |        | ms      |

|                                                                                    | Mode transition, sleep to mission                                               |                                                                             | 3                                    |        |         |

| $V_{REF}$                                                                          |                                                                                 |                                                                             |                                      |        |         |

| V <sub>REF</sub> Output Voltage                                                    | T <sub>A</sub> = +22°C                                                          | 1.193                                                                       | 1.195                                | 1.197  | V       |

| V <sub>REF</sub> Output Impedance                                                  | $I_{LOAD}$ = -10 $\mu$ A to +10 $\mu$ A                                         |                                                                             |                                      | 3.2    | kΩ      |

| V <sub>REF</sub> Power Supply Sensitivity                                          | V <sub>V3P3A</sub> = 3.0V to 3.6V                                               | -1.5                                                                        |                                      | +1.5   | mV/V    |

|                                                                                    |                                                                                 | $V_{REFT} = V_{REF22} + (T-22)TC_1 + (T-22)^2TC_2$                          |                                      | V      |         |

|                                                                                    | For 71M6545T                                                                    | TC <sub>1</sub> = 1                                                         | ΓC <sub>1</sub> = 151 - 2.77 x TRIMT |        | μV/°C   |

| V <sub>REF</sub> Temperature Sensitivity (Note 1)                                  | For 71M6545HT                                                                   | TC <sub>1</sub> = 33.264 + 0.08 x TRIMT<br>+ 1.587 x (TRIMBGB -<br>TRIMBGD) |                                      |        | μV/°C   |

|                                                                                    |                                                                                 | TC <sub>2</sub> =                                                           | -0.528 - 0.0<br>TRIMT                | 0128 x | μV/°C²  |

|                                                                                    | 71M6545T (-40°C to +85°C)                                                       | -40                                                                         |                                      | +40    |         |

| V <sub>REF</sub> Error (Note 1)                                                    | 71M6545HT (-40°C to -20°C)                                                      | -16                                                                         |                                      | +16    | ppm/°C  |

|                                                                                    | 71M6545HT (-20°C to +85°C)                                                      | -10                                                                         |                                      | +10    |         |

| ADC                                                                                |                                                                                 |                                                                             |                                      |        |         |

| Recommended Input Range<br>(All Analog Inputs, Relative to<br>V <sub>V3P3A</sub> ) |                                                                                 | -250                                                                        |                                      | +250   | mV Peak |

| Recommended Input Range, IADC0-IADC1, Preamp Enabled                               |                                                                                 | -31.25                                                                      |                                      | +31.25 | mV Peak |

| Input Impedance                                                                    | f <sub>IN</sub> = 65Hz                                                          | 40                                                                          |                                      | 100    | kΩ      |

| ADC Gain Error vs. Power<br>Supply                                                 | V <sub>IN</sub> = 200mV peak, 65Hz, V <sub>V3P3A</sub> = 3.0V to 3.6V           | -30                                                                         |                                      | +70    | ppm/%   |

(Limits are production tested at  $T_A$  = +25°C. Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization.)

| PARAMETER                               | CONDITIONS                                                                                                | MIN    | TYP        | MAX   | UNITS  |

|-----------------------------------------|-----------------------------------------------------------------------------------------------------------|--------|------------|-------|--------|

| Input Offset Voltage                    | Differential or single-ended modes                                                                        | -10    |            | +10   | mV     |

| THD                                     | 250mV peak, 65Hz, 64k points, Blackman-Harris window, FIR_LEN = 2, ADC_DIV = 1, PLL_FAST = 1, MUX_DIV = 2 |        | -93        |       | dB     |

|                                         | 20mV peak, 65Hz, 64k points, Blackman-Harris window, FIR_LEN = 2, ADC_DIV = 1, PLL_FAST = 1, MUX_DIV = 2  |        | -90        |       |        |

| LSB Size                                | FIR_LEN = 2, ADC_DIV = 1, PLL_FAST = 1, MUX_<br>DIV = 2                                                   |        | 151        |       | nV     |

| Digital Full Scale                      | FIR_LEN = 2, ADC_DIV = 1, PLL_FAST = 1, MUX_<br>DIV = 2                                                   |        | ±2,097,152 |       | LSB    |

| PREAMPLIFIER                            |                                                                                                           |        |            |       |        |

| Differential Gain                       |                                                                                                           | 7.88   | 7.98       | 8.08  | V/V    |

| Gain Variation vs. Temperature          | $T_A = -40^{\circ}C \text{ to } +85^{\circ}C \text{ (Note 1)}$                                            | -30    | -10        | +15   | ppm/°C |

| Gain Variation vs. V3P3                 | V <sub>V3P3</sub> = 2.97V to 3.63V (Note 1)                                                               | -100   |            | +100  | ppm/%  |

| Phase Shift                             | (Note 1)                                                                                                  | +10    |            | +22   | m°     |

| Preamp Input Current                    |                                                                                                           | 3      | 6          | 9     | μA     |

| THD Brooms I ADC                        | V <sub>IN</sub> = 30mV                                                                                    |        | -88        |       | dB     |

| THD, Preamp + ADC                       | V <sub>IN</sub> = 15mV                                                                                    |        | -88        |       |        |

|                                         | IADC0 = IADC1 = V <sub>V3P3</sub> + 30mV                                                                  |        | -0.63      |       |        |

|                                         | $IADC0 = IADC1 = V_{V3P3} + 15mV$                                                                         |        | -0.57      |       |        |

| Preamp Input Offset Voltage             | IADC0 = IADC1 = V <sub>V3P3</sub>                                                                         |        | -0.56      |       | mV     |

|                                         | IADC0 = IADC1 = V <sub>V3P3</sub> - 15mV                                                                  |        | -0.56      |       |        |

|                                         | IADC0 = IADC1 = V <sub>V3P3</sub> - 30mV                                                                  |        | -0.55      |       |        |

| Phase Shift Over Temperature            | (Note 1)                                                                                                  | -0.03  |            | +0.03 | m°/C   |

| FLASH MEMORY                            |                                                                                                           |        |            |       |        |

| Endurance                               |                                                                                                           | 20,000 |            |       | Cycles |

| Data Retention                          | T <sub>A</sub> = +25°C                                                                                    | 100    |            |       | Years  |

| Byte Writes Between Erase<br>Operations |                                                                                                           |        |            | 2     | Cycles |

| Write Time, per Byte                    | Per 2 bytes if using SPI                                                                                  |        |            | 50    | μs     |

| Page Erase Time                         |                                                                                                           |        |            | 22    | ms     |

| Mass Erase Time                         |                                                                                                           |        |            | 22    | ms     |

(Limits are production tested at  $T_A = +25$ °C. Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization.)

|                                                                           |      | TYP | MAX  | UNITS         |

|---------------------------------------------------------------------------|------|-----|------|---------------|

| SPI                                                                       | •    |     |      |               |

| Data-to-Clock Setup Time                                                  | 10   |     |      | ns            |

| Data Hold Time From Clock                                                 | 10   |     |      | ns            |

| Output Delay, Clock to Data                                               |      |     | 40   | ns            |

| CS-to-Clock Setup Time                                                    | 10   |     |      | ns            |

| Hold Time, CS to Clock                                                    | 15   |     |      | ns            |

| Clock High Period                                                         | 40   |     |      | ns            |

| Clock Low Period                                                          | 40   |     |      | ns            |

| Clock Frequency (as a Multiple of CPU Frequency)                          |      |     | 2.0  | MHz/MHz       |

| Space Between SPI Transactions                                            | 4.5  |     |      | CPU<br>Cycles |

| EEPROM INTERFACE                                                          |      |     |      | •             |

| MPU clock = 4.9MHz, using interrupts                                      |      | 310 |      | kHz           |

| I <sup>2</sup> C SCL Frequency  MPU clock = 4.9MHz, bit-banging DIO2-DIO3 |      | 100 |      | KHZ           |

| MPU clock = 4.9MHz, PLL_FAST = 0                                          |      | 160 |      | 1.11-         |

| 3-Wire Write Clock Frequency MPU clock = 4.9MHz, PLL_FAST = 1             |      | 490 |      | kHz           |

| RESET                                                                     |      |     |      |               |

| Reset Pulse Width (Note 1)                                                | 5    |     |      | μs            |

| Reset Pulse Fall Time (Note 1)                                            |      |     | 1    | μs            |

| INTERNAL CALENDAR                                                         |      |     |      | •             |

| Year Date Range                                                           | 2000 |     | 2255 | Years         |

### **Recommended External Components**

| NAME            | FROM                 | то   | FUNCTION                                                                                                                          | VALUE      | UNITS |

|-----------------|----------------------|------|-----------------------------------------------------------------------------------------------------------------------------------|------------|-------|

| C1              | V <sub>V3P3A</sub>   | GNDA | Bypass capacitor for 3.3V supply                                                                                                  | ≥ 0.1 ±20% | μF    |

| C2              | V <sub>V3P3D</sub>   | GNDD | Bypass capacitor for 3.3V output                                                                                                  | 0.1 ±20%   | μF    |

| CSYS            | V <sub>V3P3SYS</sub> | GNDD | Bypass capacitor for V <sub>V3P3SYS</sub>                                                                                         | ≥ 1.0 ±30% | μF    |

| CVDD            | V <sub>DD</sub>      | GNDD | Bypass capacitor for V <sub>DD</sub>                                                                                              | 0.1 ±20%   | μF    |

| XTAL            | XIN                  | XOUT | 32.768 kHz crystal; electrically similar to ECS .327-12.5-17X, Vishay XT26T or Suntsu SCP6–32.768kHz TR (load capacitance 12.5pF) | 32.768     | kHz   |

| CXS<br>(Note 2) | XIN                  | GNDA | Load capacitor values for crystal depend on crystal specifications and board parasitics. Nominal                                  | 22 ±10%    | pF    |

| CXL<br>(Note 2) | XOUT                 | GNDA | values are based on 3pF allowance for the sum of board capacitance and chip capacitance.                                          | 22 ±10%    | pF    |

**Note 1:** Parameter not tested in production, guaranteed by design to six-sigma.

Note 2: If the capacitor values of CXS = 15pF and CXL = 10pF have already been installed, then changing the CXL value to 33pF and leaving CXS = 15pF would minimize rework.

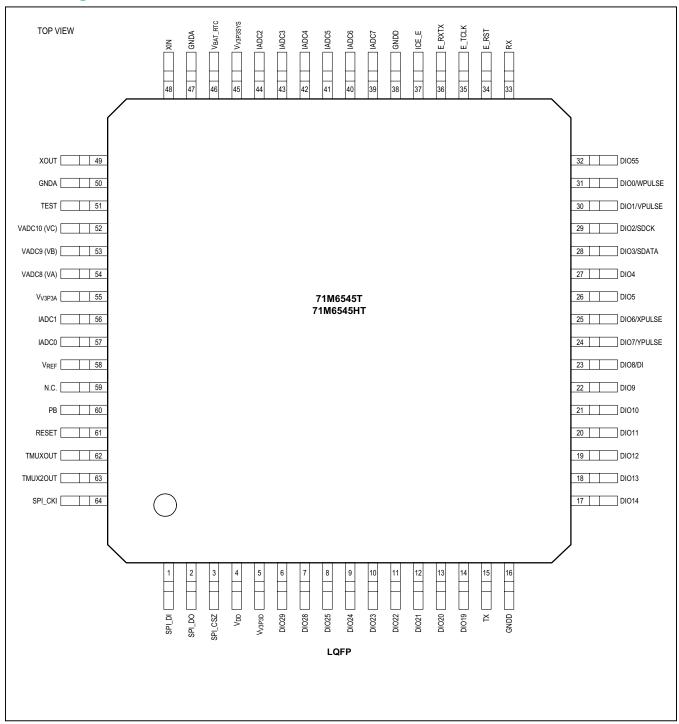

# **Pin Configuration**

# **Pin Descriptions**

| PIN        | NAME                                      | TYPE | CIRCUIT | FUNCTION                                                                                                                                                                                                                                                                                          |  |

|------------|-------------------------------------------|------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| POWER AND  | GROUND PINS                               |      |         |                                                                                                                                                                                                                                                                                                   |  |

| 47, 50     | GNDA                                      | Р    | _       | Analog Ground. This pin should be connected directly to the ground plane.                                                                                                                                                                                                                         |  |

| 16, 38     | GNDD                                      | Р    | _       | Digital Ground. This pin should be connected directly to the ground plane.                                                                                                                                                                                                                        |  |

| 55         | V <sub>V3P3A</sub>                        | Р    | _       | Analog Power Supply. A 3.3V power supply should be connected to this p $V_{V3P3A}$ must be the same voltage as $V_{V3P3SYS}$ .                                                                                                                                                                    |  |

| 45         | V <sub>V3P3SYS</sub>                      | Р    | _       | System 3.3V supply. This pin should be connected to a 3.3V power supply.                                                                                                                                                                                                                          |  |

| 5          | $V_{V3P3D}$                               | 0    | 13      | Auxiliary Voltage Output of the Chip. In mission mode, this pin is conne to $V_{V3P3SYS}$ by the internal selection switch. In BRN mode, it is internal connected to $V_{BAT}$ . $V_{V3P3D}$ is floating in LCD and sleep mode. A 0.1µF bypass capacitor to ground must be connected to this pin. |  |

| 4          | $V_{DD}$                                  | 0    | _       | Output of the 2.5V Regulator. This pin is powered in MSN and BRN modes. A 0.1µF bypass capacitor to ground should be connected to this pin.                                                                                                                                                       |  |

| 46         | V <sub>BAT_RTC</sub>                      | Р    | 12      | RTC and Oscillator Power Supply. A battery or super capacitor is to be connected between V <sub>BAT</sub> and GNDD. If no battery is used, connect V <sub>BAT</sub> _RTC to V <sub>V3P3SYS</sub> .                                                                                                |  |

| ANALOG PII | NS                                        |      |         |                                                                                                                                                                                                                                                                                                   |  |

| 57, 56     | IADC0<br>IADC1                            |      |         |                                                                                                                                                                                                                                                                                                   |  |

| 44, 43     | IADC2<br>IADC3                            |      | 6       | Differential or Single-Ended Line Current Sense Inputs. These pins are voltage inputs to the internal A/D converter. Typically, they are connected to                                                                                                                                             |  |

| 42, 41     | IADC4<br>IADC5                            |      | 6       | the outputs of current sensors. Unused pins must be tied to $V_{V3P3A}$ . Pins IADC2-IADC3, IADC4-IADC5 and IADC6-IADC7 may be configured for communication with the remote sensor interface (71M6x03).                                                                                           |  |

| 40, 39     | IADC6<br>IADC7                            |      |         |                                                                                                                                                                                                                                                                                                   |  |

| 54, 53, 52 | VADC8 (VA),<br>VADC9 (VB),<br>VADC10 (VC) | I    | 6       | Line Voltage Sense Inputs. These pins are voltage inputs to the internal A/D converter. Typically, they are connected to the outputs of resistor-dividers. Unused pins must be tied to $V_{V3P3A}$ .                                                                                              |  |

| 58         | $V_{REF}$                                 | 0    | 9       | Voltage Reference for the ADC. This pin should be left unconnected (floating).                                                                                                                                                                                                                    |  |

| 48         | XIN                                       | I    | - 8     | Crystal Inputs. A 32.768kHz crystal should be connected across these pins.  Typically, a 22pF capacitor is also connected from XIN to GNDA and a 22pF capacitor is connected from XOUT to GNDA. It is important to minimize the                                                                   |  |

| 49         | XOUT                                      | 0    |         | capacitance between these pins. See the crystal manufacturer data sheet for details. If an external clock is used, a 150mV <sub>P-P</sub> clock signal should be applied to XIN, and XOUT should be left unconnected.                                                                             |  |

# **Pin Descriptions (continued)**

| PIN         | NAME        | TYPE | CIRCUIT | FUNCTION                                                                                                                                                                                                                                                                            |  |  |

|-------------|-------------|------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| DIGITAL PII | NS          |      |         |                                                                                                                                                                                                                                                                                     |  |  |

| 31          | DIO0/WPULSE |      |         |                                                                                                                                                                                                                                                                                     |  |  |

| 30          | DIO1/VPULSE |      |         | Multiple-Use Pins. Alternative functions with proper selection of associated I/O RAM registers are: DIO0 = WPULSE                                                                                                                                                                   |  |  |

| 29          | DIO2/SDCK   |      |         |                                                                                                                                                                                                                                                                                     |  |  |

| 28          | DIO3/SDATA  |      |         |                                                                                                                                                                                                                                                                                     |  |  |

| 27          | DIO4        |      |         | DIO1 = VPULSE<br>DIO2 = SDCK                                                                                                                                                                                                                                                        |  |  |

| 26          | DIO5        |      | 2       | DIO2 = SDCK DIO3 = SDATA DIO6 = XPULSE DIO7 = YPULSE DIO8 = DI                                                                                                                                                                                                                      |  |  |

| 25          | DIO6/XPULSE | I/O  | 3       |                                                                                                                                                                                                                                                                                     |  |  |

| 24          | DIO7/YPULSE |      |         |                                                                                                                                                                                                                                                                                     |  |  |

| 23          | DIO8/DI     |      |         | DIO16 = RX3                                                                                                                                                                                                                                                                         |  |  |

| 22-17       | DIO[9:14]   |      |         | DIO17 = TX3 Unused pins must be configured as outputs or terminated to V3P3/GNDD.                                                                                                                                                                                                   |  |  |

| 14-8        | DIO[19:25]  |      |         |                                                                                                                                                                                                                                                                                     |  |  |

| 7-6         | DIO[28:29]  |      |         |                                                                                                                                                                                                                                                                                     |  |  |

| 3           | SPI_CSZ     |      |         | SPI Interface                                                                                                                                                                                                                                                                       |  |  |

| 2           | SPI_DO      | 1/0  | 3       |                                                                                                                                                                                                                                                                                     |  |  |

| 1           | SPI_DI      |      |         |                                                                                                                                                                                                                                                                                     |  |  |

| 64          | SPI_CKI     |      |         |                                                                                                                                                                                                                                                                                     |  |  |

| 32          | DIO55       | I/O  | 3       | DIO                                                                                                                                                                                                                                                                                 |  |  |

| 36          | E_RXTX      | 1/0  | 1       | Emulator Port Pins                                                                                                                                                                                                                                                                  |  |  |

| 34          | E_RST       | 1/0  | '       | Litituator Fort Filis                                                                                                                                                                                                                                                               |  |  |

| 35          | E_TCLK      | 0    | 4       |                                                                                                                                                                                                                                                                                     |  |  |

| 37          | ICE_E       | I    | 2       | ICE Enable. For production units, this pin should be pulled to GND to disable the emulator port. $ \\$                                                                                                                                                                              |  |  |

| 62          | TMUXOUT     | 0    | 4.5     | Multiplace at Clark, Output                                                                                                                                                                                                                                                         |  |  |

| 63          | TMUX2OUT    |      | 4, 5    | Multiplexer/Clock Output                                                                                                                                                                                                                                                            |  |  |

| 61          | RESET       | I    | 2       | Chip Reset. This input pin is used to reset the chip into a known state. For normal operation, this pin is pulled low. To reset the chip, this pin should be pulled high. This pin has an internal 30FA (nominal) current source pulldown No external reset circuitry is necessary. |  |  |

| 33          | RX          | I    | 3       | UART Input. If this pin is unused it must be terminated to V <sub>V3P3D</sub> or GNDD.                                                                                                                                                                                              |  |  |

| 15          | TX          | 0    | 4       | UART Output                                                                                                                                                                                                                                                                         |  |  |

| 51          | TEST        | ı    | 7       | Enables Production Test. This pin must be grounded in normal operation.                                                                                                                                                                                                             |  |  |

| 60          | PB          | 1    | 3       | Pushbutton Input. This pin must be at GNDD when not active or unused. A rising edge sets the WF_PB flag. It also causes the part to wake up if it is in SLP mode. PB does not have an internal pullup or pulldown resistor.                                                         |  |  |

| 59          | N.C.        | N.C. | _       | No Connection. Do not connect these pins.                                                                                                                                                                                                                                           |  |  |

I = Input, O = Output, P = Power

Figure 1. I/O Equivalent Circuits

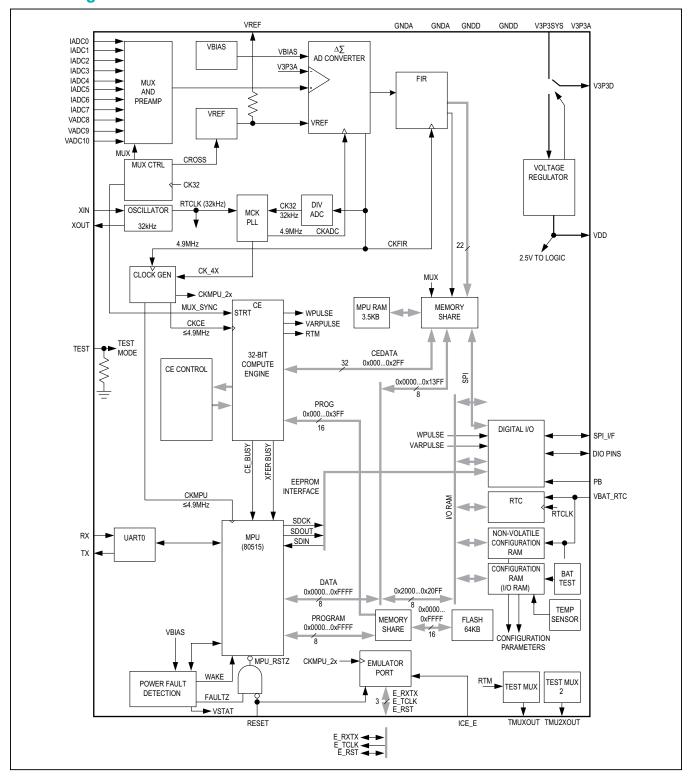

## **Block Diagram**

### **Hardware Description**

The 71M6545T/HT single-chip energy meter ICs integrate all primary functional blocks required to implement a solid-state residential electricity meter. Included on the chip are the following:

- An analog front-end (AFE) featuring a 22-bit secondorder sigma-delta ADC

- An independent 32-bit digital computation engine (CE) to implement DSP functions

- An 8051-compatible microprocessor (MPU) which executes one instruction per clock cycle (80515)

- A precision voltage reference (V<sub>REF</sub>)

- A temperature sensor for digital temperature compensation:

- Metrology digital temperature compensation (MPU)

- Automatic RTC digital temperature compensation operational in all power states

- RAM and flash memory

- A real-time clock (RTC)

- A variety of I/O pins

- · A power-failure interrupt

- A zero-crossing interrupt

- Selectable current sensor interfaces for locally-connected sensors as well as isolated sensors (i.e., using the 71M6x03 companion IC with a shunt resistor sensor)

- · Resistive shunt and current transformers are supported

Resistive shunts and current transformer (CT) current sensors are supported. Resistive shunt current sensors may be connected directly to the 71M654xT device or isolated using a companion 71M6x03 isolator IC in order to implement a variety of metering configurations. An inexpensive, small pulse transformer is used to isolate the 71M6x03 isolated sensor from the 71M654xT. The 71M654xT performs digital communications bidirectionally with the 71M6x03 and also provides power to the 71M6x03 through the isolating pulse transformer. Isolated (remote) shunt current sensors are connected to the differential input of the 71M6x03. Included on the 71M6x03 companion isolator chip are:

- · Digital isolation communications interface

- An analog front-end (AFE)

- A precision voltage reference (V<sub>REF</sub>)

- A temperature sensor (for digital temperature compensation)

- · A fully differential shunt resistor sensor input

- A preamplifier to optimize shunt current sensor performance

- Isolated power circuitry obtains dc power from pulses sent by the 71M654xT

In a typical application, the 32-bit compute engine (CE) of the 71M654xT sequentially processes the samples from the voltage inputs on analog input pins and from the external 71M6x03 isolated sensors and performs calculations to measure active energy (Wh) and reactive energy (VARh), as well as A<sup>2</sup>h, and V<sup>2</sup>h for four-quadrant metering. These measurements are then accessed by the MPU, processed further and output using the peripheral devices available to the MPU.

In addition to advanced measurement functions, the clock function allows the 71M6545T/HT to record time-of-use (TOU) metering information for multi-rate applications and to time-stamp tamper or other events.

In addition to the temperature-trimmed ultra-precision voltage reference, the on-chip digital temperature compensation mechanism includes a temperature sensor and associated controls for correction of unwanted temperature effects on measurement and RTC accuracy, e.g., to meet the requirements of ANSI and IEC standards. Temperature-dependent external components such as crystal oscillator, resistive shunts, current transformers (CTs) and their corresponding signal conditioning circuits can be characterized and their correction factors can be programmed to produce electricity meters with exceptional accuracy over the industrial temperature range.

See the Block Diagram.

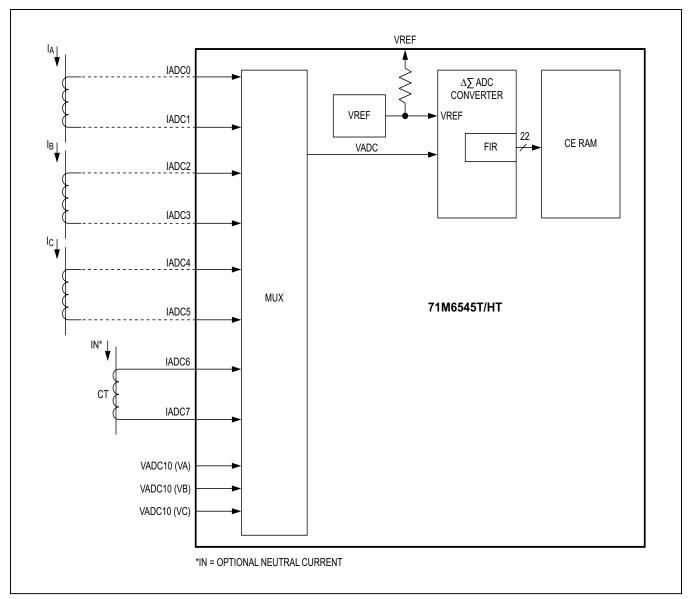

### **Analog Front-End (AFE)**

The AFE functions as a data acquisition system, controlled by the MPU. When used with locally connected sensors, as shown in Figure 2, the analog input signals (IADC0-IADC7, VADC8-VADC10) are multiplexed to the ADC input and sampled by the ADC.

The ADC output is decimated by the FIR filter and stored in CE RAM where it can be accessed and processed by the CE.

When remote isolated sensors are connected to the 71M6545T/HT using 71M6x03 remote sensor interfaces, the input multiplexer is bypassed. Instead, the extracted modulator bit stream is passed directly to a dedicated decimation filter. The output of the decimation filter is then directly stored in the appropriate CE RAM location without making use of a multiplexer cycle.

Figure 2. 71M6545T/HT Operating with Local Sensors

### **Signal Input Pins**

The 71M6545T/HT features eleven ADC inputs.

IADC0-IADC7 are intended for use as current sensor inputs. These eight current sensor inputs can be configured as four single-ended inputs, or (more frequently) can be paired to form four differential inputs. For best performance, it is recommended to configure the current sensor inputs as differential inputs. The first differential input (IADC0-IADC1) features a preamplifier with a selectable gain of 1 or 8, and is intended for direct connection to a shunt resistor sensor, and can also be used with a current transformer (CT). The remaining differential pairs may be used with CTs, or may be enabled to interface to a remote 71M6x03 isolated current sensor providing isolation for a shunt resistor sensor using a low cost pulse transformer.

The remaining inputs (VADC8-VADC10) are single-ended and sense line voltage. These single-ended inputs are referenced to the  $V_{V3P3A}$  pin.

All analog signal input pins measure voltage. In the case of shunt current sensors, currents are sensed as a voltage drop in the shunt resistor sensor. Referring to Figure 2, shunt sensors can be connected directly to the 71M654xT (referred to as a 'local' shunt sensor) or connected through an isolated 71M6x03 (referred to as a 'remote' shunt sensor) (Figure 3). In the case of current transformers, the current is measured as a voltage across a burden resistor that is connected to the secondary winding of the CT. Meanwhile, line voltages are sensed through resistive voltage dividers.

Figure 3. 71M6545T/HT Operating with Remote Sensor for Neutral Current

Pins IADC0-IADC1 can be programmed individually to be differential or single-ended. For most applications IADC0-IADC1 are configured as a differential input to work with a shunt or CT directly interfaced to the IADC0-IADC1 differential input with the appropriate external signal conditioning components.

The performance of the IADC0-IADC1 pins can be enhanced by enabling a preamplifier with a fixed gain of 8. When the PRE\_E bit = 1, IADC0-IADC1 become the inputs to the 8x preamplifier, and the output of this amplifier is supplied to the multiplexer. The 8x amplification is useful when current sensors with low sensitivity, such as shunt resistors, are used. With PRE\_E set, the IADC0-IADC1 input signal amplitude is restricted to 31.25 mV peak.

When shunt resistors are used as current sense elements on all current inputs, the IADC0-IADC1 pins are configured for differential mode to interface to a local shunt by setting the DIFFA\_E control bit. Meanwhile, the IADC2-IADC7 pins are re-configured as digital balanced pair to communicate with a 71M6x03 isolated sensor interface by setting the RMT\_E control bit. The 71M6x03 communicates with the 71M654xT using a bidirectional digital data stream through an isolating low-cost pulse transformer. The 71M654xT also supplies power to the 71M6x03 through the isolating transformer.

When using current transformers the IADC2-IADC7 pins are configured as local analog inputs (RMT\_E = 0). The IADC0-IADC1 pins cannot be configured as a remote sensor interface.

### **Input Multiplexer**

When operating with local sensors, the input multiplexer sequentially applies the input signals from the analog input pins to the input of the ADC. One complete sampling sequence is called a multiplexer frame. The multiplexer of the 71M6545T/HT can select up to seven input signals (three voltage inputs and four current inputs) per multiplexer frame. The multiplexer always starts at state 1 and proceeds until as many states as determined by MUX\_DIV[3:0] have been converted.

The 71M6545T/HT requires CE code that is written for the specific application. Moreover, each CE code requires specific AFE and MUX settings in order to function properly. Contact Maxim Integrated for specific information about alternative CE codes.

For a polyphase configuration with neutral current sensing using shunt resistor current sensors and the 71M6xx3 isolated sensors, as shown in <a href="Figure 3">Figure 3</a>, the IADC0-IADC1 input must be configured as a differential input, to be connected to a local shunt. The local shunt connected to the IADC0-IADC1 input is used to sense the Neutral current. The voltage sensors (VADC8-VADC10) are also directly connected to the 71M6545T/HT and are also routed though the multiplexer. Meanwhile, the IADC2-IADC7 current inputs are configured as remote sensor digital interfaces and the corresponding samples are not routed through the multiplexer.

For a polyphase configuration with optional neutral current sensing using Current Transformer (CTs) sensors, all four current sensor inputs must be configured as differential inputs. IADC2-IADC3 is connected to phase A, IADC4-IADC5 is connected to phase B, and IADC6-IADC7 is connected to phase C. The IADC0-IADC1 current sensor input is optionally used to sense the Neutral current for anti-tampering purposes. The voltage sensors (VADC8-VADC10), typically resistive dividers, are directly connected to the 71M6545T/HT. No 71M6xx3 isolated sensors are used in this configuration and all signals are routed though the multiplexer.

The multiplexer sequence shown in Figure 4 corresponds to the configuration shown in Figure 3. The frame duration is 13 CK32 cycles (where CK32 = 32,768Hz), therefore, the resulting sample rate is 32,768Hz/13 = 2,520.6Hz. Note that Figure 4 only shows the currents that pass through the 71M6545T/HT multiplexer, and does not show the currents that are copied directly into CE RAM from the remote sensors (see Figure 3), which are sampled during the second half of the multiplexer frame. The two unused conversion slots shown are necessary to produce the desired 2,520.6Hz sample rate.