Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

CMOS TRIPLE BUS SyncFIFO™ WITH BUS-MATCHING 256 x 36 x 2, 512 x 36 x 2 1,024 x 36 x 2

IDT723626 IDT723636 IDT723646

## **FEATURES:**

. Memory storage capacity:

IDT723626 - 256 x 36 x 2 IDT723636 - 512 x 36 x 2 IDT723646 - 1,024 x 36 x 2

- Clock frequencies up to 67 MHz (10ns access time)

- Two independent FIFOs buffer data between one bidirectional 36-bit port and two unidirectional 18-bit ports (Port C receives and Port B transmits)

- 18-bit (word) and 9-bit (byte) bus sizing of 18 bits (word) on Ports B and C

- Select IDT Standard timing (using EFA, EFB, FFA, and FFC flag functions) or First Word Fall Through Timing (using ORA, ORB, IRA, and IRC flag functions)

- Programmable Almost-Empty and Almost-Full flags; each has three default offsets (8, 16 and 64)

- Serial or parallel programming of partial flags

- . Big- or Little-Endian format for word and byte bus sizes

- Master Reset clears data and configures FIFO, Partial Reset clears data but retains configuration settings

- . Mailbox bypass registers for each FIFO

- Free-running CLKA, CLKB and CLKC may be asynchronous or coincident (simultaneous reading and writing of data on a single clock edge is permitted)

- Auto power down minimizes power dissipation

- Available in a space-saving 128-pin Thin Quad Flatpack (TQFP)

- . Green parts available, see ordering information

## **DESCRIPTION:**

The IDT723626/723636/723646 is a monolithic, high-speed, low-power, CMOS Triple Bus synchronous (clocked) FIFO memory which supports clock frequencies up to 67 MHz and has read access times as fast as 10 ns. Two

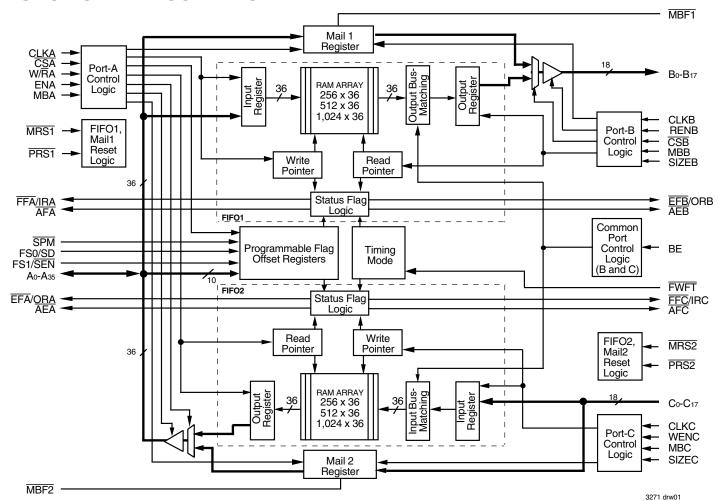

## **FUNCTIONAL BLOCK DIAGRAM**

IDT and the IDT logo are registered trademarks of Integrated Device Technology, Inc. The SyncFIFO is a trademark of Integrated Device Technology, Inc. The SyncFIFO is a trademark of Integrated Device Technology, Inc. The SyncFIFO is a trademark of Integrated Device Technology, Inc. The SyncFIFO is a trademark of Integrated Device Technology, Inc. The SyncFIFO is a trademark of Integrated Device Technology, Inc. The SyncFIFO is a trademark of Integrated Device Technology, Inc. The SyncFIFO is a trademark of Integrated Device Technology, Inc. The SyncFIFO is a trademark of Integrated Device Technology, Inc. The SyncFIFO is a trademark of Integrated Device Technology, Inc. The SyncFIFO is a trademark of Integrated Device Technology, Inc. The SyncFIFO is a trademark of Integrated Device Technology, Inc. The SyncFIFO is a trademark of Integrated Device Technology, Inc. The SyncFIFO is a trademark of Integrated Device Technology, Inc. The SyncFIFO is a trademark of Integrated Device Technology, Inc. The SyncFIFO is a trademark of Integrated Device Technology, Inc. The SyncFIFO is a trademark of Integrated Device Technology, Inc. The SyncFIFO is a trademark of Integrated Device Technology, Inc. The SyncFIFO is a trademark of Integrated Device Technology, Inc. The SyncFIFO is a trademark of Integrated Device Technology, Inc. The SyncFIFO is a trademark of Integrated Device Technology, Inc. The SyncFIFO is a trademark of Integrated Device Technology, Inc. The SyncFIFO is a trademark of Integrated Device Technology, Inc. The SyncFIFO is a trademark of Integrated Device Technology, Inc. The SyncFIFO is a trademark of Integrated Device Technology, Inc. The SyncFIFO is a trademark of Integrated Device Technology, Inc. The SyncFIFO is a trademark of Integrated Device Technology, Inc. The SyncFIFO is a trademark of Integrated Device Technology, Inc. The SyncFIFO is a trademark of Integrated Device Technology, Inc. The SyncFIFO is a trademark of Integrated Device Technology, Inc. The SyncFIFO is a trademark of Integrated Dev

**COMMERCIAL TEMPERATURE RANGE**

**JULY 2014**

## **DESCRIPTION (CONTINUED)**

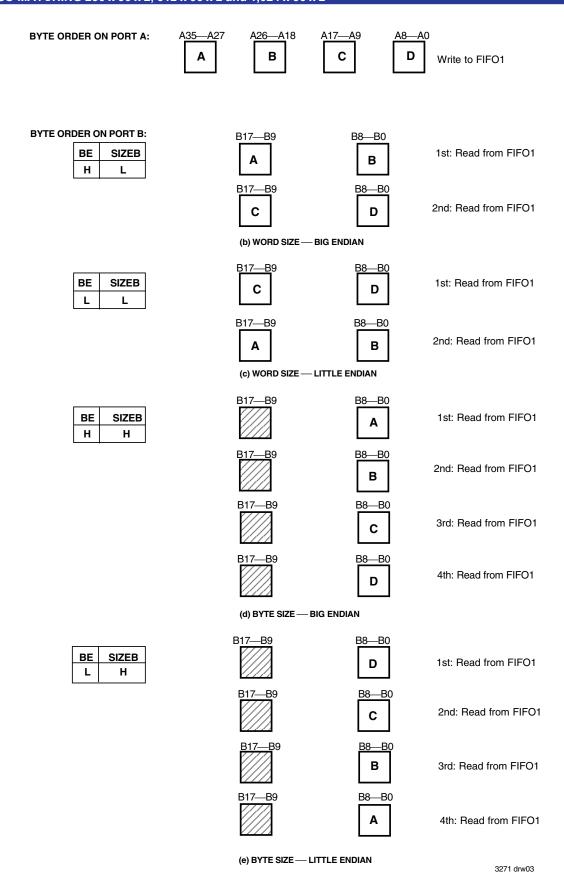

independent 256/512/1,024 x 36 dual-port SRAM FIFOs on board each chip buffer data between a bidirectional 36-bit bus (Port A) and two unidirectional 18-bit buses (Port B transmits data, Port C receives data.) FIFO data can be read out of Port B and written into Port C using either 18-bit or 9-bit formats with a choice of Big- or Little-Endian configurations.

These devices are a synchronous (clocked) FIFO, meaning each port employs a synchronous interface. All data transfers through a port are gated to the LOW-to-HIGH transition of a port clock by enable signals. The clocks for each port are independent of one another and can be asynchronous or coincident. The enables for each port are arranged to provide a simple

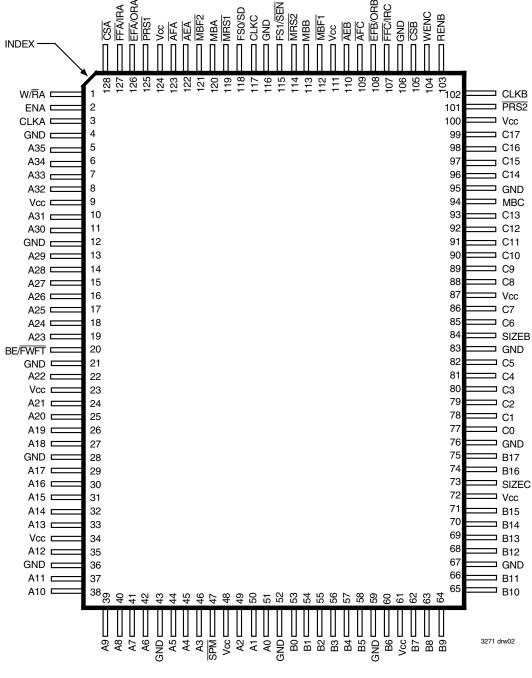

## PIN CONFIGURATION

TQFP (PK128-1, order code: PF)

TOP VIEW

bidirectional interface between microprocessors and/or buses with synchronous control.

Communication between each port may bypass the FIFOs via two mailbox registers. The mailbox registers' width matches the selected bus width of ports B and C. Each mailbox register has a flag ( $\overline{\text{MBF1}}$  and  $\overline{\text{MBF2}}$ ) to signal when new mail has been stored.

Two kinds of reset are available on these FIFOs: Master Reset and Partial Reset. Master Reset initializes the read and write pointers to the first location of the memory array and selects serial flag programming, parallel flag programming, or one of three possible default flag offset settings, 8, 16 or 64. Each FIFO has its own, independent Master Reset pin,  $\overline{\text{MRS1}}$  and  $\overline{\text{MRS2}}$ .

Partial Reset also sets the read and write pointers to the first location of the memory. Unlike Master Reset, any settings existing prior to Partial Reset (i.e., programming method and partial flag default offsets) are retained. Partial Reset is useful since it permits flushing of the FIFO memory without changing any configuration settings. Each FIFO has its own, independent Partial Reset pin, PRS1 and PRS2.

These devices have two modes of operation: In the *IDT Standard mode*, the first word written to an empty FIFO is deposited into the memory array. A read operation is required to access that word (along with all other words residing in memory). In the *First Word Fall Through mode* (FWFT), the first word written to an empty FIFO appears automatically on the outputs, no read operation required (Nevertheless, accessing subsequent words does necessitate a formal read request). The state of the BE/FWFT pin during Master Reset determines the mode in use.

Each FIFO has a combined Empty/Output Ready Flag (EFA/ORA and EFB/ORB) and a combined Full/Input Ready Flag (FFA/IRA and FFC/IRC). The EF and FF functions are selected in the IDT Standard mode. EF indicates whether or not the FIFO memory is empty. FF shows whether the memory is

full or not. The IR and OR functions are selected in the First Word Fall Through mode. IR indicates whether or not the FIFO has available memory locations. OR shows whether the FIFO has data available for reading or not. It marks the presence of valid data on the outputs.

Each FIFO has a programmable Almost-Empty flag (ĀEĀ and ĀEB) and a programmable Almost-Full flag (ĀFĀ and ĀFC). ĀEĀ and ĀEB indicate when a selected number of words remain in the FIFO memory. ĀFĀ and ĀFC indicate when the FIFO contains more than a selected number of words.

FFA/IRA, FFC/IRC, ĀFA and ĀFC are two-stage synchronized to the Port Clock that writes data into its array. ĒFA/ORA, ĒFB/ORB, ĀEĀ, and ĀEB are two-stage synchronized to the Port Clock that reads data from its array. Programmable offsets for ĀEĀ, ĀEB, ĀFĀ, ĀFC are loaded in parallel using Port A or in serial via the SD input. The Serial Programming Mode pin (\$\overline{SPM}\$) makes this selection. Three default offset settings are also provided. The ĀEĀ and ĀEB threshold can be set at 8, 16 or 64 locations from the empty boundary and the ĀFĀ and ĀFC threshold can be set at 8, 16 or 64 locations from the full boundary. All these choices are made using the FS0 and FS1 inputs during Master Reset.

Two or more FIFOs may be used in parallel to create wider data paths. Such a width expansion requires no additional, external components. Furthermore, two IDT723626/723636/723646 FIFOs can be combined with unidirectional FIFOs capable of First Word Fall Through timing (i.e. the SuperSync FIFO family) to form a depth expansion.

If, at any time, the FIFO is not actively performing a function, the chip will automatically power down. During the power down state, supply current consumption (ICC) is at a minimum. Initiating any operation (by activating control inputs) will immediately take the device out of the power down state.

The IDT723626/723636/723646s are characterized for operation from  $0^{\circ}\text{C}$  to  $70^{\circ}\text{C}$ . They are fabricated using high speed, submicron CMOS technology.

## **PIN DESCRIPTIONS**

| Symbol  | Name                                               | I/O | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|---------|----------------------------------------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A0-A35  | Port A Data                                        | I/O | 36-bit bidirectional data port for side A.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| ĀĒĀ     | Port A Almost-Empty<br>Flag                        | 0   | Programmable Almost-Empty flag synchronized to CLKA. It is LOW when the number of words in FIFO2 is less than or equal to the value in the Almost-Empty A Offset register, X2.                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| ĀĒB     | Port B Almost-Empty<br>Flag                        | 0   | Programmable Almost-Empty flag synchronized to CLKB. It is LOW when the number of words in FIFO1 is less than or equal to the value in the Almost-Empty B Offset register, X1.                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| ĀFĀ     | Port A Almost-Full<br>Flag                         | 0   | Programmable Almost-Full flag synchronized to CLKA. It is LOW when the number of empty locations in FIFO1 is less than or equal to the value in the Almost-Full A Offset register, Y1.                                                                                                                                                                                                                                                                                                                                                                                                                              |

| ĀFC     | Port C Almost-Full<br>Flag                         | 0   | Programmable Almost-Full flag synchronized to CLKC. It is LOW when the number of empty locations in FIFO2 is less than or equal to the value in the Almost-Full C Offset register, Y2.                                                                                                                                                                                                                                                                                                                                                                                                                              |

| B0-B17  | Port B Data                                        | 0   | 18-bit output data port for side B.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| BE/FWFT | Big-Endian/<br>FirstWord<br>Fall Through<br>Select | I   | This is a dual purpose pin. During Master Reset, a HIGH on BE will select Big-Endian operation. In this case, depending on the bus size, the <i>most</i> significant byte or word on Port A is read from Port B first (A-to-B data flow) or is written to Port C first (C-to-A data flow). A LOW on BE will select Little-Endian operation. In this case, the <i>least</i> significant byte or word on Port A is read from Port B first (A-to-B data flow) or is written to Port C first (C-to-A data flow).  After Master Reset, this pin selects the timing mode. A HIGH on FWFT selects IDT Standard mode, a LOW |

|         |                                                    |     | selects First Word Fall Through mode. Once the timing mode has been selected, the level on FWFT must be static throughout device operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| C0-C17  | Port C Data                                        | I   | 18-bit input data port for side C.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| CLKA    | Port A Clock                                       | I   | CLKA is a continuous clock that synchronizes all data transfers through Port A and can be asynchronous or coincident to CLKB. FFA/IRA, EFA/ORA, ĀFĀ, and ĀEĀ are all synchronized to the LOW-to-HIGH transition of CLKA.                                                                                                                                                                                                                                                                                                                                                                                            |

| CLKB    | Port B Clock                                       | I   | CLKB is a continuous clock that synchronizes all data transfers through Port B and can be asynchronous or coincident to CLKA. <u>EFB</u> /ORB and <u>AEB</u> are synchronized to the LOW-to-HIGH transition of CLKB.                                                                                                                                                                                                                                                                                                                                                                                                |

| CLKC    | Port C Clock                                       | ı   | CLKC is a continuous clock that synchronizes all data transfers through Port C and can be asynchronous or coincident to CLKA. FFC/IRC and AFC are synchronized to the LOW-to-HIGH transition of CLKC.                                                                                                                                                                                                                                                                                                                                                                                                               |

| CSA     | Port A Chip Select                                 | I   | CSA must be LOW to enable to LOW-to-HIGH transition of CLKA to read or write on Port A. The A0-A35 outputs are in the high-impedance state when CSA is HIGH.                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| CSB     | Port B Chip Select                                 | I   | CSB must be LOW to enable a LOW-to-HIGH transition of CLKB to read data on Port B. The B0-B17 outputs are in the high-impedance state when CSB is HIGH.                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| EFA/ORA | Port A Empty/<br>Output Ready Flag                 | 0   | This is a dual function pin. In the IDT Standard mode, the EFA function is selected. EFA indicates whether or not the FIFO2 memory is empty. In the FWFT mode, the ORA function is selected. ORA indicates the presence of valid data on the A0-A35 outputs, available for reading. EFA/ORA is synchronized to the LOW-to-HIGH transition of CLKA.                                                                                                                                                                                                                                                                  |

| EFB/ORB | Port B Empty/<br>Output Ready Flag                 | 0   | This is a dual function pin. In the IDT Standard mode, the $\overline{EFB}$ function is selected. $\overline{EFB}$ indicates whether or not the FIFO1 memory is empty. In the FWFT mode, the ORB function is selected. ORB indicates the presence of valid data on the B0-B17 outputs, available for reading. $\overline{EFB}$ /ORB is synchronized to the LOW-to-HIGH transition of CLKB.                                                                                                                                                                                                                          |

| ENA     | Port A Enable                                      | I   | ENA must be HIGH to enable a LOW-to-HIGH transition of CLKA to read or write data on Port A.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| FFA/IRA | Port A Full/<br>Input Ready Flag                   | 0   | This is a dual function pin. In the IDT Standard mode, the FFA function is selected. FFA indicates whether or not the FIFO1 memory is full. In the FWFT mode, the IRA function is selected. IRA indicates whether or not there is space available for writing to the FIFO1 memory. FFA/IRA is synchronized to the LOW-to-HIGH transition of CLKA.                                                                                                                                                                                                                                                                   |

| FFC/IRC | Port C Full/<br>Input Ready Flag                   | 0   | This is a dual function pin. In the IDT Standard mode, the FFC function is selected. FFC indicates whether or not the FIFO2 memory is full. In the FWFT mode, the IRC function is selected. IRC indicates whether or not there is space available for writing to the FIFO2 memory. FFC/IRC is synchronized to the LOW-to-HIGH transition of CLKC.                                                                                                                                                                                                                                                                   |

## PIN DESCRIPTIONS (CONTINUED)

| g. During Master Reset,<br>nree Offset register<br>6, or 64), parallel load                                        |

|--------------------------------------------------------------------------------------------------------------------|

| n enable synchronous to<br>bead the bit present on<br>set registers is 32 for the<br>he Y-register (Y1) MSB        |

| /hen the A0-A35 outputs<br>W level selects FIFO2                                                                   |

| B0-B17 outputs are<br>evel selects FIFO1 output                                                                    |

| nust be HIGH during                                                                                                |

| ster. Writes to the mail1<br>on of CLKB when a<br>r Partial Reset of FIFO1.                                        |

| ster. Writes to the mail2<br>on of CLKA when a Port<br>tial Reset of FIFO2.                                        |

| nory and sets the Port B<br>g method (serial or parallel)<br>s ports B and C for bus size<br>H transitions of CLKB |

| y and sets the Port A output<br>1, selects the programming<br>-HIGH transitions of CLKA                            |

| nory and sets the Port B<br>rrangement, programming                                                                |

| nory and sets the Port A<br>rrangement, programming                                                                |

| B.                                                                                                                 |

| e. A LOW on this pin<br>d endian arrangement for                                                                   |

| ze. A LOW on this pin<br>d endian arrangement for                                                                  |

| ects parallel programming                                                                                          |

| tC.                                                                                                                |

| W-to-HIGH transition of                                                                                            |

| ze. And en                                                                                                         |

<sup>1.</sup> SIZEB, SIZEC and \$\overline{SPM}\$ are not TTL compatible. These inputs should be tied to GND or VCC.

## ABSOLUTE MAXIMUM RATINGS OVER OPERATING FREE-AIR TEMPERATURE RANGE (Unless otherwise noted)<sup>(1)</sup>

| Symbol            | Rating                                      | Commercial      | Unit |

|-------------------|---------------------------------------------|-----------------|------|

| Vcc               | Supply Voltage Range                        | –0.5 to 7       | V    |

| VI <sup>(2)</sup> | Input Voltage Range                         | -0.5 to Vcc+0.5 | V    |

| Vo <sup>(2)</sup> | Output Voltage Range                        | -0.5 to Vcc+0.5 | V    |

| lık               | Input Clamp Current (VI < 0 or VI > VCC)    | ±20             | mA   |

| Іок               | Output Clamp Current (Vo = < 0 or Vo > Vcc) | ±50             | mA   |

| Іоит              | Continuous Output Current (Vo = 0 to Vcc)   | ±50             | mA   |

| Icc               | Continuous Current Through Vcc or GND       | ±400            | mA   |

| Tstg              | Storage Temperature Range                   | -65 to 150      | °C   |

#### NOTES:

## RECOMMENDED OPERATING CONDITIONS

| Symbol | Parameter                                   | Min. | Тур. | Max. | Unit |

|--------|---------------------------------------------|------|------|------|------|

| Vcc    | Supply Voltage (Commercial)                 | 4.5  | 5.0  | 5.5  | ٧    |

| VIH    | High-Level Input Voltage (Commercial)       | 2    | _    |      | V    |

| VIL    | Low-Level Input Voltage (Commercial)        |      | _    | 0.8  | V    |

| Іон    | High-Level Output Current (Commercial)      | _    | _    | -4   | mA   |

| lol    | Low-Level Output Current (Commercial)       | -    | _    | 8    | mA   |

| TA     | Operating Free-Air Temperature (Commercial) | 0    |      | 70   | °C   |

ELECTRICAL CHARACTERISTICS OVER RECOMMENDED OPERATING FREE-AIR TEMPERATURE RANGE (Unless otherwise noted)

|                     |                                                    |             | C                    |      |                     |      |      |

|---------------------|----------------------------------------------------|-------------|----------------------|------|---------------------|------|------|

| Symbol              | Parameter                                          | Test        | Conditions           | Min. | Typ. <sup>(1)</sup> | Max. | Unit |

| Vон                 | Output Logic "1" Voltage                           | Vcc = 4.5V, | Iон = –4 mA          | 2.4  | _                   | _    | V    |

| Vol                 | Output Logic "0" Voltage                           | Vcc = 4.5V, | IoL = 8 mA           | _    | _                   | 0.5  | V    |

| ILI                 | InputLeakage Current (Any Input)                   | Vcc = 5.5V, | VI = Vcc or 0        | _    | _                   | ±10  | μA   |

| ILO                 | Output Leakage Current                             | Vcc = 5.5V, | Vo = Vcc or 0        | _    | _                   | ±10  | μA   |

| ICC2 <sup>(2)</sup> | Standby Current (with CLKA, CLKB and CLKC running) | Vcc = 5.5V, | VI = Vcc - 0.2V or 0 | _    | _                   | 8    | mA   |

| ICC3 <sup>(2)</sup> | Standby Current (no clocks running)                | Vcc = 5.5V, | Vi = Vcc - 0.2V or 0 | _    | _                   | 1    | mA   |

| CIN <sup>(3)</sup>  | Input Capacitance                                  | Vı = 0,     | f = 1 MHz            | _    | 4                   | _    | рF   |

| Cout <sup>(3)</sup> | Output Capacitance                                 | Vo = 0,     | f = 1 MHZ            | -    | 8                   | _    | pF   |

- 1. All typical values are at Vcc = 5V, TA = 25°C.

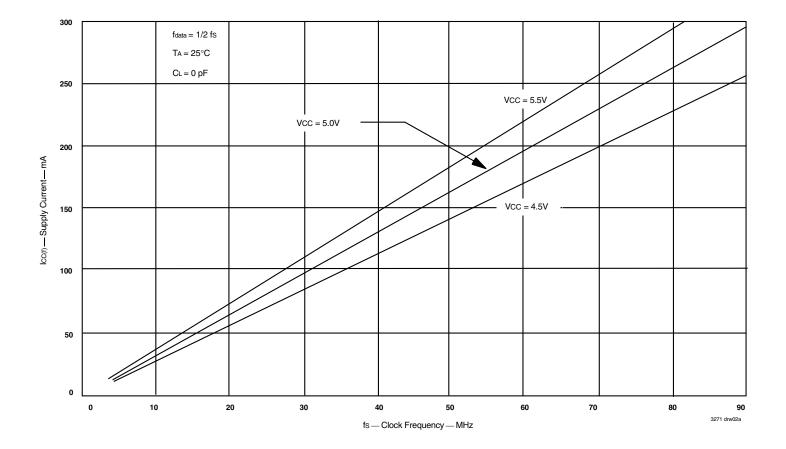

- 2. For additional lcc information, see Figure 1, Typical Characteristics: Supply Current (Icc) vs. Clock Frequency (fs).

- 3. Characterized values, not currently tested.

<sup>1.</sup> Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

<sup>2.</sup> The input and output voltage ratings may be exceeded provided the input and output current ratings are observed.

## DETERMINING ACTIVE CURRENT CONSUMPTION AND POWER DISSIPATION

The Icc(f) current for the graph in Figure 1 was taken while simultaneously reading and writing a FIFO on the IDT723626/723636/723646 with CLKA, CLKB and CLKC set to fs. All data inputs and data outputs change state during each clock cycle to consume the highest supply current. Data outputs were disconnected to normalize the graph to a zero capacitance load. Once the capacitance load per data-output channel and the number of IDT723626/723636/723646 inputs driven by TTL HIGH levels are known, the power dissipation can be calculated with the equation below.

## **CALCULATING POWER DISSIPATION**

With ICC(f) taken from Figure 1, the maximum power dissipation (PT) of these FIFOs may be calculated by:

PT = VCC x [ICC(f) + (N x

$$\triangle$$

ICC x dc)] +  $\Sigma$ (CL x VCC<sup>2</sup> X fo)

Ν

where:

N = number of inputs driven by TTL levels

ΔICC = increase in power supply current for each input at a TTL HIGH level

dc = duty cycle of inputs at a TTL HIGH level of 3.4V

CL = output capacitance load fo = switching frequency of an output

Figure 1. Typical Characteristics: Supply Current (ICC) vs. Clock Frequency (fs)

## TIMING REQUIREMENTS OVER RECOMMENDED RANGES OF SUPPLY VOLTAGE AND OPERATING FREE-AIR TEMPERATURE

(Commercial: VCC =  $5.0V \pm 10\%$ , TA =  $0^{\circ}$ C to  $+70^{\circ}$ C)

|              |                                                                                                                                             | Com<br>IDT72<br>IDT72<br>IDT72 |      |      |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|------|------|

| Symbol       | Parameter                                                                                                                                   | Min.                           | Max. | Unit |

| fs           | Clock Frequency, CLKA, CLKB, or CLKC                                                                                                        |                                | 66.7 | MHz  |

| tclk         | Clock Cycle Time, CLKA, CLKB, or CLKC                                                                                                       | 15                             | _    | ns   |

| tclkh        | Pulse Duration, CLKA, CLKB, or CLKC HIGH                                                                                                    | 6                              |      | ns   |

| tclkl        | Pulse Duration, CLKA, CLKB, OR CLKC LOW                                                                                                     | 6                              | _    | ns   |

| tos          | Setup Time, A0-A35 before CLKA↑ and C0-C17 before CLKC↑                                                                                     | 4                              | _    | ns   |

| tENS1        | Setup Time, CSA and W/RA before CLKA↑; CSB before CLKB↑                                                                                     | 4.5                            | _    | ns   |

| tENS2        | Setup Time, ENA and MBA before CLKA1; RENB and MBB before CLKB1; WENC and MBC before CLKC1                                                  | 4.5                            | _    | ns   |

| trsts        | Setup Time, MRS1, MRS2, PRS1, or PRS2 LOW before CLKA↑ or CLKB↑(1)                                                                          | 5                              | _    | ns   |

| trss         | Setup Time, FS0 and FS1 before MRS1 and MRS2 HIGH                                                                                           | 7.5                            | _    | ns   |

| tBES         | Setup Time, BE/FWFT before MRS1 and MRS2 HIGH                                                                                               | 7.5                            | _    | ns   |

| tspms        | Setup Time, SPM before MRS1 and MRS2 HIGH                                                                                                   | 7.5                            | _    | ns   |

| tsds         | Setup Time, FS0/SD before CLKA↑                                                                                                             | 4                              | _    | ns   |

| tsens        | Setup Time, FS1/SEN before CLKA↑                                                                                                            | 4                              | _    | ns   |

| trws         | Setup Time, BE/FWFT before CLKA↑                                                                                                            | 0                              | _    | ns   |

| <b>t</b> DH  | Hold Time, A0-A35 after CLKA↑ and C0-C17 after CLKC↑                                                                                        | 1                              | _    | ns   |

| tenh         | Hold Time, CSA, W/RA, ENA, and MBA after CLKA↑; CSB, RENB, and MBB after CLKB↑; WENC and MBC after CLKC↑                                    | 1                              | _    | ns   |

| trsth        | Hold Time, MRS1, MRS2, PRS1 or PRS2 LOW after CLKA↑ or CLKB↑(1)                                                                             | 4                              | _    | ns   |

| tFSH         | Hold Time, FS0 and FS1 after MRS1 and MRS2 HIGH                                                                                             | 2                              | _    | ns   |

| <b>t</b> BEH | Hold Time, BE/FWFT after MRS1 and MRS2 HIGH                                                                                                 | 2                              | _    | ns   |

| tspmh        | Hold Time, SPM after MRS1 and MRS2 HIGH                                                                                                     | 2                              | _    | ns   |

| tsdh         | Hold Time, FS0/SD after CLKA↑                                                                                                               | 1                              | _    | ns   |

| tsenh        | Hold Time, FS1/ <del>SEN</del> HIGH after CLKA↑                                                                                             | 1                              | _    | ns   |

| tsph         | Hold Time, FS1/SEN HIGH after MRS1 and MRS2 HIGH                                                                                            | 2                              |      | ns   |

| tskew1(2)    | Skew Time, between CLKA Tand CLKB for EFB/ORB and FFA/IRA; between CLKA and CLKC for EFA/ORA and FFC/IRC                                    | 7.5                            | _    | ns   |

| tskew2(2,3)  | Skew Time, between CLKA <sup>↑</sup> and CLKB <sup>↑</sup> for AEB and AFA; between CLKA <sup>↑</sup> and CLKC <sup>↑</sup> for AEA and AFC | 12                             | _    | ns   |

- 1. Requirement to count the clock edge as one of at least four needed to reset a FIFO.

- 2. Skew time is not a timing constraint for proper device operation and is only included to illustrate the timing relationship among CLKA cycle, CLKB cycle, and CLKC cycle.

- 3. Design simulated, not tested (typical values).

# SWITCHING CHARACTERISTICS OVER RECOMMENDED RANGES OF SUPPLY VOLTAGE AND OPERATING FREE-AIR TEMPERATURE, CL = 30pF

(Commercial:  $VCC = 5.0V \pm 10\%$ ,  $TA = 0^{\circ}C$  to  $+70^{\circ}C$ )

|        |                                                                                                                                                                  | Com<br>IDT72<br>IDT72<br>IDT72 |      |      |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|------|------|

| Symbol | Parameter                                                                                                                                                        | Min.                           | Max. | Unit |

| tA     | Access Time, CLKA↑ to A0-A35 and CLKB↑ to B0-B17                                                                                                                 | 2                              | 10   | ns   |

| twff   | Propagation Delay Time, CLKA↑ to FFA/IRA and CLKC↑ to FFC/IRC                                                                                                    | 2                              | 8    | ns   |

| tref   | Propagation Delay Time, CLKA↑ to EFA/ORA and CLKB↑ to EFB/ORB                                                                                                    | 1                              | 8    | ns   |

| tPAE   | Propagation Delay Time, CLKA↑ to AEA and CLKB↑ to AEB                                                                                                            | 1                              | 8    | ns   |

| tPAF   | Propagation Delay Time, CLKA↑ to AFA and CLKC↑ to AFC                                                                                                            | 1                              | 8    | ns   |

| tPMF   | Propagation Delay Time, CLKA↑ to MBF1 LOW or MBF2 HIGH, CLKB↑ to MBF1 HIGH, and CLKC↑ to MBF2 LOW                                                                | 0                              | 8    | ns   |

| tPMR   | Propagation Delay Time, CLKA↑ to B0-B17 <sup>(1)</sup> and CLKC↑ to A0-A35 <sup>(2)</sup>                                                                        | 2                              | 10   | ns   |

| tMDV   | Propagation Delay Time, MBA to A0-A35 valid and MBB to B0-B17 valid                                                                                              | 2                              | 10   | ns   |

| tRSF   | Propagation Delay Time, MRS1 or PRS1 LOW to AEB LOW, AFA HIGH, and MBF1 HIGH and MRS2 or PRS2 LOW to AEA LOW, AFC HIGH, and MBF2 HIGH                            | 1                              | 15   | ns   |

| tEN    | Enable Time, $\overline{\text{CSA}}$ or W/ $\overline{\text{R}}$ A LOW to A0-A35 Active and $\overline{\text{CSB}}$ LOW to B0-B17 Active                         | 2                              | 10   | ns   |

| tdis   | Disable Time, $\overline{\text{CSA}}$ or W/ $\overline{\text{RA}}$ HIGH to A0-A35 at HIGH impedance and $\overline{\text{CSB}}$ HIGH to B0-B17 at HIGH impedance | 1                              | 8    | ns   |

- 1. Writing data to the mail1 register when the B0-B17 outputs are active and MBB is HIGH.

- 2. Writing data to the mail2 register when the A0-A35 outputs are active and MBA is HIGH.

## SIGNAL DESCRIPTION

## MASTER RESET (MRS1, MRS2)

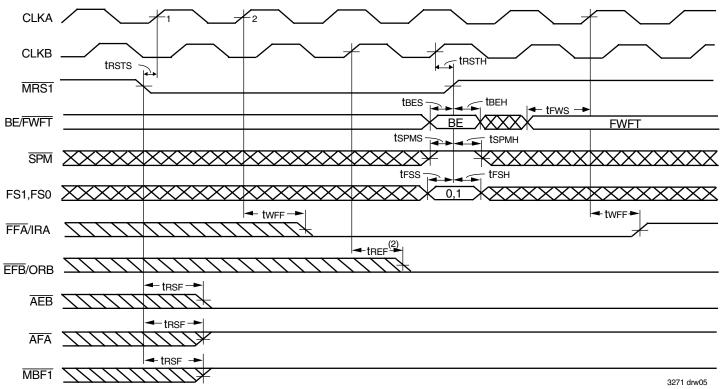

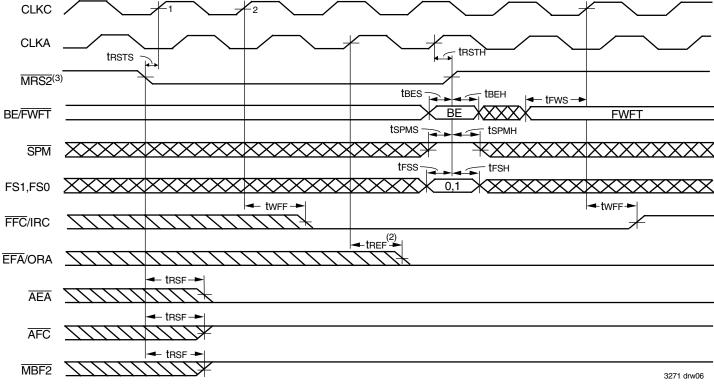

After power up, a Master Reset operation must be performed by providing a LOW pulse to MRS1 and MRS2 simultaneously. Afterwards, the FIFO1 memory of the IDT723626/723636/723646 undergoes a complete reset by taking its associated Master Reset (MRS1) input LOW for at least four Port A Clock (CLKA) and four Port B Clock (CLKB) LOW-to-HIGH transitions. The FIFO2 memory undergoes a complete reset by taking its associated Master Reset (MRS2) input LOW for at least four Port A Clock (CLKA) and four Port C Clock (CLKC) LOW-to-HIGH transitions. The Master Reset inputs can switch asvnchronously to the clocks. A Master Reset initializes the associated read and write pointers to the first location of the memory and forces the Full/Input Ready flag (FFA/IRA, FFC/IRC) LOW, the Empty/Output Ready flag (EFA/ORA, EFB/ ORB) LOW, the Almost-Empty flag (AEA, AEB) LOW, and the Almost-Full flag (AFA, AFC) HIGH. A Master Reset also forces the associated Mailbox Flag (MBF1, MBF2) of the parallel mailbox register HIGH. After a Master Reset, the FIFO's Full/Input Ready flag is set HIGH after two Write clock cycles. Then the FIFO is ready to be written to.

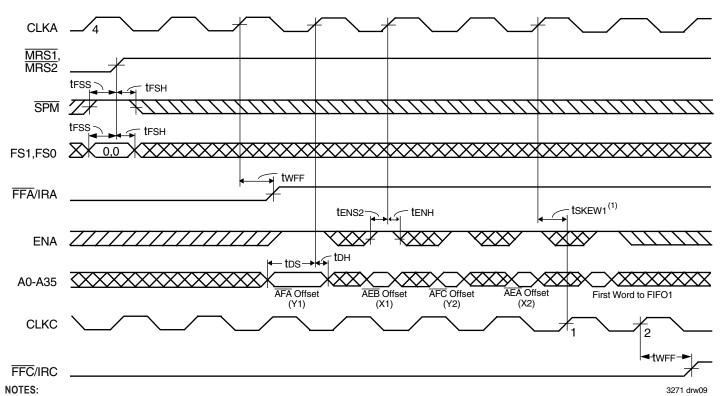

A LOW-to-HIGH transition on a FIFO1 Master Reset ( $\overline{MRS1}$ ,  $\overline{MRS2}$ ) input latches the value of the Big-Endian (BE) input for determining the order by which bytes are transferred through ports B and C. It also latches the values of the Flag Select (FS0, FS1) and Serial Programming Mode ( $\overline{SPM}$ ) inputs for choosing the Almost-Full and Almost-Empty offset programming mode.

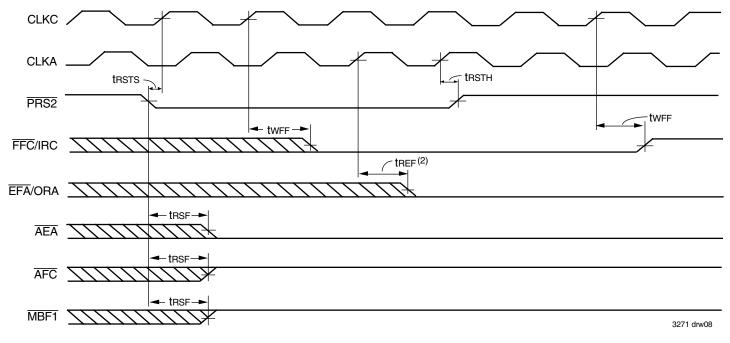

ALOW-to-HIGH transition on the FIFO2 Master Reset ( $\overline{\text{MRS2}}$ ) clears the flag offset registers of FIFO2 (X2, Y2). ALOW-to-HIGH transition on the FIFO2 Master Reset input ( $\overline{\text{MRS2}}$ ) latches the value of the Big-Endian (BE) input for Ports B and C and also latches the values of the Flag Select (FS0, FS1) and Serial Programming Mode ( $\overline{\text{SPM}}$ ) inputs for choosing the Almost-Full and Almost-Empty offset programming method (for details see Table 1, Flag Programming, and Almost-Empty and Almost-Full Flag Offset Programming section). The relevant Master Reset timing diagrams can be found in Figure 4 and 5.

Note that MBC must be HIGH during Master Reset (until FFA/IRA and FFC/IRC go HIGH). MBA and MBB are "don't care" inputs¹ during Master Reset.

## PARTIAL RESET (PRS1, PRS2)

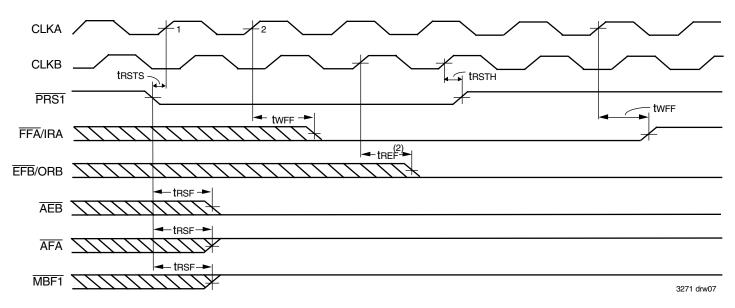

The FIFO1 memory of these devices undergoes a limited reset by taking its associated Partial Reset ( $\overline{PRS1}$ ) input LOW for at least four Port A Clock (CLKA) and four Port B Clock (CLKB) LOW-to-HIGH transitions. The FIFO2 memory undergoes a limited reset by taking its associated Partial Reset ( $\overline{PRS2}$ ) input LOW for at least four Port A Clock (CLKA) and four Port C Clock (CLKC) LOW-to-HIGH transitions. The Partial Reset inputs can switch asynchronously to the clocks. A Partial Reset initializes the internal read and write pointers and forces the Full/Input Ready flag ( $\overline{FFA}$ /IRA,  $\overline{FFC}$ /IRC) LOW, the Empty/Output Ready flag ( $\overline{EFA}$ /ORA,  $\overline{EFB}$ /ORB) LOW, the Almost-Empty flag ( $\overline{AEA}$ ,  $\overline{AEB}$ ) LOW, and the Almost-Full flag ( $\overline{AFA}$ ,  $\overline{AFC}$ ) HIGH. A Partial Reset also forces the Mailbox Flag ( $\overline{MBF1}$ ,  $\overline{MBF2}$ ) of the parallel mailbox register HIGH. After a Partial Reset, the FIFO's Full/Input Ready flag is set HIGH after two Write clock cycles.

Whatever flag offsets, programming method (parallel or serial), and timing mode (FWFT or IDT Standard mode) are currently selected at the time a Partial Reset is initiated, those settings will remain unchanged upon completion of the

reset operation. A Partial Reset may be useful in the case where reprogramming a FIFO following a Master Reset would be inconvenient. See Figure 6 and 7 for Partial Reset timing diagrams.

## BIG-ENDIAN/FIRST WORD FALL THROUGH (BE/FWFT)

#### — ENDIAN SELECTION

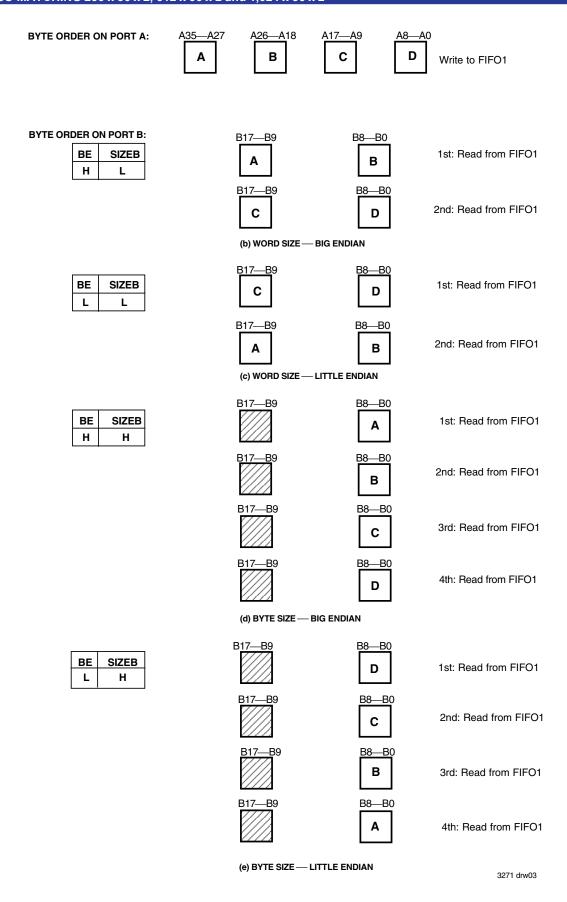

This is a dual purpose pin. At the time of Master Reset, the BE select function is active, permitting a choice of Big- or Little-Endian byte arrangement for data written to Port C or read from Port B. This selection determines the order by which bytes (or words) of data are transferred through those ports. For the following illustrations, note that both ports B and C are configured to have a byte (or a word) bus size.

AHIGH on the BE/FWFT input when the Master Reset (MRS1, MRS2) inputs go from LOW to HIGH will select a Big-Endian arrangement. When data is moving in the direction from Port A to Port B, the most significant byte (word) of the long word written to Port A will be read from Port B first; the least significant byte (word) of the long word written to Port A will be read from Port B last. When data is moving in the direction from Port C to Port A, the byte (word) written to Port C first will be read from Port A as the most significant byte (word) of the long word; the byte (word) written to Port C last will be read from Port A as the least significant byte (word) of the long word.

ALOW on the BE/FWFT input when the Master Reset (MRS1, MRS2) inputs go from LOW to HIGH will select a Little-Endian arrangement. When data is moving in the direction from Port A to Port B, the least significant byte (word) of the long word written to Port A will be read from Port B first; the most significant byte (word) of the long word written to Port A will be read from Port B last. When data is moving in the direction from Port C to Port A, the byte (word) written to Port C first will be read from Port A as the least significant byte (word) of the long word; the byte (word) written to Port C last will be read from Port A as the most significant byte (word) of the long word. Refer to Figures 2 and 3 for illustrations of the BE function. See Figure 4 (FIFO1 Master Reset) and 5 (FIFO2 Master Reset) for Endian Select timing diagrams.

#### — TIMING MODE SELECTION

After Master Reset, the FWFT select function is available, permitting a choice between two possible timing modes: IDT Standard mode or First Word Fall Through (FWFT) mode. Once the Master Reset ( $\overline{\text{MRS1}}$ ,  $\overline{\text{MRS2}}$ ) input is HIGH, a HIGH on the BE/ $\overline{\text{FWFT}}$  input during the next LOW-to-HIGH transition of CLKA (for FIFO1) and CLKC (for FIFO2) will select IDT Standard mode. This mode uses the Empty Flag function ( $\overline{\text{EFA}}$ ,  $\overline{\text{EFB}}$ ) to indicate whether or not there are any words present in the FIFO memory. It uses the Full Flag function ( $\overline{\text{FFA}}$ ,  $\overline{\text{FFC}}$ ) to indicate whether or not the FIFO memory has any free space for writing. In IDT Standard mode, every word read from the FIFO, including the first, must be requested using a formal read operation.

Once the Master Reset (MRS1, MRS2) input is HIGH, a LOW on the BE/FWFT input during the next LOW-to-HIGH transition of CLKA (for FIFO1) and CLKC (for FIFO2) will select FWFT mode. This mode uses the Output Ready function (ORA, ORB) to indicate whether or not there is valid data at the data outputs (A0-A35 or B0-B17). It also uses the Input Ready function (IRA, IRC) to indicate whether or not the FIFO memory has any free space for writing. In the FWFT mode, the first word written to an empty FIFO goes directly to the data

#### NOTE

<sup>1.</sup> Either a HIGH or LOW can be applied to a "don't care" input with no change to the logical operation of the FIFO. Nevertheless, inputs that are temporarily "don't care" (along with unused inputs) must not be left open, rather they must be either HIGH or LOW.

outputs, no read request necessary. Subsequent words must be accessed by performing a formal read operation. Refer to Figure 4 (FIFO1 Master Reset) and Figure 5 (FIFO2 Master Reset) for First Word Fall Through select timing diagrams.

Following Master Reset, the level applied to the BE/FWFT input to choose the desired timing mode must remain static throughout FIFO operation.

#### PROGRAMMING THE ALMOST-EMPTY AND ALMOST-FULL FLAGS

Four registers in these FIFOs are used to hold the offset values for the Almost-Empty and Almost-Full flags. The Port B Almost-Empty flag ( $\overline{AEB}$ ) Offset register is labeled X1 and the Port A Almost-Empty flag ( $\overline{AEA}$ ) Offset register is labeled X2. The Port A Almost-Full flag ( $\overline{AFA}$ ) Offset register is labeled Y1 and the Port C Almost-Full flag ( $\overline{AFC}$ ) Offset register is labeled Y2. The index of each register name corresponds to its FIFO number. The Offset registers can be loaded with preset values during the reset of a FIFO, programmed in parallel using the FIFO's Port A data inputs, or programmed in serial using the Serial Data (SD) input (see Table 1).

SPM, FS0/SD, and FS1/SEN function the same way in both IDT Standard and FWFT modes.

#### — PRESET VALUES

To load a FIFO's Almost-Empty flag and Almost-Full flag Offset registers with one of the three preset values listed in Table 1, the Serial Program Mode  $(\overline{SPM})$  and at least one of the flag-select inputs must be HIGH during the LOW-to-HIGH transition of its Master Reset  $(\overline{MRS1})$  and  $\overline{MRS2}$  input. For example, to load the preset value of 64 into X1 and Y1,  $\overline{SPM}$ , FS0 and FS1 must be HIGH when FIFO1 reset  $(\overline{MRS1})$  returns HIGH. Flag Offset registers associated with FIFO2 are loaded with one of the preset values in the same way with FIFO2 Master Reset  $(\overline{MRS2})$  toggled simultaneously with FIFO1 Master Reset  $(\overline{MRS1})$ . For relevant Preset value loading timing diagrams, see Figure 4 and 5.

#### --- PARALLEL LOAD FROM PORT A

To program the X1, X2, Y1, and Y2 registers from Port A, perform a Master Reset on both FIFOs simultaneously with  $\overline{SPM}$  HIGH and FS0 and FS1 LOW during the LOW-to-HIGH transition of  $\overline{MRS1}$  and  $\overline{MRS2}$ . After this reset is

complete, the first four writes to FIFO1 do not store data in RAM but load the Offset registers in the order Y1, X1, Y2, X2. The Port A data inputs used by the Offset registers are (A7-A0), (A8-A0), or (A9-A0) for the IDT723626, IDT723636, or IDT723646, respectively. The highest numbered input is used as the most significant bit of the binary number in each case. Valid programming values for the registers range from 1 to 252 for the IDT723626; 1 to 508 for the IDT723636; and 1 to 1,020 for the IDT723646. After all the Offset registers are programmed from Port A, the Port C Full/Input Ready flag ( $\overline{\text{FFC}}/\text{IRC}$ ) is set HIGH, and both FIFOs begin normal operation.

Refer to Figure 8 for a timing diagram illustration for parallel programming of the flag offset values.

#### -SERIAL LOAD

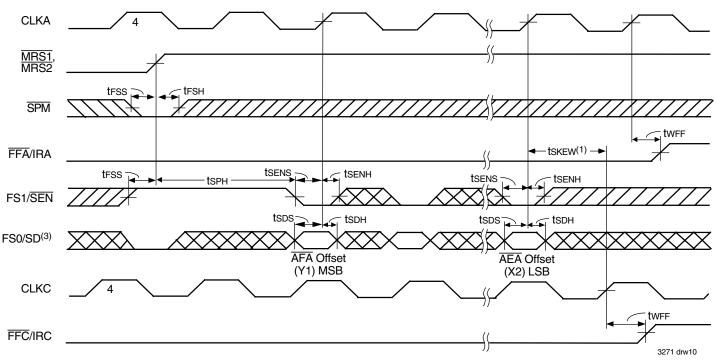

To program the X1, X2, Y1, and Y2 registers serially, initiate a Master Reset with  $\overline{SPM}$  LOW, FS0/SD LOW and FS1/\$\overline{SEN}\$ HIGH during the LOW-to-HIGH transition of \$\overline{MRS1}\$ and \$\overline{MRS2}\$. After this reset is complete, the X and Y register values are loaded bit-wise through the FS0/SD input on each LOW-to-HIGH transition of CLKA that the FS1/\$\overline{SEN}\$ input is LOW. There are 32-, 36-, or 40-bit writes needed to complete the programming for the IDT723626, IDT723636, or IDT723646, respectively. The four registers are written in the order Y1, X1, Y2 and finally, X2. The first-bit write stores the most significant bit of the Y1 register and the last-bit write stores the least significant bit of the X2 register. Each register value can be programmed from 1 to 252 (IDT723626), 1 to 508 (IDT723636), or 1 to 1,020 (IDT723646).

When the option to program the Offset registers serially is chosen, the Port A Full/Input Ready ( $\overline{FFA}$ /IRA) flag remains LOW until all register bits are written.  $\overline{FFA}$ /IRA is set HIGH by the LOW-to-HIGH transition of CLKA after the last bit is loaded to allow normal FIFO1 operation. The Port B Full/Input Ready ( $\overline{FFC}$ /IRC) flag also remains LOW throughout the serial programming process, until all register bits are written.  $\overline{FFC}$ /IRC is set HIGH by the LOW-to-HIGH transition of CLKC after the last bit is loaded to allow normal FIFO2 operation.

See Figure 9 timing diagram, Serial Programming of the Almost-Full Flag and Almost-Empty Flag Offset Values after Reset (IDT Standard and FWFT Modes).

## **TABLE 1 — FLAG PROGRAMMING**

| SPM | FS1/SEN | FS0/SD | MRS1     | MRS2     | X1 AND Y1 REGISTERS(1)          | X2 AND Y2 REGISTERS(2)          |

|-----|---------|--------|----------|----------|---------------------------------|---------------------------------|

| Н   | Н       | Н      | 1        | Х        | 64                              | X                               |

| Н   | Н       | Н      | 1        | 1        | 64                              | 64                              |

| Н   | Н       | L      | <b>↑</b> | Х        | 16                              | X                               |

| Н   | Н       | L      | 1        | 1        | 16                              | 16                              |

| Н   | L       | Н      | <b>↑</b> | Х        | 8                               | X                               |

| Н   | L       | Н      | <b>↑</b> | <b>↑</b> | 8                               | 8                               |

| Н   | L       | L      | 1        | 1        | Parallel programming via Port A | Parallel programming via Port A |

| L   | Н       | L      | 1        | 1        | Serial programming via SD       | Serial programming via SD       |

| L   | Н       | Н      | 1        | 1        | Reserved                        | Reserved                        |

| L   | L       | Н      | 1        | 1        | Reserved                        | Reserved                        |

| L   | L       | L      | 1        | 1        | Reserved                        | Reserved                        |

- 1. X1 register holds the offset for  $\overline{\text{AEB}}$ ; Y1 register holds the offset for  $\overline{\text{AFA}}$ .

- 2. X2 register holds the offset for AEA; Y2 register holds the offset for AFC.

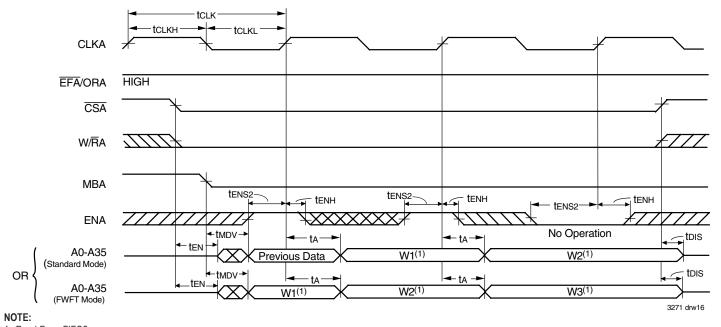

#### FIFO WRITE/READ OPERATION

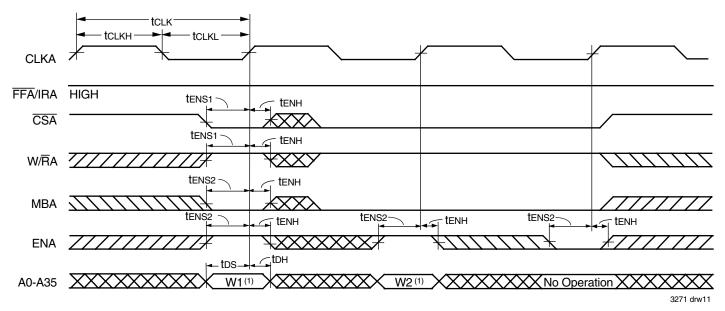

The state of the Port A data (A0-A35) outputs is controlled by Port A Chip Select ( $\overline{CSA}$ ) and Port A Write/Read Select ( $W/\overline{R}A$ ). The A0-A35 outputs are in the High-impedance state when either  $\overline{CSA}$  or  $W/\overline{R}A$  is HIGH. The A0-A35 outputs are active when both  $\overline{CSA}$  and  $W/\overline{R}A$  are LOW.

Data is loaded into FIFO1 from the A0-A35 inputs on a LOW-to-HIGH transition of CLKA when  $\overline{CSA}$  is LOW, W/ $\overline{RA}$  is HIGH, ENA is HIGH, MBA is LOW, and  $\overline{FFA}$ /IRA is HIGH. Data is read from FIFO2 to the A0-A35 outputs by a LOW-to-HIGH transition of CLKA when  $\overline{CSA}$  is LOW, W/ $\overline{RA}$  is LOW, ENA is HIGH, MBA is LOW, and  $\overline{EFA}$ /ORA is HIGH (see Table 2). FIFO reads and writes on Port A are independent of any concurrent Port B and Port C operation.

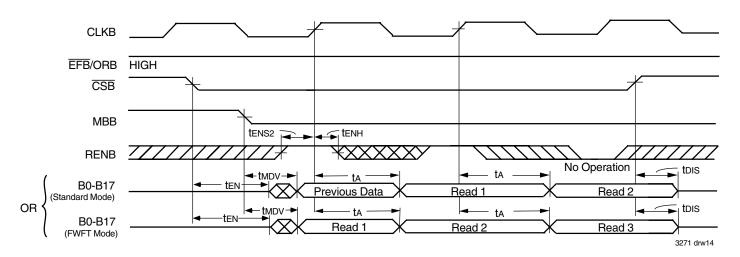

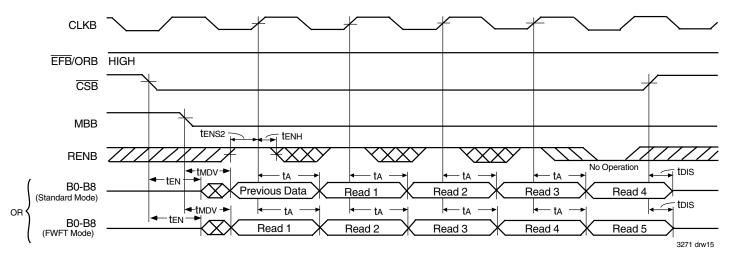

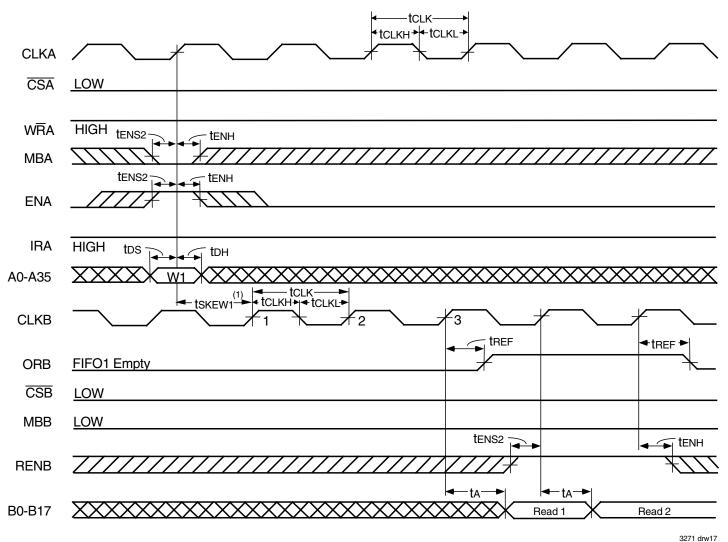

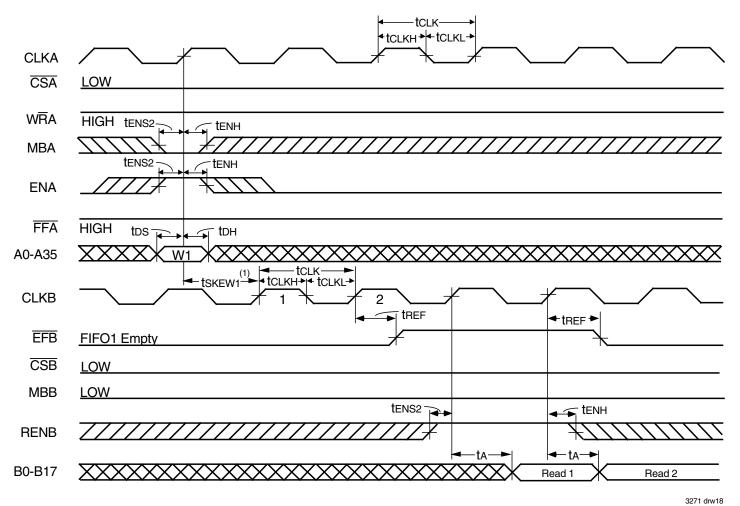

The state of the Port B data (B0-B17) outputs is controlled by the Port B Chip Select ( $\overline{\text{CSB}}$ ). The B0-B17 outputs are in the high-impedance state when  $\overline{\text{CSB}}$  is HIGH. The B0-B17 outputs are active when  $\overline{\text{CSB}}$  is LOW.

Data is read from FIFO1 to the B0-B17 outputs by a LOW-to-HIGH transition of CLKB when  $\overline{\text{CSB}}$  is LOW, RENB is HIGH, MBB is LOW and  $\overline{\text{EFB}}/\text{ORB}$  is HIGH (see Table 3). FIFO reads on Port B are independent of any concurrent Port A and Port C operations.

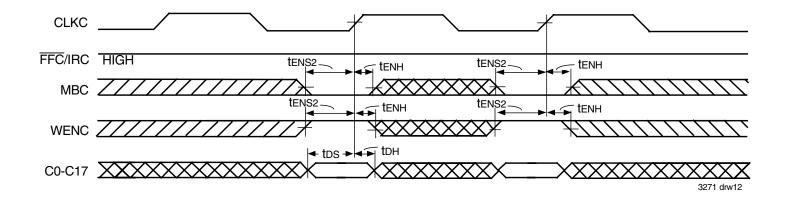

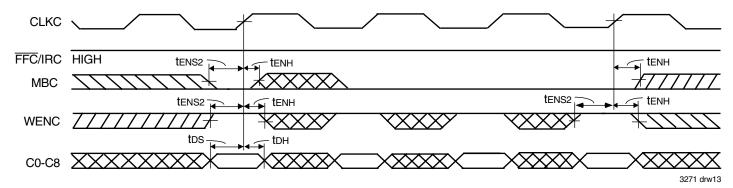

Data is loaded into FIFO2 from the C0-C17 inputs on a LOW-to-HIGH transition of CLKC when WENB is HIGH, MBC is LOW, and FFC/IRC is HIGH (see Table 4). FIFO writes on Port C are independent of any concurrent Port A and Port B operation.

The setup and hold time constraints for  $\overline{CSA}$  and  $W/\overline{R}A$  with regard to CLKA as well as  $\overline{CSB}$  with regard to CLKB are only for enabling write and read operations and are not related to high-impedance control of the data outputs. If ENA is LOW during a clock cycle, either  $\overline{CSA}$  or  $W/\overline{R}A$  may change states during the setup and hold time window of the cycle. This is also true for  $\overline{CSB}$  when RENB is LOW.

When operating the FIFO in FWFT mode and the Output Ready flag is LOW, the next word written is automatically sent to the FIFO's output register by the LOW-to-HIGH transition of the port clock that sets the Output Ready flag HIGH. When the Output Ready flag is HIGH, subsequent data is clocked to the output registers only when a read is selected using  $\overline{\text{CSA}}$ ,  $W/\overline{\text{RA}}$ , ENA and MBA at Port A or using  $\overline{\text{CSB}}$ , RENB and MBB at Port B.

When operating the FIFO in IDT Standard mode, the first word will cause the Empty Flag to change state on the second LOW-to-HIGH transition of the read clock. The data word will not be automatically sent to the output register. Instead, data residing in the FIFO's memory array is clocked to the output register only when a read is selected using  $\overline{CSA}$  W/RA ENA and MBA at Port A or using  $\overline{CSB}$ , RENB and MBB at Port B. Relevant write and read timing diagrams for Port A can be found in Figure 10 and 15. Relevant read and write timing diagrams for Port B and Port C, together with Bus-Matching and Endian Select operations can be found in Figures 11 to 14.

## **TABLE 2 — PORT A ENABLE FUNCTION TABLE**

| CSA | W/RA | ENA | MBA | CLKA     | DATA A (A0-A35) I/O | PORT FUNCTION              |

|-----|------|-----|-----|----------|---------------------|----------------------------|

| Н   | Х    | Х   | Х   | Х        | High-Impedance      | None                       |

| L   | Н    | L   | Х   | Х        | Input               | None                       |

| L   | Н    | Н   | L   | 1        | Input               | FIFO1 write                |

| L   | Н    | Н   | Н   | 1        | Input               | Mail1 write                |

| L   | L    | L   | L   | Х        | Output              | None                       |

| L   | L    | Н   | L   | <b>↑</b> | Output              | FIFO2 read                 |

| L   | L    | L   | Н   | Х        | Output              | None                       |

| L   | L    | Н   | Н   | <b>↑</b> | Output              | Mail2 read (set MBF2 HIGH) |

## TABLE 3 — PORT B ENABLE FUNCTION TABLE

| CSB | RENB | MBB | CLKB | DATA B (B0-B17) OUTPUTS | PORT FUNCTION              |

|-----|------|-----|------|-------------------------|----------------------------|

| Н   | Х    | Х   | Х    | High-Impedance          | None                       |

| L   | L    | L   | Х    | Output                  | None                       |

| L   | Н    | L   | 1    | Output                  | FIFO1 read                 |

| L   | L    | Н   | Х    | Output                  | None                       |

| L   | Н    | Н   | 1    | Output                  | Mail1 read (set MBF1 HIGH) |

## TABLE 4 — PORT C ENABLE FUNCTION TABLE

| WENC | MBC | CLKC     | DATA C (C0-C17) INPUTS | PORT FUNCTION |

|------|-----|----------|------------------------|---------------|

| Н    | L   | <b>↑</b> | Input                  | FIFO2 write   |

| Н    | Н   | 1        | Input                  | Mail2 write   |

| L    | L   | Х        | Input                  | None          |

| L    | Н   | Х        | Input                  | None          |

#### SYNCHRONIZED FIFO FLAGS

Each FIFO is synchronized to its port clock through at least two flip-flop stages. This is done to improve flag signal reliability by reducing the probability of metastable events when CLKA operates asynchronously with respect to either CLKB or CLKC. EFA/ORA, AEA, FFA/IRA, and AFA are synchronized to CLKA. EFB/ORB and AEB are synchronized to CLKB. FFC/IRC and AFC are synchronized to CLKC. Tables 5 and 6 show the relationship of each port flag to FIFO1 and FIFO2.

## EMPTY/OUTPUT READY FLAGS (EFA/ORA, EFB/ORB)

These are dual purpose flags. In the FWFT mode, the Output Ready (ORA, ORB) function is selected. When the Output Ready flag is HIGH, new data is present in the FIFO output register. When the Output Ready flag is LOW, the previous data word is present in the FIFO output register and attempted FIFO reads are ignored.

In the IDT Standard mode, the Empty Flag ( $\overline{EFA}$ ,  $\overline{EFB}$ ) function is selected. When the Empty Flag is HIGH, data is available in the FIFO's RAM memory for reading to the output register. When the Empty Flag is LOW, the previous data word is present in the FIFO output register and attempted FIFO reads are ignored.

The Empty/Output Ready flag of a FIFO is synchronized to the port clock that reads data from its array. For both the FWFT and IDT Standard modes, the FIFO read pointer is incremented each time a new word is clocked to its output register. The state machine that controls an Output Ready flag monitors a write

pointer and read pointer comparator that indicates when the FIFO memory status is empty, empty+1, or empty+2.

In FWFT mode, from the time a word is written to a FIFO, it can be shifted to the FIFO output register in a minimum of three cycles of the Output Ready flag synchronizing clock. Therefore, an Output Ready flag is LOW if a word in memory is the next data to be sent to the FIFO output register and three cycles of the port clock that reads data from the FIFO have not elapsed since the time the word was written. The Output Ready flag of the FIFO remains LOW until the third LOW-to-HIGH transition of the synchronizing clock occurs, simultaneously forcing the Output Ready flag HIGH and shifting the word to the FIFO output register.

In IDT Standard mode, from the time a word is written to a FIFO, the Empty Flag will indicate the presence of data available for reading in a minimum of two cycles of the Empty Flag synchronizing clock. Therefore, an Empty Flag is LOW if a word in memory is the next data to be sent to the FIFO output register and two cycles of the port Clock that reads data from the FIFO have not elapsed since the time the word was written. The Empty Flag of the FIFO remains LOW until the second LOW-to-HIGH transition of the synchronizing clock occurs, forcing the Empty Flag HIGH; only then can data be read.

ALOW-to-HIGH transition on an Empty/Output Ready flag synchronizing clock begins the first synchronization cycle of a write if the clock transition occurs at time tskew1 or greater after the write. Otherwise, the subsequent clock cycle can be the first synchronization cycle (see Figures 16, 17, 18 and 19).

## TABLE 5 — FIFO1 FLAG OPERATION (IDT Standard and FWFT modes)

| Nu                       | mber of Words in FIFO Memory | Synchro<br>to CL         |         | Synchronized to CLKA |     |         |

|--------------------------|------------------------------|--------------------------|---------|----------------------|-----|---------|

| IDT723626 <sup>(3)</sup> | IDT723636 <sup>(3)</sup>     | IDT723646 <sup>(3)</sup> | EFB/ORB | ĀĒB                  | ĀFĀ | FFA/IRA |

| 0                        | 0                            | 0                        | L       | L                    | Н   | Н       |

| 1 to X1                  | 1 to X1                      | 1 to X1                  | Н       | L                    | Н   | Н       |

| (X1+1) to [256-(Y1+1)]   | (X1+1) to [512-(Y1+1)]       | (X1+1) to [1,024-(Y1+1)] | Н       | Н                    | Н   | Н       |

| (256-Y1) to 255          | (512-Y1) to 511              | (1,024-Y1) to 1,023      | Н       | Н                    | L   | Н       |

| 256                      | 512                          | 1,024                    | Н       | Н                    | L   | L       |

#### NOTES:

- 1. When a word loaded to an empty FIFO is shifted to the output register, its previous FIFO memory location is free.

- Data in the output register does not count as a "word in FIFO memory". Since in FWFT mode, the first word written to an empty FIFO goes unrequested to the output register (no read operation necessary), it is not included in the FIFO memory count.

- 3. X1 is the almost-empty offset for FIFO1 used by AEB. Y1 is the almost-full offset for FIFO1 used by AFA. Both X1 and Y1 are selected during a FIFO1 reset or port A programming.

- 4. The ORB and IRA functions are active during FWFT mode; the EFB and FFA functions are active in IDT Standard mode.

## TABLE 6 — FIFO2 FLAG OPERATION (IDT Standard and FWFT modes)

| ADILO IIIO                                        | ZI ZAO OI ZIVA         | Synchr                   |         | Synchronized |     |         |  |

|---------------------------------------------------|------------------------|--------------------------|---------|--------------|-----|---------|--|

| Nu                                                | to Cl                  | _KA                      | to CLKC |              |     |         |  |

| IDT723626 <sup>(3)</sup> IDT723636 <sup>(3)</sup> |                        | IDT723646 <sup>(3)</sup> | EFA/ORA | ĀĒĀ          | ĀFC | FFC/IRC |  |

| 0                                                 | 0                      | 0                        | L       | L            | Н   | Н       |  |

| 1 to X2                                           | 1 to X2                | 1 to X2                  | Н       | L            | Н   | Н       |  |

| (X2+1) to [256-(Y2+1)]                            | (X2+1) to [512-(Y2+1)] | (X2+1) to [1,024-(Y2+1)] | Н       | Н            | Н   | Н       |  |

| (256-Y2) to 255                                   | (512-Y2) to 511        | (1,024-Y2) to 1,023      | Н       | Н            | L   | Н       |  |

| 256                                               | 512                    | 1,024                    | Н       | Н            | L   | L       |  |

- 1. When a word loaded to an empty FIFO is shifted to the output register, its previous FIFO memory location is free.

- 2. Data in the output register does not count as a "word in FIFO memory". Since in FWFT mode, the first word written to an empty FIFO goes unrequested to the output register (no read operation necessary), it is not included in the FIFO memory count.

- 3. X2 is the almost-empty offset for FIFO2 used by AEA. Y2 is the almost-full offset for FIFO2 used by AEC. Both X2 and Y2 are selected during a FIFO2 reset or port A programming.

- 4. The ORA and IRC functions are active during FWFT mode; the EFA and FFC functions are active in IDT Standard mode.

## FULL/INPUT READY FLAGS (FFA/IRA, FFC/IRC)

These are dual purpose flags. In FWFT mode, the Input Ready (IRA and IRC) function is selected. In IDT Standard mode, the Full Flag (FFA and FFC) function is selected. For both timing modes, when the Full/Input Ready flag is HIGH, a memory location is free in the FIFO to receive new data. No memory locations are free when the Full/Input Ready flag is LOW and attempted writes to the FIFO are ignored.

The Full/Input Ready flag of a FIFO is synchronized to the port clock that writes data to its array. For both FWFT and IDT Standard modes, each time a word is written to a FIFO, its write pointer is incremented. The state machine that controls a Full/Input Ready flag monitors a write pointer and read pointer comparator that indicates when the FIFO memory status is full, full-1, or full-2. From the time a word is read from a FIFO, its previous memory location is ready to be written to in a minimum of two cycles of the Full/Input Ready flag synchronizing clock. Therefore, an Full/Input Ready flag is LOW if less than two cycles of the Full/Input Ready flag synchronizing clock have elapsed since the next memory write location has been read. The second LOW-to-HIGH transition on the Full/Input Ready flag synchronizing clock after the read sets the Full/Input Ready flag HIGH.

A LOW-to-HIGH transition on a Full/Input Ready flag synchronizing clock begins the first synchronization cycle of a read if the clock transition occurs at time tskew1 or greater after the read. Otherwise, the subsequent clock cycle can be the first synchronization cycle (see Figures 20, 21, 22, and 23).

## ALMOST-EMPTY FLAGS (AEA, AEB)

The Almost-Empty flag of a FIFO is synchronized to the port clock that reads data from its array. The state machine that controls an Almost-Empty flag monitors a write pointer and read pointer comparator that indicates when the FIFO memory status is almost-empty, almost-empty+1, or almost-empty+2. The almost-empty state is defined by the contents of register X1 for  $\overline{\text{AEB}}$  and register X2 for  $\overline{\text{AEA}}$ . These registers are loaded with preset values during a FIFO reset, programmed from Port A, or programmed serially (see Almost-Empty flag and Almost-Full flag offset programming section). An Almost-Empty flag is LOW when its FIFO contains X or less words and is HIGH when its FIFO contains (X+1) or more words. A data word present in the FIFO output register has been read from memory.

Two LOW-to-HIGH transitions of the Almost-Empty flag synchronizing clock are required after a FIFO write for its Almost-Empty flag to reflect the new level of fill. Therefore, the Almost-Empty flag of a FIFO containing (X+1) or more words remains LOW if two cycles of its synchronizing clock have not elapsed since the write that filled the memory to the (X+1) level. An Almost-Empty flag is set HIGH by the second LOW-to-HIGH transition of its synchronizing clock after the FIFO write that fills memory to the (X+1) level. A LOW-to-HIGH transition of an Almost-Empty flag synchronizing clock begins the first synchronization cycle if it occurs at time tskew2 or greater after the write that fills the FIFO to (X+1) words. Otherwise, the subsequent synchronizing clock cycle may be the first synchronization cycle. (See Figures 24 and 25).

## ALMOST-FULL FLAGS (AFA, AFC)

The Almost-Full flag of a FIFO is synchronized to the port clock that writes data to its array. The state machine that controls an Almost-Full flag monitors a write pointer and read pointer comparator that indicates when the FIFO memory status is almost-full, almost-full-1, or almost-full-2. The almost-full state is defined by the contents of register Y1 for AFA and register Y2 for AFC. These registers are loaded with preset values during a FIFO reset,

programmed from Port A, or programmed serially (see *Almost-Empty flag and Almost-Full flag offset programming* section). An Almost-Full flag is LOW when the number of words in its FIFO is greater than or equal to (256-Y), (512-Y), or (1,024-Y) for the IDT723626, IDT723636, or IDT723646 respectively. An Almost-Full flag is HIGH when the number of words in its FIFO is less than or equal to [256-(Y+1)], [512-(Y+1)], or [1,024-(Y+1)] for the IDT723626, IDT723636, or IDT723646 respectively. Note that a data word present in the FIFO output register has been read from memory.

Two LOW-to-HIGH transitions of the Almost-Full flag synchronizing clock are required after a FIFO read for its Almost-Full flag to reflect the new level of fill. Therefore, the Almost-Full flag of a FIFO containing [256/512/1,024-(Y+1)] or less words remains LOW if two cycles of its synchronizing clock have not elapsed since the read that reduced the number of words in memory to [256/512/1,024-(Y+1)]. An Almost-Full flag is set HIGH by the second LOW-to-HIGH transition of its synchronizing clock after the FIFO read that reduces the number of words in memory to [256/512/1,024-(Y+1)]. A LOW-to-HIGH transition of an Almost-Full flag synchronizing clock begins the first synchronization cycle if it occurs at time tskew2 or greater after the read that reduces the number of words in memory to [256/512/1,024-(Y+1)]. Otherwise, the subsequent synchronizing clock cycle may be the first synchronization cycle (see Figures 26 and 27).

## **MAILBOX REGISTERS**

Each FIFO has an 18-bit bypass register allowing the passage of command and control information from Port A to Port B or from Port C to Port A without putting it in queue. The Mailbox Select (MBA, MBB and MBC) inputs choose between a mail register and a FIFO for a port data transfer operation. The usable width of both the Mail1 and Mail2 registers matches the selected bus size for ports B and C.

When sending data from Port A to Port B via the Mail1 Register, the following is the case: ALOW-to-HIGH transition on CLKA writes data to the Mail1 Register when a Port A write is selected by  $\overline{\text{CSA}}$ , W/ $\overline{\text{R}}$ A, and ENA with MBA HIGH. If the selected Port B bus size is 18 bits, then the usable width of the Mail1 Register employs data lines A0-A17. (In this case, A18-A35 are don't care inputs.) If the selected Port B bus size is 9 bits, then the usable width of the Mail1 Register employs data lines A0-A8. (In this case, A9-A35 are don't care inputs.)

When sending data from Port C to Port A via the Mail2 Register, the following is the case: A LOW-to-HIGH transition on CLKC writes data to the Mail2 Register when a Port C write is selected by WENC with MBC HIGH. If the selected Port C bus size is 18 bits, then the usable width of the Mail2 Register employs data lines C0-C17. If the selected Port C bus size is 9 bits, then the usable width of the Mail2 Register employs data lines C0-C8. (In this case, C9-C17 are don't care inputs.)

Writing data to a mail register sets its corresponding flag (MBF1 or MBF2) LOW. Attempted writes to a mail register are ignored while the mail flag is LOW.

When data outputs of a port are active, the data on the bus comes from the FIFO output register when the port Mailbox select input is LOW and from the mail register when the port mailbox select input is HIGH.

The Mail1 Register Flag ( $\overline{MBF1}$ ) is set HIGH by a LOW-to-HIGH transition on CLKB when a Port B read is selected by  $\overline{CSB}$ , and RENB with MBB HIGH. For an 18-bit bus size, 18 bits of mailbox data are placed on B0-B17. For the 9-bit bus size, 9 bits of mailbox data are placed on B0-B8. (In this case, B9-B17 are indeterminate.)

The Mail2 Register Flag (MBF2) is set HIGH by a LOW-to-HIGH transition on CLKA when a Port A read is selected by CSA, W/RA, and ENA with MBA HIGH. The data in a mail register remains intact after it is read and changes only when new data is written to the register. For an 18-bit bus size, 18 bits of mailbox

data appear on A18-A35. (In this case, A0-A17 are indeterminate.) For a 9-bit bus size, 9 bits of mailbox data appear on A18-A26. (In this case, A0-A17 and A27-A35 are indeterminate.)

The data in a mail register remains intact after it is read and changes only when new data is written to the register. The Endian Select feature has no effect on mailbox data.

Note that MBC must be HIGH during Master Reset (until FFA/IRA and FFC/IRC go HIGH. MBA and MBB are don't care inputs during Master Reset. For mail registers and mail register flag timing diagrams, see Figure 28 and 29.

#### **BUS SIZING**

Port B may be configured in either an 18-bit word or a 9-bit byte format for data read from FIFO1. Port C may be configured in either an 18-bit word or a 9-bit byte format for data written to FIFO2. The bus size can be selected independently for Ports B and C. The level applied to the Port B Size Select (SIZEB) input determines the Port B bus size and the level applied to the Port C Size Select (SIZEC) input determines the Port C bus size. These levels should be static throughout FIFO operation. Both bus size selections are implemented at the completion of Master Reset, by the time the Full/Input Ready flag is set HIGH, as shown in Figures 2 and 3.