Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

### Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

#### INTEGRATED CIRCUITS

# DATA SHEET

### 74ABT899

9-bit dual latch transceiver with 8-bit parity generator/checker (3-State)

Product specification Supersedes data of 1993 Oct 04 IC23 Data Handbook

### 9-bit dual latch transceiver with 8-bit parity generator/checker (3-State)

74ABT899

#### **FEATURES**

- Symmetrical (A and B bus functions are identical)

- Selectable generate parity or "feed-through" parity for A-to-B and B-to-A directions

- Independent transparent latches for A-to-B and B-to-A directions

- Selectable ODD/EVEN parity

- Continuously checks parity of both A bus and B bus latches as ERRA and ERRB

- Ability to simultaneously generate and check parity

- Can simultaneously read/latch A and B bus data

- Output capability: +64 mA/–32mA

- Latch-up protection exceeds 500mA per Jedec JC40.2 Std 17

- ESD protection exceeds 2000 V per MIL STD 883 Method 3015 and 200 V per Machine Model

- Power up 3-State

- Power-up reset

- Live insertion/extraction permitted

#### DESCRIPTION

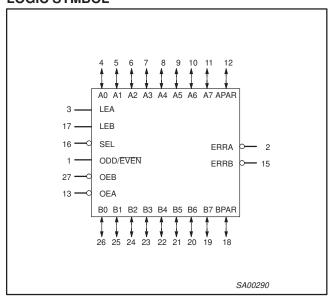

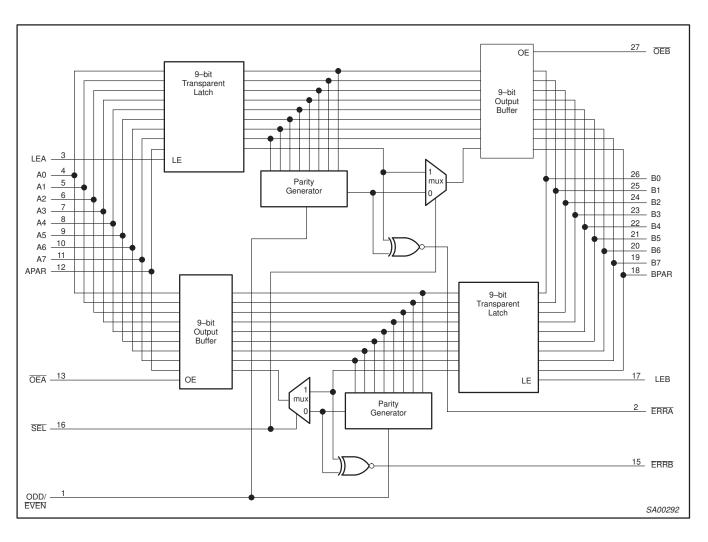

The 74ABT899 is a 9-bit to 9-bit parity transceiver with separate transparent latches for the A bus and B bus. Either bus can generate or check parity. The parity bit can be fed-through with no change or the generated parity can be substituted with the SEL input.

Parity error checking of the A and B bus latches is continuously provided with ERRA and ERRB, even with both buses in 3-State.

The 74ABT899 features independent latch enables for the A and B bus latches, a select pin for ODD/EVEN parity, and separate error signal output pins for checking parity.

#### **FUNCTIONAL DESCRIPTION**

The 74ABT899 has three principal modes of operation which are outlined below. All modes apply to both the A-to-B and B-to-A directions.

Transparent latch, Generate parity, Check A and B bus parity: Bus A (B) communicates to Bus B (A), parity is generated and passed on to the B (A) Bus as BPAR (APAR). If LEA and LEB are High and the Mode Select (SEL) is Low, the parity generated from A0-A7 and B0-B7 can be checked and monitored by ERRA and ERRB. (Fault detection on both input and output buses.)

### Transparent latch, Feed-through parity, Check A and B bus parity:

Bus A (B) communicates to Bus B (A) in a feed-through mode if SEL is High. Parity is still generated and checked as ERRA and ERRB and can be used as an interrupt to signal a data/parity bit error to the CPU.

### Latched input, Generate/Feed-through parity, Check A (and B) bus parity:

Independent latch enables (LEA and LEB) allow other permutations of:

- Transparent latch / 1 bus latched / both buses latched

- Feed-through parity / generate parity

- Check in bus parity / check out bus parity / check in and out bus parity

#### **QUICK REFERENCE DATA**

| SYMBOL                               | PARAMETER                                 | CONDITIONS<br>T <sub>amb</sub> = 25°C; GND = 0V | TYPICAL | UNIT |

|--------------------------------------|-------------------------------------------|-------------------------------------------------|---------|------|

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation delay<br>An to Bn or Bn to An | $C_L = 50pF; V_{CC} = 5V$                       | 2.9     | ns   |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation delay<br>An to ERRA           | $C_L = 50pF; V_{CC} = 5V$                       | 6.1     | ns   |

| C <sub>IN</sub>                      | Input capacitance                         | $V_I = 0V$ or $V_{CC}$                          | 4       | рF   |

| C <sub>I/O</sub>                     | Output capacitance                        | Outputs disabled; $V_O = 0V$ or $V_{CC}$        | 7       | рF   |

| I <sub>CCZ</sub>                     | Total supply current                      | Outputs disabled; V <sub>CC</sub> =5.5V         | 50      | μΑ   |

#### **ORDERING INFORMATION**

| PACKAGES            | TEMPERATURE RANGE | OUTSIDE NORTH AMERICA | NORTH AMERICA | DWG NUMBER |

|---------------------|-------------------|-----------------------|---------------|------------|

| 28-Pin Plastic PLCC | -40°C to +85°C    | 74ABT899 A            | 74ABT899 A    | SOT261-3   |

| 28-Pin Plastic SOP  | -40°C to +85°C    | 74ABT899 D            | 74ABT899 D    | SOT136-1   |

| 28-Pin Plastic SSOP | -40°C to +85°C    | 74ABT899 DB           | 74ABT899 DB   | SOT341-1   |

### 9-bit dual latch transceiver with 8-bit parity generator/checker (3-State)

74ABT899

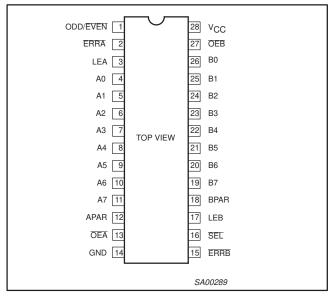

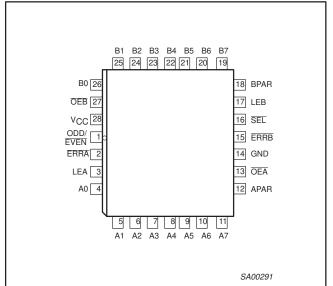

#### **PIN CONFIGURATION**

#### PLCC PIN CONFIGURATION

#### **PIN DESCRIPTION**

| SYMBOL              | PIN<br>NUMBER                           | NAME AND FUNCTION                          |  |  |  |  |  |

|---------------------|-----------------------------------------|--------------------------------------------|--|--|--|--|--|

| A0 - A7             | 4, 5, 6, 7,<br>8, 9, 10,<br>11          | Latched A bus 3-State inputs/outputs       |  |  |  |  |  |

| B0 - B7             | 19, 20,<br>21, 22,<br>23, 24,<br>25, 26 | Latched B bus 3-State inputs/outputs       |  |  |  |  |  |

| APAR                | 12                                      | A bus parity 3-State input                 |  |  |  |  |  |

| BPAR                | 18                                      | B bus parity 3-State input                 |  |  |  |  |  |

| ODD/<br>EVEN        | 1                                       | Parity select input (Low for EVEN parity)  |  |  |  |  |  |

| OEA, OEB            | 13, 27                                  | Output enable inputs (gate A to B, B to A) |  |  |  |  |  |

| SEL                 | 16                                      | Mode select input (Low for generate)       |  |  |  |  |  |

| LEA, LEB            | 3, 17                                   | Latch enable inputs (transparent High)     |  |  |  |  |  |

| ERRA,<br>ERRB 2, 15 |                                         | Error signal outputs (active-Low)          |  |  |  |  |  |

| GND                 | 14                                      | Ground (0V)                                |  |  |  |  |  |

| V <sub>CC</sub>     | 28                                      | Positive supply voltage                    |  |  |  |  |  |

#### LOGIC SYMBOL

74ABT899

#### **FUNCTION TABLE**

|           | I   | NPUTS | <b>;</b> |     | OPERATING MODE                                                                                    |  |  |  |  |  |  |

|-----------|-----|-------|----------|-----|---------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| OEB       | OEA | SEL   | LEA      | LEB |                                                                                                   |  |  |  |  |  |  |

| Н         | Н   | Х     | Х        | Х   | 3-State A bus and B bus (input A & B simultaneously)                                              |  |  |  |  |  |  |

| Н         | L   | L     | L        | Н   | $B \rightarrow A$ , transparent B latch, generate parity from B0 - B7, check B bus parity         |  |  |  |  |  |  |

| Н         | L   | L     | Н        | Н   | $B \rightarrow A$ , transparent A & B latch, generate parity from B0 - B7, check A & B bus parity |  |  |  |  |  |  |

| Н         | L   | L     | Х        | L   | $B \rightarrow A$ , B bus latched, generate parity from latched B0 - B7 data, check B bus parity  |  |  |  |  |  |  |

| Н         | L   | Н     | Х        | Н   | $B \to A,$ transparent B latch, parity feed-through, check B bus parity                           |  |  |  |  |  |  |

| Н         | L   | Н     | Н        | Н   | $B \rightarrow A$ , transparent A & B latch, parity feed-through, check A & B bus parity          |  |  |  |  |  |  |

| L         | Н   | L     | Н        | Х   | $A \rightarrow B$ , transparent A latch, generate parity from A0 - A7, check A bus parity         |  |  |  |  |  |  |

| L         | Н   | L     | Н        | Н   | $A \rightarrow B$ , transparent A & B latch, generate parity from A0 - A7, check A & B bus parity |  |  |  |  |  |  |

| L         | Н   | L     | L        | Х   | $A \rightarrow B$ , A bus latched, generate parity from latched A0 - A7 data, check A bus parity  |  |  |  |  |  |  |

| L         | Н   | Н     | Н        | L   | $A \to B,$ transparent A latch, parity feed-through, check A bus parity                           |  |  |  |  |  |  |

| L         | Н   | Н     | Н        | Н   | $A \rightarrow B$ , transparent A & B latch, parity feed-through, check A & B bus parity          |  |  |  |  |  |  |

| L L X X X |     |       |          |     | Output to A bus and B bus (NOT ALLOWED)                                                           |  |  |  |  |  |  |

H = High voltage level

L = Low voltage level

X = Don't care

### 9-bit dual latch transceiver with 8-bit parity generator/checker (3-State)

74ABT899

#### PARITY AND ERROR FUNCTION TABLE

|     | INPU <sup>-</sup> | TS               |                     |                  | OUTPUTS |        |      |                           |  |  |  |

|-----|-------------------|------------------|---------------------|------------------|---------|--------|------|---------------------------|--|--|--|

| SEL | ODD/EVEN          | xPAR<br>(A or B) | Σ of High<br>Inputs | xPAR<br>(B or A) | ERRt    | ERRr*  |      | PARITY MODES              |  |  |  |

| Н   | Н                 | Н                | Even<br>Odd         | H<br>H           | H<br>L  | H<br>L | Odd  |                           |  |  |  |

| Н   | Н                 | L                | Even<br>Odd         | L<br>L           | L<br>H  | L<br>H | Mode | Feed-through/check parity |  |  |  |

| Н   | L                 | Н                | Even<br>Odd         | H                | L<br>H  | L<br>H | Even |                           |  |  |  |

| Н   | L                 | L                | Even<br>Odd         | LL               | H<br>L  | H<br>L | Mode |                           |  |  |  |

| L   | Н                 | Н                | Even<br>Odd         | H<br>L           | H<br>L  | H<br>H | Odd  |                           |  |  |  |

| L   | Н                 | L                | Even<br>Odd         | H                | L<br>H  | H<br>H | Mode | Generate parity           |  |  |  |

| L   | L                 | Н                | Even<br>Odd         | L<br>H           | L<br>H  | H<br>H | Even |                           |  |  |  |

| L   | L                 | L                | Even<br>Odd         | L<br>H           | H<br>L  | H<br>H | Mode |                           |  |  |  |

H = High voltage level

Low voltage level

= Transmit—if the data path is from A→B then ERRt is ERRA = Receive—if the data path is from A→B then ERRr is ERRB Blocked if latch is not transparent

#### ABSOLUTE MAXIMUM RATINGS<sup>1, 2</sup>

| SYMBOL           | PARAMETER                      | CONDITIONS                  | RATING       | UNIT |

|------------------|--------------------------------|-----------------------------|--------------|------|

| V <sub>CC</sub>  | DC supply voltage              |                             | -0.5 to +7.0 | V    |

| I <sub>IK</sub>  | DC input diode current         | V <sub>I</sub> < 0          | -18          | mA   |

| VI               | DC input voltage <sup>3</sup>  |                             | -1.2 to +7.0 | V    |

| l <sub>OK</sub>  | DC output diode current        | V <sub>O</sub> < 0          | -50          | mA   |

| V <sub>OUT</sub> | DC output voltage <sup>3</sup> | output in Off or High state | -0.5 to +5.5 | V    |

| l <sub>OUT</sub> | DC output current              | output in Low state         | 128          | mA   |

| T <sub>stg</sub> | Storage temperature range      |                             | -65 to 150   | °C   |

#### NOTES:

- 1. Stresses beyond those listed may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

- 2. The performance capability of a high-performance integrated circuit in conjunction with its thermal environment can create junction temperatures which are detrimental to reliability. The maximum junction temperature of this integrated circuit should not exceed 1505C.

3. The input and output voltage ratings may be exceeded if the input and output current ratings are observed.

74ABT899

#### RECOMMENDED OPERATING CONDITIONS

| SYMBOL           | PARAMETER                            | LIM | ITS             | UNIT |

|------------------|--------------------------------------|-----|-----------------|------|

|                  |                                      | Min | Max             |      |

| V <sub>CC</sub>  | DC supply voltage                    | 4.5 | 5.5             | V    |

| VI               | Input voltage                        | 0   | V <sub>CC</sub> | V    |

| V <sub>IH</sub>  | High-level input voltage             | 2.0 |                 | V    |

| V <sub>IL</sub>  | Low-level Input voltage              |     | 0.8             | V    |

| I <sub>OH</sub>  | High-level output current            |     | -32             | mA   |

| I <sub>OL</sub>  | Low-level output current             |     | 64              | mA   |

| Δt/Δν            | Input transition rise or fall rate   | 0   | 5               | ns/V |

| T <sub>amb</sub> | Operating free-air temperature range | -40 | +85             | °C   |

#### DC ELECTRICAL CHARACTERISTICS

|                                    |                                           |               |                                                                                    |             |                     | LIMITS |                    |               |      |

|------------------------------------|-------------------------------------------|---------------|------------------------------------------------------------------------------------|-------------|---------------------|--------|--------------------|---------------|------|

| SYMBOL                             | PARAM                                     | ETER          | TEST CONDITIONS                                                                    | Tar         | <sub>nb</sub> = +25 | °C     | T <sub>amb</sub> = | –40°C<br>35°C | UNIT |

|                                    |                                           |               |                                                                                    | Min         | Тур                 | Max    | Min                | Max           |      |

| V <sub>IK</sub>                    | Input clamp volt                          | age           | V <sub>CC</sub> = 4.5V; I <sub>IK</sub> = -18mA                                    |             | -0.9                | -1.2   |                    | -1.2          | V    |

|                                    |                                           |               | $V_{CC} = 4.5V$ ; $I_{OH} = -3mA$ ; $V_I = V_{IL}$ or $V_{IH}$                     | 2.5         | 3.5                 |        | 2.5                |               | V    |

| V <sub>OH</sub>                    | High-level outpu                          | ıt voltage    | $V_{CC} = 5.0V$ ; $I_{OH} = -3mA$ ; $V_I = V_{IL}$ or $V_{IH}$                     | 3.0         | 4.0                 |        | 3.0                |               | V    |

|                                    |                                           |               | $V_{CC} = 4.5V$ ; $I_{OH} = -32mA$ ; $V_I = V_{IL}$ or $V_{IH}$                    | 2.0         | 2.6                 |        | 2.0                |               | V    |

| V <sub>OL</sub>                    | Low-level outpu                           | t voltage     | $V_{CC} = 4.5V$ ; $I_{OL} = 64mA$ ; $V_I = V_{IL}$ or $V_{IH}$                     |             | 0.42                | 0.55   |                    | 0.55          | V    |

| V <sub>RST</sub>                   | Power-up outpu<br>voltage <sup>3</sup>    | t low         | $V_{CC} = 5.5V$ ; $I_O = 1mA$ ; $V_I = GND$ or $V_{CC}$                            |             | 0.13                | 0.55   |                    | 0.55          | V    |

| l <sub>l</sub>                     | Input leakage Control pins                |               | V <sub>CC</sub> = 5.5V; V <sub>I</sub> = GND or 5.5V                               |             | ±0.01               | ±1.0   |                    | ±1.0          | μА   |

|                                    | current                                   | Data pins     | $V_{CC} = 5.5V; V_I = GND \text{ or } 5.5V$                                        |             | ±5                  | ±100   |                    | ±100          | μΑ   |

| I <sub>OFF</sub>                   | Power-off leaka                           | ge current    | $V_{CC} = 0.0V; V_O \text{ or } V_{1 \le} 4.5V$                                    |             | ±5.0                | ±100   |                    | ±100          | μА   |

| I <sub>PU</sub> /I <sub>PD</sub>   | Power-up/down output current <sup>4</sup> | 3-State       | $V_{CC}$ = 2.1V; $V_{O}$ = 0.5V; $V_{I}$ = GND or $V_{CC}$ ; $V_{OE}$ = Don't care |             | ±5.0                | ±50    |                    | ±50           | μА   |

| I <sub>IH</sub> + I <sub>OZH</sub> | 3-State output H                          | ligh current  | $V_{CC} = 5.5V; V_O = 2.7V; V_I = V_{IL} \text{ or } V_{IH}$                       |             | 5.0                 | 50     |                    | 50            | μА   |

| I <sub>IL</sub> + I <sub>OZL</sub> | 3-State output L                          | ow current    | $V_{CC} = 5.5V; V_O = 0.5V; V_I = V_{IL} \text{ or } V_{IH}$                       |             | -5.0                | -50    |                    | -50           | μА   |

| I <sub>CEX</sub>                   | Output High lea                           | kage current  | $V_{CC} = 5.5V; V_{O} = 5.5V; V_{I} = GND \text{ or } V_{CC}$                      |             | 5.0                 | 50     |                    | 50            | μА   |

| IO                                 | Output current <sup>1</sup>               |               | V <sub>CC</sub> = 5.5V; V <sub>O</sub> = 2.5V                                      | <b>-</b> 50 | -80                 | -180   | -50                | -180          | mA   |

| I <sub>CCH</sub>                   |                                           |               | $V_{CC} = 5.5V$ ; Outputs High, $V_{I} = GND$ or $V_{CC}$                          |             | 50                  | 250    |                    | 250           | μА   |

| I <sub>CCL</sub>                   | Quiescent supply current                  |               | $V_{CC} = 5.5V$ ; Outputs Low, $V_I = GND$ or $V_{CC}$                             |             | 28                  | 34     |                    | 34            | mA   |

| I <sub>CCZ</sub>                   |                                           |               | $V_{CC}$ = 5.5V; Outputs 3-State; $V_{I}$ = GND or $V_{CC}$                        |             | 50                  | 250    |                    | 250           | μА   |

| Δl <sub>CC</sub>                   | Additional supplinput pin <sup>2</sup>    | y current per | $V_{CC}$ = 5.5V; one input at 3.4V, other inputs at $V_{CC}$ or GND                |             | 0.3                 | 1.5    |                    | 1.5           | mA   |

#### NOTES:

- 1. Not more than one output should be tested at a time, and the duration of the test should not exceed one second.

- 2. This is the increase in supply current for each input at 3.4V.

- 3. For valid test results, data must not be loaded into the flip-flops (or latches) after applying the power.

- This parameter is valid for any V<sub>CC</sub> between 0V and 2.1V, with a transition time of up to 10msec. From V<sub>CC</sub> = 2.1V to V<sub>CC</sub> = 5V ± 10%, a transition time of up to 100µsec is permitted.

# 9-bit dual latch transceiver with 8-bit parity generator/checker (3-State)

74ABT899

#### **AC CHARACTERISTICS**

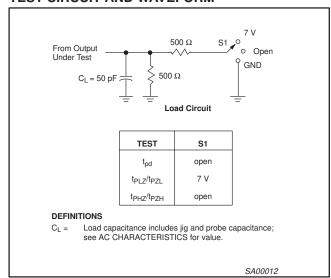

GND = 0V;  $t_R$  =  $t_F$  = 2.5ns;  $C_L$  = 50pF,  $R_L$  = 500 $\!\Omega$

|                                      |                                                           |          |            |                                                                        | LIMITS     |                                                                                       |             |    |

|--------------------------------------|-----------------------------------------------------------|----------|------------|------------------------------------------------------------------------|------------|---------------------------------------------------------------------------------------|-------------|----|

| SYMBOL                               | PARAMETER                                                 | WAVEFORM | ٦          | $F_{amb} = +25^{\circ}$ $V_{CC} = +5.0$ $C_L = 50pF$ $R_L = 500\Omega$ | /          | T <sub>amb</sub> = -4<br>V <sub>CC</sub> = +5<br>C <sub>L</sub> =<br>R <sub>L</sub> = | UNIT        |    |

|                                      |                                                           |          | Min        | Тур                                                                    | Max        | Min                                                                                   | Max         |    |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation delay<br>An to Bn or Bn to An                 | 1        | 1.0<br>1.0 | 3.2<br>2.7                                                             | 4.5<br>4.1 | 1.0<br>1.0                                                                            | 4.9<br>4.6  | ns |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation delay<br>An to BPAR or Bn to APAR             | 2        | 3.0<br>2.5 | 6.0<br>6.4                                                             | 7.5<br>7.9 | 3.0<br>2.5                                                                            | 9.0<br>8.8  | ns |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation delay<br>An to ERRA or Bn to ERRB             | 3        | 2.8<br>2.8 | 6.0<br>6.7                                                             | 8.0<br>8.5 | 2.8<br>2.8                                                                            | 9.1<br>9.3  | ns |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation delay<br>APAR to BPAR or BPAR to APAR         | 1        | 2.0<br>1.3 | 4.0<br>3.2                                                             | 5.2<br>4.4 | 2.0<br>1.3                                                                            | 5.7<br>5.0  | ns |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation delay<br>APAR to ERRA or BPAR to ERRB         | 6        | 1.5<br>1.5 | 4.2<br>4.0                                                             | 5.4<br>5.4 | 1.5<br>1.5                                                                            | 6.0<br>6.1  | ns |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation delay<br>ODD/EVEN to APAR or BPAR             | 5        | 2.6<br>2.5 | 5.5<br>5.3                                                             | 6.8<br>6.7 | 2.6<br>2.5                                                                            | 8.1<br>7.8  | ns |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation delay ODD/EVEN to ERRA or ERRB                | 4        | 2.3<br>2.6 | 5.4<br>5.7                                                             | 6.8<br>7.2 | 2.3<br>2.6                                                                            | 7.9<br>8.4  | ns |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation delay<br>SEL to APAR or BPAR                  | 8        | 1.3<br>1.4 | 4.1<br>4.1                                                             | 5.2<br>5.3 | 1.3<br>1.4                                                                            | 6.0<br>5.9  | ns |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation delay<br>SEL to ERRA or ERRB                  | 8        | 3.7<br>5.1 | 6.8<br>8.3                                                             | 8.3<br>9.7 | 3.7<br>5.1                                                                            | 9.8<br>11.0 | ns |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation delay<br>LEA to Bn or LEB to An               | 9        | 1.0<br>1.0 | 3.2<br>3.1                                                             | 4.4<br>4.5 | 1.0<br>1.0                                                                            | 4.9<br>5.0  | ns |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation delay<br>LEA to BPAR or LEB to APAR           | 9        | 2.0<br>1.7 | 6.8<br>6.3                                                             | 8.3<br>7.9 | 2.0<br>1.7                                                                            | 9.7<br>9.0  | ns |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation delay<br>LEA to ERRA or LEB to ERRB           | 7        | 2.0<br>2.0 | 6.3<br>7.1                                                             | 8.3<br>9.2 | 2.0<br>2.0                                                                            | 9.6<br>10.3 | ns |

| t <sub>PZH</sub><br>t <sub>PZL</sub> | Output enable time<br>OEA to An, APAR or OEB to Bn, BPAR  | 11, 12   | 1.0<br>1.0 | 3.0<br>3.4                                                             | 4.3<br>4.8 | 1.0<br>1.0                                                                            | 5.1<br>5.4  | ns |

| t <sub>PHZ</sub>                     | Output disable time<br>OEA to An, APAR or OEB to Bn, BPAR | 11, 12   | 1.0<br>0.5 | 3.4<br>3.0                                                             | 4.7<br>4.2 | 1.0<br>0.5                                                                            | 5.5<br>4.7  | ns |

#### **AC SETUP REQUIREMENTS**

GND = 0V;  $t_B = t_F = 2.5 \text{ns}$ ;  $C_L = 50 \text{pF}$ ,  $R_L = 500 \Omega$

| SYMBOL                                   | PARAMETER                                                     | $ \begin{array}{c} T_{amb} = +25^{\circ}C & T_{amb} = -40 \text{ tr} \\ V_{CC} = +5.0V & V_{CC} = +5.0V \\ C_{L} = 50 \text{pF} & C_{L} = 50 \\ R_{L} = 500 \Omega & R_{L} = 50 \end{array} $ |            |             |     |            | 50pF | UNIT |

|------------------------------------------|---------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-------------|-----|------------|------|------|

|                                          |                                                               |                                                                                                                                                                                               | Min        | Тур         | Max | Min        | Max  |      |

| t <sub>s</sub> (H)<br>t <sub>s</sub> (L) | Setup time, High or Low<br>An, APAR to LEA or Bn, BPAR to LEB | 10                                                                                                                                                                                            | 2.0<br>1.5 | 0.4<br>0.0  |     | 2.0<br>1.5 |      | ns   |

| t <sub>h</sub> (H)<br>t <sub>h</sub> (L) | Hold time, High or Low<br>An, APAR to LEA or Bn, BPAR to LEB  | 10                                                                                                                                                                                            | 1.5<br>1.0 | 0.0<br>-0.2 |     | 1.5<br>1.0 |      | ns   |

| t <sub>w</sub> (H)                       | Pulse width, High<br>LEA or LEB                               | 10                                                                                                                                                                                            | 3.0        | 1.9         |     | 3.0        |      | ns   |

### 9-bit dual latch transceiver with 8-bit parity generator/checker (3-State)

74ABT899

#### **AC WAVEFORMS**

$V_M = 1.5V$ ,  $V_{IN} = GND$  to 3.0V

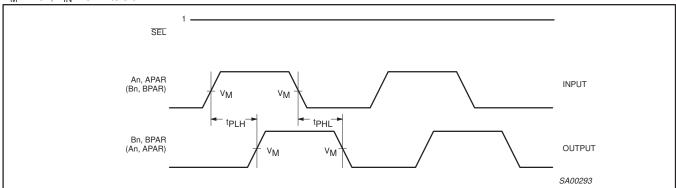

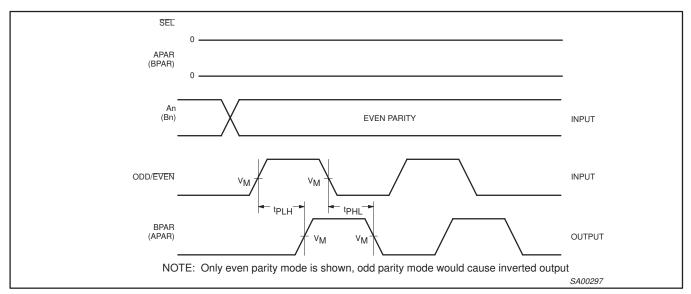

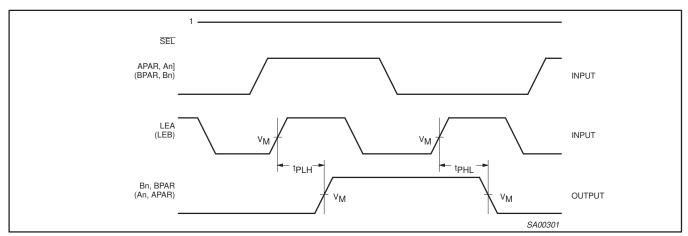

Waveform 1. Propagation Delay, An to Bn, Bn to An, APAR to BPAR, BPAR to APAR

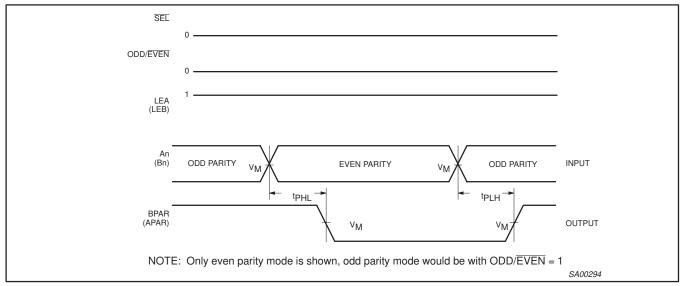

Waveform 2. Propagation Delay, An to BPAR or Bn to APAR

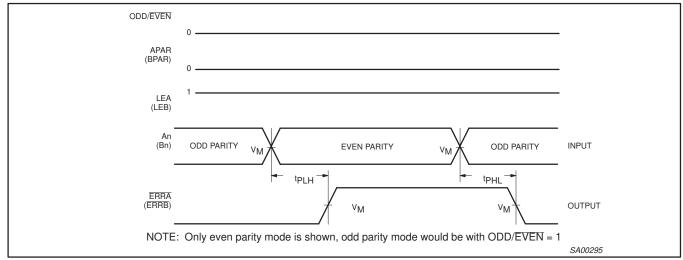

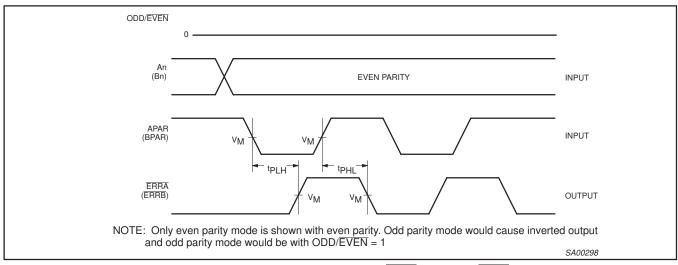

Waveform 3. Propagation Delay, An to ERRA or Bn to ERRB

## 9-bit dual latch transceiver with 8-bit parity generator/checker (3-State)

74ABT899

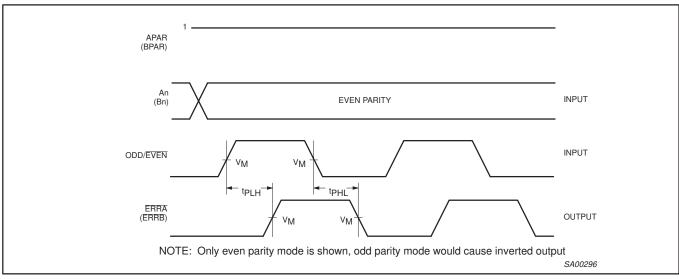

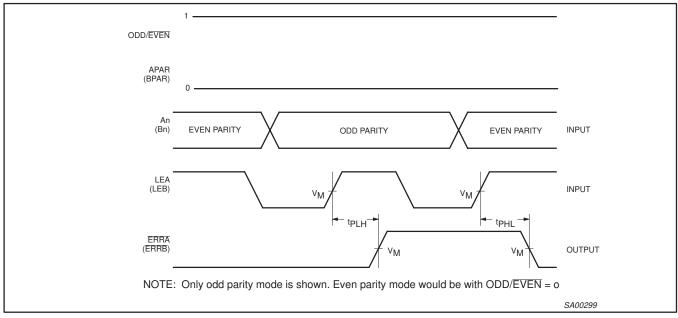

Waveform 4. Propagation Delay, ODD/EVEN to ERRA or ODD/EVEN to ERRB

Waveform 5. Propagation Delay, ODD/EVEN to APAR or ODD/EVEN to BPAR

## 9-bit dual latch transceiver with 8-bit parity generator/checker (3-State)

74ABT899

Waveform 6. Propagation Delay, APAR to ERRA or BPAR to ERRB

Waveform 7. Propagation Delay, LEA to ERRA or LEB to ERRB

### 9-bit dual latch transceiver with 8-bit parity generator/checker (3-State)

74ABT899

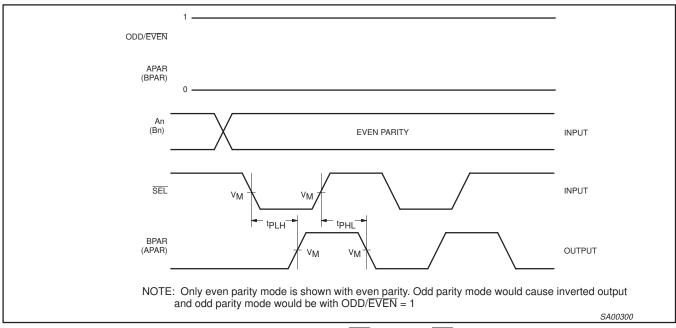

Waveform 8. Propagation Delay, SEL to BPAR or SEL to APAR

Waveform 9. Propagation Delay, LEA to BPAR or LEB to APAR, LEA to Bn or LEB to An

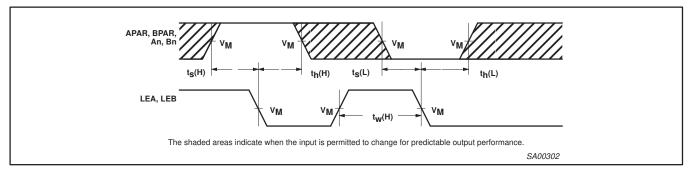

Waveform 10. Data Setup and Hold Times, Pulse Width High

## 9-bit dual latch transceiver with 8-bit parity generator/checker (3-State)

74ABT899

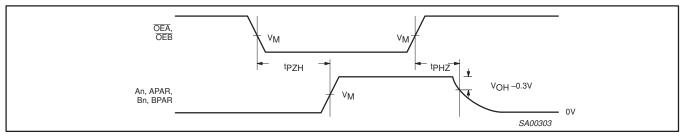

Waveform 11. 3-State Output Enable Time to High Level and Output Disable Time from High Level

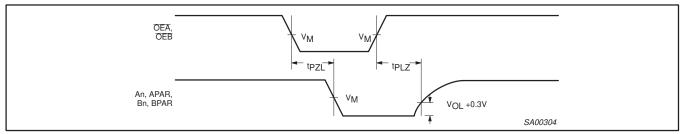

Waveform 12. 3-State Output Enable Time to Low Level and Output Disable Time from Low Level

#### **TEST CIRCUIT AND WAVEFORM**

74ABT899

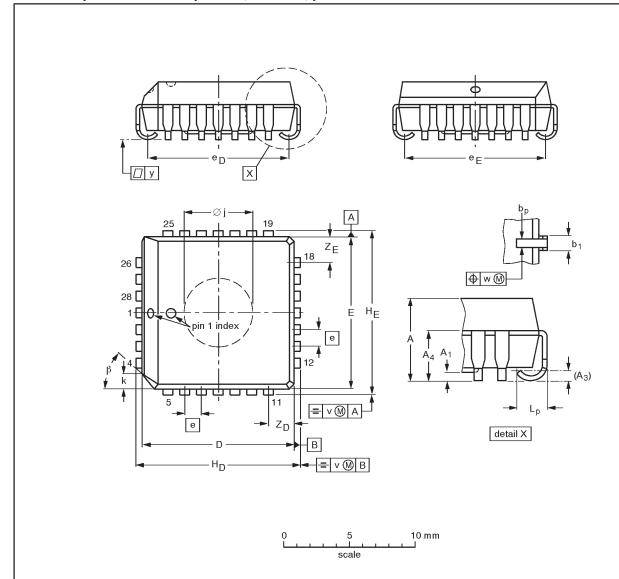

#### PLCC28: plastic leaded chip carrer; 28 leads; pedestal

SOT261-3

#### DIMENSIONS (millimetre dimensions are derived from the original inch dimensions)

| UNIT   | А              | A <sub>1</sub><br>min. | <b>A</b> <sub>3</sub> | A <sub>4</sub><br>max. | bp           | b <sub>1</sub> | D <sup>(1)</sup> | E <sup>(1)</sup> | е | еD             | еE | H <sub>D</sub> | HE             | k            | øj           | Lp           | v     | w     | у     | Z <sub>D</sub> <sup>(1)</sup><br>max. | Z <sub>E</sub> <sup>(1)</sup><br>max. | β   |

|--------|----------------|------------------------|-----------------------|------------------------|--------------|----------------|------------------|------------------|---|----------------|----|----------------|----------------|--------------|--------------|--------------|-------|-------|-------|---------------------------------------|---------------------------------------|-----|

| mm     | 4.57<br>4.19   | 0.13                   | 0.25                  | 3.05                   | 0.53<br>0.33 | 0.81<br>0.66   | 11.58<br>11.43   | 11.58<br>11.43   |   | 10.92<br>9.91  |    |                | 12.57<br>12.32 | 1.22<br>1.07 | 5.69<br>5.54 | 1.44<br>1.02 | 0.18  | 0.18  | 0.10  | 2.06                                  | 2.06                                  | 45° |

| inches | 0.180<br>0.165 | 0.005                  | 0.01                  | 0.12                   |              | 0.032<br>0.026 |                  |                  |   | 0.430<br>0.390 |    |                | 0.495<br>0.485 |              |              |              | 0.007 | 0.007 | 0.004 | 0.081                                 | 0.081                                 | 40  |

#### Note

1. Plastic or metal protrusions of 0.01 inches maximum per side are not included.

| OUTLINE  |     | REFER    | EUROPEAN | ISSUE DATE |            |                                 |

|----------|-----|----------|----------|------------|------------|---------------------------------|

| VERSION  | IEC | JEDEC    | EIAJ     |            | PROJECTION | ISSUE DATE                      |

| SOT261-3 |     | MO-047AB |          |            |            | <del>95-02-25</del><br>97-12-16 |

74ABT899

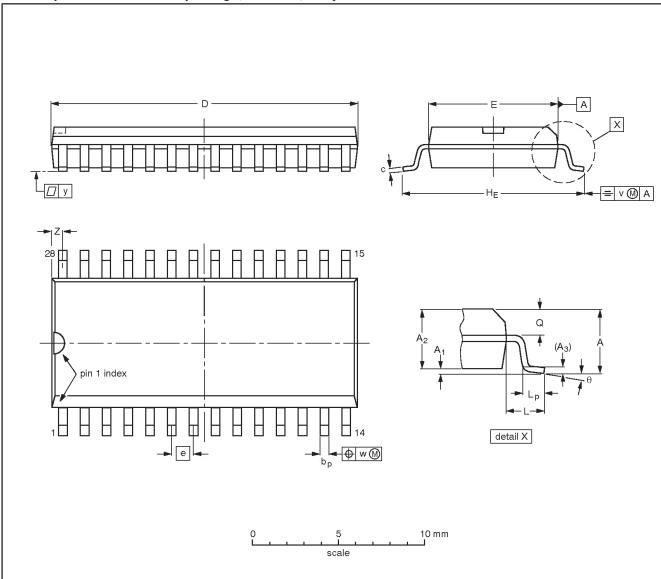

#### SO28: plastic small outline package; 28 leads; body width 7.5mm

SOT136-1

#### DIMENSIONS (inch dimensions are derived from the original mm dimensions)

| UNIT   | A<br>max. | A <sub>1</sub> | A <sub>2</sub> | А3   | bр             | С              | D <sup>(1)</sup> | E <sup>(1)</sup> | е     | HE             | L     | Lp             | Q              | v    | w    | у     | z <sup>(1)</sup> | θ  |

|--------|-----------|----------------|----------------|------|----------------|----------------|------------------|------------------|-------|----------------|-------|----------------|----------------|------|------|-------|------------------|----|

| mm     | 2.65      | 0.30<br>0.10   | 2.45<br>2.25   | 0.25 | 0.49<br>0.36   | 0.32<br>0.23   | 18.1<br>17.7     | 7.6<br>7.4       | 1.27  | 10.65<br>10.00 | 1.4   | 1.1<br>0.4     | 1.1<br>1.0     | 0.25 | 0.25 | 0.1   | 0.9<br>0.4       | 8° |

| inches | 0.10      | 0.012<br>0.004 | 0.096<br>0.089 | 0.01 | 0.019<br>0.014 | 0.013<br>0.009 | 0.71<br>0.69     | 0.30<br>0.29     | 0.050 | 0.419<br>0.394 | 0.055 | 0.043<br>0.016 | 0.043<br>0.039 | 0.01 | 0.01 | 0.004 | 0.035<br>0.016   | 0° |

#### Note

1. Plastic or metal protrusions of 0.15 mm maximum per side are not included.

| OUTLINE  |        | REFER    | EUROPEAN | ISSUE DATE |            |                                  |

|----------|--------|----------|----------|------------|------------|----------------------------------|

| VERSION  | IEC    | JEDEC    | EIAJ     |            | PROJECTION | ISSUE DATE                       |

| SOT136-1 | 075E06 | MS-013AE |          |            |            | <del>-95-01-24</del><br>97-05-22 |

74ABT899

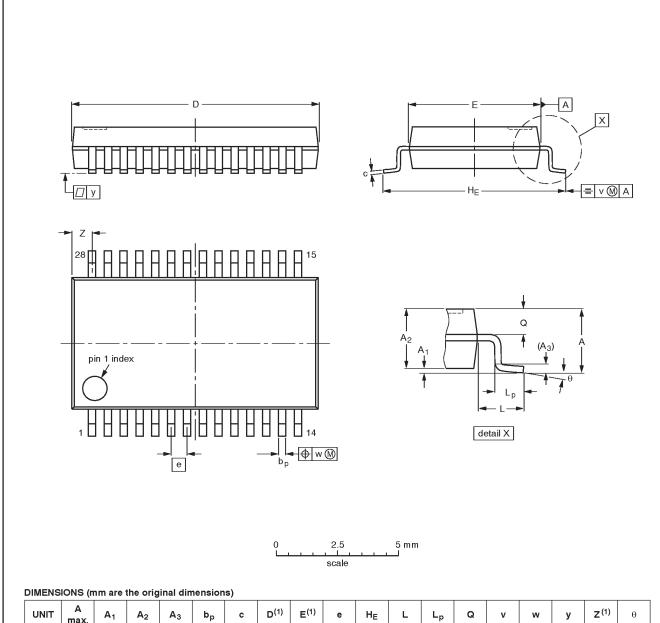

#### SSOP28: plastic shrink small outline package; 28 leads; body width 5.3mm

SOT341-1

| UNIT | A<br>max. | A <sub>1</sub> | A <sub>2</sub> | Α3   | bp           | c            | D <sup>(1)</sup> | E <sup>(1)</sup> | е    | HE         | L    | Lp           | Q          | v   | w    | у   | Z <sup>(1)</sup> | θ        |

|------|-----------|----------------|----------------|------|--------------|--------------|------------------|------------------|------|------------|------|--------------|------------|-----|------|-----|------------------|----------|

| mm   | 2.0       | 0.21<br>0.05   | 1.80<br>1.65   | 0.25 | 0.38<br>0.25 | 0.20<br>0.09 | 10.4<br>10.0     | 5.4<br>5.2       | 0.65 | 7.9<br>7.6 | 1.25 | 1.03<br>0.63 | 0.9<br>0.7 | 0.2 | 0.13 | 0.1 | 1.1<br>0.7       | 8°<br>0° |

#### Note

1. Plastic or metal protrusions of 0.20 mm maximum per side are not included.

| OUTLINE  |     | REFER    | RENCES | EUROPEAN   | ISSUE DATE                      |

|----------|-----|----------|--------|------------|---------------------------------|

| VERSION  | IEC | JEDEC    | EIAJ   | PROJECTION | ISSUE DATE                      |

| SOT341-1 |     | MO-150AH |        |            | <del>93-09-08</del><br>95-02-04 |

### 9-bit dual latch transceiver with 8-bit parity generator/checker (3-State)

74ABT899

#### Data sheet status

| Data sheet status         | Product status | Definition [1]                                                                                                                                                                                                                                            |

|---------------------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Objective specification   | Development    | This data sheet contains the design target or goal specifications for product development. Specification may change in any manner without notice.                                                                                                         |

| Preliminary specification | Qualification  | This data sheet contains preliminary data, and supplementary data will be published at a later date. Philips Semiconductors reserves the right to make chages at any time without notice in order to improve design and supply the best possible product. |

| Product specification     | Production     | This data sheet contains final specifications. Philips Semiconductors reserves the right to make changes at any time without notice in order to improve design and supply the best possible product.                                                      |

<sup>[1]</sup> Please consult the most recently issued datasheet before initiating or completing a design.

#### **Definitions**

**Short-form specification** — The data in a short-form specification is extracted from a full data sheet with the same type number and title. For detailed information see the relevant data sheet or data handbook.

**Limiting values definition** — Limiting values given are in accordance with the Absolute Maximum Rating System (IEC 134). Stress above one or more of the limiting values may cause permanent damage to the device. These are stress ratings only and operation of the device at these or at any other conditions above those given in the Characteristics sections of the specification is not implied. Exposure to limiting values for extended periods may affect device reliability.

**Application information** — Applications that are described herein for any of these products are for illustrative purposes only. Philips Semiconductors make no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

#### **Disclaimers**

**Life support** — These products are not designed for use in life support appliances, devices or systems where malfunction of these products can reasonably be expected to result in personal injury. Philips Semiconductors customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Philips Semiconductors for any damages resulting from such application.

**Right to make changes** — Philips Semiconductors reserves the right to make changes, without notice, in the products, including circuits, standard cells, and/or software, described or contained herein in order to improve design and/or performance. Philips Semiconductors assumes no responsibility or liability for the use of any of these products, conveys no license or title under any patent, copyright, or mask work right to these products, and makes no representations or warranties that these products are free from patent, copyright, or mask work right infringement, unless otherwise specified.

Philips Semiconductors 811 East Arques Avenue P.O. Box 3409 Sunnyvale, California 94088–3409 Telephone 800-234-7381 © Copyright Philips Electronics North America Corporation 1998 All rights reserved. Printed in U.S.A.

print code Date of release: 05-96

Document order number: 9397-750-03478

Let's make things better.

Philips Semiconductors