# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

### 74ACT16373

### 16-BIT D-TYPE LATCH WITH 3-STATE OUTPUTS (NON INVERTED)

- HIGH SPEED: t<sub>PD</sub> = 5.3ns (TYP.) at V<sub>CC</sub> = 5V

- LOW POWER DISSIPATION:  $I_{CC} = 8\mu A(MAX.)$  at  $T_A=25^{\circ}C$

- COMPATIBLE WITH TTL OUTPUTS

V<sub>IH</sub> = 2V (MIN.), V<sub>IL</sub> = 0.8V (MAX.)

- 50Ω TRANSMISSION LINE DRIVING CAPABILITY

- SYMMETRICAL OUTPUT IMPEDANCE: |I<sub>OH</sub>| = I<sub>OL</sub> = 24mA (MIN)

- OPERATING VOLTAGE RANGE:

V<sub>CC</sub> (OPR) = 4.5V to 5.5V

- IMPROVED LATCH-UP IMMUNITY

#### DESCRIPTION

The 74ACT16373 is an advanced high-speed CMOS 16-BIT D-TYPE LATCH (3-STATE) fabricated with sub-micron silicon gate and double-layer metal wiring C<sup>2</sup>MOS tecnology.

This 16 bit D-Type latch is controlled by two latch enable inputs (LE) and two output enable inputs  $(\overline{OE})$ . The device can be used as two 8-bit latches or one 16-bit latch.

While the LE input is held at a high level, the Q outputs will follow the data inputs precisely. When the LE is taken low, the Q outputs will be latched precisely at the levels set up at the D inputs. While the (OE) input is low, the outputs will be in a normal logic state (high or low logic level) and while OE is in high level the outputs will be in a high impedance state.

This device is designed to interface directly High Speed CMOS systems with TTL and NMOS components.

All inputs and outputs are equipped with protection circuits against static discharge, giving them 2KV ESD immunity and transient excess voltage.

#### **ORDER CODES**

| PACKAGE | TUBE | T & R         |  |  |  |

|---------|------|---------------|--|--|--|

| TSSOP   |      | 74ACT16373TTR |  |  |  |

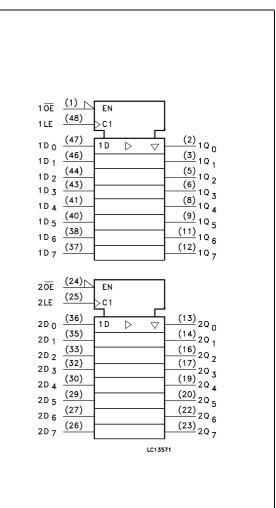

#### **PIN CONNECTION**

| 1                     | ] 48 1LE              |

|-----------------------|-----------------------|

| 1 Q <sub>0</sub> 2 [  | ] 47 1 D <sub>0</sub> |

| 1 Q <sub>1</sub> 3 [  | ] 46 1 D <sub>1</sub> |

| GND ₄[                | ] 45 GND              |

| 1 Q 2 5 [             | ] 44 1 D 2            |

| 1 Q 3 6 [             | ] 43 1 D 3            |

| V <sub>сс</sub> 7 [   | ] 42 V <sub>CC</sub>  |

| 1 Q <sub>4</sub> в [  | ]41 1D4               |

| 1 Q 5 9 [             | ]₄0 1D <sub>5</sub>   |

| GND 10                | ] 39 GND              |

| 1 Q <sub>6</sub> 11 [ | ] 38 1 D <sub>6</sub> |

| 1 Q <sub>7</sub> 12 [ | ] 37 1 D 7            |

| 2 Q <sub>0</sub> 13 [ | ] 36 2 D <sub>0</sub> |

| 2Q1 14 [              | ] 35 2 D <sub>1</sub> |

| GND 15 [              | ] 34 GND              |

| 2Q3 16                | ] 33 2 D 2            |

| 2 Q 3 17 [            | ] 32 2 D 3            |

| V <sub>CC</sub> 18 [  | ] 31 V <sub>CC</sub>  |

| 2 Q 4 19 [            | ] 30 2 D 4            |

| 2 Q 5 20 [            | ] 29 2 D 5            |

| GND 21 [              | ] 28 GND              |

| 2 Q <sub>6</sub> 22 [ | ] 27 2 D <sub>6</sub> |

| 2 Q <sub>7</sub> 23 [ | ] 26 2 D 7            |

| 20E 24 [              | ] 25 2LE              |

|                       | PC12000               |

|                       |                       |

February 2003

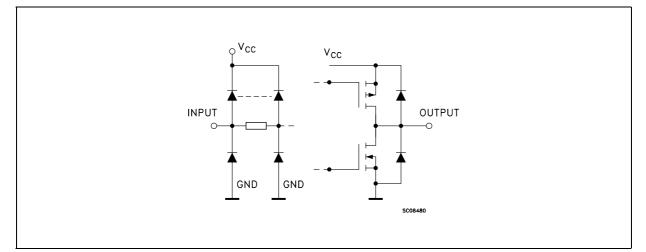

#### INPUT AND OUTPUT EQUIVALENT CIRCUIT

#### **PIN DESCRIPTION**

| PIN No                            | SYMBOL            | NAME AND FUNCTION                           |

|-----------------------------------|-------------------|---------------------------------------------|

| 1                                 | 1 <mark>0E</mark> | 3 State Output Enable<br>Input (Active LOW) |

| 2, 3, 5, 6, 8, 9,<br>11, 12       | 1Q0 to 1Q7        | 3-State Outputs                             |

| 13, 14, 16, 17,<br>19, 20, 22, 23 | 2Q0 to 2Q7        | 3-State Outputs                             |

| 24                                | 2 <mark>0E</mark> | 3 State Output Enable<br>Input (Active LOW) |

| 25                                | 2LE               | Latch Enable Input                          |

| 36, 35, 33, 32,<br>30, 29, 27, 26 | 2D0 to 2D7        | Data Inputs                                 |

| 47, 46, 44, 43,<br>41, 40, 38, 37 | 1D0 to 1D7        | Data Inputs                                 |

| 48                                | 1LE               | Latch Enable Input                          |

| 4, 10, 15, 21,<br>28, 34, 39, 45  | GND               | Ground (0V)                                 |

| 7, 18, 31, 42                     | V <sub>CC</sub>   | Positive Supply Voltage                     |

#### **TRUTH TABLE**

|    | INPUTS |   |             |  |  |  |  |

|----|--------|---|-------------|--|--|--|--|

| OE | LE     | D | Q           |  |  |  |  |

| Н  | Х      | Х | Z           |  |  |  |  |

| L  | L      | Х | NO CHANGE * |  |  |  |  |

| L  | Н      | L | L           |  |  |  |  |

| L  | Н      | Н | Н           |  |  |  |  |

X : Don't Care

Z : High Impedance

\* : Q outputs are latched at the time when the LE input is taken low

logic level.

#### **IEC LOGIC SYMBOLS**

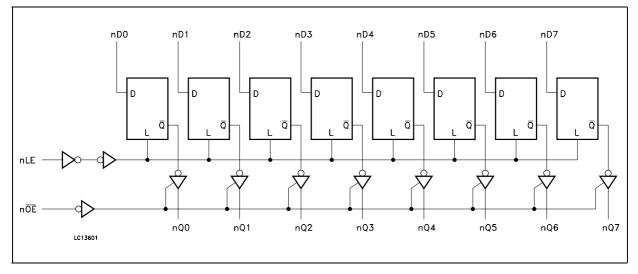

#### LOGIC DIAGRAM

This logic diagram has not to be used to estimate propagation delays

#### **ABSOLUTE MAXIMUM RATINGS**

| Symbol                        | Parameter                            | Value                         | Unit |

|-------------------------------|--------------------------------------|-------------------------------|------|

| V <sub>CC</sub>               | Supply Voltage                       | -0.5 to +7                    | V    |

| VI                            | DC Input Voltage                     | -0.5 to V <sub>CC</sub> + 0.5 | V    |

| V <sub>O</sub>                | DC Output Voltage                    | -0.5 to V <sub>CC</sub> + 0.5 | V    |

| I <sub>IK</sub>               | DC Input Diode Current               | ± 20                          | mA   |

| I <sub>OK</sub>               | DC Output Diode Current              | ± 20                          | mA   |

| Ι <sub>Ο</sub>                | DC Output Current                    | ± 50                          | mA   |

| $\rm I_{CC}$ or $\rm I_{GND}$ | DC V <sub>CC</sub> or Ground Current | ± 400                         | mA   |

| T <sub>stg</sub>              | Storage Temperature                  | -65 to +150                   | °C   |

| ΤL                            | Lead Temperature (10 sec)            | 300                           | °C   |

Absolute Maximum Ratings are those values beyond which damage to the device may occur. Functional operation under these conditions is not implied.

#### **RECOMMENDED OPERATING CONDITIONS**

| Symbol          | Parameter                                                | Value                | Unit |

|-----------------|----------------------------------------------------------|----------------------|------|

| V <sub>CC</sub> | Supply Voltage                                           | 4.5 to 5.5           | V    |

| VI              | Input Voltage                                            | 0 to V <sub>CC</sub> | V    |

| Vo              | Output Voltage                                           | 0 to V <sub>CC</sub> | V    |

| T <sub>op</sub> | Operating Temperature                                    | -55 to 125           | °C   |

| dt/dv           | Input Rise and Fall Time $V_{CC}$ = 4.5 to 5.5V (note 1) | 8                    | ns/V |

1) V<sub>IN</sub> from 0.8V to 2.0V

#### DC SPECIFICATIONS

|                  |                                             | Test Condition  |                                                                         | Value |         |       |        |      |        |       |      |

|------------------|---------------------------------------------|-----------------|-------------------------------------------------------------------------|-------|---------|-------|--------|------|--------|-------|------|

| Symbol           | Parameter                                   | V <sub>CC</sub> |                                                                         | Т     | A = 25° | С     | -40 to | 85°C | -55 to | 125°C | Unit |

|                  |                                             | (Ŭ)             |                                                                         | Min.  | Тур.    | Max.  | Min.   | Max. | Min.   | Max.  |      |

| VIH              | High Level Input                            | 4.5             | V <sub>O</sub> = 0.1 V or                                               | 2.0   | 1.5     |       | 2.0    |      | 2.0    |       |      |

|                  | Voltage                                     | 5.5             | V <sub>CC</sub> -0.1V                                                   | 2.0   | 1.5     |       | 2.0    |      | 2.0    |       | V    |

| V <sub>IL</sub>  | Low Level Input                             | 4.5             | V <sub>O</sub> = 0.1 V or                                               |       | 1.5     | 0.8   |        | 0.8  |        | 0.8   |      |

|                  | Voltage                                     | 5.5             | V <sub>CC</sub> -0.1V                                                   |       | 1.5     | 0.8   |        | 0.8  |        | 0.8   |      |

| V <sub>OH</sub>  | High Level Output                           | 4.5             | I <sub>O</sub> =-50 μA                                                  | 4.4   | 4.49    |       | 4.4    |      | 4.4    |       | V    |

|                  | Voltage                                     | 5.5             | I <sub>O</sub> =-50 μA                                                  | 5.4   | 5.49    |       | 5.4    |      | 5.4    |       | 1    |

|                  |                                             | 4.5             | I <sub>O</sub> =-24 mA                                                  | 3.86  |         |       | 3.76   |      | 3.7    |       |      |

|                  |                                             | 5.5             | I <sub>O</sub> =-24 mA                                                  | 4.86  |         |       | 4.76   |      | 4.7    |       | l    |

| V <sub>OL</sub>  | Low Level Output                            | 4.5             | I <sub>O</sub> =50 μA                                                   |       | 0.001   | 0.1   |        | 0.1  |        | 0.1   | v    |

|                  | Voltage                                     | 5.5             | I <sub>O</sub> =50 μA                                                   |       | 0.001   | 0.1   |        | 0.1  |        | 0.1   | v    |

|                  |                                             | 4.5             | I <sub>O</sub> =24 mA                                                   |       |         | 0.36  |        | 0.44 |        | 0.5   | l    |

|                  |                                             | 5.5             | I <sub>O</sub> =24 mA                                                   |       |         | 0.36  |        | 0.44 |        | 0.5   | l    |

| I                | Input Leakage Cur-<br>rent                  | 5.5             | $V_{I} = V_{CC}$ or GND                                                 |       |         | ± 0.1 |        | ± 1  |        | ± 1   | μA   |

| I <sub>OZ</sub>  | High Impedance<br>Output Leakege<br>Current | 5.5             | $V_{I} = V_{IH} \text{ or } V_{IL}$<br>$V_{O} = V_{CC} \text{ or } GND$ |       |         | ± 0.5 |        | ± 5  |        | ± 10  | μA   |

| I <sub>CCT</sub> | Max I <sub>CC</sub> /Input                  | 5.5             | $V_{I} = V_{CC} - 2.1V$                                                 |       | 0.6     |       |        | 1.5  |        | 1.6   | mA   |

| I <sub>CC</sub>  | Quiescent Supply<br>Current                 | 5.5             | $V_{I} = V_{CC}$ or GND                                                 |       |         | 8     |        | 80   |        | 160   | μA   |

| I <sub>OLD</sub> | Dynamic Output                              | 5.5             | $V_{OLD} = 1.65 \text{ V max}$                                          |       |         |       |        | 75   |        | 50    | mA   |

| I <sub>OHD</sub> | Current (note 1, 2)                         | 5.5             | V <sub>OHD</sub> = 3.85 V min                                           |       |         |       |        | -75  |        | -50   | mA   |

57

1) Maximum test duration 2ms, one output loaded at time 2) Incident wave switching is guaranteed on transmission lines with impedances as low as  $50\Omega$

|                   |                                    | ٦                  | est Condition | Value |         |      |        |      |        |       |      |

|-------------------|------------------------------------|--------------------|---------------|-------|---------|------|--------|------|--------|-------|------|

| Symbol            | Parameter                          | v <sub>cc</sub>    |               | т     | A = 25° | С    | -40 to | 85°C | -55 to | 125°C | Unit |

|                   |                                    | (V)                |               | Min.  | Тур.    | Max. | Min.   | Max. | Min.   | Max.  |      |

| t <sub>PLH</sub>  | Propagation Delay                  | 5.0 <sup>(*)</sup> |               |       | 4.2     | 6.5  |        | 12.8 |        | 13.7  | ns   |

| t <sub>PHL</sub>  | Time LE to Q                       | 5.0( )             |               |       | 5.0     | 7.7  |        | 12.2 |        | 13.0  | ns   |

| t <sub>PLH</sub>  | Propagation Delay                  | 5.0 <sup>(*)</sup> |               |       | 4.1     | 6.3  |        | 11.1 |        | 11.8  | 20   |

| t <sub>PHL</sub>  | Time D to Q                        | 5.0( )             |               |       | 5.3     | 8.5  |        | 12.3 |        | 13.0  | ns   |

| t <sub>PZL</sub>  | Output Enable                      | 5.0 <sup>(*)</sup> |               |       | 5.7     | 6.5  |        | 14.2 |        | 15.1  | 20   |

| t <sub>PZH</sub>  | Time                               | 5.0( /             |               |       | 5.0     | 7.7  |        | 12.1 |        | 13.0  | ns   |

| t <sub>PLZ</sub>  | Output Disable                     | 5.0 <sup>(*)</sup> |               |       | 5.6     | 8.2  |        | 9.4  |        | 9.8   | ns   |

| t <sub>PHZ</sub>  | Time                               | 5.0( /             |               |       | 5.0     | 7.0  |        | 10.7 |        | 11.0  | 115  |

| t <sub>W(H)</sub> | LE Minimum Pulse<br>Width HIGH     | 5.0 <sup>(*)</sup> |               | 2.2   | 1.7     |      | 2.6    |      | 2.6    |       | ns   |

| t <sub>s</sub>    | Setup Time D to<br>LE, HIGH or LOW | 5.0 <sup>(*)</sup> |               | 1.2   | <1.0    |      | 1.4    |      | 1.4    |       | ns   |

| t <sub>h</sub>    | Hold Time D to LE,<br>HIGH or LOW  | 5.0 <sup>(*)</sup> |               | 1.3   | <1.0    |      | 1.6    |      | 1.6    |       | ns   |

#### AC ELECTRICAL CHARACTERISTICS (CL = 50 pF, RL = 500 $\Omega$ , Input tr = tf = 3ns)

(\*) Voltage range is  $5.0V\pm0.5V$

#### **CAPACITIVE CHARACTERISTICS**

|                  |                                              | Test Condition |                         | Value |         |      |        |      |        |       |      |

|------------------|----------------------------------------------|----------------|-------------------------|-------|---------|------|--------|------|--------|-------|------|

| Symbol           | Parameter                                    | Vcc            | v <sub>cc</sub>         |       | A = 25° | С    | -40 to | 85°C | -55 to | 125°C | Unit |

|                  |                                              | (V)            |                         | Min.  | Тур.    | Max. | Min.   | Max. | Min.   | Max.  |      |

| C <sub>IN</sub>  | Input Capacitance                            | 5.0            |                         |       | 3.5     |      |        |      |        |       | pF   |

| C <sub>OUT</sub> | Output Capaci-<br>tance                      | 5.0            |                         |       | 11      |      |        |      |        |       | pF   |

| C <sub>PD</sub>  | Power Dissipation<br>Capacitance (note<br>1) | 5.0            | f <sub>IN</sub> = 10MHz |       | 31      |      |        |      |        |       | pF   |

1)  $C_{PD}$  is defined as the value of the IC's internal equivalent capacitance which is calculated from the operating current consumption without load. (Refer to Test Circuit). Average operating current can be obtained by the following equation.  $C_{C(opr)} = C_{PD} \times V_{CC} \times f_{IN} + I_{CC}/16$  (per circuit)

57

#### 74ACT16373

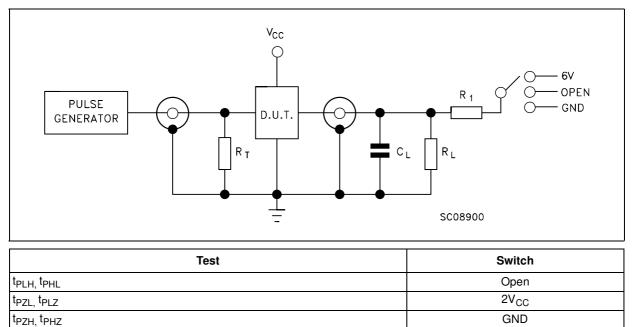

#### **TEST CIRCUIT**

$\begin{array}{l} C_L = 50 pF \text{ or equivalent (includes jig and probe capacitance)} \\ R_L = R_1 = 500 \Omega \text{ or equivalent} \\ R_T = Z_{OUT} \text{ of pulse generator (typically 50 \Omega)} \end{array}$

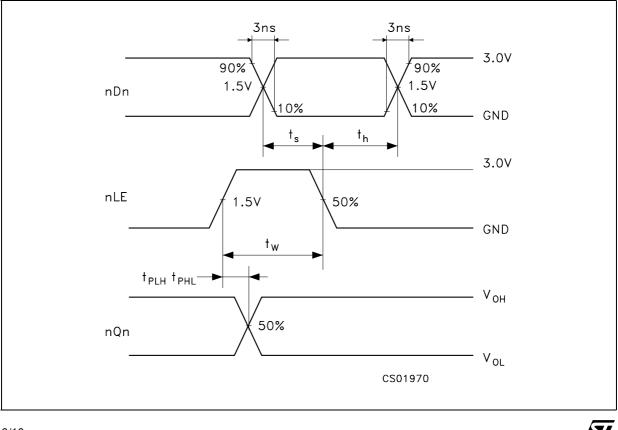

#### WAVEFORM 1: PROPAGATION DELAYS, PULSE WIDTH, SETUP AND HOLD TIMES (f=1MHz; 50% duty cycle)

6/10

57

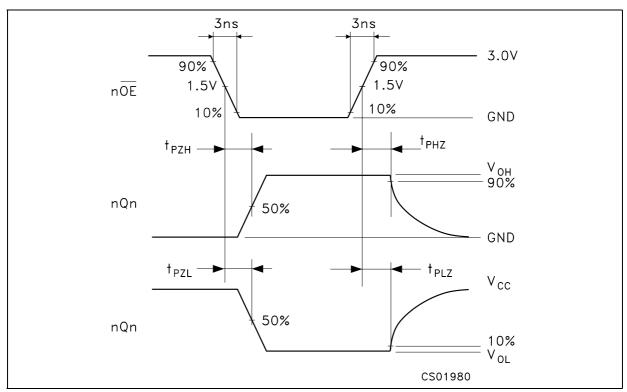

WAVEFORM 2: OUTPUT ENABLE AND DISABLE TIMES (f=1MHz; 50% duty cycle)

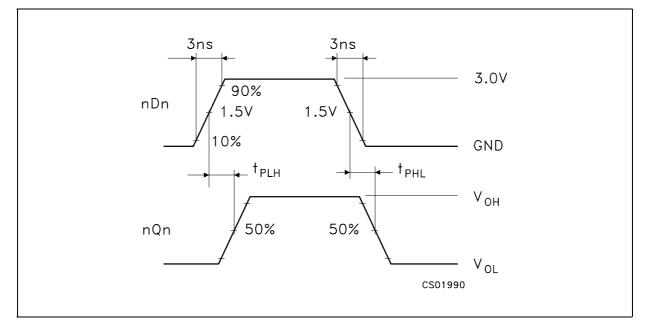

#### WAVEFORM 3: PROPAGATION DELAYS TIME (f=1MHz; 50% duty cycle)

#### 74ACT16373

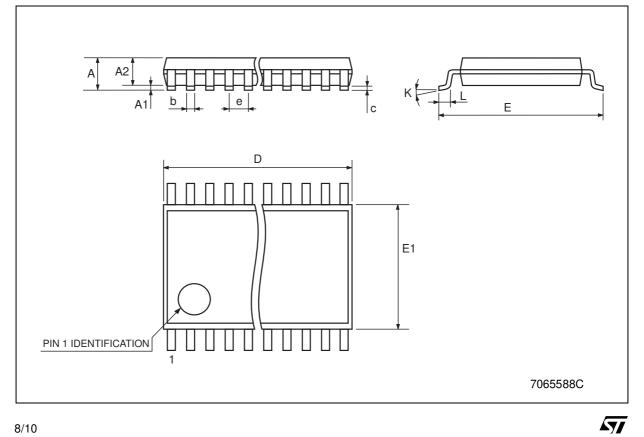

|       | TSSOP48 MECHANICAL DATA |         |      |        |            |        |  |  |  |  |

|-------|-------------------------|---------|------|--------|------------|--------|--|--|--|--|

| DIM.  |                         | mm.     |      | inch   |            |        |  |  |  |  |

| Diwi. | MIN.                    | ТҮР     | MAX. | MIN.   | TYP.       | MAX.   |  |  |  |  |

| А     |                         |         | 1.2  |        |            | 0.047  |  |  |  |  |

| A1    | 0.05                    |         | 0.15 | 0.002  |            | 0.006  |  |  |  |  |

| A2    |                         | 0.9     |      |        | 0.035      |        |  |  |  |  |

| b     | 0.17                    |         | 0.27 | 0.0067 |            | 0.011  |  |  |  |  |

| с     | 0.09                    |         | 0.20 | 0.0035 |            | 0.0079 |  |  |  |  |

| D     | 12.4                    |         | 12.6 | 0.488  |            | 0.496  |  |  |  |  |

| E     |                         | 8.1 BSC |      |        | 0.318 BSC  |        |  |  |  |  |

| E1    | 6.0                     |         | 6.2  | 0.236  |            | 0.244  |  |  |  |  |

| е     |                         | 0.5 BSC |      |        | 0.0197 BSC |        |  |  |  |  |

| К     | 0°                      |         | 8°   | 0°     |            | 8°     |  |  |  |  |

| L     | 0.50                    |         | 0.75 | 0.020  |            | 0.030  |  |  |  |  |

8/10

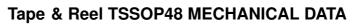

| DIM.  |      | mm. |      |       | inch |        |

|-------|------|-----|------|-------|------|--------|

| DIVI. | MIN. | ТҮР | MAX. | MIN.  | TYP. | MAX.   |

| А     |      |     | 330  |       |      | 12.992 |

| С     | 12.8 |     | 13.2 | 0.504 |      | 0.519  |

| D     | 20.2 |     |      | 0.795 |      |        |

| Ν     | 60   |     |      | 2.362 |      |        |

| Т     |      |     | 30.4 |       |      | 1.197  |

| Ao    | 8.7  |     | 8.9  | 0.343 |      | 0.350  |

| Bo    | 13.1 |     | 13.3 | 0.516 |      | 0.524  |

| Ko    | 1.5  |     | 1.7  | 0.059 |      | 0.067  |

| Po    | 3.9  |     | 4.1  | 0.153 |      | 0.161  |

| Р     | 11.9 |     | 12.1 | 0.468 |      | 0.476  |

Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics.

© The ST logo is a registered trademark of STMicroelectronics

© 2003 STMicroelectronics - Printed in Italy - All Rights Reserved STMicroelectronics GROUP OF COMPANIES Australia - Brazil - Canada - China - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan - Malaysia - Malta - Morocco Singapore - Spain - Sweden - Switzerland - United Kingdom - United States. © http://www.st.com