Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

August 1999 Revised March 2005

#### 74ACT533

# **Octal Transparent Latch with 3-STATE Outputs**

#### **General Description**

The ACT533 consists of eight latches with 3-STATE outputs for bus organized system applications. The flip-flops appear transparent to the data when Latch Enable (LE) is HIGH. When LE is low, the data satisfying the input timing requirements is latched. Data appears on the bus when the Output Enable (OE) is LOW. When OE is HIGH, the bus output is in the high impedance state.

#### **Features**

- I<sub>CC</sub> and I<sub>OZ</sub> reduced by 50%

- Eight latches in a single package

- 3-STATE outputs drive bus lines or buffer memory address registers

- Outputs source/sink 24 mA

- Inverted version of the ACT373

- TTL-compatible inputs

#### **Ordering Code:**

| Order Number | Package Number | Package Description                                                         |  |  |  |

|--------------|----------------|-----------------------------------------------------------------------------|--|--|--|

| 74ACT533SC   | M20B           | 20-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-013, 0.300" Wide  |  |  |  |

| 74ACT533MTC  | MTC20          | 20-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 4.4mm Wide |  |  |  |

| 74ACT533PC   | N20A           | 20-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300" Wide      |  |  |  |

Device also available in Tape and Reel. Specify by appending suffix letter "X" to the ordering code

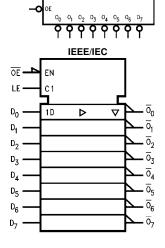

#### **Logic Symbols**

#### **Connection Diagram**

#### **Pin Descriptions**

| Pin Names                           | Description           |  |  |

|-------------------------------------|-----------------------|--|--|

| D <sub>0</sub> –D <sub>7</sub>      | Data Inputs           |  |  |

| LE                                  | Latch Enable Input    |  |  |

| ŌĒ                                  | Output Enable Input   |  |  |

| $\overline{O}_0$ – $\overline{O}_7$ | 3-STATE Latch Outputs |  |  |

FACT™ is a trademark of Fairchild Semiconductor Corporation.

#### **Functional Description**

The ACT533 contains eight D-type latches with 3-STATE standard outputs. When the Latch Enable (LE) input is HIGH, data on the  $D_n$  inputs enters the latches. In this condition the latches are transparent, i.e., a latch output will change state each time its D input changes. When LE is LOW, the latches store the information that was present on the D inputs at setup time preceding the HIGH-to-LOW transition of LE. The 3-STATE standard outputs are controlled by the Output Enable  $(\overline{OE})$  input. When  $\overline{OE}$  is  $\underline{LOW}$ , the standard outputs are in the 2-state mode. When  $\overline{\text{OE}}$  is HIGH, the standard outputs are in the high impedance mode but this does not interfere with entering new data into the latches.

#### **Truth Table**

|    | Outputs |                |                  |

|----|---------|----------------|------------------|

| LE | ŌĒ      | D <sub>n</sub> | $\overline{O}_n$ |

| Х  | Н       | Х              | Z                |

| Н  | L       | L              | Н                |

| Н  | L       | Н              | L                |

| L  | L       | Х              | $\overline{O}_0$ |

- H = HIGH Voltage Level

- L = LOW Voltage Level

Z = High Impedance

X = Immaterial

- $\overline{O}_0$  = Previous  $\overline{O}_0$  before HIGH-to-LOW transition of Latch Enable

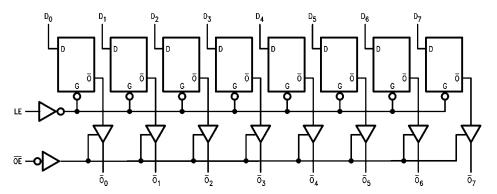

#### **Logic Diagram**

Please note that this diagram is provided only for the understanding of logic operations and should not be used to estimate propagation delays.

#### **Absolute Maximum Ratings**(Note 1)

Supply Voltage ( $V_{CC}$ ) - 0.5V to + 7.0V

DC Input Diode Current (I<sub>IK</sub>)

$$\begin{split} &V_I = -~0.5V & -~20~\text{mA} \\ &V_I = V_{CC} + 0.5V & +~20~\text{mA} \\ &DC~\text{Input Voltage}~(V_I) & -0.5V~\text{to}~V_{CC} + 0.5V \end{split}$$

DC Output Diode Current (I<sub>OK</sub>)

$$\begin{split} \text{V}_{\text{O}} &= -0.5 \text{V} & -20 \text{ mA} \\ \text{V}_{\text{O}} &= \text{V}_{\text{CC}} + 0.5 \text{V} & +20 \text{ mA} \end{split}$$

DC Output Voltage ( $V_O$ ) -0.5V to  $V_{CC} + 0.5V$

DC Output Source

or Sink Current ( $I_O$ )  $\pm$  50 mA

DC V<sub>CC</sub> or Ground Current

per Output Pin ( $I_{CC}$  or  $I_{GND}$ )  $\pm$  50 mA

Storage Temperature ( $T_{STG}$ )  $-65^{\circ}C$  to  $+150^{\circ}C$

DC Latchup Source

or Sink Current ± 300 mA

Junction Temperature (T<sub>J</sub>)

PDIP 140°C

# Recommended Operating Conditions

Minimum Input Edge Rate  $\Delta V/\Delta t$

V<sub>IN</sub> from 0.8V to 2.0V

V<sub>CC</sub> @ 4.5V, 5.5V 125 mV/ns

Note 1: Absolute maximum ratings are those values beyond which damage to the device may occur. The databook specifications should be met, without exception, to ensure that the system design is reliable over its power supply, temperature, and output/input loading variables. Fairchild does not recommend operation of FACTTU circuits outside databook specifications.

#### **DC Electrical Characteristics**

| Symbol           | Parameter               | v <sub>cc</sub> | $T_A = +25^{\circ}C$  |       | $T_A = -40^{\circ}C \text{ to } +85^{\circ}C$ | Units      | Conditions                        |  |

|------------------|-------------------------|-----------------|-----------------------|-------|-----------------------------------------------|------------|-----------------------------------|--|

| Syllibol         |                         | (V)             | Typ Guaranteed Limits |       | Onns                                          | Conditions |                                   |  |

| V <sub>IH</sub>  | Minimum HIGH Level      | 4.5             | 1.5                   | 2.0   | 2.0                                           | V          | V <sub>OUT</sub> = 0.1V           |  |

|                  | Input Voltage           | 5.5             | 1.5                   | 2.0   | 2.0                                           | V          | or V <sub>CC</sub> – 0.1V         |  |

| V <sub>IL</sub>  | Maximum LOW Level       | 4.5             | 1.5                   | 0.8   | 0.8                                           | V          | V <sub>OUT</sub> = 0.1V           |  |

|                  | Input Voltage           | 5.5             | 1.5                   | 0.8   | 0.8                                           | V          | or V <sub>CC</sub> – 0.1V         |  |

| V <sub>OH</sub>  | Minimum HIGH Level      | 4.5             | 4.49                  | 4.4   | 4.4                                           | V          | I <sub>OUT</sub> = -50 μA         |  |

|                  | Output Voltage          | 5.5             | 5.49                  | 5.4   | 5.4                                           | V          |                                   |  |

|                  |                         |                 |                       |       |                                               |            | $V_{IN} = V_{IL}$ or $V_{IH}$     |  |

|                  |                         | 4.5             |                       | 3.86  | 3.76                                          | V          | $I_{OH} = -24 \text{ mA}$         |  |

|                  |                         | 5.5             |                       | 4.86  | 4.76                                          |            | I <sub>OH</sub> = -24 mA (Note 2) |  |

| V <sub>OL</sub>  | Maximum LOW Level       | 4.5             | 0.001                 | 0.1   | 0.1                                           | V          | I <sub>OUT</sub> = 50 μA          |  |

|                  | Output Voltage          | 5.5             | 0.001                 | 0.1   | 0.1                                           | V          |                                   |  |

|                  |                         |                 |                       |       |                                               |            | $V_{IN} = V_{IL}$ or $V_{IH}$     |  |

|                  |                         | 4.5             |                       | 0.36  | 0.44                                          | V          | I <sub>OL</sub> = 24 mA           |  |

|                  |                         | 5.5             |                       | 0.36  | 0.44                                          |            | I <sub>OL</sub> = 24 mA (Note 2)  |  |

| I <sub>IN</sub>  | Maximum Input           | 5.5             |                       | ±0.1  | ±1.0                                          | μА         | $V_I = V_{CC}$ , GND              |  |

|                  | Leakage Current         |                 |                       |       |                                               |            |                                   |  |

| l <sub>OZ</sub>  | Maximum 3-STATE         | 5.5             |                       | ±0.25 | ±2.5                                          | ^          | $V_I = V_{IL}, V_{IH}$            |  |

|                  | Leakage Current         | 5.5             |                       | ±0.25 | ±2.5                                          | μА         | $V_O = V_{CC}$ , GND              |  |

| I <sub>CCT</sub> | Maximum                 | 5.5             | 0.6                   |       | 1.5                                           | mA         | $V_{I} = V_{CC} - 2.1V$           |  |

|                  | I <sub>CC</sub> /Input  |                 |                       |       |                                               |            |                                   |  |

| I <sub>OLD</sub> | Minimum Dynamic         | 5.5             |                       |       | 75                                            | mA         | V <sub>OLD</sub> = 1.65V Max      |  |

| I <sub>OHD</sub> | Output Current (Note 3) | 5.5             |                       |       | -75                                           | mA         | V <sub>OHD</sub> = 3.85V Min      |  |

| I <sub>CC</sub>  | Maximum Quiescent       |                 |                       | 4.0   | 40.0                                          | μА         | $V_{IN} = V_{CC}$                 |  |

|                  | Supply Current          | 5.5             |                       |       | 40.0                                          |            | or GND                            |  |

Note 2: All outputs loaded; thresholds on input associated with output under test.

Note 3: Maximum test duration 2.0 ms, one output loaded at a time.

## **AC Electrical Characteristics**

| Symbol                              | Parameter                        | V <sub>CC</sub><br>(V) | T <sub>A</sub> = + 25°C<br>C <sub>L</sub> = 50 pF |     |      | $T_A = -40$ °C to $+85$ °C $C_L = 50$ pF |      | Units |

|-------------------------------------|----------------------------------|------------------------|---------------------------------------------------|-----|------|------------------------------------------|------|-------|

|                                     |                                  | (Note 4)               | Min                                               | Тур | Max  | Min                                      | Max  |       |

| t <sub>PHL</sub>                    | Propagation Delay                | 5.0                    | 2.0                                               | 6.0 | 8.0  | 2.0                                      | 8.5  | ns    |

| t <sub>PLH</sub>                    | D <sub>n</sub> to O <sub>n</sub> |                        |                                                   |     |      |                                          |      |       |

| t <sub>PHL</sub>                    | Propagation Delay                | 5.0                    | 2.5                                               | 7.0 | 9.0  | 2.5                                      | 9.5  | ns    |

| t <sub>PLH</sub>                    | LE to O <sub>n</sub>             |                        |                                                   |     |      |                                          |      |       |

| t <sub>PZL</sub> , t <sub>PZH</sub> | Output Enable Time               | 5.0                    | 2.0                                               | 7.0 | 9.0  | 2.0                                      | 9.5  | ns    |

| t <sub>PHZ</sub> , t <sub>PLZ</sub> | Output Disable Time              | 5.0                    | 1.0                                               | 8.0 | 10.0 | 1.0                                      | 10.5 | ns    |

Note 4: Voltage Range 5.0 is 5.0V ± 0.5V.

## **AC Operating Requirements**

| Symbol         | Parameter               | V <sub>CC</sub><br>(V) | T <sub>A</sub> = + 25°C<br>C <sub>L</sub> = 50 pF |       | $T_A = -40$ °C to $+85$ °C<br>$C_L = 50$ pF | Units |

|----------------|-------------------------|------------------------|---------------------------------------------------|-------|---------------------------------------------|-------|

|                |                         | (Note 5)               | Тур                                               | Guara | nteed Minimum                               |       |

| t <sub>S</sub> | Setup Time, HIGH or LOW | 5.0                    | 0                                                 | 3.0   | 3.0                                         | ns    |

|                | D <sub>n</sub> to LE    |                        |                                                   |       |                                             |       |

| t <sub>H</sub> | Hold Time, HIGH or LOW  | 5.0                    | 0                                                 | 1.5   | 1.5                                         | ns    |

|                | D <sub>n</sub> to LE    |                        |                                                   |       |                                             |       |

| t <sub>W</sub> | LE Pulse Width, HIGH    | 5.0                    | 2.0                                               | 4.0   | 4.0                                         | ns    |

Note 5: Voltage Range 5.0 is 5.0V  $\pm$  0.5V.

#### Capacitance

| Symbol          | Parameter                     | Тур | Units | Conditions             |

|-----------------|-------------------------------|-----|-------|------------------------|

| C <sub>IN</sub> | Input Capacitance             | 4.5 | pF    | V <sub>CC</sub> = OPEN |

| C <sub>PD</sub> | Power Dissipation Capacitance | 40  | pF    | V <sub>CC</sub> = 5.0V |

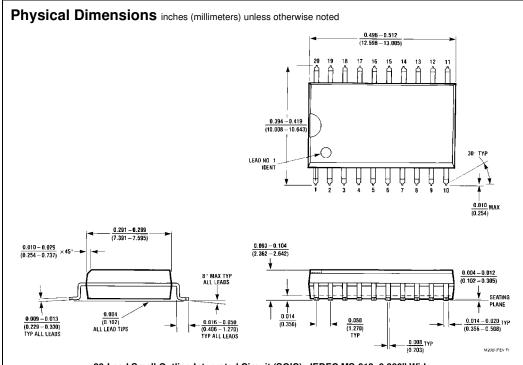

20-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-013, 0.300" Wide Package Number M20B

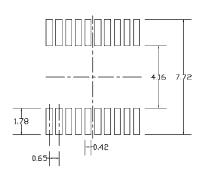

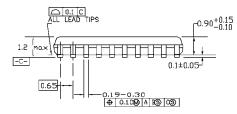

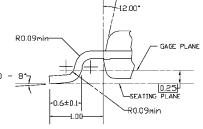

### Physical Dimensions inches (millimeters) unless otherwise noted (Continued)

LAND PATTERN RECOMMENDATION

DIMENSIONS ARE IN MILLIMETERS

#### NOTES:

- A. CONFORMS TO JEDEC REGISTRATION MID-153, VARIATION AC, REF NOTE 6. DATE 7/93.

- B. DIMENSIONS ARE IN MILLIMETERS.

- C. DIMENSIONS ARE EXCLUSIVE OF BURRS, MOLDS FLASH, AND THE BAR EXTRUSIONS.

- D. DIMENSIONS AND TOLERANCES PER ANSI Y14.5M, 1982.

# SEE DETAIL A 0.09-0.20<sup>3</sup>

DETAIL A

#### MTC20REVD1

20-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 4.4mm Wide Package Number MTC20

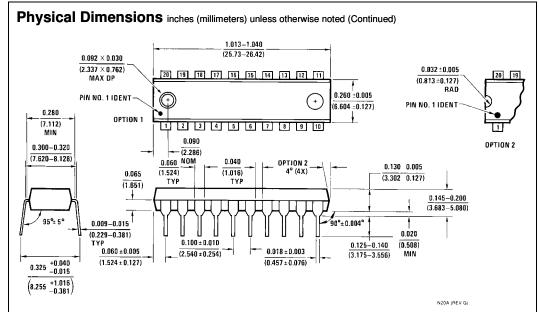

20-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300" Wide Package Number N20A

Fairchild does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and Fairchild reserves the right at any time without notice to change said circuitry and specifications.

#### LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component in any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

www.fairchildsemi.com