Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

### Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

#### Important notice

Dear Customer,

On 7 February 2017 the former NXP Standard Product business became a new company with the tradename **Nexperia**. Nexperia is an industry leading supplier of Discrete, Logic and PowerMOS semiconductors with its focus on the automotive, industrial, computing, consumer and wearable application markets

In data sheets and application notes which still contain NXP or Philips Semiconductors references, use the references to Nexperia, as shown below.

Instead of <a href="http://www.nxp.com">http://www.nxp.com</a>, <a href="http://www.semiconductors.philips.com/">http://www.nxp.com</a>, <a href="http://www.nexperia.com">http://www.nexperia.com</a>, <a href="http://www.nexperia.com">http://www.nexperia.com</a>)

Instead of sales.addresses@www.nxp.com or sales.addresses@www.semiconductors.philips.com, use salesaddresses@nexperia.com (email)

Replace the copyright notice at the bottom of each page or elsewhere in the document, depending on the version, as shown below:

- © NXP N.V. (year). All rights reserved or © Koninklijke Philips Electronics N.V. (year). All rights reserved

Should be replaced with:

- © Nexperia B.V. (year). All rights reserved.

If you have any questions related to the data sheet, please contact our nearest sales office via e-mail or telephone (details via **salesaddresses@nexperia.com**). Thank you for your cooperation and understanding,

Kind regards,

Team Nexperia

## **74AVCH2T45**

# Dual-bit, dual-supply voltage level translator/transceiver; 3-state

Rev. 6 — 2 April 2013

**Product data sheet**

### 1. General description

The 74AVCH2T45 is a dual bit, dual supply transceiver that enables bidirectional level translation. It features two data input-output ports (nA and nB), a direction control input (DIR) and dual supply pins ( $V_{CC(A)}$  and  $V_{CC(B)}$ ). Both  $V_{CC(A)}$  and  $V_{CC(B)}$  can be supplied at any voltage between 0.8 V and 3.6 V making the device suitable for translating between any of the low voltage nodes (0.8 V, 1.2 V, 1.5 V, 1.8 V, 2.5 V and 3.3 V). Pins nA and DIR are referenced to  $V_{CC(A)}$  and pins nB are referenced to  $V_{CC(B)}$ . A HIGH on DIR allows transmission from nA to nB and a LOW on DIR allows transmission from nB to nA.

The device is fully specified for partial power-down applications using  $I_{OFF}$ . The  $I_{OFF}$  circuitry disables the output, preventing any damaging backflow current through the device when it is powered down. In suspend mode when either  $V_{CC(A)}$  or  $V_{CC(B)}$  are at GND level, both A and B are in the high-impedance OFF-state.

The 74AVCH2T45 has active bus hold circuitry which is provided to hold unused or floating data inputs at a valid logic level. This feature eliminates the need for external pull-up or pull-down resistors.

#### 2. Features and benefits

- Wide supply voltage range:

- ◆ V<sub>CC(A)</sub>: 0.8 V to 3.6 V

- ◆ V<sub>CC(B)</sub>: 0.8 V to 3.6 V

- High noise immunity

- Complies with JEDEC standards:

- ◆ JESD8-12 (0.8 V to 1.3 V)

- ◆ JESD8-11 (0.9 V to 1.65 V)

- ◆ JESD8-7 (1.2 V to 1.95 V)

- ◆ JESD8-5 (1.8 V to 2.7 V)

- ◆ JESD8-B (2.7 V to 3.6 V)

- ESD protection:

- HBM JESD22-A114F Class 3B exceeds 8000 V

- MM JESD22-A115-A exceeds 200 V

- CDM JESD22-C101C exceeds 1000 V

- Maximum data rates:

- ◆ 500 Mbps (1.8 V to 3.3 V translation)

- ◆ 320 Mbps (< 1.8 V to 3.3 V translation)</p>

- ◆ 320 Mbps (translate to 2.5 V or 1.8 V)

#### Dual-bit, dual-supply voltage level translator/transceiver; 3-state

- ◆ 280 Mbps (translate to 1.5 V)

- ◆ 240 Mbps (translate to 1.2 V)

- Suspend mode

- Bus hold on data inputs

- Latch-up performance exceeds 100 mA per JESD 78 Class II

- Inputs accept voltages up to 3.6 V

- Low noise overshoot and undershoot < 10 % of V<sub>CC</sub>

- I<sub>OFF</sub> circuitry provides partial Power-down mode operation

- Multiple package options

- Specified from -40 °C to +85 °C and -40 °C to +125 °C

### 3. Ordering information

Table 1. Ordering information

| Type number  | Package           |        |                                                                                                           |          |

|--------------|-------------------|--------|-----------------------------------------------------------------------------------------------------------|----------|

|              | Temperature range | Name   | Description                                                                                               | Version  |

| 74AVCH2T45DC | –40 °C to +125 °C | VSSOP8 | plastic very thin shrink small outline package; 8 leads; body width 2.3 mm                                | SOT765-1 |

| 74AVCH2T45GT | –40 °C to +125 °C | XSON8  | plastic extremely thin small outline package; no leads; 8 terminals; body 1 $\times$ 1.95 $\times$ 0.5 mm | SOT833-1 |

| 74AVCH2T45GF | –40 °C to +125 °C | XSON8  | extremely thin small outline package; no leads; 8 terminals; body $1.35 \times 1 \times 0.5$ mm           | SOT1089  |

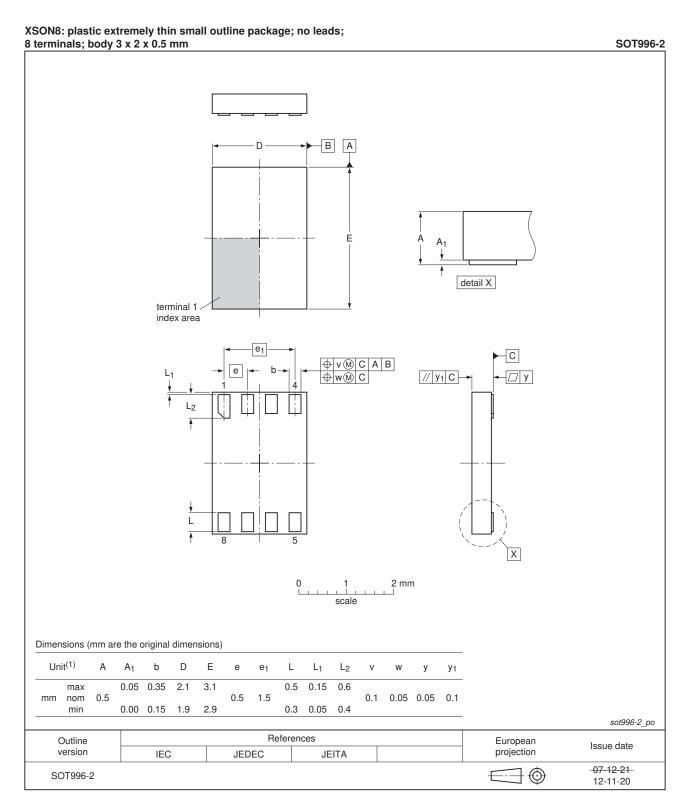

| 74AVCH2T45GD | –40 °C to +125 °C | XSON8  | plastic extremely thin small outline package; no leads; 8 terminals; body 3 $\times$ 2 $\times$ 0.5 mm    | SOT996-2 |

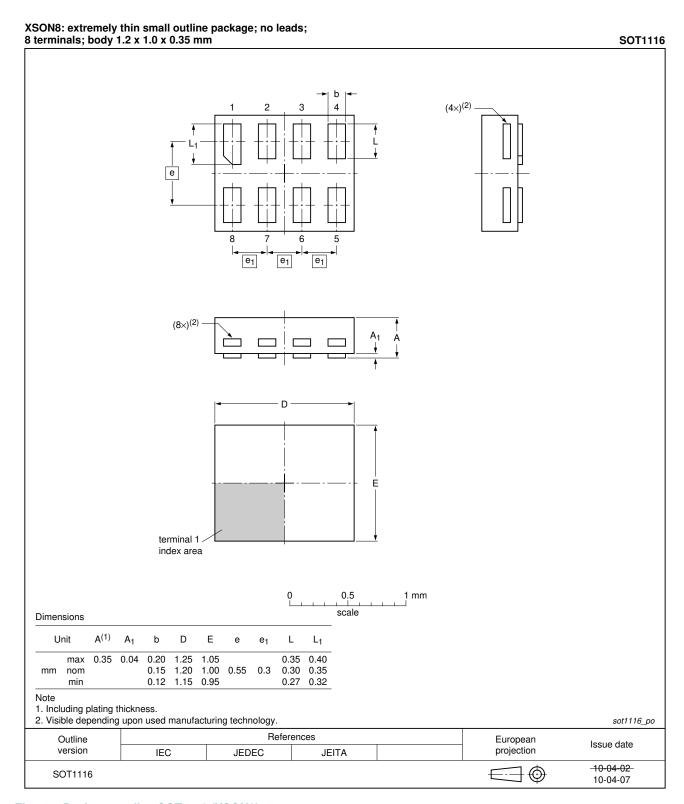

| 74AVCH2T45GN | –40 °C to +125 °C | XSON8  | extremely thin small outline package; no leads; 8 terminals; body 1.2 $\times$ 1.0 $\times$ 0.35 mm       | SOT1116  |

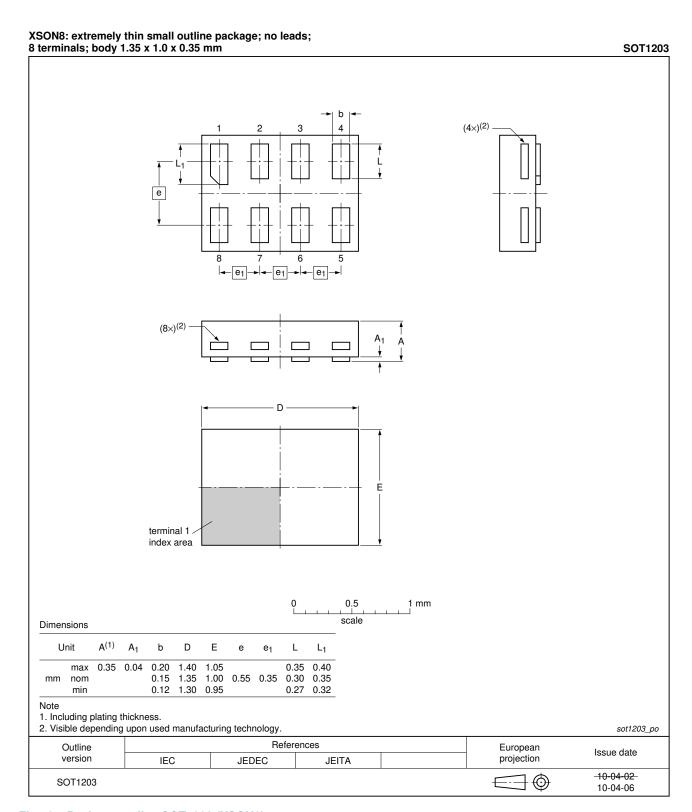

| 74AVCH2T45GS | –40 °C to +125 °C | XSON8  | extremely thin small outline package; no leads; 8 terminals; body 1.35 $\times$ 1.0 $\times$ 0.35 mm      | SOT1203  |

### 4. Marking

Table 2. Marking

| national marking |                             |

|------------------|-----------------------------|

| Type number      | Marking code <sup>[1]</sup> |

| 74AVCH2T45DC     | K45                         |

| 74AVCH2T45GT     | K45                         |

| 74AVCH2T45GF     | K5                          |

| 74AVCH2T45GD     | K45                         |

| 74AVCH2T45GN     | K5                          |

| 74AVCH2T45GS     | K5                          |

<sup>[1]</sup> The pin 1 indicator is located on the lower left corner of the device, below the marking code.

74AVCH2T45

#### Dual-bit, dual-supply voltage level translator/transceiver; 3-state

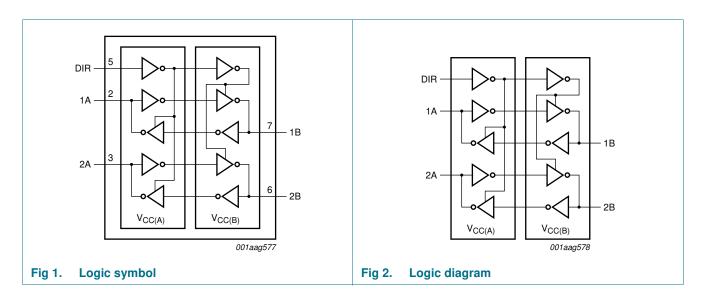

### 5. Functional diagram

**NXP Semiconductors**

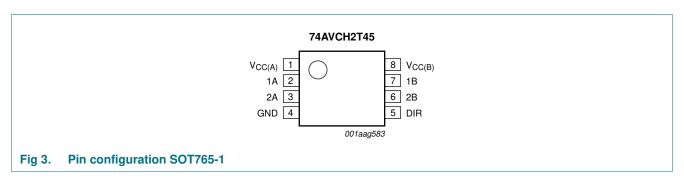

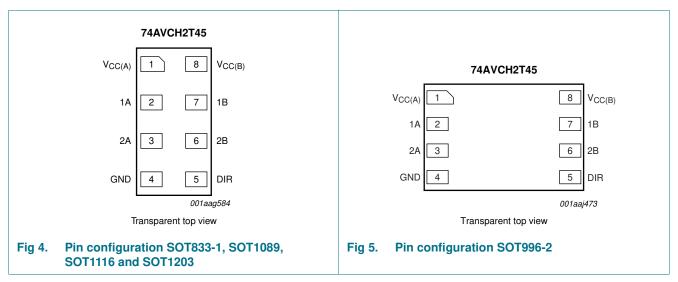

### 6. Pinning information

#### 6.1 Pinning

74AVCH2T45

All information provided in this document is subject to legal disclaimers.

#### Dual-bit, dual-supply voltage level translator/transceiver; 3-state

### 6.2 Pin description

Table 3. Pin description

| Symbol      | Pin | Description                   |

|-------------|-----|-------------------------------|

| $V_{CC(A)}$ | 1   | supply voltage port A and DIR |

| 1A          | 2   | data input or output          |

| 2A          | 3   | data input or output          |

| GND         | 4   | ground (0 V)                  |

| DIR         | 5   | direction control             |

| 2B          | 6   | data input or output          |

| 1B          | 7   | data input or output          |

| $V_{CC(B)}$ | 8   | supply voltage port B         |

### 7. Functional description

Table 4. Function table[1]

| Supply voltage                          | Input  | Input/output[2] |         |  |  |  |

|-----------------------------------------|--------|-----------------|---------|--|--|--|

| V <sub>CC(A)</sub> , V <sub>CC(B)</sub> | DIR[3] | nA              | nB      |  |  |  |

| 0.8 V to 3.6 V                          | L      | nA = nB         | input   |  |  |  |

| 0.8 V to 3.6 V                          | Н      | input           | nB = nA |  |  |  |

| GND[4]                                  | X      | Z               | Z       |  |  |  |

<sup>[1]</sup> H = HIGH voltage level; L = LOW voltage level; X = don't care; Z = high-impedance OFF-state.

<sup>[2]</sup> The input circuit of the data I/O is always active.

<sup>[3]</sup> The DIR input circuit is referenced to  $V_{CC(A)}$ .

<sup>[4]</sup> If at least one of  $V_{CC(A)}$  or  $V_{CC(B)}$  is at GND level, the device goes into suspend mode.

#### Dual-bit, dual-supply voltage level translator/transceiver; 3-state

### 8. Limiting values

Table 5. Limiting values

In accordance with the Absolute Maximum Rating System (IEC 60134). Voltages are referenced to GND (ground = 0 V).

| Symbol           | Parameter               | Conditions                                                           | Min             | Max             | Unit |

|------------------|-------------------------|----------------------------------------------------------------------|-----------------|-----------------|------|

| $V_{CC(A)}$      | supply voltage A        |                                                                      | -0.5            | +4.6            | V    |

| $V_{CC(B)}$      | supply voltage B        |                                                                      | -0.5            | +4.6            | V    |

| I <sub>IK</sub>  | input clamping current  | $V_1 < 0 V$                                                          | -50             | -               | mA   |

| VI               | input voltage           |                                                                      | <u>[1]</u> –0.5 | +4.6            | V    |

| I <sub>OK</sub>  | output clamping current | V <sub>O</sub> < 0 V                                                 | -50             | -               | mA   |

| $V_{O}$          | output voltage          | Active mode                                                          | [1][2][3] -0.5  | $V_{CCO} + 0.5$ | V    |

|                  |                         | Suspend or 3-state mode                                              | <u>[1]</u> –0.5 | +4.6            | V    |

| Io               | output current          | $V_O = 0 V \text{ to } V_{CCO}$                                      | -               | ±50             | mA   |

| I <sub>CC</sub>  | supply current          | $I_{CC(A)}$ or $I_{CC(B)}$                                           | -               | 100             | mA   |

| $I_{GND}$        | ground current          |                                                                      | -100            | -               | mA   |

| T <sub>stg</sub> | storage temperature     |                                                                      | -65             | +150            | °C   |

| P <sub>tot</sub> | total power dissipation | $T_{amb} = -40  ^{\circ}\text{C} \text{ to } +125  ^{\circ}\text{C}$ | <u>[4]</u> -    | 250             | mW   |

<sup>[1]</sup> The minimum input voltage rating and output voltage ratings may be exceeded if the input and output current ratings are observed.

### 9. Recommended operating conditions

Table 6. Recommended operating conditions

| Symbol              | Parameter                           | Conditions                         | Min          | Max       | Unit |

|---------------------|-------------------------------------|------------------------------------|--------------|-----------|------|

| $V_{CC(A)}$         | supply voltage A                    |                                    | 0.8          | 3.6       | V    |

| $V_{CC(B)}$         | supply voltage B                    |                                    | 0.8          | 3.6       | V    |

| VI                  | input voltage                       |                                    | 0            | 3.6       | V    |

| V <sub>O</sub>      | output voltage                      | Active mode                        | <u>[1]</u> 0 | $V_{CCO}$ | V    |

|                     |                                     | Suspend or 3-state mode            | 0            | 3.6       | V    |

| T <sub>amb</sub>    | ambient temperature                 |                                    | -40          | +125      | °C   |

| $\Delta t/\Delta V$ | input transition rise and fall rate | $V_{CCI} = 0.8 \text{ V}$ to 3.6 V | -            | 5         | ns/V |

<sup>[1]</sup> V<sub>CCO</sub> is the supply voltage associated with the output port.

<sup>[2]</sup>  $V_{CCO}$  is the supply voltage associated with the output port.

<sup>[3]</sup>  $V_{CCO} + 0.5 V$  should not exceed 4.6 V.

<sup>[4]</sup> For VSSOP8 package: above 110 °C the value of P<sub>tot</sub> derates linearly with 8 mW/K. For XSON8 packages: above 118 °C the value of P<sub>tot</sub> derates linearly with 7.8 mW/K.

#### Dual-bit, dual-supply voltage level translator/transceiver; 3-state

#### 10. Static characteristics

Table 7. Typical static characteristics at  $T_{amb} = 25 \text{ °C}_{\frac{[1][2]}{2}}$

At recommended operating conditions; voltages are referenced to GND (ground = 0 V).

| Symbol            | Parameter                       | Conditions                                                                                                   | N            | <b>/</b> lin | Тур    | Max   | Unit |

|-------------------|---------------------------------|--------------------------------------------------------------------------------------------------------------|--------------|--------------|--------|-------|------|

| $V_{OH}$          | HIGH-level output voltage       | $V_I = V_{IH}$ or $V_{IL}$                                                                                   |              |              |        |       |      |

|                   |                                 | $I_{O} = -1.5 \text{ mA}; V_{CC(A)} = V_{CC(B)} = 0.8 \text{ V}$                                             | -            |              | 0.69   | -     | V    |

| $V_{OL}$          | LOW-level output voltage        | $V_I = V_{IH}$ or $V_{IL}$                                                                                   |              |              |        |       |      |

|                   |                                 | $I_O = 1.5 \text{ mA}; V_{CC(A)} = V_{CC(B)} = 0.8 \text{ V}$                                                | -            |              | 0.07   | -     | V    |

| l <sub>I</sub>    | input leakage current           | DIR input; $V_I = 0 \text{ V or } 3.6 \text{ V}$ ; $V_{CC(A)} = V_{CC(B)} = 0.8 \text{ V to } 3.6 \text{ V}$ | -            |              | ±0.025 | ±0.25 | μА   |

| I <sub>BHL</sub>  | bus hold LOW current            | $V_I = 0.42 \text{ V}; V_{CC(A)} = V_{CC(B)} = 1.2 \text{ V}$                                                | [3] _        |              | 26     | -     | μΑ   |

| I <sub>BHH</sub>  | bus hold HIGH current           | $V_{I} = 0.78 \text{ V}; V_{CC(A)} = V_{CC(B)} = 1.2 \text{ V}$                                              | [4] _        |              | -24    | -     | μΑ   |

| I <sub>BHLO</sub> | bus hold LOW overdrive current  | $V_I = GND$ to $V_{CCI}$ ; $V_{CC(A)} = V_{CC(B)} = 1.2 \text{ V}$                                           | <u>[5]</u> _ |              | 28     | -     | μА   |

| I <sub>BHHO</sub> | bus hold HIGH overdrive current | $V_I = GND$ to $V_{CCI}$ ; $V_{CC(A)} = V_{CC(B)} = 1.2 \text{ V}$                                           | [6] _        |              | -26    | -     | μА   |

| l <sub>OZ</sub>   | OFF-state output current        | A or B port; $V_O = 0$ V or $V_{CCO}$ ; $V_{CC(A)} = V_{CC(B)} = 0.8$ V to 3.6 V                             | [7] -        |              | ±0.5   | ±2.5  | μА   |

| I <sub>OFF</sub>  | power-off leakage current       | A port; $V_1$ or $V_0 = 0$ V to 3.6 V;<br>$V_{CC(A)} = 0$ V; $V_{CC(B)} = 0.8$ V to 3.6 V                    | -            |              | ±0.1   | ±1    | μА   |

|                   |                                 | B port; $V_I$ or $V_O = 0$ V to 3.6 V; $V_{CC(B)} = 0$ V; $V_{CC(A)} = 0.8$ V to 3.6 V                       | -            |              | ±0.1   | ±1    | μА   |

| Cı                | input capacitance               | DIR input; $V_I = 0 \text{ V or } 3.3 \text{ V}$ ; $V_{CC(A)} = V_{CC(B)} = 3.3 \text{ V}$                   | -            |              | 1.0    | -     | pF   |

| C <sub>I/O</sub>  | input/output capacitance        | A and B port; Suspend mode; $V_O = V_{CCO}$ or GND; $V_{CC(A)} = V_{CC(B)} = 3.3 \text{ V}$                  | -            |              | 4.0    | -     | pF   |

<sup>[1]</sup>  $V_{CCO}$  is the supply voltage associated with the output port.

<sup>[2]</sup> V<sub>CCI</sub> is the supply voltage associated with the data input port.

<sup>[3]</sup> The bus hold circuit can sink at least the minimum low sustaining current at V<sub>IL</sub> max. I<sub>BHL</sub> should be measured after lowering V<sub>I</sub> to GND and then raising it to V<sub>IL</sub> max.

<sup>[4]</sup> The bus hold circuit can source at least the minimum high sustaining current at V<sub>IH</sub> min. I<sub>BHH</sub> should be measured after raising V<sub>I</sub> to V<sub>CC</sub> and then lowering it to V<sub>IH</sub> min.

<sup>[5]</sup> An external driver must source at least I<sub>BHLO</sub> to switch this node from LOW to HIGH.

<sup>[6]</sup> An external driver must sink at least  $I_{BHHO}$  to switch this node from HIGH to LOW.

<sup>[7]</sup> For I/O ports, the parameter  $I_{OZ}$  includes the input leakage current.

#### Dual-bit, dual-supply voltage level translator/transceiver; 3-state

**Table 8.** Static characteristics [1][2]

At recommended operating conditions; voltages are referenced to GND (ground = 0 V).

| Symbol   | Parameter      | Conditions                                                             | –40 °C t               | o +85 °C               | –40 °C to              | Unit                   |   |

|----------|----------------|------------------------------------------------------------------------|------------------------|------------------------|------------------------|------------------------|---|

|          |                |                                                                        | Min                    | Max                    | Min                    | Max                    |   |

| $V_{IH}$ | HIGH-level     | data input                                                             | '                      |                        | 1                      |                        |   |

|          | input voltage  | V <sub>CCI</sub> = 0.8 V                                               | 0.70V <sub>CCI</sub>   | -                      | 0.70V <sub>CCI</sub>   | -                      | V |

|          |                | V <sub>CCI</sub> = 1.1 V to 1.95 V                                     | 0.65V <sub>CCI</sub>   | -                      | 0.65V <sub>CCI</sub>   | -                      | V |

|          |                | $V_{CCI}$ = 2.3 V to 2.7 V                                             | 1.6                    | -                      | 1.6                    | -                      | V |

|          |                | $V_{CCI} = 3.0 \text{ V to } 3.6 \text{ V}$                            | 2                      | -                      | 2                      | -                      | V |

|          |                | DIR input                                                              |                        |                        |                        |                        |   |

|          |                | $V_{CC(A)} = 0.8 \text{ V}$                                            | 0.70V <sub>CC(A)</sub> | -                      | 0.70V <sub>CC(A)</sub> | -                      | V |

|          |                | $V_{CC(A)} = 1.1 \text{ V to } 1.95 \text{ V}$                         | 0.65V <sub>CC(A)</sub> | -                      | 0.65V <sub>CC(A)</sub> | -                      | V |

|          |                | $V_{CC(A)} = 2.3 \text{ V to } 2.7 \text{ V}$                          | 1.6                    | -                      | 1.6                    | -                      | V |

|          |                | $V_{CC(A)} = 3.0 \text{ V to } 3.6 \text{ V}$                          | 2                      | -                      | 2                      | -                      | V |

| $V_{IL}$ | LOW-level      | data input                                                             |                        |                        |                        |                        |   |

|          | input voltage  | V <sub>CCI</sub> = 0.8 V                                               | -                      | 0.30V <sub>CCI</sub>   | -                      | 0.30V <sub>CCI</sub>   | V |

|          |                | V <sub>CCI</sub> = 1.1 V to 1.95 V                                     | -                      | 0.35V <sub>CCI</sub>   | -                      | 0.35V <sub>CCI</sub>   | V |

|          |                | $V_{CCI}$ = 2.3 V to 2.7 V                                             | -                      | 0.7                    | -                      | 0.7                    | V |

|          |                | $V_{CCI} = 3.0 \text{ V to } 3.6 \text{ V}$                            | -                      | 0.9                    | -                      | 0.9                    | V |

|          |                | DIR input                                                              |                        |                        |                        |                        |   |

|          |                | $V_{CC(A)} = 0.8 \text{ V}$                                            | -                      | 0.30V <sub>CC(A)</sub> | -                      | 0.30V <sub>CC(A)</sub> | ٧ |

|          |                | $V_{CC(A)} = 1.1 \text{ V to } 1.95 \text{ V}$                         | -                      | 0.35V <sub>CC(A)</sub> | -                      | 0.35V <sub>CC(A)</sub> | V |

|          |                | $V_{CC(A)} = 2.3 \text{ V to } 2.7 \text{ V}$                          | -                      | 0.7                    | -                      | 0.7                    | V |

|          |                | $V_{CC(A)} = 3.0 \text{ V to } 3.6 \text{ V}$                          | -                      | 0.9                    | -                      | 0.9                    | V |

| $V_{OH}$ | HIGH-level     | $V_I = V_{IH}$ or $V_{IL}$                                             |                        |                        |                        |                        |   |

|          | output voltage | $I_O = -100 \ \mu A;$ $V_{CC(A)} = V_{CC(B)} = 0.8 \ V \ to \ 3.6 \ V$ | V <sub>CCO</sub> - 0.1 | -                      | V <sub>CCO</sub> - 0.1 | -                      | V |

|          |                | $I_{O} = -3 \text{ mA};$<br>$V_{CC(A)} = V_{CC(B)} = 1.1 \text{ V}$    | 0.85                   | -                      | 0.85                   | -                      | V |

|          |                | $I_{O} = -6 \text{ mA};$<br>$V_{CC(A)} = V_{CC(B)} = 1.4 \text{ V}$    | 1.05                   | -                      | 1.05                   | -                      | V |

|          |                | $I_O = -8 \text{ mA};$<br>$V_{CC(A)} = V_{CC(B)} = 1.65 \text{ V}$     | 1.2                    | -                      | 1.2                    | -                      | V |

|          |                | $I_{O} = -9 \text{ mA};$<br>$V_{CC(A)} = V_{CC(B)} = 2.3 \text{ V}$    | 1.75                   | -                      | 1.75                   | -                      | V |

|          |                | $I_O = -12 \text{ mA};$<br>$V_{CC(A)} = V_{CC(B)} = 3.0 \text{ V}$     | 2.3                    | -                      | 2.3                    | -                      | V |

**Table 8.** Static characteristics ...continued 11[2]

At recommended operating conditions; voltages are referenced to GND (ground = 0 V).

| Symbol          | Parameter                | Conditions                                                                                                  | –40 °        | C to +85 °C | –40 °C to  | +125 °C | Uni        |

|-----------------|--------------------------|-------------------------------------------------------------------------------------------------------------|--------------|-------------|------------|---------|------------|

|                 |                          |                                                                                                             | Min          | Max         | Min        | Max     |            |

| √ <sub>OL</sub> | LOW-level                | $V_I = V_{IH}$ or $V_{IL}$                                                                                  |              |             |            |         |            |

|                 | output voltage           | $I_{O} = 100 \ \mu A;$ $V_{CC(A)} = V_{CC(B)} = 0.8 \ V \ to \ 3.6 \ V$                                     | -            | 0.1         | -          | 0.1     | V          |

|                 |                          | $I_O = 3 \text{ mA}; V_{CC(A)} = V_{CC(B)} = 1.1 \text{ V}$                                                 | -            | 0.25        | -          | 0.25    | V          |

|                 |                          | $I_{O} = 6 \text{ mA}; V_{CC(A)} = V_{CC(B)} = 1.4 \text{ V}$                                               | -            | 0.35        | -          | 0.35    | ٧          |

|                 |                          | $I_{O} = 8 \text{ mA};$<br>$V_{CC(A)} = V_{CC(B)} = 1.65 \text{ V}$                                         | -            | 0.45        | -          | 0.45    | V          |

|                 |                          | $I_O = 9 \text{ mA}; V_{CC(A)} = V_{CC(B)} = 2.3 \text{ V}$                                                 | -            | 0.55        | -          | 0.55    | V          |

|                 |                          | $I_O = 12 \text{ mA};$<br>$V_{CC(A)} = V_{CC(B)} = 3.0 \text{ V}$                                           | -            | 0.7         | -          | 0.7     | V          |

| I               | input leakage<br>current | DIR input; $V_I = 0 \text{ V or } 3.6 \text{ V};$ $V_{CC(A)} = V_{CC(B)} = 0.8 \text{ V to } 3.6 \text{ V}$ | -            | ±1          | -          | ±1.5    | μ <b>A</b> |

| BHL             | bus hold LOW<br>current  | A or B port                                                                                                 | [3]          |             |            |         |            |

|                 |                          | $V_{I} = 0.49 \text{ V};$<br>$V_{CC(A)} = V_{CC(B)} = 1.4 \text{ V}$                                        | 15           | -           | 15         | -       | μΑ         |

|                 |                          | $V_{I} = 0.58 \text{ V};$<br>$V_{CC(A)} = V_{CC(B)} = 1.65 \text{ V}$                                       | 25           | -           | 25         | -       | μΑ         |

|                 |                          | $V_{I} = 0.70 \text{ V};$<br>$V_{CC(A)} = V_{CC(B)} = 2.3 \text{ V}$                                        | 45           | -           | 45         | -       | μΑ         |

|                 |                          | $V_{I} = 0.80 \text{ V};$<br>$V_{CC(A)} = V_{CC(B)} = 3.0 \text{ V}$                                        | 100          | -           | 90         | -       | μΑ         |

| ВНН             | bus hold HIGH<br>current | A or B port                                                                                                 | <u>[4]</u>   |             |            |         |            |

|                 |                          | $V_{I} = 0.91 \text{ V};$<br>$V_{CC(A)} = V_{CC(B)} = 1.4 \text{ V}$                                        | -15          | -           | -15        | -       | μΑ         |

|                 |                          | $V_{I} = 1.07 \text{ V};$<br>$V_{CC(A)} = V_{CC(B)} = 1.65 \text{ V}$                                       | -25          | -           | -25        | -       | μΑ         |

|                 |                          | $V_{I} = 1.60 \text{ V};$<br>$V_{CC(A)} = V_{CC(B)} = 2.3 \text{ V}$                                        | -45          | -           | <b>-45</b> | -       | μΑ         |

|                 |                          | $V_{I} = 2.00 \text{ V};$<br>$V_{CC(A)} = V_{CC(B)} = 3.0 \text{ V}$                                        | -100         | -           | -100       | -       | μΑ         |

| BHLO            | bus hold LOW             | A or B port                                                                                                 | <u>[5]</u>   |             |            |         |            |

|                 | overdrive<br>current     | $V_{CC(A)} = V_{CC(B)} = 1.6 \text{ V}$                                                                     | 125          | -           | 125        | -       | μΑ         |

|                 | carrent                  | $V_{CC(A)} = V_{CC(B)} = 1.95 \text{ V}$                                                                    | 200          | -           | 200        | -       | μΑ         |

|                 |                          | $V_{CC(A)} = V_{CC(B)} = 2.7 \text{ V}$                                                                     | 300          | -           | 300        | -       | μΑ         |

|                 |                          | $V_{CC(A)} = V_{CC(B)} = 3.6 \text{ V}$                                                                     | 500          | -           | 500        | -       | μΑ         |

| внно            | bus hold HIGH            | A or B port                                                                                                 | [6]          |             |            |         |            |

|                 | overdrive<br>current     | $V_{CC(A)} = V_{CC(B)} = 1.6 \text{ V}$                                                                     | -125         | -           | -125       | -       | μΑ         |

|                 | Janon                    | $V_{CC(A)} = V_{CC(B)} = 1.95 \text{ V}$                                                                    | -200         | -           | -200       | -       | μΑ         |

|                 |                          | $V_{CC(A)} = V_{CC(B)} = 2.7 \text{ V}$                                                                     | -300         | -           | -300       | -       | μΑ         |

|                 |                          | $V_{CC(A)} = V_{CC(B)} = 3.6 \text{ V}$                                                                     | -500         | -           | -500       | -       | μΑ         |

| OZ              | OFF-state output current | A or B port; $V_O = 0$ V or $V_{CCO}$ ; $V_{CC(A)} = V_{CC(B)} = 0.8$ to 3.6 V                              | <u>[7]</u> _ | ±5          | -          | ±7.5    | μΑ         |

#### Dual-bit, dual-supply voltage level translator/transceiver; 3-state

Table 8. Static characteristics ... continue o[1][2]

At recommended operating conditions; voltages are referenced to GND (ground = 0 V).

| Symbol           | Parameter            | Conditions                                                                                                                                             | –40 °C t | o +85 °C | –40 °C to | +125 °C | Unit |

|------------------|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|----------|----------|-----------|---------|------|

|                  |                      |                                                                                                                                                        | Min      | Max      | Min       | Max     |      |

| I <sub>OFF</sub> | power-off<br>leakage | A port; $V_1$ or $V_O = 0$ V to 3.6 V; $V_{CC(A)} = 0$ V; $V_{CC(B)} = 0.8$ V to 3.6 V                                                                 | -        | ±5       | -         | ±35     | μΑ   |

|                  | current              | B port; $V_1$ or $V_O = 0$ V to 3.6 V; $V_{CC(B)} = 0$ V; $V_{CC(A)} = 0.8$ V to 3.6 V                                                                 | -        | ±5       | -         | ±35     | μΑ   |

| I <sub>CC</sub>  | supply current       | A port; $V_I = 0 V \text{ or } V_{CCI}$ ; $I_O = 0 A$                                                                                                  |          |          |           |         |      |

|                  |                      | $V_{CC(A)} = 0.8 \text{ V to } 3.6 \text{ V};$<br>$V_{CC(B)} = 0.8 \text{ V to } 3.6 \text{ V}$                                                        | -        | 8        | -         | 11.5    | μΑ   |

|                  |                      | $V_{CC(A)} = 3.6 \text{ V}; V_{CC(B)} = 0 \text{ V}$                                                                                                   | -        | 8        | -         | 11.5    | μΑ   |

|                  |                      | V <sub>CC(A)</sub> = 0 V; V <sub>CC(B)</sub> = 3.6 V                                                                                                   | -2       | -        | -8        | -       | μΑ   |

|                  |                      | B port; $V_I = 0 V \text{ or } V_{CCI}$ ; $I_O = 0 A$                                                                                                  |          |          |           |         |      |

|                  |                      | $V_{CC(A)} = 0.8 \text{ V to } 3.6 \text{ V};$<br>$V_{CC(B)} = 0.8 \text{ V to } 3.6 \text{ V}$                                                        | -        | 8        | -         | 11.5    | μΑ   |

|                  |                      | $V_{CC(A)} = 3.6 \text{ V}; V_{CC(B)} = 0 \text{ V}$                                                                                                   | -2       | -        | -8        | -       | μΑ   |

|                  |                      | V <sub>CC(A)</sub> = 0 V; V <sub>CC(B)</sub> = 3.6 V                                                                                                   | -        | 8        | -         | 11.5    | μΑ   |

|                  |                      | A plus B port ( $I_{CC(A)} + I_{CC(B)}$ );<br>$I_O = 0$ A; $V_I = 0$ V or $V_{CCI}$ ;<br>$V_{CC(A)} = 0.8$ V to 3.6 V;<br>$V_{CC(B)} = 0.8$ V to 3.6 V | -        | 16       | -         | 23      | μА   |

<sup>[1]</sup>  $V_{CCO}$  is the supply voltage associated with the output port.

<sup>[2]</sup>  $V_{CCI}$  is the supply voltage associated with the data input port.

<sup>[3]</sup> The bus hold circuit can sink at least the minimum low sustaining current at  $V_{IL}$  max.  $I_{BHL}$  should be measured after lowering  $V_I$  to GND and then raising it to  $V_{IL}$  max.

<sup>[4]</sup> The bus hold circuit can source at least the minimum high sustaining current at V<sub>IH</sub> min. I<sub>BHH</sub> should be measured after raising V<sub>I</sub> to V<sub>CC</sub> and then lowering it to V<sub>IH</sub> min.

<sup>[5]</sup> An external driver must source at least I<sub>BHLO</sub> to switch this node from LOW to HIGH.

<sup>[6]</sup> An external driver must sink at least I<sub>BHHO</sub> to switch this node from HIGH to LOW.

<sup>[7]</sup> For I/O ports, the parameter  $I_{OZ}$  includes the input leakage current.

### 11. Dynamic characteristics

Table 9. Typical dynamic characteristics at  $V_{CC(A)} = 0.8 \text{ V}$  and  $T_{amb} = 25 \text{ °C } \square$

Voltages are referenced to GND (ground = 0 V); for test circuit see Figure 8; for wave forms see Figure 6 and Figure 7

| Symbol           | Parameter         | Conditions |       |       | Vco   | C(B)  |       |       | Unit |

|------------------|-------------------|------------|-------|-------|-------|-------|-------|-------|------|

|                  |                   |            | 0.8 V | 1.2 V | 1.5 V | 1.8 V | 2.5 V | 3.3 V |      |

| t <sub>pd</sub>  | propagation delay | A to B     | 15.8  | 8.4   | 8.0   | 8.0   | 8.7   | 9.5   | ns   |

|                  |                   | B to A     | 15.8  | 12.7  | 12.4  | 12.2  | 12.0  | 11.8  | ns   |

| t <sub>dis</sub> | disable time      | DIR to A   | 12.2  | 12.2  | 12.2  | 12.2  | 12.2  | 12.2  | ns   |

|                  |                   | DIR to B   | 11.7  | 7.9   | 7.6   | 8.2   | 8.7   | 10.2  | ns   |

| t <sub>en</sub>  | enable time       | DIR to A   | 27.5  | 20.6  | 20.0  | 20.4  | 20.7  | 22.0  | ns   |

|                  |                   | DIR to B   | 28.0  | 20.6  | 20.2  | 20.2  | 20.9  | 21.7  | ns   |

<sup>[1]</sup> t<sub>pd</sub> is the same as t<sub>PLH</sub> and t<sub>PHL</sub>; t<sub>dis</sub> is the same as t<sub>PLZ</sub> and t<sub>PHZ</sub>; t<sub>en</sub> is the same as t<sub>PZL</sub> and t<sub>PZH</sub>. t<sub>en</sub> is a calculated value using the formula shown in Section 13.4 "Enable times"

Table 10. Typical dynamic characteristics at  $V_{CC(B)} = 0.8 \text{ V}$  and  $T_{amb} = 25 \text{ °C}$  [1]

Voltages are referenced to GND (ground = 0 V); for test circuit see Figure 8; for wave forms see Figure 6 and Figure 7

| Symbol           | mbol Parameter Conditions V <sub>CC(A)</sub> |          |       |       |       |       |       | Unit  |    |

|------------------|----------------------------------------------|----------|-------|-------|-------|-------|-------|-------|----|

|                  |                                              |          | 0.8 V | 1.2 V | 1.5 V | 1.8 V | 2.5 V | 3.3 V |    |

| t <sub>pd</sub>  | propagation delay                            | A to B   | 15.8  | 12.7  | 12.4  | 12.2  | 12.0  | 11.8  | ns |

|                  |                                              | B to A   | 15.8  | 8.4   | 8.0   | 8.0   | 8.7   | 9.5   | ns |

| t <sub>dis</sub> | disable time                                 | DIR to A | 12.2  | 4.9   | 3.8   | 3.7   | 2.8   | 3.4   | ns |

|                  |                                              | DIR to B | 11.7  | 9.2   | 9.0   | 8.8   | 8.7   | 8.6   | ns |

| t <sub>en</sub>  | enable time                                  | DIR to A | 27.5  | 17.6  | 17.0  | 16.8  | 17.4  | 18.1  | ns |

|                  |                                              | DIR to B | 28.0  | 17.6  | 16.2  | 15.9  | 14.8  | 15.2  | ns |

<sup>[1]</sup> t<sub>pd</sub> is the same as t<sub>PLH</sub> and t<sub>PHL</sub>; t<sub>dis</sub> is the same as t<sub>PLZ</sub> and t<sub>PHZ</sub>; t<sub>en</sub> is the same as t<sub>PZL</sub> and t<sub>PZH</sub>.

t<sub>en</sub> is a calculated value using the formula shown in Section 13.4 "Enable times"

Table 11. Typical power dissipation capacitance at  $V_{CC(A)} = V_{CC(B)}$  and  $T_{amb} = 25 \, ^{\circ}C$  [1][2]

Voltages are referenced to GND (ground = 0 V).

| Symbol   | Parameter                     | Conditions                                                |       |       | V <sub>CC(A)</sub> ar | nd V <sub>CC(B)</sub> |       |       | Unit |

|----------|-------------------------------|-----------------------------------------------------------|-------|-------|-----------------------|-----------------------|-------|-------|------|

|          |                               |                                                           | 0.8 V | 1.2 V | 1.5 V                 | 1.8 V                 | 2.5 V | 3.3 V |      |

| $C_{PD}$ | power dissipation capacitance | A port: (direction A to B);<br>B port: (direction B to A) | 1     | 2     | 2                     | 2                     | 2     | 2     | pF   |

|          |                               | A port: (direction B to A);<br>B port: (direction A to B) | 9     | 11    | 11                    | 12                    | 14    | 17    | pF   |

<sup>[1]</sup>  $C_{PD}$  is used to determine the dynamic power dissipation ( $P_D$  in  $\mu W$ ).

$P_D = C_{PD} \times V_{CC}{}^2 \times f_i \times N + \Sigma (C_L \times V_{CC}{}^2 \times f_o) \text{ where:}$

f<sub>i</sub> = input frequency in MHz;

$f_0$  = output frequency in MHz;

C<sub>L</sub> = load capacitance in pF;

V<sub>CC</sub> = supply voltage in V;

N = number of inputs switching;

$\Sigma(C_L \times V_{CC}^2 \times f_o)$  = sum of the outputs.

[2]  $f_i = 10 \text{ MHz; } V_I = \text{GND to } V_{CC}; t_r = t_f = 1 \text{ ns; } C_L = 0 \text{ pF; } R_L = \infty \ \Omega.$

74AVCH2T45

All information provided in this document is subject to legal disclaimers.

#### Dual-bit, dual-supply voltage level translator/transceiver; 3-state

Table 12. Dynamic characteristics for temperature range –40 °C to +85 °C [1]

Voltages are referenced to GND (ground = 0 V); for test circuit see Figure 8; for wave forms see Figure 6 and Figure 7.

| Symbol               | Parameter            | Conditions | V <sub>CC(B)</sub> | . 0 4 1/ | 451 | . 0 4 14 | 461/ | 0.45.11 | 0.5.\ |         | 0.0.17 | . 0.034 | Uni |

|----------------------|----------------------|------------|--------------------|----------|-----|----------|------|---------|-------|---------|--------|---------|-----|

|                      |                      |            |                    | ± 0.1 V  |     | ± 0.1 V  |      | 0.15 V  |       | ± 0.2 V |        | ± 0.3 V |     |

|                      |                      |            | Min                | Max      | Min | Max      | Min  | Max     | Min   | Max     | Min    | Max     |     |

| $V_{CC(A)} =$        | 1.1 V to 1.3 V       |            |                    |          |     |          |      |         |       |         |        |         |     |

| t <sub>pd</sub>      | propagation          | A to B     | 1.0                | 9.0      | 0.7 | 6.8      | 0.6  | 6.1     | 0.5   | 5.7     | 0.5    | 6.1     | ns  |

|                      | delay                | B to A     | 1.0                | 9.0      | 8.0 | 8.0      | 0.7  | 7.7     | 0.6   | 7.2     | 0.5    | 7.1     | ns  |

| t <sub>dis</sub>     | disable time         | DIR to A   | 2.2                | 8.8      | 2.2 | 8.8      | 2.2  | 8.8     | 2.2   | 8.8     | 2.2    | 8.8     | ns  |

|                      |                      | DIR to B   | 2.2                | 8.4      | 1.8 | 6.7      | 2.0  | 6.9     | 1.7   | 6.2     | 2.4    | 7.2     | ns  |

| t <sub>en</sub>      | enable time          | DIR to A   | -                  | 17.4     | -   | 14.7     | -    | 14.6    | -     | 13.4    | -      | 14.3    | ns  |

|                      |                      | DIR to B   | -                  | 17.8     | -   | 15.6     | -    | 14.9    | -     | 14.5    | -      | 14.9    | ns  |

| $V_{CC(A)} =$        | 1.4 V to 1.6 V       |            |                    |          |     |          |      |         |       |         |        |         |     |

| t <sub>pd</sub>      | propagation          | A to B     | 1.0                | 8.0      | 0.7 | 5.4      | 0.6  | 4.6     | 0.5   | 3.7     | 0.5    | 3.5     | ns  |

|                      | delay                | B to A     | 1.0                | 6.8      | 8.0 | 5.4      | 0.7  | 5.1     | 0.6   | 4.7     | 0.5    | 4.5     | ns  |

| t <sub>dis</sub>     | disable time         | DIR to A   | 1.6                | 6.3      | 1.6 | 6.3      | 1.6  | 6.3     | 1.6   | 6.3     | 1.6    | 6.3     | ns  |

|                      |                      | DIR to B   | 2.0                | 7.6      | 1.8 | 5.9      | 1.6  | 6.0     | 1.2   | 4.8     | 1.7    | 5.5     | ns  |

| t <sub>en</sub>      | enable time          | DIR to A   | -                  | 14.4     | -   | 11.3     | -    | 11.1    | -     | 9.5     | -      | 10.0    | ns  |

|                      |                      | DIR to B   | -                  | 14.3     | -   | 11.7     | -    | 10.9    | -     | 10.0    | -      | 9.8     | ns  |

| V <sub>CC(A)</sub> = | 1.65 V to 1.95       | V          |                    |          |     |          |      |         |       |         |        |         |     |

| t <sub>pd</sub>      | propagation<br>delay | A to B     | 1.0                | 7.7      | 0.6 | 5.1      | 0.5  | 4.3     | 0.5   | 3.4     | 0.5    | 3.1     | ns  |

|                      |                      | B to A     | 1.0                | 6.1      | 0.7 | 4.6      | 0.5  | 4.4     | 0.5   | 3.9     | 0.5    | 3.7     | ns  |

| t <sub>dis</sub>     | disable time         | DIR to A   | 1.6                | 5.5      | 1.6 | 5.5      | 1.6  | 5.5     | 1.6   | 5.5     | 1.6    | 5.5     | ns  |

|                      |                      | DIR to B   | 1.8                | 7.8      | 1.8 | 5.7      | 1.4  | 5.8     | 1.0   | 4.5     | 1.5    | 5.2     | ns  |

| t <sub>en</sub>      | enable time          | DIR to A   | -                  | 13.9     | -   | 10.3     | -    | 10.2    | -     | 8.4     | -      | 8.9     | ns  |

|                      |                      | DIR to B   | -                  | 13.2     | -   | 10.6     | -    | 9.8     | -     | 8.9     | -      | 8.6     | ns  |

| V <sub>CC(A)</sub> = | 2.3 V to 2.7 V       |            |                    |          |     |          |      |         |       |         |        |         |     |

| t <sub>pd</sub>      | propagation          | A to B     | 1.0                | 7.2      | 0.5 | 4.7      | 0.5  | 3.9     | 0.5   | 3.0     | 0.5    | 2.6     | ns  |

|                      | delay                | B to A     | 1.0                | 5.7      | 0.6 | 3.8      | 0.5  | 3.4     | 0.5   | 3.0     | 0.5    | 2.8     | ns  |

| t <sub>dis</sub>     | disable time         | DIR to A   | 1.5                | 4.2      | 1.5 | 4.2      | 1.5  | 4.2     | 1.5   | 4.2     | 1.5    | 4.2     | ns  |

|                      |                      | DIR to B   | 1.7                | 7.3      | 2.0 | 5.2      | 1.5  | 5.1     | 0.6   | 4.2     | 1.1    | 4.8     | ns  |

| t <sub>en</sub>      | enable time          | DIR to A   | -                  | 13.0     | -   | 9.0      | -    | 8.5     | -     | 7.2     | -      | 7.6     | ns  |

|                      |                      | DIR to B   | -                  | 11.4     | -   | 8.9      | -    | 8.1     | -     | 7.2     | -      | 6.8     | ns  |

| V <sub>CC(A)</sub> = | 3.0 V to 3.6 V       |            |                    |          |     |          |      |         |       |         |        |         |     |

| t <sub>pd</sub>      | propagation          | A to B     | 1.0                | 7.1      | 0.5 | 4.5      | 0.5  | 3.7     | 0.5   | 2.8     | 0.5    | 2.4     | ns  |

|                      | delay                | B to A     | 1.0                | 6.1      | 0.6 | 3.6      | 0.5  | 3.1     | 0.5   | 2.6     | 0.5    | 2.4     | ns  |

| t <sub>dis</sub>     | disable time         | DIR to A   | 1.5                | 4.7      | 1.5 | 4.7      | 1.5  | 4.7     | 1.5   | 4.7     | 1.5    | 4.7     | ns  |

|                      |                      | DIR to B   | 1.7                | 7.2      | 0.7 | 5.5      | 0.6  | 5.5     | 0.7   | 4.1     | 1.7    | 4.7     | ns  |

| t <sub>en</sub>      | enable time          | DIR to A   | -                  | 13.3     | -   | 9.1      | -    | 8.6     | -     | 6.7     | -      | 7.1     | ns  |

| ten eriable          |                      | DIR to B   | -                  | 11.8     | -   | 9.2      | -    | 8.4     | -     | 7.5     | -      | 7.1     | ns  |

<sup>[1]</sup>  $t_{pd}$  is the same as  $t_{PLH}$  and  $t_{PHL}$ ;  $t_{dis}$  is the same as  $t_{PLZ}$  and  $t_{PHZ}$ ;  $t_{en}$  is the same as  $t_{PZL}$  and  $t_{PZH}$ .  $t_{en}$  is a calculated value using the formula shown in <u>Section 13.4 "Enable times"</u>

#### Dual-bit, dual-supply voltage level translator/transceiver; 3-state

Table 13. Dynamic characteristics for temperature range –40 °C to +125 °C 11 Voltages are referenced to GND (ground = 0 V); for test circuit see Figure 8; for wave forms see Figure 6 and Figure 7

| Symbo                       | l Parameter      | Conditions | V <sub>CC(B)</sub> |         |       |         |         |        |       |         |       |         | Unit |

|-----------------------------|------------------|------------|--------------------|---------|-------|---------|---------|--------|-------|---------|-------|---------|------|

|                             |                  |            | 1.2 V              | ± 0.1 V | 1.5 V | ± 0.1 V | 1.8 V ± | 0.15 V | 2.5 V | ± 0.2 V | 3.3 V | ± 0.3 V |      |

|                             |                  |            | Min                | Max     | Min   | Max     | Min     | Max    | Min   | Max     | Min   | Max     |      |

| V <sub>CC(A)</sub>          | = 1.1 V to 1.3 V | •          | '                  | '       |       |         |         |        |       | '       |       | •       |      |

| t <sub>pd</sub>             | propagation      | A to B     | 1.0                | 9.9     | 0.7   | 7.5     | 0.6     | 6.8    | 0.5   | 6.3     | 0.5   | 6.8     | ns   |

|                             | delay            | B to A     | 1.0                | 9.9     | 8.0   | 8.8     | 0.7     | 8.5    | 0.6   | 8.0     | 0.5   | 7.9     | ns   |

| $t_{dis}$                   | disable time     | DIR to A   | 2.2                | 9.7     | 2.2   | 9.7     | 2.2     | 9.7    | 2.2   | 9.7     | 2.2   | 9.7     | ns   |

|                             |                  | DIR to B   | 2.2                | 9.2     | 1.8   | 7.4     | 2.0     | 7.6    | 1.7   | 6.9     | 2.4   | 8.0     | ns   |

| t <sub>en</sub>             | enable time      | DIR to A   | -                  | 19.1    | -     | 16.2    | -       | 16.1   | -     | 14.9    | -     | 15.9    | ns   |

|                             |                  | DIR to B   | -                  | 19.6    | -     | 17.2    | -       | 16.5   | -     | 16.0    | -     | 16.5    | ns   |

| V <sub>CC(A)</sub>          | = 1.4 V to 1.6 V |            |                    |         |       |         |         |        |       |         |       |         |      |

| t <sub>pd</sub> propagation | A to B           | 1.0        | 8.8                | 0.7     | 6.0   | 0.6     | 5.1     | 0.5    | 4.1   | 0.5     | 3.9   | ns      |      |

|                             | delay            | B to A     | 1.0                | 7.5     | 8.0   | 6.0     | 0.7     | 5.7    | 0.6   | 5.2     | 0.5   | 5.0     | ns   |

| $t_{dis}$                   | disable time     | DIR to A   | 1.6                | 7.0     | 1.6   | 7.0     | 1.6     | 7.0    | 1.6   | 7.0     | 1.6   | 7.0     | ns   |

|                             |                  | DIR to B   | 2.0                | 8.3     | 1.8   | 6.5     | 1.6     | 6.6    | 1.2   | 5.3     | 1.7   | 6.1     | ns   |

| t <sub>en</sub>             | enable time      | DIR to A   | -                  | 15.8    | -     | 12.5    | -       | 12.3   | -     | 10.5    | -     | 11.1    | ns   |

|                             |                  | DIR to B   | -                  | 15.8    | -     | 13.0    | -       | 12.7   | -     | 11.1    | -     | 10.9    | ns   |

| V <sub>CC(A)</sub>          | = 1.65 V to 1.95 | V          |                    |         |       |         |         |        |       |         |       |         |      |

| $t_{pd}$                    | propagation      | A to B     | 1.0                | 8.5     | 0.6   | 5.7     | 0.5     | 4.8    | 0.5   | 3.8     | 0.5   | 3.5     | ns   |

|                             | delay            | B to A     | 1.0                | 6.8     | 0.7   | 5.1     | 0.5     | 4.9    | 0.5   | 4.3     | 0.5   | 4.1     | ns   |

| $t_{dis}$                   | disable time     | DIR to A   | 1.6                | 6.1     | 1.6   | 6.1     | 1.6     | 6.1    | 1.6   | 6.1     | 1.6   | 6.1     | ns   |

|                             |                  | DIR to B   | 1.8                | 8.6     | 1.8   | 6.3     | 1.4     | 6.4    | 1.0   | 5.0     | 1.5   | 5.8     | ns   |

| t <sub>en</sub>             | enable time      | DIR to A   | -                  | 15.4    | -     | 11.4    | -       | 11.3   | -     | 9.3     | -     | 9.9     | ns   |

|                             |                  | DIR to B   | -                  | 14.6    | -     | 11.8    | -       | 10.9   | -     | 9.9     | -     | 9.6     | ns   |

| V <sub>CC(A)</sub>          | = 2.3 V to 2.7 V |            |                    |         |       |         |         |        |       |         |       |         |      |

| $t_{pd}$                    | propagation      | A to B     | 1.0                | 8.0     | 0.5   | 5.2     | 0.5     | 4.3    | 0.5   | 3.3     | 0.5   | 2.9     | ns   |

|                             | delay            | B to A     | 1.0                | 6.3     | 0.6   | 4.2     | 0.5     | 3.8    | 0.5   | 3.3     | 0.5   | 3.1     | ns   |

| $t_{dis}$                   | disable time     | DIR to A   | 1.5                | 4.7     | 1.5   | 4.7     | 1.5     | 4.7    | 1.5   | 4.7     | 1.5   | 4.7     | ns   |

|                             |                  | DIR to B   | 1.7                | 8.0     | 2.0   | 5.8     | 1.5     | 5.7    | 0.6   | 4.7     | 1.1   | 5.3     | ns   |

| t <sub>en</sub>             | enable time      | DIR to A   | -                  | 14.3    | -     | 10.0    | -       | 9.5    | -     | 8.0     | -     | 8.4     | ns   |

|                             |                  | DIR to B   | -                  | 12.7    | -     | 9.9     | -       | 9.0    | -     | 8.0     | -     | 7.6     | ns   |

| V <sub>CC(A)</sub>          | = 3.0 V to 3.6 V |            |                    |         |       |         |         |        |       |         |       |         |      |

| $t_{pd}$                    | propagation      | A to B     | 1.0                | 7.9     | 0.5   | 5.0     | 0.5     | 4.1    | 0.5   | 3.1     | 0.5   | 2.7     | ns   |

|                             | delay            | B to A     | 1.0                | 6.8     | 0.6   | 4.0     | 0.5     | 3.5    | 0.5   | 2.9     | 0.5   | 2.7     | ns   |

| $t_{dis}$                   | disable time     | DIR to A   | 1.5                | 5.2     | 1.5   | 5.2     | 1.5     | 5.2    | 1.5   | 5.2     | 1.5   | 5.2     | ns   |

|                             |                  | DIR to B   | 1.7                | 7.9     | 0.7   | 6.1     | 0.6     | 6.1    | 0.7   | 4.6     | 1.7   | 5.2     | ns   |

| t <sub>en</sub>             | enable time      | DIR to A   | -                  | 14.7    | -     | 10.1    | -       | 9.6    | -     | 7.5     | -     | 7.9     | ns   |

|                             |                  | DIR to B   | -                  | 13.1    | -     | 10.2    | -       | 9.3    | -     | 8.3     | -     | 7.9     | ns   |

<sup>[1]</sup>  $t_{pd}$  is the same as  $t_{PLH}$  and  $t_{PHL}$ ;  $t_{dis}$  is the same as  $t_{PLZ}$  and  $t_{PHZ}$ ;  $t_{en}$  is the same as  $t_{PZL}$  and  $t_{PZH}$ .  $t_{en}$  is a calculated value using the formula shown in <u>Section 13.4 "Enable times"</u>

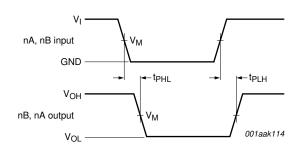

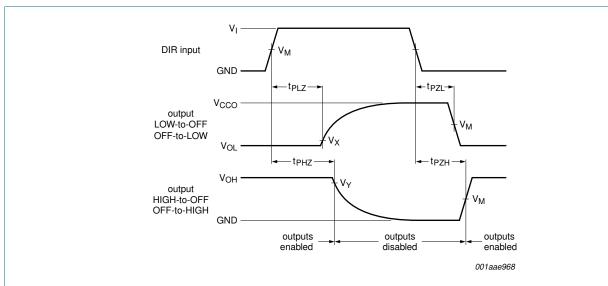

#### 12. Waveforms

Measurement points are given in Table 14.

$\ensuremath{V_{OL}}$  and  $\ensuremath{V_{OH}}$  are typical output voltage levels that occur with the output load.

Fig 6. The data input (nA, nB) to output (nB, nA) propagation delay times

Measurement points are given in Table 14.

V<sub>OL</sub> and V<sub>OH</sub> are typical output voltage levels that occur with the output load.

Fig 7. Enable and disable times

Table 14. Measurement points

| Supply voltage                          | Input[1]            | Output[2]           |                          |                          |

|-----------------------------------------|---------------------|---------------------|--------------------------|--------------------------|

| V <sub>CC(A)</sub> , V <sub>CC(B)</sub> | V <sub>M</sub>      | V <sub>M</sub>      | V <sub>X</sub>           | V <sub>Y</sub>           |

| 1.1 V to 1.6 V                          | 0.5V <sub>CCI</sub> | 0.5V <sub>CCO</sub> | V <sub>OL</sub> + 0.1 V  | $V_{OH} - 0.1 V$         |

| 1.65 V to 2.7 V                         | 0.5V <sub>CCI</sub> | 0.5V <sub>CCO</sub> | V <sub>OL</sub> + 0.15 V | V <sub>OH</sub> – 0.15 V |

| 3.0 V to 3.6 V                          | 0.5V <sub>CCI</sub> | 0.5V <sub>CCO</sub> | V <sub>OL</sub> + 0.3 V  | V <sub>OH</sub> – 0.3 V  |

<sup>[1]</sup>  $V_{CCI}$  is the supply voltage associated with the data input port.

<sup>[2]</sup>  $V_{\text{CCO}}$  is the supply voltage associated with the output port.

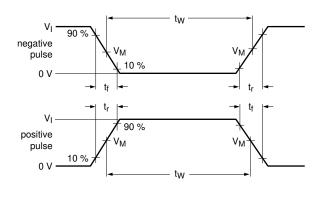

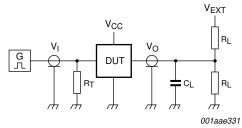

Test data is given in Table 15.

$R_L$  = Load resistance.

$C_L$  = Load capacitance including jig and probe capacitance.

$R_T$  = Termination resistance.

$V_{\text{EXT}}$  = External voltage for measuring switching times.

Fig 8. Test circuit for measuring switching times

Table 15. Test data

| Supply voltage                          | Input              |                 | Load  |      | V <sub>EXT</sub>                    | V <sub>EXT</sub>                    |                                         |  |  |

|-----------------------------------------|--------------------|-----------------|-------|------|-------------------------------------|-------------------------------------|-----------------------------------------|--|--|

| V <sub>CC(A)</sub> , V <sub>CC(B)</sub> | V <sub>I</sub> [1] | Δt/ΔV[2]        | CL    | RL   | t <sub>PLH</sub> , t <sub>PHL</sub> | t <sub>PZH</sub> , t <sub>PHZ</sub> | t <sub>PZL</sub> , t <sub>PLZ</sub> [3] |  |  |

| 1.1 V to 1.6 V                          | $V_{CCI}$          | $\leq$ 1.0 ns/V | 15 pF | 2 kΩ | open                                | GND                                 | 2V <sub>CCO</sub>                       |  |  |

| 1.65 V to 2.7 V                         | $V_{CCI}$          | $\leq$ 1.0 ns/V | 15 pF | 2 kΩ | open                                | GND                                 | 2V <sub>CCO</sub>                       |  |  |

| 3.0 V to 3.6 V                          | $V_{CCI}$          | ≤ 1.0 ns/V      | 15 pF | 2 kΩ | open                                | GND                                 | 2V <sub>CCO</sub>                       |  |  |

[1]  $V_{CCI}$  is the supply voltage associated with the data input port.

[2] dV/dt ≥ 1.0 V/ns

[3]  $V_{CCO}$  is the supply voltage associated with the output port.

#### Dual-bit, dual-supply voltage level translator/transceiver; 3-state

### 13. Application information

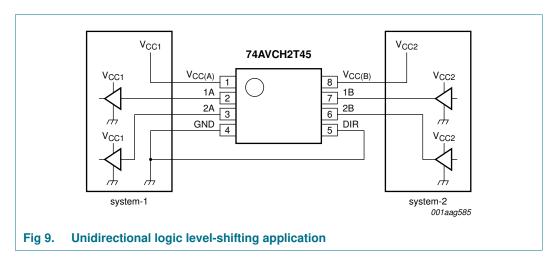

#### 13.1 Unidirectional logic level-shifting application

The circuit given in Figure 9 is an example of the 74AVCH2T45 being used in an unidirectional logic level-shifting application.

Table 16. Unidirectional logic level-shifting application

| Pin | Name               | Function  | Description                                               |

|-----|--------------------|-----------|-----------------------------------------------------------|

| 1   | $V_{\text{CC}(A)}$ | $V_{CC1}$ | supply voltage of system-1 (0.8 V to 3.6 V)               |

| 2   | 1A                 | OUT1      | output level depends on V <sub>CC1</sub> voltage          |

| 3   | 2A                 | OUT2      | output level depends on V <sub>CC1</sub> voltage          |

| 4   | GND                | GND       | device GND                                                |

| 5   | DIR                | DIR       | the GND (LOW level) determines B port to A port direction |

| 6   | 2B                 | IN2       | input threshold value depends on V <sub>CC2</sub> voltage |

| 7   | 1B                 | IN1       | input threshold value depends on V <sub>CC2</sub> voltage |

| 8   | $V_{CC(B)}$        | $V_{CC2}$ | supply voltage of system-2 (0.8 V to 3.6 V)               |

|     |                    |           |                                                           |

#### Dual-bit, dual-supply voltage level translator/transceiver; 3-state

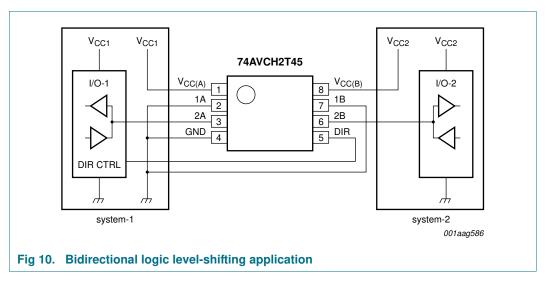

#### 13.2 Bidirectional logic level-shifting application

<u>Figure 10</u> shows the 74AVCH2T45 being used in a bidirectional logic level-shifting application. Since the device does not have an output enable (OE) pin, the system designer should take precautions to avoid bus contention between system-1 and system-2 when changing directions.

<u>Table 17</u> gives a sequence that will illustrate data transmission from system-1 to system-2 and then from system-2 to system-1.

Table 17. Bidirectional logic level-shifting application[1]

| State | DIR CTRL | I/O-1  | I/O-2  | Description                                                                                                               |

|-------|----------|--------|--------|---------------------------------------------------------------------------------------------------------------------------|

| 1     | Н        | output | input  | system-1 data to system-2                                                                                                 |

| 2     | Н        | Z      | Z      | system-2 is getting ready to send data to system-1. I/O-1 and I/O-2 are disabled. The bus-line state depends on bus hold. |

| 3     | L        | Z      | Z      | DIR bit is set LOW. I/O-1 and I/O-2 still are disabled. The bus-line state depends on bus hold.                           |

| 4     | L        | input  | output | system-2 data to system-1                                                                                                 |

<sup>[1]</sup> H = HIGH voltage level;

L = LOW voltage level;

Z = high-impedance OFF-state.

#### Dual-bit, dual-supply voltage level translator/transceiver; 3-state

#### 13.3 Power-up considerations

The device is designed such that no special power-up sequence is required other than GND being applied first.

Table 18. Typical total supply current  $(I_{CC(A)} + I_{CC(B)})$

|                    |                    |                    |       | . ,   | · /   |       |       |    |  |  |  |  |

|--------------------|--------------------|--------------------|-------|-------|-------|-------|-------|----|--|--|--|--|

| V <sub>CC(A)</sub> | V <sub>CC(B)</sub> | V <sub>CC(B)</sub> |       |       |       |       |       |    |  |  |  |  |

|                    | 0 V                | 0.8 V              | 1.2 V | 1.5 V | 1.8 V | 2.5 V | 3.3 V |    |  |  |  |  |

| 0 V                | 0                  | 0.1                | 0.1   | 0.1   | 0.1   | 0.1   | 0.1   | μΑ |  |  |  |  |

| 0.8 V              | 0.1                | 0.1                | 0.1   | 0.1   | 0.1   | 0.7   | 2.3   | μΑ |  |  |  |  |

| 1.2 V              | 0.1                | 0.1                | 0.1   | 0.1   | 0.1   | 0.3   | 1.4   | μΑ |  |  |  |  |

| 1.5 V              | 0.1                | 0.1                | 0.1   | 0.1   | 0.1   | 0.1   | 0.9   | μΑ |  |  |  |  |

| 1.8 V              | 0.1                | 0.1                | 0.1   | 0.1   | 0.1   | 0.1   | 0.5   | μΑ |  |  |  |  |

| 2.5 V              | 0.1                | 0.7                | 0.3   | 0.1   | 0.1   | 0.1   | 0.1   | μΑ |  |  |  |  |

| 3.3 V              | 0.1                | 2.3                | 1.4   | 0.9   | 0.5   | 0.1   | 0.1   | μΑ |  |  |  |  |

#### 13.4 Enable times

The enable times for the 74AVCH2T45 are calculated from the following formulas:

- $t_{en}$  (DIR to nA) =  $t_{dis}$  (DIR to nB) +  $t_{pd}$  (nB to nA)

- $t_{en}$  (DIR to nB) =  $t_{dis}$  (DIR to nA) +  $t_{pd}$  (nA to nB)

In a bidirectional application, these enable times provide the maximum delay from the time the DIR bit is switched until an output is expected. For example, if the 74AVCH2T45 initially is transmitting from A to B, then the DIR bit is switched, the B port of the device must be disabled before presenting it with an input. After the B port has been disabled, an input signal applied to it appears on the corresponding A port after the specified propagation delay.

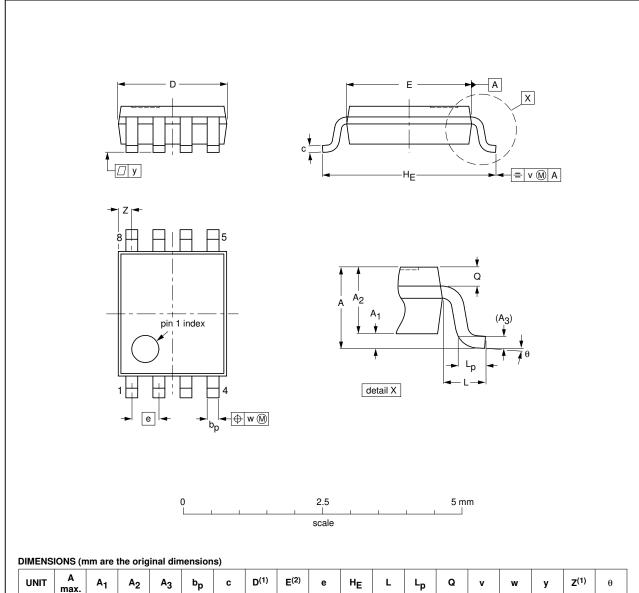

### 14. Package outline

VSSOP8: plastic very thin shrink small outline package; 8 leads; body width 2.3 mm

SOT765-1

| UNIT | A<br>max. | A <sub>1</sub> | A <sub>2</sub> | A <sub>3</sub> | bp           | С            | D <sup>(1)</sup> | E <sup>(2)</sup> | е   | HE         | L   | Lp           | Q            | v   | w    | у   | Z <sup>(1)</sup> | θ        |  |

|------|-----------|----------------|----------------|----------------|--------------|--------------|------------------|------------------|-----|------------|-----|--------------|--------------|-----|------|-----|------------------|----------|--|

| mm   | 1         | 0.15<br>0.00   | 0.85<br>0.60   | 0.12           | 0.27<br>0.17 | 0.23<br>0.08 | 2.1<br>1.9       | 2.4<br>2.2       | 0.5 | 3.2<br>3.0 | 0.4 | 0.40<br>0.15 | 0.21<br>0.19 | 0.2 | 0.13 | 0.1 | 0.4<br>0.1       | 8°<br>0° |  |

- Plastic or metal protrusions of 0.15 mm maximum per side are not included.

Plastic or metal protrusions of 0.25 mm maximum per side are not included.

| OUTLINE  |  | REFER  | EUROPEAN | ISSUE DATE |            |  |

|----------|--|--------|----------|------------|------------|--|

| VERSION  |  | JEDEC  | JEITA    | PROJECTION | ISSUE DATE |  |

| SOT765-1 |  | MO-187 |          |            | 02-06-07   |  |

Fig 11. Package outline SOT765-1 (VSSOP8)

74AVCH2T45

All information provided in this document is subject to legal disclaimers.

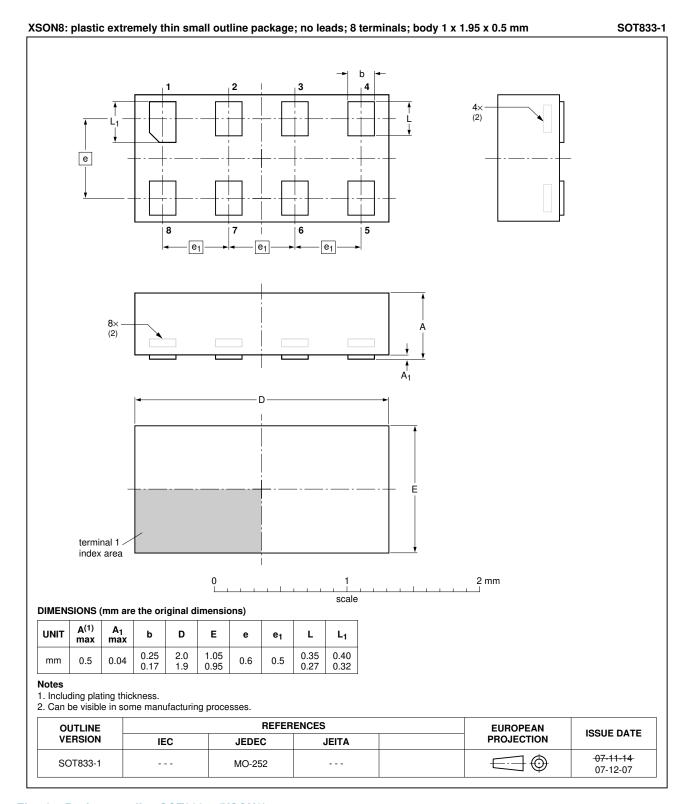

Fig 12. Package outline SOT833-1 (XSON8)

74AVCH2T45 All information provided in this document is subject to legal disclaimers.

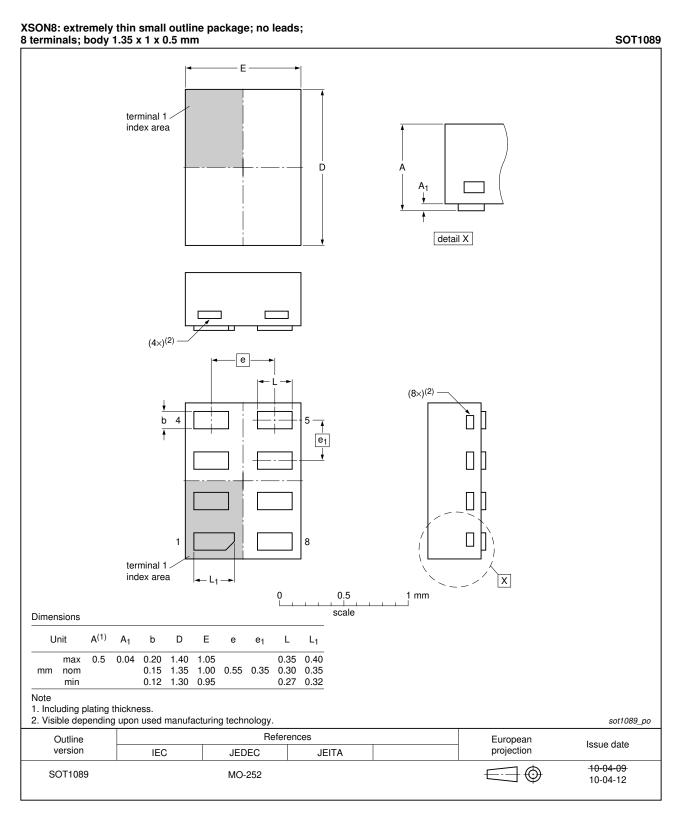

Fig 13. Package outline SOT1089 (XSON8)

74AVCH2T45 All information provided in this document is subject to legal disclaimers.

Fig 14. Package outline SOT996-2 (XSON8)

74AVCH2T45

All information provided in this document is subject to legal disclaimers.

Fig 15. Package outline SOT1116 (XSON8)

74AVCH2T45 All information provided in this document is subject to legal disclaimers.

Fig 16. Package outline SOT1203 (XSON8)

74AVCH2T45 All information provided in this document is subject to legal disclaimers.

### Dual-bit, dual-supply voltage level translator/transceiver; 3-state

### 15. Abbreviations

#### Table 19. Abbreviations

| Acronym | Description             |

|---------|-------------------------|

| CDM     | Charged Device Model    |

| DUT     | Device Under Test       |

| ESD     | ElectroStatic Discharge |

| НВМ     | Human Body Model        |

| MM      | Machine Model           |

### 16. Revision history

#### Table 20. Revision history

|                | -                                |                         |                      |                |

|----------------|----------------------------------|-------------------------|----------------------|----------------|

| Document ID    | Release date                     | Data sheet status       | Change notice        | Supersedes     |

| 74AVCH2T45 v.6 | 20130402                         | Product data sheet      | -                    | 74AVCH2T45 v.5 |

| Modifications: | <ul> <li>For type nun</li> </ul> | nber 74AVCH2T45GD XSON8 | U has changed to XS0 | ON8.           |

| 74AVCH2T45 v.5 | 20111214                         | Product data sheet      | -                    | 74AVCH2T45 v.4 |

| Modifications: | <ul> <li>Legal pages</li> </ul>  | updated.                |                      |                |

| 74AVCH2T45 v.4 | 20101124                         | Product data sheet      | -                    | 74AVCH2T45 v.3 |

| 74AVCH2T45 v.3 | 20090506                         | Product data sheet      | -                    | 74AVCH2T45 v.2 |

| 74AVCH2T45 v.2 | 20090203                         | Product data sheet      | -                    | 74AVCH2T45 v.1 |

| 74AVCH2T45 v.1 | 20070703                         | Product data sheet      | -                    | -              |

|                |                                  |                         |                      |                |