# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

## 74F322 **Octal Serial/Parallel Register with Sign Extend**

#### **General Description**

FAIRCHILD

SEMICONDUCTOR

The 74F322 is an 8-bit shift register with provision for either serial or parallel loading and with 3-STATE parallel outputs plus a bi-state serial output. Parallel data inputs and parallel outputs are multiplexed to minimize pin count. State changes are initiated by the rising edge of the clock. Four synchronous modes of operation are possible: hold (store), shift right with serial entry, shift right with sign extend and parallel load. An asynchronous Master Reset ( $\overline{\text{MR}})$  input overrides clocked operation and clears the register.

April 1988

#### Features

- Multiplexed parallel I/O ports

- Separate serial input and output

- Sign extend function

- 3-STATE outputs for bus applications

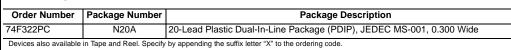

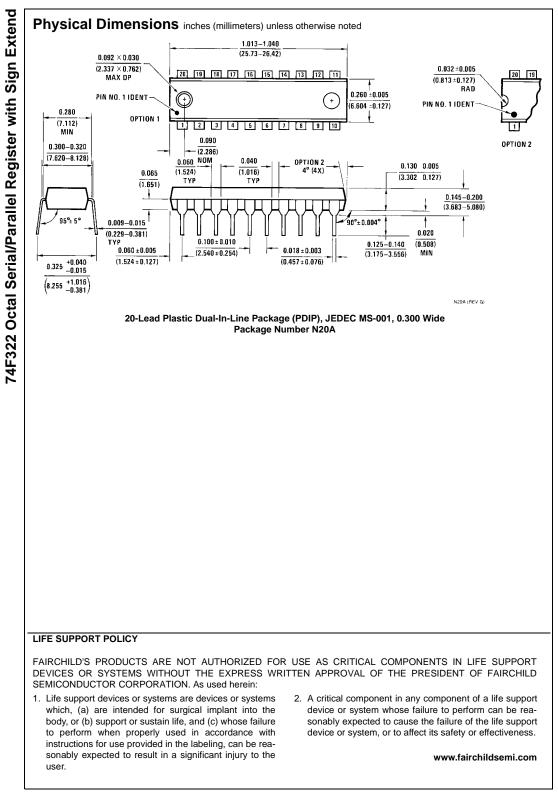

#### **Ordering Code:**

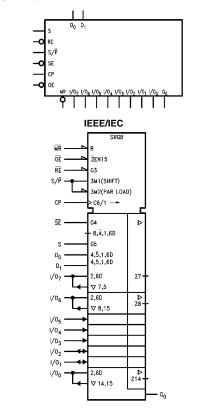

#### Logic Symbols

#### **Connection Diagram**

| _                  |    |    |                   |

|--------------------|----|----|-------------------|

|                    |    |    |                   |

| RE -               | 1  | 20 | -v <sub>cc</sub>  |

| s/P-               | 2  | 19 | -s                |

| D <sub>0</sub> —   | 3  | 18 | - SE              |

| 1/0 <sub>7</sub> — | 4  | 17 | -D1               |

| 1/05-              | 5  | 16 | -1/0 <sub>6</sub> |

| 1/03-              | 6  | 15 | -1/0 <sub>4</sub> |

| 1/0 <sub>1</sub> - | 7  | 14 | -1/0 <sub>2</sub> |

| OE -               | 8  | 13 | -1/0 <sub>0</sub> |

| MR -               | 9  | 12 | - Q <sub>0</sub>  |

| GND —              | 10 | 11 | — CP              |

| L                  |    |    |                   |

www.fairchildsemi.com

#### Unit Loading/Fan Out

| <b>D</b> <sup>1</sup>              |                                                    | U.L.          | Input I <sub>IH</sub> /I <sub>IL</sub>  |

|------------------------------------|----------------------------------------------------|---------------|-----------------------------------------|

| Pin Names                          | Description                                        | HIGH/LOW      | Output I <sub>OH</sub> /I <sub>OL</sub> |

| RE                                 | Register Enable Input (Active LOW)                 | 1.0/1.0       | 20 µA/-0.6 mA                           |

| S/P                                | Serial (HIGH) or Parallel (LOW) Mode Control Input | 1.0/1.0       | 20 µA/–0.6 mA                           |

| SE                                 | Sign Extend Input (Active LOW)                     | 1.0/3.0       | 20 μA/–1.8 mA                           |

| S                                  | Serial Data Select Input                           | 1.0/2.0       | 20 μA/–1.2 mA                           |

| D <sub>0</sub> , D <sub>1</sub>    | Serial Data Inputs                                 | 1.0/1.0       | 20 µA/–0.6 mA                           |

| СР                                 | Clock Pulse Input (Active Rising Edge)             | 1.0/1.0       | 20 µA/–0.6 mA                           |

| MR                                 | Asynchronous Master Reset Input (Active LOW)       | 1.0/1.0       | 20 µA/–0.6 mA                           |

| OE                                 | 3-STATE Output Enable Input (Active LOW)           | 1.0/1.0       | 20 µA/–0.6 mA                           |

| Q <sub>0</sub>                     | Bi-State Serial Output                             | 50/33.3       | –1 mA/–20 mA                            |

| I/O <sub>0</sub> –I/O <sub>7</sub> | Multiplexed Parallel Data Inputs or                | 3.5/1.083     | 70 μA/–0.65 mA                          |

|                                    | 3-STATE Parallel Data Outputs                      | 150/40 (33.3) | -3 mA/24 mA (20 mA)                     |

#### **Functional Description**

The 74F322 contains eight D-type edge triggered flip-flops and the interstage gating required to perform right shift and the intrastage gating necessary for hold and synchronous parallel load operations. A LOW signal on  $\overline{RE}$  enables shifting or parallel loading, while a HIGH signal enables the hold mode. A HIGH signal on S/ $\overline{P}$  enables shift right, while a LOW signal disables the 3-STATE output buffers and enables parallel loading. In the shift right mode a HIGH signal on  $\overline{SE}$  enables serial entry from either  $D_0$  or  $D_1$ , as determined by the S input. A LOW signal on  $\overline{SE}$  enables shift right but  $Q_7$  reloads its contents, thus performing the sign extend function required for the 74F384 Twos Complement Multiplier. A HIGH signal on  $\overline{OE}$  disables the 3-STATE output buffers, regardless of the other control inputs. In this condition the shifting and loading operations can still be performed.

#### Mode Select Table

|          |    |    |     | Inpu | ts |                |    |                  |                  |                  | Out              | puts             |                  |                  |                  |                |

|----------|----|----|-----|------|----|----------------|----|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|----------------|

| Mode     | MR | RE | S/P | SE   | S  | OE<br>(Note 1) | СР | I/O <sub>7</sub> | I/O <sub>6</sub> | I/O <sub>5</sub> | I/O <sub>4</sub> | I/O <sub>3</sub> | I/O <sub>2</sub> | I/O <sub>1</sub> | I/O <sub>0</sub> | Q <sub>0</sub> |

| Clear    | L  | Х  | Х   | Х    | Х  | L              | Х  | L                | L                | L                | L                | L                | L                | L                | L                | L              |

|          | L  | х  | Х   | х    | Х  | н              | Х  | Z                | Z                | Z                | Z                | Z                | Z                | Z                | Ζ                | L              |

| Parallel | Н  | L  | L   | Х    | Х  | Х              | ~  | ۱ <sub>7</sub>   | $I_6$            | $I_5$            | $I_4$            | $I_3$            | $I_2$            | I <sub>1</sub>   | I <sub>0</sub>   | I <sub>0</sub> |

| Load     |    |    |     |      |    |                |    |                  |                  |                  |                  |                  |                  |                  |                  |                |

| Shift    | Н  | L  | Н   | Н    | L  | L              | ~  | D <sub>0</sub>   | 0 <sub>7</sub>   | O <sub>6</sub>   | O <sub>5</sub>   | O <sub>4</sub>   | O <sub>3</sub>   | O <sub>2</sub>   | 0 <sub>1</sub>   | 0 <sub>1</sub> |

| Right    | н  | L  | н   | н    | Н  | L              | ~  | D <sub>1</sub>   | 0 <sub>7</sub>   | O <sub>6</sub>   | $O_5$            | O <sub>4</sub>   | O <sub>3</sub>   | O <sub>2</sub>   | 0 <sub>1</sub>   | 0 <sub>1</sub> |

| Sign     | Н  | L  | Н   | L    | Х  | L              | ~  | 07               | O <sub>7</sub>   | O <sub>6</sub>   | O <sub>5</sub>   | O <sub>4</sub>   | O <sub>3</sub>   | O <sub>2</sub>   | 0 <sub>1</sub>   | 0 <sub>1</sub> |

| Extend   |    |    |     |      |    |                |    |                  |                  |                  |                  |                  |                  |                  |                  |                |

| Hold     | н  | н  | Х   | Х    | Х  | L              | ~  | NC               | NC             |

H = HIGH Voltage Level L = LOW Voltage Level

Z = High Impedance Output State

$rac{1}{2}$  = LOW-to-HIGH Transition

NC = No Change

Note:  $|_{7}-I_{0} = The$  level of the steady-state input at the respective I/O terminal is loaded into the flip-flop while the flip-flop outputs (except Q<sub>0</sub>) are isolated from the I/O terminal.

Note:  $D_0$ ,  $D_1$  = The level of the steady-state inputs to the serial multiplexer input.

Note:  $O_7 - O_0 =$  The level of the respective  $Q_n$  flip-flop prior to the last Clock LOW-to-HIGH transition.

Note 1: When the OE input is HIGH all I/On terminals are at the high impedance state; sequential operation or clearing of the register is not affected.

www.fairchildsemi.com

#### Absolute Maximum Ratings(Note 2)

| Storage Temperature                         | –65°C to +150°C                                 |

|---------------------------------------------|-------------------------------------------------|

| Ambient Temperature under Bias              | $-55^{\circ}C$ to $+125^{\circ}C$               |

| Junction Temperature under Bias             | -55°C to +150°C                                 |

| V <sub>CC</sub> Pin Potential to Ground Pin | -0.5V to +7.0V                                  |

| Input Voltage (Note 3)                      | -0.5V to +7.0V                                  |

| Input Current (Note 3)                      | -30 mA to +5.0 mA                               |

| Voltage Applied to Output                   |                                                 |

| in HIGH State (with $V_{CC} = 0V$ )         |                                                 |

| Standard Output                             | -0.5V to V <sub>CC</sub>                        |

| 3-STATE Output                              | -0.5V to +5.5V                                  |

| Current Applied to Output                   |                                                 |

| in LOW State (Max)                          | twice the rated $\mathrm{I}_{\mathrm{OL}}$ (mA) |

|                                             |                                                 |

## Recommended Operating Conditions

| Free Air Ambient Temperature |  |

|------------------------------|--|

| Supply Voltage               |  |

0°C to +70°C +4.5V to +5.5V

Note 2: Absolute maximum ratings are values beyond which the device may be damaged or have its useful life impaired. Functional operation under these conditions is not implied.

Note 3: Either voltage limit or current limit is sufficient to protect inputs.

#### **DC Electrical Characteristics**

| Symbol            | Parame                            | ter                 | Min  | Тур | Max  | Units | V <sub>CC</sub>         | Conditions                                                                             |

|-------------------|-----------------------------------|---------------------|------|-----|------|-------|-------------------------|----------------------------------------------------------------------------------------|

| V <sub>IH</sub>   | Input HIGH Voltage                |                     | 2.0  |     |      | V     |                         | Recognized as a HIGH Signal                                                            |

| VIL               | Input LOW Voltage                 |                     |      |     | 0.8  | V     |                         | Recognized as a LOW Signal                                                             |

| V <sub>CD</sub>   | Input Clamp Diode Volta           | age                 |      |     | -1.2 | V     | Min                     | $I_{IN} = -18 \text{ mA}$                                                              |

| V <sub>OH</sub>   | Output HIGH Voltage               | 10% V <sub>CC</sub> | 2.5  |     |      |       |                         | $I_{OH} = -1 \text{ mA} (Q_0, I/O_n)$                                                  |

|                   |                                   | 10% V <sub>CC</sub> | 2.4  |     |      | v     | Min                     | $I_{OH} = -3 \text{ mA} (I/O_n)$                                                       |

|                   |                                   | 5% V <sub>CC</sub>  | 2.7  |     |      | v     | IVIIN                   | $I_{OH} = -1 \text{ mA} (Q_0, I/O_n)$                                                  |

|                   |                                   | 5% V <sub>CC</sub>  | 2.7  |     |      |       |                         | $I_{OH} = -3 \text{ mA} (I/O_n)$                                                       |

| V <sub>OL</sub>   | Output LOW Voltage                | 10% V <sub>CC</sub> |      |     | 0.5  | V     | Min                     | $I_{OL} = 20 \text{ mA} (Q_0)$                                                         |

|                   |                                   | 10% V <sub>CC</sub> |      |     | 0.5  |       |                         | I <sub>OL</sub> = 24 mA (I/O <sub>n</sub> )                                            |

| IIH               | Input HIGH Current                |                     |      |     | 5.0  | μA    | Max                     | $V_{IN} = 2.7V$                                                                        |

| I <sub>BVI</sub>  | Input HIGH Current Breakdown Test |                     |      |     | 7.0  | μΑ    | Max                     | V <sub>IN</sub> = 7.0V (Non-I/O Inputs)                                                |

| I <sub>BVIT</sub> | Input HIGH Current Bre            |                     |      | 0.5 | mA   | Max   | $V_{IN} = 5.5V (I/O_n)$ |                                                                                        |

| ICEX              | Output HIGH Leakage Current       |                     |      |     | 50   | μΑ    | Max                     | V <sub>OUT</sub> = V <sub>CC</sub>                                                     |

| V <sub>ID</sub>   | Input Leakage                     |                     | 4.75 |     |      | V     | 0.0                     | I <sub>ID</sub> = 1.9 μA                                                               |

|                   | Test                              |                     |      |     |      |       |                         | All Other Pins Grounded                                                                |

| I <sub>OD</sub>   | Output Leakage                    |                     |      |     | 3.75 | μΑ    | 0.0                     | V <sub>IOD</sub> = 150 mV                                                              |

|                   | Circuit Current                   |                     |      |     |      |       |                         | All Other Pins Grounded                                                                |

| IIL               | Input LOW Current                 |                     |      |     | -0.6 | mA    | Max                     | $V_{IN} = 0.5V (\overline{RE}, S/\overline{P}, D_n, CP, \overline{MR}, \overline{OE})$ |

|                   |                                   |                     |      |     | -1.2 | mA    | Max                     | V <sub>IN</sub> = 0.5V (S)                                                             |

|                   |                                   |                     |      |     | -1.8 | mA    | Max                     | $V_{\rm IN} = 0.5 V (\overline{\rm SE})$                                               |

| I <sub>IH</sub> + | Output Leakage Curren             | t                   |      |     | 70   | μA    | Max                     | $V_{I/O} = 2.7V (I/O_n)$                                                               |

| I <sub>OZH</sub>  |                                   |                     |      |     |      |       |                         |                                                                                        |

| I <sub>IL</sub> + | Output Leakage Curren             | t                   |      |     | -650 | μΑ    | Max                     | $V_{I/O} = 0.5V (I/O_n)$                                                               |

| I <sub>OZL</sub>  |                                   |                     |      |     |      |       |                         |                                                                                        |

| I <sub>OS</sub>   | Output Short-Circuit Cu           | rrent               | -60  |     | -150 | mA    | Max                     | V <sub>OUT</sub> = 0V                                                                  |

| I <sub>ZZ</sub>   | Bus Drainage Test                 |                     |      |     | 500  | μA    | 0.0V                    | V <sub>OUT</sub> = 5.25V                                                               |

| I <sub>CC</sub>   | Power Supply Current              |                     |      | 60  | 90   | mA    | Max                     |                                                                                        |

### **AC Electrical Characteristics**

| Symbol           | Parameter               |     | $T_{A} = +25^{\circ}C$<br>$V_{CC} = +5.0V$ | ,    |     | C to +125°C<br>50 pF | T <sub>A</sub> = 0°C<br>C <sub>L</sub> = | Units |     |

|------------------|-------------------------|-----|--------------------------------------------|------|-----|----------------------|------------------------------------------|-------|-----|

|                  |                         | Min | С <sub>L</sub> = 50 pF<br>Тур              | Max  | Min | Max                  | Min                                      | Max   |     |

| f <sub>MAX</sub> | Maximum Clock Frequency | 70  | 90                                         |      | 50  |                      | 70                                       |       | MHz |

| t <sub>PLH</sub> | Propagation Delay       | 3.5 | 7.0                                        | 7.5  | 3.5 | 9.5                  | 3.5                                      | 8.5   | ns  |

| t <sub>PHL</sub> | CP to I/On              | 5.0 | 8.5                                        | 11.0 | 3.5 | 10.0                 | 5.0                                      | 12.0  |     |

| t <sub>PLH</sub> | Propagation Delay       | 3.5 | 7.0                                        | 9.0  | 3.5 | 11.0                 | 3.5                                      | 10.0  |     |

| t <sub>PHL</sub> | CP to Q <sub>0</sub>    | 3.5 | 7.0                                        | 8.0  | 3.5 | 10.0                 | 3.5                                      | 9.0   |     |

| t <sub>PHL</sub> | Propagation Delay       | 6.0 | 10.0                                       | 13.0 | 6.0 | 15.0                 | 6.0                                      | 14.0  | ns  |

|                  | MR to I/On              |     |                                            |      |     |                      |                                          |       |     |

| t <sub>PHL</sub> | Propagation Delay       | 5.5 | 7.5                                        | 12.0 | 5.5 | 14.0                 | 5.5                                      | 13.0  | ns  |

|                  | MR to Q <sub>0</sub>    |     |                                            |      |     |                      |                                          |       |     |

| t <sub>PZH</sub> | Output Enable Time      | 3.0 | 6.5                                        | 9.0  | 3.0 | 12.5                 | 3.0                                      | 10.0  | ns  |

| t <sub>PZL</sub> | OE to I/On              | 4.0 | 8.5                                        | 11.0 | 4.0 | 14.5                 | 4.0                                      | 12.0  |     |

| t <sub>PHZ</sub> | Output Disable Time     | 2.0 | 4.5                                        | 6.0  | 2.0 | 8.0                  | 2.0                                      | 7.0   |     |

| t <sub>PLZ</sub> | OE to I/On              | 2.0 | 5.0                                        | 7.0  | 2.0 | 10.0                 | 2.0                                      | 8.0   |     |

| t <sub>PZH</sub> | Output Enable Time      | 4.5 | 8.0                                        | 10.5 | 4.5 | 13.5                 | 4.5                                      | 11.5  | ns  |

| t <sub>PZL</sub> | S/P to I/On             | 5.5 | 10.0                                       | 14.0 | 5.5 | 17.0                 | 5.5                                      | 15.0  |     |

| t <sub>PHZ</sub> | Output Disable Time     | 5.0 | 9.0                                        | 11.5 | 5.0 | 16.5                 | 5.0                                      | 12.5  |     |

| t <sub>PLZ</sub> | S/P to I/On             | 6.0 | 12.0                                       | 15.5 | 6.0 | 19.5                 | 6.0                                      | 16.5  |     |

### AC Operating Requirements

|                    |                                                           | <b>T</b> <sub>A</sub> = - | +25°C         | $T_A = -55^{\circ}C$ | to +125°C | $T_A = 0C$ | Units |     |

|--------------------|-----------------------------------------------------------|---------------------------|---------------|----------------------|-----------|------------|-------|-----|

| Symbol             | Parameter                                                 | V <sub>CC</sub> =         | + <b>5.0V</b> |                      |           |            |       |     |

|                    |                                                           | Min                       | Max           | Min                  | Max       | Min        | Max   |     |

| t <sub>S</sub> (H) | Setup Time, HIGH or LOW                                   | 6.0                       |               | 14.0                 |           | 7.0        |       |     |

| t <sub>S</sub> (L) | RE to CP                                                  | 14.0                      |               | 18.0                 |           | 16.0       |       | ns  |

| t <sub>H</sub> (H) | Hold Time, HIGH or LOW                                    | 0                         |               | 0                    |           | 0          |       |     |

| t <sub>H</sub> (L) | RE to CP                                                  | 0                         |               | 0                    |           | 0          |       | ns  |

| t <sub>S</sub> (H) | Setup Time, HIGH or LOW                                   | 6.5                       |               | 8.5                  |           | 7.5        |       |     |

| t <sub>S</sub> (L) | D <sub>0</sub> , D <sub>1</sub> or I/O <sub>n</sub> to CP | 6.5                       |               | 8.5                  |           | 7.5        |       | ns  |

| t <sub>H</sub> (H) | Hold Time, HIGH or LOW                                    | 2.0                       |               | 3.0                  |           | 3.0        |       | ns  |

| t <sub>H</sub> (L) | D <sub>0</sub> , D <sub>1</sub> or I/O <sub>n</sub> to CP | 2.0                       |               | 3.0                  |           | 3.0        |       | 115 |

| t <sub>S</sub> H)  | Setup Time, HIGH or LOW                                   | 7.0                       |               | 9.0                  |           | 8.0        |       |     |

| t <sub>S</sub> (L) | SE to CP                                                  | 2.5                       |               | 11.0                 |           | 3.5        |       | ns  |

| t <sub>H</sub> (H) | Hold Time, HIGH or LOW                                    | 2.0                       |               | 2.0                  |           | 2.0        |       |     |

| t <sub>H</sub> (L) | SE to CP                                                  | 0.0                       |               | 1.0                  |           | 0.0        |       | ns  |

| t <sub>S</sub> (H) | Setup Time, HIGH or LOW                                   | 11.0                      |               | 13.0                 |           | 12.0       |       |     |

| t <sub>S</sub> (L) | S/P to CP                                                 | 13.5                      |               | 21.0                 |           | 15.5       |       | ns  |

| t <sub>S</sub> (H) | Setup Time, HIGH or LOW                                   | 6.5                       |               | 8.5                  |           | 7.5        |       |     |

| t <sub>S</sub> (L) | S to CP                                                   | 9.0                       |               | 11.0                 |           | 10.0       |       | ns  |

| t <sub>H</sub> (H) | Hold Time, HIGH or LOW                                    | 0                         |               | 1.0                  |           | 0          |       |     |

| t <sub>H</sub> (L) | S or S/P to CP                                            | 0                         |               | 0                    |           | 0          |       | ns  |

| t <sub>W</sub> (H) | CP Pulse Width, HIGH or LOW                               | 7.0                       |               | 8.0                  |           | 7.0        |       | ns  |

| t <sub>W</sub> (L) |                                                           |                           |               |                      |           |            |       |     |

| t <sub>W</sub> (L) | MR Pulse Width, LOW                                       | 5.5                       |               | 7.5                  |           | 6.5        |       |     |

| t <sub>REC</sub>   | Recovery Time                                             | 8.0                       |               | 12.0                 |           | 8.0        |       | ns  |

|                    | MR to CP                                                  |                           |               |                      |           |            |       |     |

74F322

www.fairchildsemi.com

Fairchild does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and Fairchild reserves the right at any time without notice to change said circuitry and specifications.