Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

February 1989 Revised August 1999

#### 74F899

# 9-Bit Latchable Transceiver with Parity Generator/Checker

#### **General Description**

The 74F899 is a 9-bit to 9-bit parity transceiver with transparent latches. The device can operate as a feed-through transceiver or it can generate/check parity from the 8-bit data busses in either direction. It has a guaranteed current sinking capability of 24 mA at the A-bus and 64 mA at the

The 74F899 features independent latch enables for the A-to-B direction and the B-to-A direction, a select pin for ODD/EVEN parity, and separate error signal output pins for checking parity.

#### **Features**

- Latchable transceiver with output sink of 24 mA at the A-bus and 64 mA at the B-bus

- Option to select generate parity and check or "feed-through" data/parity in directions A-to-B or B-to-A

- Independent latch enables for A-to-B and B-to-A directions

- Select pin for ODD/EVEN parity

- ERRA and ERRB output pins for parity checking

- Ability to simultaneously generate and check parity

- May be used in systems applications in place of the 74F543 and 74F280

- May be used in system applications in place of the 74F657 and 74F373 (no need to change T/R to check parity)

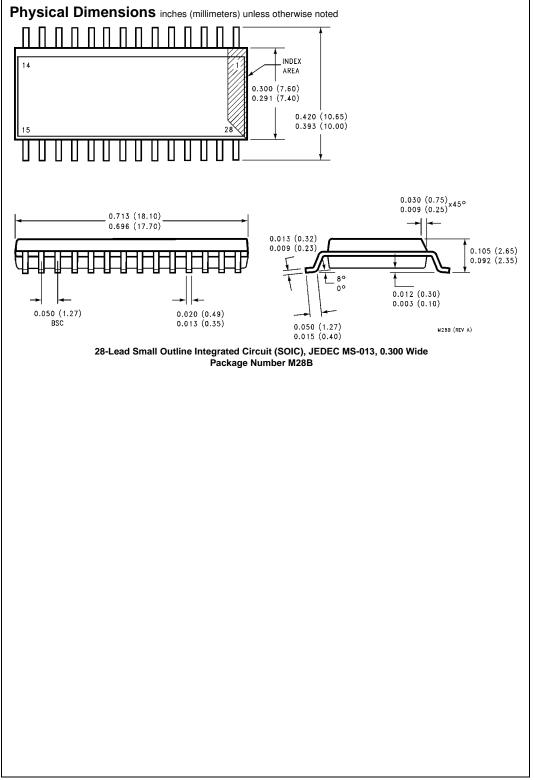

#### **Ordering Code:**

| Order Number | Package Number | Package Description                                                       |

|--------------|----------------|---------------------------------------------------------------------------|

| 74F899SC     | M28B           | 28-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-013, 0.300 Wide |

| 74F899QC     | V28A           | 28-Lead Plastic Lead Chip Carrier (PLCC), JEDEC MO-047, 0.450 Square      |

Devices also available in Tape and Reel. Specify by appending the suffix letter "X" to the ordering code.

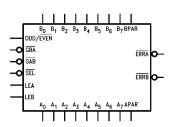

#### **Connection Diagrams**

# A3 A2 A1 8 77 6 5 4 A2 2 ERRA 1 DOD/EVEN 2 GAB 2 B2 Pin Assignment for PCC APAR 12 GBA 13 GND 14 SEL 116 1 BPAR 18

19 20 21 22 23 24 25 B7 B6 B5 B4 B3 B2 B1

#### **Logic Symbol**

## **Input Loading/Fan-Out**

|                                |                      | HIGH/LOW  |                                         |  |  |  |

|--------------------------------|----------------------|-----------|-----------------------------------------|--|--|--|

| Pin Names                      | Description          | U.L.      | Input I <sub>IH</sub> /I <sub>IL</sub>  |  |  |  |

|                                |                      | HIGH/LOW  | Output I <sub>OH</sub> /I <sub>OL</sub> |  |  |  |

| A <sub>0</sub> -A <sub>7</sub> | Data Inputs/         | 1.0/1.0   | 20 μA/–0.6 mA                           |  |  |  |

|                                | Data Outputs         | 150/40    | −3 mA/24 mA                             |  |  |  |

| B <sub>0</sub> –B <sub>7</sub> | Data Inputs/         | 1.0/1.0   | 20 μA/-0.6 mA                           |  |  |  |

|                                | Data Outputs         | 600/106.6 | -12 mA/64 mA                            |  |  |  |

| APAR                           | A Bus Parity         | 1.0/1.0   | 20 μA/-0.6 mA                           |  |  |  |

|                                | Input/Output         | 150/40    | −3 mA/24 mA                             |  |  |  |

| BPAR                           | B Bus Parity         | 1.0/1.0   | 20 μA/-0.6 mA                           |  |  |  |

|                                | Input/Output         | 600/106.6 | -12 mA/64 mA                            |  |  |  |

| ODD/EVEN                       | Parity Select Input  | 1.0/1.0   | 20 μA/-0.6 mA                           |  |  |  |

| GBA, GAB                       | Output Enable Inputs | 1.0/1.0   | 20 μA/-0.6 mA                           |  |  |  |

| SEL                            | Mode Select Input    | 1.0/1.0   | 20 μA/-0.6 mA                           |  |  |  |

| LEA, LEB                       | Latch Enable Inputs  | 1.0/1.0   | 20 μA/-0.6 mA                           |  |  |  |

| ERRA, ERRB                     | Error Signal Outputs | 50/33.3   | −1 mA/20 mA                             |  |  |  |

## **Pin Descriptions**

| Pin Names                      | Description                                                                     |  |  |  |  |  |

|--------------------------------|---------------------------------------------------------------------------------|--|--|--|--|--|

| A <sub>0</sub> -A <sub>7</sub> | A Bus Data Inputs/Data Outputs                                                  |  |  |  |  |  |

| B <sub>0</sub> –B <sub>7</sub> | B Bus Data Inputs/Data Outputs                                                  |  |  |  |  |  |

| APAR, BPAR                     | A and B Bus Parity Inputs                                                       |  |  |  |  |  |

| ODD/EVEN                       | ODD/EVEN Parity Select, Active LOW for EVEN Parity                              |  |  |  |  |  |

| GBA, GAB                       | Output Enables for A or B Bus, Active LOW                                       |  |  |  |  |  |

| SEL                            | Select Pin for Feed-Through or Generate Mode, LOW for Generate Mode             |  |  |  |  |  |

| LEA, LEB                       | Latch Enables for A and B Latches, HIGH for Transparent Mode                    |  |  |  |  |  |

| ERRA, ERRB                     | Error Signals for Checking Generated Parity with Parity In, LOW if Error Occurs |  |  |  |  |  |

#### **Functional Description**

The 74F899 has three principal modes of operation which are outlined below. These modes apply to both the A-to-B and B-to-A directions.

- Bus A (B) communicates to Bus B (A), parity is generated and passed on to the B (A) Bus as BPAR (APAR). If LEB (LEA) is HIGH and the Mode Select (SEL) is LOW, the parity generated from B[0:7] (A[0:7]) can be checked and monitored by ERRB (ERRA).

- Bus A (B) communicates to Bus B (A) in a feed-through mode if <u>SEL</u> is <u>HIGH</u>. <u>Parity</u> is still generated and checked as <u>ERRA</u> and <u>ERRB</u> in the feed-through mode (can be used as an interrupt to signal a data/parity bit error to the CPU).

- Independent Latch Enables (LEA and LEB) allow other permutations of generating/checking (see Function Table).

## **Function Table**

| Inputs |     |     |     |     |                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

|--------|-----|-----|-----|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| GAB    | GBA | SEL | LEA | LEB | Operation                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

| Н      | Н   | Х   | Χ   | Х   | Busses A and B are 3-STATE.                                                                                                                                                                                                                                        |  |  |  |  |  |  |

| Н      | L   | L   | L   | Н   | Generates parity from B[0:7] based on O/ $\overline{E}$ (Note 1). Generated parity $\to$ APAR. Generated parity checked against BPAR and output as $\overline{ERRB}$ .                                                                                             |  |  |  |  |  |  |

| Н      | L   | L   | Н   | Н   | Generates parity from B[0:7] based on $O/\overline{E}$ . Generated parity $\to$ APAR. Generated parity checked against BPAR and output as $\overline{ERRB}$ . Generated parity also fed back through the A latch for generate/check as $\overline{ERRA}$ .         |  |  |  |  |  |  |

| Н      | L   | L   | Х   | L   | Generates parity from B latch data based on O/E. Generated parity → APAR. Generated parity checked against latched BPAR and output as ERRB.                                                                                                                        |  |  |  |  |  |  |

| Н      | L   | Н   | Х   | Н   | BPAR/B[0:7] → APAR/A0:7] Feed-through mode. Generated parity checked against BPAR and output as ERRB.                                                                                                                                                              |  |  |  |  |  |  |

| Н      | L   | Н   | Н   | Н   | $BPAR/B[0:7] \to APAR/A[0:7]$                                                                                                                                                                                                                                      |  |  |  |  |  |  |

|        |     |     |     |     | Feed-through mode. Generated parity checked against BPAR and output <u>as ERRB.</u><br>Generated parity also fed back through the A latch for generate/check as ERRA.                                                                                              |  |  |  |  |  |  |

| L      | Н   | L   | Н   | L   | Generates parity for A[0:7] based on $O/\overline{E}$ . Generated parity $\to$ BPAR. Generated parity checked against APAR and output as ERRA.                                                                                                                     |  |  |  |  |  |  |

| L      | Н   | L   | Н   | Н   | Generates parity from A[0:7] based on $O/\overline{E}$ . Generated parity $\rightarrow$ BPAR. Generated parity checked against APAR and output as $\overline{ERRA}$ . Generated parity also fed back through the B latch for generate/check as $\overline{ERRB}$ . |  |  |  |  |  |  |

| L      | Н   | L   | L   | Х   | Generates parity from A latch data based on O/E. Generated parity → BPAR. Generated parity checked against latched APAR and output as ERRA.                                                                                                                        |  |  |  |  |  |  |

| L      | Н   | Н   | Н   | L   | $APAR/A[0:7] \to BPAR/B[0:7]$                                                                                                                                                                                                                                      |  |  |  |  |  |  |

|        |     |     |     |     | Feed-through mode. Generated parity checked against APAR and output as ERRA.                                                                                                                                                                                       |  |  |  |  |  |  |

| L      | Н   | Н   | Н   | Н   | $APAR/A[0:7] \to BPAR/B[0:7]$                                                                                                                                                                                                                                      |  |  |  |  |  |  |

|        |     |     |     |     | Feed-through mode. Generated parity checked against APAR and output <u>as ERRA</u> . Generated parity also fed back through the B latch for generate/check as ERRB.                                                                                                |  |  |  |  |  |  |

H = HIGH Voltage Level

Note 1:  $O/\overline{E} = ODD/\overline{EVEN}$

L = LOW Voltage Level

X = Immaterial

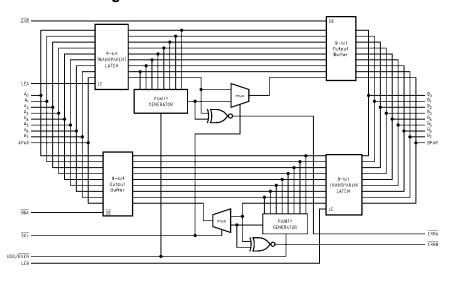

# **Functional Block Diagram**

#### Absolute Maximum Ratings(Note 2)

# Recommended Operating Conditions

Storage Temperature -65°C to +150°C

$\begin{tabular}{lll} Ambient Temperature under Bias & $-55^{\circ}$C to $+125^{\circ}$C \\ Junction Temperature under Bias & $-55^{\circ}$C to $+150^{\circ}$C \\ \end{tabular}$

$\begin{array}{lll} \mbox{V}_{\mbox{CC}} \mbox{ Pin Potential to Ground Pin} & -0.5\mbox{V to } +7.0\mbox{V} \\ \mbox{Input Voltage (Note 3)} & -0.5\mbox{V to } +7.0\mbox{V} \\ \mbox{Input Current (Note 3)} & -30\mbox{ mA to } +5.0\mbox{ mA} \\ \end{array}$

Voltage Applied to Output in HIGH State (with  $V_{CC} = 0V$ )

$\begin{array}{ll} \mbox{Standard Output} & -0.5\mbox{V to V}_{\mbox{CC}} \\ \mbox{3-STATE Output} & -0.5\mbox{V to } +5.5\mbox{V} \end{array}$

Current Applied to Output

in LOW State (Max) Twice the Rated  $I_{OL}$  (mA) ESD Last Passing Voltage (Min) 4000V

Free Air Ambient Temperature  $0^{\circ}\text{C to } +70^{\circ}\text{C}$  Supply Voltage +4.5V to +5.5V

**Note 2:** Absolute maximum ratings are values beyond which the device may be damaged or have its useful life impaired. Functional operation under these conditions is not implied.

Note 3: Either voltage limit or current limit is sufficient to protect inputs.

#### **DC Electrical Characteristics**

| Symbol            | Param              | eter                | Min  | Тур  | Max  | Units    | V <sub>CC</sub>                             | Conditions                                                               |

|-------------------|--------------------|---------------------|------|------|------|----------|---------------------------------------------|--------------------------------------------------------------------------|

| V <sub>IH</sub>   | Input HIGH Voltage |                     | 2.0  |      |      | V        |                                             | Recognized as a                                                          |

|                   |                    |                     |      |      |      |          |                                             | HIGH Signal                                                              |

| V <sub>IL</sub>   | Input LOW Voltage  |                     |      |      | 8.0  | V        |                                             | Recognized as a                                                          |

|                   |                    |                     |      |      |      |          |                                             | LOW Signal                                                               |

| V <sub>CD</sub>   | Input Clamp Diode  | Voltage             |      |      | -1.2 | V        | Min                                         | I <sub>IN</sub> = -18 mA                                                 |

| V <sub>OH</sub>   | Output HIGH        | 10% V <sub>CC</sub> | 2.5  |      |      |          |                                             | $I_{OH} = -1 \text{ mA}$                                                 |

|                   | Voltage            | 10% V <sub>CC</sub> | 2.4  |      |      |          |                                             | $I_{OH} = -3 \text{ mA}$                                                 |

|                   |                    | 10% V <sub>CC</sub> | 2.0  |      |      | V        |                                             | $I_{OH} = -15 \text{ mA } (B_n, BPAR)$                                   |

|                   |                    | 5% V <sub>CC</sub>  | 2.7  |      |      |          |                                             | $I_{OH} = -1 \text{ mA}$                                                 |

|                   |                    | 5% V <sub>CC</sub>  | 2.7  |      |      |          |                                             | $I_{OH} = -3 \text{ mA}$                                                 |

| V <sub>OL</sub>   | Output LOW         | 10% V <sub>CC</sub> |      |      | 0.5  |          |                                             | I <sub>OL</sub> = 20 mA                                                  |

|                   | Voltage            |                     |      |      |      |          |                                             | (A <sub>n</sub> , APAR, ERRA, ERRB)                                      |

|                   |                    | 5% V <sub>CC</sub>  |      |      | 0.55 | V        |                                             | I <sub>OL</sub> = 24 mA                                                  |

|                   |                    | 00                  |      |      |      |          |                                             | (A <sub>n</sub> , APAR, ERRA, ERRB)                                      |

|                   |                    | 10% V <sub>CC</sub> |      |      | 0.55 |          |                                             | I <sub>OL</sub> = 64 mA (B <sub>n</sub> , BPAR)                          |

| V <sub>TH</sub>   | Input Threshold Vo |                     |      | 1.45 | 0.00 | V        |                                             | ±0.1V, Sweep Edge Rate must be > 1V/50 ns                                |

| V <sub>OLV</sub>  | Negative Ground B  | •                   |      |      |      |          |                                             | Observed on "quiet" output during                                        |

| OLV               | Voltage            |                     |      | 1.0  |      | V        |                                             | simultaneous switching of remaining outputs                              |

| V <sub>OLP</sub>  | Positive Ground Bo | ounce               |      |      |      |          |                                             | Observed on "quiet" output during                                        |

| OLI               | Voltage            |                     | 1.0  |      | V    |          | simultaneous switching of remaining outputs |                                                                          |

| I <sub>IL</sub>   | Input Low Current  |                     |      |      | -0.6 | mA       | Max                                         | V <sub>IN</sub> = 0.5V                                                   |

| I <sub>IH</sub>   | Input HIGH         |                     |      |      |      |          |                                             |                                                                          |

|                   | Current            |                     |      |      | 5.0  | μA       | Max                                         | $V_{IN} = 2.7V$                                                          |

| I <sub>BVI</sub>  | Input HIGH Curren  | t                   |      |      |      | _        |                                             | V <sub>IN</sub> = 7.0V                                                   |

|                   | Breakdown Test     |                     |      |      | 7.0  | μΑ       | Max                                         | (ODD/EVEN, GBA, GAB, SEL, LEA, LEB)                                      |

| I <sub>BVIT</sub> | Input HIGH Curren  | t                   |      |      |      |          |                                             | V <sub>IN</sub> = 5.5V                                                   |

| DVIII             | Breakdown (I/O)    |                     |      |      | 0.5  | mA       | Max                                         | (A <sub>n</sub> , B <sub>n</sub> , A <sub>PAB</sub> , B <sub>PAB</sub> ) |

| I <sub>CEX</sub>  | Output HIGH        |                     |      |      |      | _        |                                             |                                                                          |

| OLX               | Leakage Current    |                     |      |      | 50   | μA       | Max                                         | $V_{OUT} = V_{CC}$                                                       |

| V <sub>ID</sub>   | Input Leakage      |                     |      |      |      |          |                                             | I <sub>ID</sub> = 1.9 μA                                                 |

| .5                | Test               |                     | 4.75 |      |      | V        | 0.0                                         | All Other Pins Grounded                                                  |

| I <sub>OD</sub>   | Output Leakage     |                     |      |      |      | _        |                                             | V <sub>IOD</sub> = 150 mV                                                |

| 05                | Circuit Current    |                     |      |      | 3.75 | μA       | 0.0                                         | All Other Pins Grounded                                                  |

| I <sub>IL</sub>   | Input Low Current  |                     |      |      | -0.6 | mA       | Max                                         | V <sub>IN</sub> = 0.5V                                                   |

| I <sub>IH+</sub>  | Output Leakage Cu  | urrent              |      |      | _    | <b>†</b> | V <sub>I/O</sub> = 2.7V                     |                                                                          |

| I <sub>OZH</sub>  | Current            |                     |      |      | 70   | μΑ       | Max                                         | (A <sub>n</sub> , B <sub>n</sub> , APAR, BPAR)                           |

# DC Electrical Characteristics (Continued)

| Symbol           | Parameter                    | Min  | Тур | Max  | Units | v <sub>cc</sub> | Conditions                                     |

|------------------|------------------------------|------|-----|------|-------|-----------------|------------------------------------------------|

| I <sub>IL+</sub> | Output Leakage               |      |     | -650 | μА    | Max             | $V_{I/O} = 0.5V$                               |

| I <sub>OZL</sub> | Current                      |      |     | -050 | μА    | IVIAX           | (A <sub>n</sub> , B <sub>n</sub> , APAR, BPAR) |

| Ios              | Output Short-Circuit Current | -60  |     | -150 |       | Max             | V <sub>OUT</sub> = 0V                          |

|                  |                              |      |     |      | mA    |                 | (A <sub>n</sub> , APAR, ERRA, ERRB)            |

|                  |                              | -100 |     | -225 |       | Max             | $V_{OUT} = 0V (B_n, BPAR)$                     |

| I <sub>ZZ</sub>  | Bus Drainage Test            |      |     | 500  | μΑ    | 0.0V            | V <sub>OUT</sub> = 5.25V                       |

| I <sub>CCH</sub> | Power Supply Current         |      | 132 | 155  | mA    | Max             | V <sub>O</sub> = HIGH                          |

| I <sub>CCL</sub> | Power Supply Current         |      | 178 | 210  | mA    | Max             | V <sub>O</sub> = LOW, GAB = LOW,               |

|                  |                              |      |     |      |       |                 | GBA = HIGH, V <sub>IL</sub> = LOW              |

| I <sub>CCZ</sub> | Power Supply Current         |      | 160 | 190  | mA    | Max             | V <sub>O</sub> = HIGH Z                        |

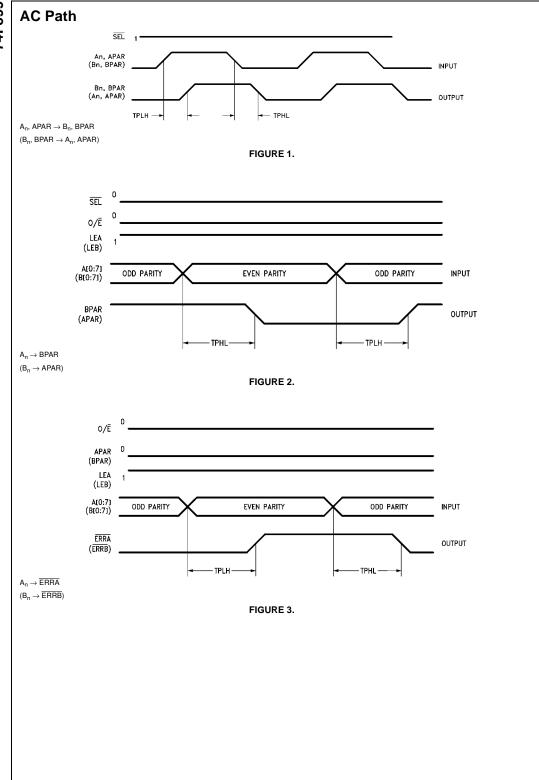

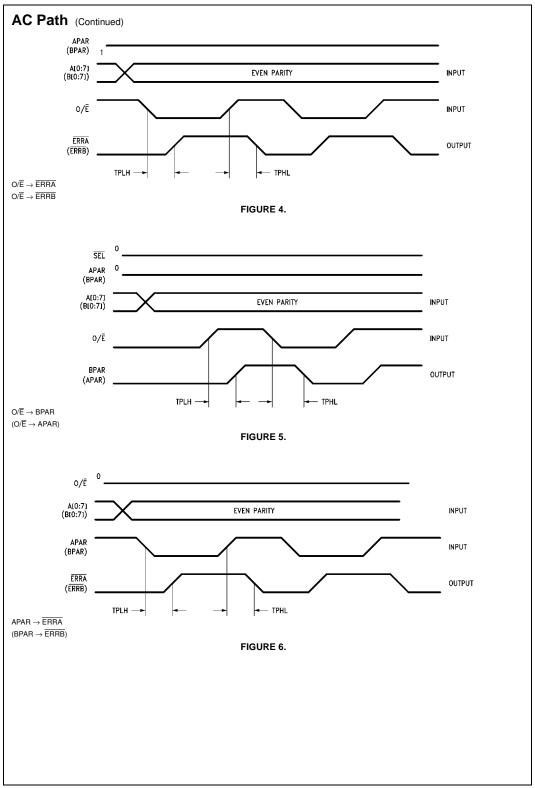

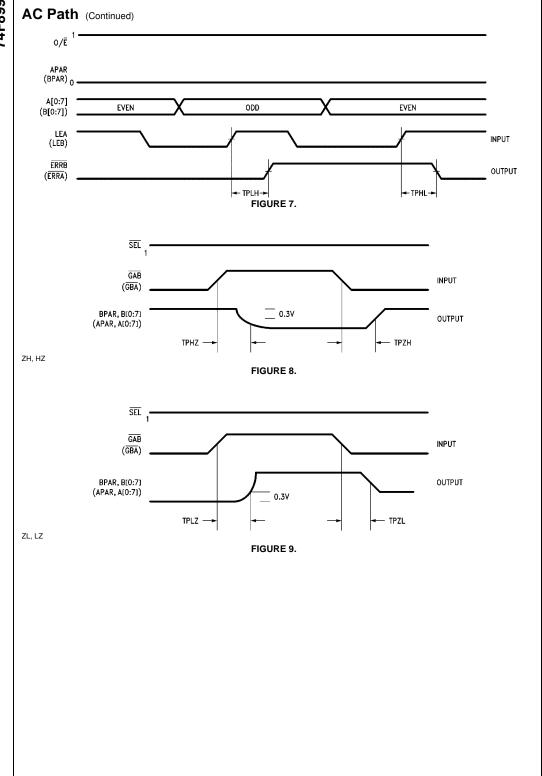

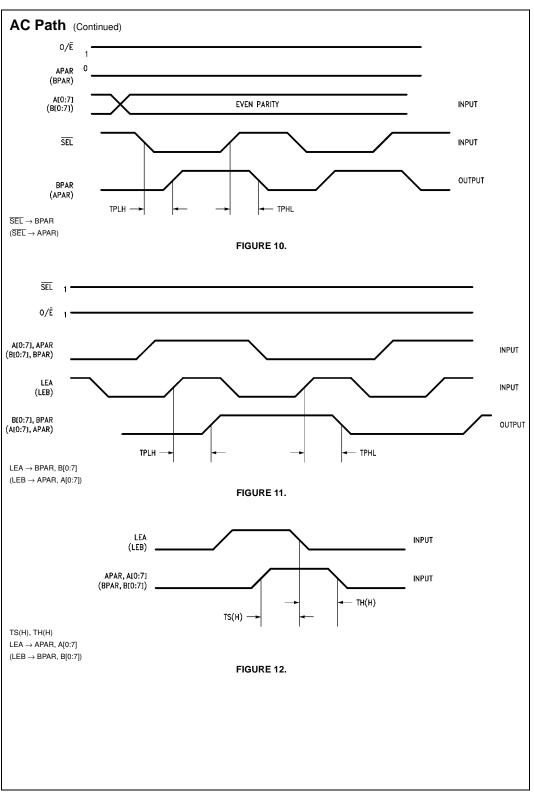

## **AC Electrical Characteristics**

| ,                  |                                                |     | T <sub>A</sub> = +25°C | ;    | T <sub>A</sub> = 0°C   | to +70°C | Unite | Figure                  |

|--------------------|------------------------------------------------|-----|------------------------|------|------------------------|----------|-------|-------------------------|

| Symbol             | Parameter                                      |     | $V_{CC} = +5.0$        | /    | V <sub>CC</sub> =      | +5.0V    |       |                         |

|                    | Parameter                                      |     | $C_L = 50 \text{ pF}$  |      | C <sub>L</sub> = 50 pF |          | Units | Number                  |

|                    |                                                | Min | Тур                    | Max  | Min                    | Max      | †     |                         |

| t <sub>PLH</sub>   | Propagation Delay                              | 4.0 | 7.5                    | 13.0 | 4.0                    | 14.0     | ns    | Figure 1                |

| $t_{PHL}$          | A <sub>n</sub> , APAR to B <sub>n</sub> , BPAR | 4.0 | 8.5                    | 13.0 | 4.0                    | 14.0     | 115   | Figure 1                |

| t <sub>PLH</sub>   | Propagation Delay                              | 7.5 | 12.0                   | 17.0 | 7.5                    | 18.0     | ns    | Figure 2                |

| t <sub>PHL</sub>   | A <sub>n</sub> , B <sub>n</sub> to BPAR, APAR  | 7.5 | 12.5                   | 17.0 | 7.5                    | 18.0     | 113   | r igure z               |

| t <sub>PLH</sub>   | Propagation Delay                              | 7.5 | 12.0                   | 17.0 | 7.5                    | 18.0     | ns    | Figure 3                |

| t <sub>PHL</sub>   | A <sub>n</sub> , B <sub>n</sub> to ERRA, ERRB  | 7.5 | 12.5                   | 17.0 | 7.5                    | 18.0     | 115   | rigule 3                |

| t <sub>PLH</sub>   | Propagation Delay                              | 4.5 | 7.5                    | 11.0 | 4.5                    | 12.0     |       | Figure 4                |

| t <sub>PHL</sub>   | ODD/EVEN to ERRA, ERRB                         | 4.5 | 8.0                    | 11.0 | 4.5                    | 12.0     | ns    | Figure 4                |

| t <sub>PLH</sub>   | Propagation Delay                              | 4.5 | 7.5                    | 11.5 | 4.5                    | 12.5     |       | Figure 5                |

| t <sub>PHL</sub>   | ODD/EVEN to APAR, BPAR                         | 4.5 | 8.5                    | 11.5 | 4.5                    | 12.5     | ns    |                         |

| t <sub>PLH</sub>   | Propagation Delay                              | 5.5 | 9.0                    | 13.0 | 5.5                    | 14.0     |       | <u> </u>                |

| t <sub>PHL</sub>   | APAR, BPAR to ERRA, ERRB                       | 5.5 | 9.5                    | 13.0 | 5.5                    | 14.0     | ns    | Figure 6                |

| t <sub>PLH</sub>   | LEA/LEB to                                     | 9.5 | 13.0                   | 17.5 | 7.5                    | 18.0     |       | Figure 7                |

| t <sub>PHL</sub>   | ERRA /ERRB                                     | 9.7 |                        | 17.5 | 7.5                    | 18.0     | ns    |                         |

| t <sub>PLH</sub>   | Propagation Delay                              | 3.0 | 6.0                    | 10.0 | 3.0                    | 11.0     |       | Figure 10               |

| t <sub>PHL</sub>   | SEL to APAR, BPAR                              | 3.0 | 7.0                    | 10.0 | 3.0                    | 11.0     | ns    |                         |

| t <sub>PLH</sub>   | Propagation Delay                              | 3.5 | 7.0                    | 10.0 | 3.5                    | 11.0     |       | F: 44                   |

| t <sub>PHL</sub>   | LEB to A <sub>n</sub> , APAR                   | 3.5 | 8.0                    | 10.0 | 3.5                    | 11.0     | ns    | Figure 11               |

| t <sub>PLH</sub>   | Propagation Delay                              | 3.5 | 6.5                    | 10.0 | 3.5                    | 11.0     |       | Cierre 11               |

| t <sub>PHL</sub>   | LEA to B <sub>n</sub> , BPAR                   | 3.5 | 7.5                    | 10.0 | 3.5                    | 11.0     | ns    | Figure 11               |

| t <sub>PZH</sub>   | Output Enable Time                             | 1.0 | 4.5                    | 10.0 | 1.0                    | 11.0     |       |                         |

| $t_{PZL}$          | GBA or GAB to A <sub>n</sub> ,                 | 1.0 | 6.5                    | 10.0 | 1.0                    | 11.0     | ns    | Figure 8,<br>Figure 9   |

|                    | APAR or B <sub>n</sub> , BPAR                  |     |                        |      |                        |          |       | 1 iguic o               |

| t <sub>PHZ</sub>   | Output Disable Time                            | 1.0 | 4.0                    | 7.0  | 1.0                    | 8.0      |       |                         |

| $t_{PLZ}$          | GBA or GAB to A <sub>n</sub> ,                 | 1.0 | 4.0                    | 7.0  | 1.0                    | 8.0      | ns    | Figure 8,<br>Figure 9   |

|                    | APAR or B <sub>n</sub> , BPAR                  |     |                        |      |                        |          |       |                         |

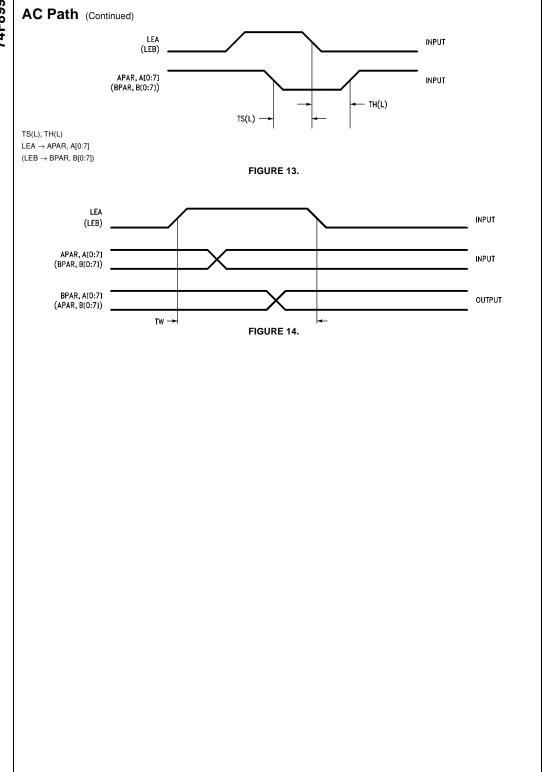

| t <sub>S</sub> (H) | Setup Time, HIGH or LOW                        | 5.0 | 1.6                    |      | 5.0                    |          |       | Figure 12,<br>Figure 13 |

| t <sub>S</sub> (L) | A <sub>n</sub> , B <sub>n</sub> to LEA, LEB    | 5.0 | 1.8                    |      | 5.0                    |          | ns    |                         |

| t <sub>H</sub> (H) | Hold Time, HIGH or LOW                         | 0   | -1.7                   |      | 0                      |          | no    | Figure 12,<br>Figure 13 |

| t <sub>H</sub> (L) | A <sub>n</sub> , B <sub>n</sub> to LEA, LEB    | 0   | -1.5                   |      | 0                      |          | ns    |                         |

| t <sub>W</sub>     | Pulse Width for LEA, LEB                       | 6.0 | 2.0                    |      | 6.0                    |          | ns    | Figure 14               |

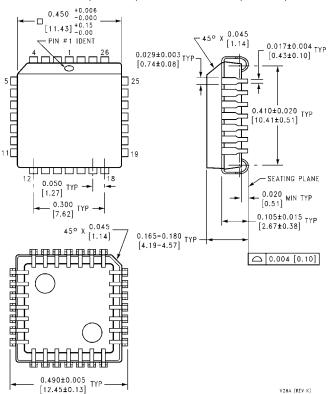

#### Physical Dimensions inches (millimeters) unless otherwise noted (Continued)

28-Lead Plastic Lead Chip Carrier (PLCC), JEDEC MO-047, 0.450 Square Package Number V28A

Fairchild does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and Fairchild reserves the right at any time without notice to change said circuitry and specifications.

#### LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component in any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

www.fairchildsemi.com