# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# FAST CMOS OCTAL D FLIP-FLOP WITH CLOCK ENABLE

IDT74FCT377AT/CT/DT

#### FEATURES:

- A, C, and D grades

- Low input and output leakage ≤1µA (max.)

- CMOS power levels

- True TTL input and output compatibility:

- VOH = 3.3V (typ.)

- VOL = 0.3V (typ.)

- High Drive outputs (-15mA IOH, 48mA IOL)

- Meets or exceeds JEDEC standard 18 specifications

- Power off disable outputs permit "live insertion"

- Available in SOIC and QSOP packages

#### **DESCRIPTION:**

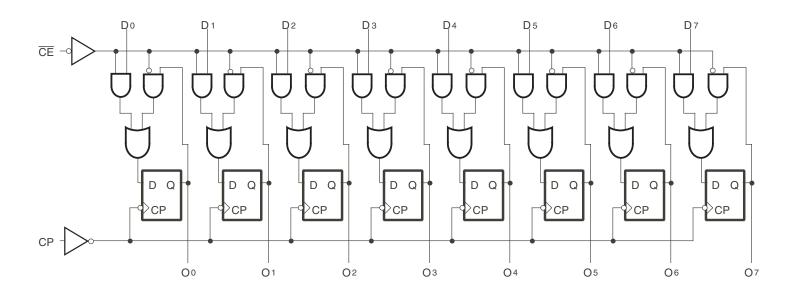

The IDT74FCT377T is an octal D flip-flop built using an advanced dual metal CMOS technology. The IDT74FCT377T has eight edge-triggered, D-type flip-flops with individual D inputs and O outputs. The common buffered Clock (CP) input loads all flip-flops simultaneously when the Clock Enable ( $\overline{CE}$ ) is low. The register is fully edge-triggered. The state of each D input, one set-up time before the low-to-high clock transition, is transferred to the corresponding flip-flop's O output. The  $\overline{CE}$  input must be stable only one set-up time prior to the low-to-high transition for predictable operation.

# FUNCTIONAL BLOCK DIAGRAM

The IDT logo is a registered trademark of Integrated Device Technology, Inc.

#### OCTOBER 2009

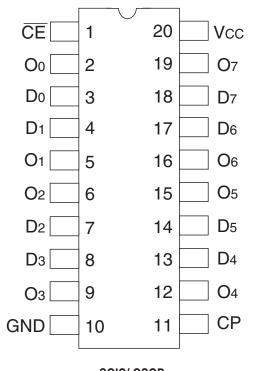

#### **PIN CONFIGURATION**

SOIC/ QSOP **TOP VIEW**

#### **INDUSTRIAL TEMPERATURE RANGE**

### **ABSOLUTE MAXIMUM RATINGS**<sup>(1)</sup>

| Symbol               | Description                          | Max             | Unit |

|----------------------|--------------------------------------|-----------------|------|

| VTERM <sup>(2)</sup> | Terminal Voltage with Respect to GND | –0.5 to +7      | V    |

| VTERM <sup>(3)</sup> | Terminal Voltage with Respect to GND | -0.5 to Vcc+0.5 | V    |

| TSTG                 | Storage Temperature                  | -65 to +150     | °C   |

| Ιουτ                 | DC Output Current                    | -60 to +120     | mA   |

NOTES:

1. Stresses greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability. No terminal voltage may exceed Vcc by +0.5V unless otherwise noted.

2. Inputs and Vcc terminals only.

3. Output and I/O terminals only.

#### CAPACITANCE (TA = +25°C, F = 1.0MHz)

| Symbol | Parameter <sup>(1)</sup> | Conditions | Тур. | Max. | Unit |

|--------|--------------------------|------------|------|------|------|

| CIN    | Input Capacitance        | VIN = 0V   | 6    | 10   | рF   |

| Соит   | Output Capacitance       | Vout = 0V  | 8    | 12   | pF   |

NOTE:

1. This parameter is measured at characterization but not tested.

#### PIN DESCRIPTION

| Pin Names | Description               |  |

|-----------|---------------------------|--|

| D0 – D7   | Data Inputs               |  |

| CE        | Clock Enable (Active LOW) |  |

| O0 – O7   | DataOutputs               |  |

| СР        | Clock Pulse Input         |  |

#### **FUNCTION TABLE(1)**

|                |            | Inputs | Outputs |           |

|----------------|------------|--------|---------|-----------|

| Operating Mode | СР         | Ē      | D       | 0         |

| Load "1"       | $\uparrow$ | I      | h       | Н         |

| Load "0"       | $\uparrow$ | I      | I       | L         |

| Hold           | $\uparrow$ | h      | Х       | No Change |

|                | Н          | Н      | Х       | No Change |

#### NOTE:

1. H = HIGH Voltage Level

h = HIGH Voltage Level one setup time prior to the LOW-to-HIGH Clock Transition

L = LOW Voltage Level I = LOW Voltage Level one setup time prior to the LOW-to-HIGH Clock Transition

X = Don't Care  $\uparrow = LOW-to-HIGH Clock Transition$

# DC ELECTRICAL CHARACTERISTICS OVER OPERATING RANGE

Following Conditions Apply Unless Otherwise Specified:

Industrial : TA =  $-40^{\circ}$ C to  $+85^{\circ}$ C, VCC =  $5.0V \pm 5\%$

| Symbol | Parameter                         | Test Con                             | Test Conditions <sup>(1)</sup>       |     | Typ. <sup>(2)</sup> | Max. | Unit |

|--------|-----------------------------------|--------------------------------------|--------------------------------------|-----|---------------------|------|------|

| Vih    | Input HIGH Level                  | Guaranteed Logic HIGH Level          | Guaranteed Logic HIGH Level          |     | —                   | —    | V    |

| VIL    | Input LOW Level                   | Guaranteed Logic LOW Level           |                                      | —   | _                   | 0.8  | V    |

| Ін     | Input HIGH Current <sup>(4)</sup> | Vcc = Max.                           | VI = 2.7V                            | —   | _                   | ±1   | μA   |

| lil    | Input LOW Current <sup>(4)</sup>  | Vcc = Max.                           | VI = 0.5V                            | _   | _                   | ±1   | μA   |

| li     | Input HIGH Current <sup>(4)</sup> | Vcc = Max., VI = Vcc (Max.)          | •                                    | _   | _                   | ±1   | μA   |

| Vik    | Clamp Diode Voltage               | Vcc = Min., IN = -18mA               | Vcc = Min., IN = -18mA               |     | -0.7                | -1.2 | V    |

| los    | Short Circuit Current             | Vcc = Max. <sup>(3)</sup> , Vo = GND | Vcc = Max. <sup>(3)</sup> , Vo = GND |     | -120                | -225 | mA   |

| Vон    | Output HIGH Voltage               | Vcc = Min.                           | IOH = -8mA                           | 2.4 | 3.3                 | _    | V    |

|        |                                   | VIN = VIH or VIL                     | Iон = –12mA                          | 2   | 3                   | —    |      |

| Vol    | Output LOW Voltage                | Vcc = Min.                           | IOL = 48mA                           | —   | 0.3                 | 0.5  | V    |

|        |                                   | VIN = VIH or VIL                     |                                      |     |                     |      |      |

| IOFF   | Input/Output Power Off            | Vcc = 0V, VIN or Vo - 4.5V           | •                                    | _   | _                   | ±1   | μA   |

|        | Leakage <sup>(5)</sup>            |                                      |                                      |     |                     |      |      |

| Vн     | Input Hysteresis                  | -                                    | _                                    |     | 200                 | —    | mV   |

| Icc    | Quiescent Power                   | Vcc = Max.                           | Vcc = Max.                           |     | 0.01                | 1    | mA   |

|        | Supply Current                    | VIN = GND or VCC                     | VIN = GND or Vcc                     |     |                     |      |      |

NOTES:

1. For conditions shown as Max. or Min., use appropriate value specified under Electrical Characteristics for the applicable device type.

2. Typical values are at Vcc = 5.0V,  $+25^{\circ}C$  ambient.

3. Not more than one output should be shorted at one time. Duration of the short circuit test should not exceed one second.

4. The test limit for this parameter is  $\pm 5\mu A$  at TA =  $-55^{\circ}C$ .

5. This parameter is guaranted but not tested.

### **POWER SUPPLY CHARACTERISTICS**

| Symbol | Parameter                                         | Test Conditions <sup>(1)</sup>                                                            |                         | Min. | Typ. <sup>(2)</sup> | Max.                | Unit       |

|--------|---------------------------------------------------|-------------------------------------------------------------------------------------------|-------------------------|------|---------------------|---------------------|------------|

| Δlcc   | Quiescent Power Supply<br>Current TTL Inputs HIGH | Vcc = Max.<br>VIN = 3.4V <sup>(3)</sup>                                                   |                         | -    | 0.5                 | 2                   | mA         |

| ICCD   | Dynamic Power Supply<br>Current <sup>(4)</sup>    | Vcc = Max., Outputs Open<br>$\overline{CE}$ = GND<br>One Input Toggling<br>50% Duty Cycle | VIN = VCC<br>VIN = GND  | —    | 0.15                | 0.25                | mA/<br>MHz |

| lc     | Total Power Supply<br>Current <sup>(6)</sup>      | Vcc = Max., Outputs Open<br>fcP = 10MHz                                                   | VIN = VCC<br>VIN = GND  | —    | 1.5                 | 3.5                 | mA         |

|        |                                                   | $\overline{CE}$ = GNDOne Bit Togglingfi = 5MHz50% Duty Cycle                              | VIN = 3.4V<br>VIN = GND | —    | 2                   | 5.5                 |            |

|        |                                                   | Vcc = Max., Outputs Open<br>fcP = 10MHz, 50% Duty Cycle                                   | VIN = VCC<br>VIN = GND  | —    | 3.8                 | 7.3 <sup>(5)</sup>  |            |

|        |                                                   | $\overline{CE} = GND$ Eight Bits Toggling<br>fi = 2.5MHz<br>50% Duty Cycle                | VIN = 3.4V<br>VIN = GND | _    | 6                   | 16.3 <sup>(5)</sup> |            |

NOTES:

1. For conditions shown as Min. or Max., use appropriate value specified under Electrical Characteristics for the applicable device type.

2. Typical values are at Vcc = 5.0V, +25°C ambient.

3. Per TTL driven input; (VIN = 3.4V). All other inputs at Vcc or GND.

4. This parameter is not directly testable, but is derived for use in Total Power Supply Calculations.

5. Values for these conditions are examples of  $\Delta$ Icc formula. These limits are guaranteed but not tested.

6. IC = IQUIESCENT + INPUTS + IDYNAMIC

IC = ICC +  $\Delta$ ICC DHNT + ICCD (fCP/2+ fiNi)

Icc = Quiescent Current

$\Delta Icc$  = Power Supply Current for a TTL High Input (VIN = 3.4V)

DH = Duty Cycle for TTL Inputs High

NT = Number of TTL Inputs at DH

ICCD = Dynamic Current caused by an Input Transition Pair (HLH or LHL)

fcP = Clock Frequency for Register Devices (Zero for Non-Register Devices)

fi = Output Frequency

Ni = Number of Outputs at fi

All currents are in milliamps and all frequencies are in megahertz.

# SWITCHING CHARACTERISTICS OVER OPERATING RANGE

|              |                            |                          | 74FCT377AT          |      | 74FCT               | 377CT | 74FCT               | 377DT |          |

|--------------|----------------------------|--------------------------|---------------------|------|---------------------|-------|---------------------|-------|----------|

| Symbol       | Parameter                  | Condition <sup>(1)</sup> | Min. <sup>(2)</sup> | Max. | Min. <sup>(2)</sup> | Max.  | Min. <sup>(2)</sup> | Max.  | Unit     |

| tPLH         | Propagation Delay          | CL = 50pF                | 2                   | 7.2  | 2                   | 5.2   | 2                   | 4.4   | ns       |

| <b>t</b> PHL | CP to Qx                   | $RL = 500\Omega$         |                     |      |                     |       |                     |       |          |

| ts∪          | Set-up Time HIGH or LOW    |                          | 2                   | -    | 2                   | —     | 2                   | —     | ns       |

|              | Dx to CP                   |                          |                     |      |                     |       |                     |       |          |

| tΗ           | Hold Time HIGH or LOW      |                          | 1.5                 | —    | 1.5                 | —     | 1                   | —     | ns       |

|              | Dx to CP                   |                          |                     |      |                     |       |                     |       |          |

| ts∪          | Set-up Time HIGH or LOW    |                          | 3.5                 | —    | 3.5                 | —     | 3                   | —     | ns       |

|              | CE to CP                   |                          |                     |      |                     |       |                     |       |          |

| tΗ           | Hold Time HIGH or LOW      |                          | 1.5                 | _    | 1.5                 | —     | 0                   | _     | ns       |

|              | CE to CP                   |                          |                     |      |                     |       |                     |       |          |

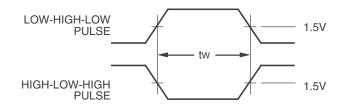

| tw           | CP Pulse Width HIGH or LOW |                          | 8                   | _    | 6                   | _     | 3                   | _     | ns       |

|              | I                          |                          |                     | I    | ļ                   |       | I                   |       | <u> </u> |

NOTES:

1. See test circuit and waveforms.

2. Minimum limits are guaranteed but not tested on Propagation Delays.

#### IDT74FCT377AT/CT/DT FAST CMOS OCTAL D FLIP-FLOP WITH CLOCK ENABLE

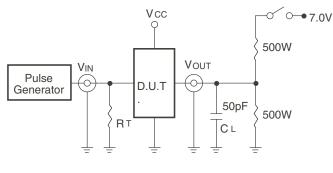

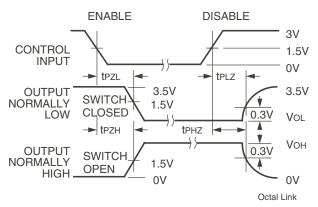

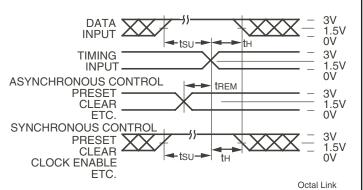

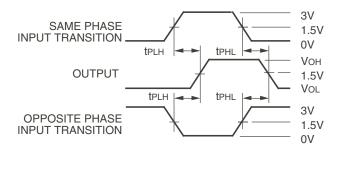

### **TEST CIRCUITS AND WAVEFORMS**

Octal Link

| Test                                    | Switch |

|-----------------------------------------|--------|

| Open Drain<br>Disable Low<br>Enable Low | Closed |

| All Other Tests                         | Open   |

**DEFINITIONS:**

CL = Load capacitance: includes jig and probe capacitance.

RT = Termination resistance: should be equal to ZOUT of the Pulse Generator.

Pulse Width

Octal Link

#### Enable and Disable Times

#### NOTES:

- 1. Diagram shown for input Control Enable-LOW and input Control Disable-HIGH.

- 2. Pulse Generator for All Pulses: Rate  $\leq$  1.0MHz; tF  $\leq$  2.5ns; tR  $\leq$  2.5ns.

Set-Up, Hold, and Release Times

Propagation Delay

Octal Link

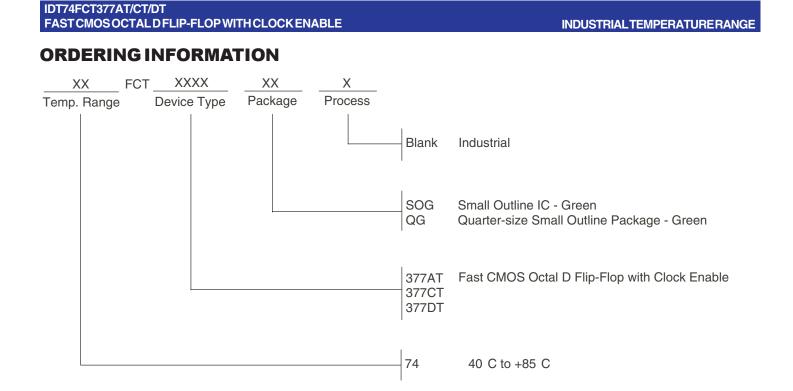

# **Datasheet Document History**

10/03/09 Pg. 6 Updated the ordering information by removing the "IDT" notation and non RoHS part.

**CORPORATE HEADQUARTERS** 6024 Silver Creek Valley Road San Jose, CA 95138 for SALES: 800-345-7015 or 408-284-8200 fax: 408-284-2775 www.idt.com for Tech Support: logichelp@idt.com