# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

#### DATASHEET

#### Description

The 74FCT3807S is a low skew, single input to ten output, clock buffer. The 74FCT3807S has best in class additive phase Jitter of sub 50 fsec.

IDT makes many non-PLL and PLL based low skew output devices as well as Zero Delay Buffers to synchronize clocks. Contact us for all of your clocking needs.

#### **Features**

- · Low additive phase jitter RMS: 50fs

- · Low skew outputs (50ps)

- Packaged in 20-pin TSSOP, SSOP, QSOP and VFQFPN packages, Pb (lead) free

- Operating voltages of 1.8V to 3.3V

- · Input/Output clock frequency up to 200 MHz

- Advanced, low power CMOS process

- Extended temperature range (-40°C to +105°C)

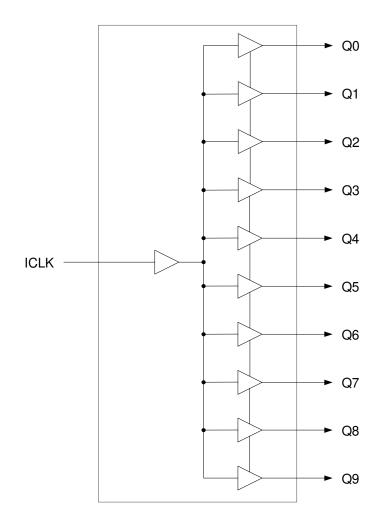

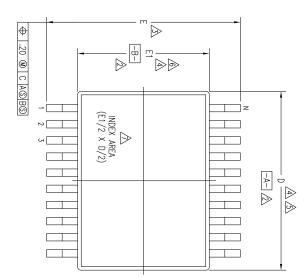

#### **Block Diagram**

#### **Pin Assignments**

#### **Pin Descriptions**

| Pin<br>Number | Pin<br>Name | Pin<br>Type | Pin Description                      |

|---------------|-------------|-------------|--------------------------------------|

| 1             | ICLK        | Input       | Clock input.                         |

| 2             | GND         | Power       | Connect to ground.                   |

| 3             | Q0          | Output      | Clock output 0.                      |

| 4             | VDD         | Power       | Connect to +1.8V, +2.5 V, or +3.3 V. |

| 5             | Q1          | Output      | Clock output 1.                      |

| 6             | GND         | Power       | Connect to ground.                   |

| 7             | Q2          | Output      | Clock Output 2.                      |

| 8             | VDD         | Power       | Connect to +1.8V, +2.5 V, or +3.3 V. |

| 9             | Q3          | Output      | Clock Output 3.                      |

| 10            | GND         | Power       | Connect to ground.                   |

| 11            | Q4          | Output      | Clock Output 4.                      |

| 12            | Q5          | Output      | Clock Output 5.                      |

| 13            | GND         | Power       | Connect to ground.                   |

| 14            | Q6          | Output      | Clock Output 6.                      |

| 15            | VDD         | Power       | Connect to +1.8V, +2.5 V, or +3.3 V. |

| 16            | Q7          | Output      | Clock Output 7.                      |

| 17            | GND         | Power       | Connect to ground.                   |

| 18            | Q8          | Output      | Clock Output 8.                      |

| 19            | Q9          | Output      | Clock Output 9.                      |

| 20            | VDD         | Power       | Connect to +1.8V, +2.5 V, or +3.3 V. |

#### **External Components**

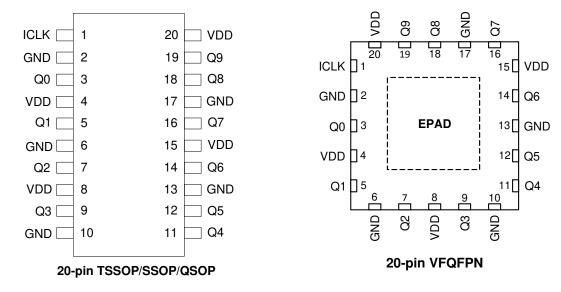

A minimum number of external components are required for proper operation. A decoupling capacitor of  $0.01\mu$ F should be connected between VDD pins and GND pins, as close to the device as possible. A  $33\Omega$  series terminating resistor may be used on each clock output if the trace is longer than 1 inch.

To achieve the low output skew that the 74FCT3807S is capable of, careful attention must be paid to board layout. Essentially, all ten outputs must have identical terminations, identical loads and identical trace geometries. If they do not, the output skew will be degraded. For example, using a  $30\Omega$  series termination on one output (with  $33\Omega$  on the others) will cause at least 15 ps of skew.

#### **Absolute Maximum Ratings**

Stresses above the ratings listed below can cause permanent damage to the 74FCT3807S. These ratings, which are standard values for IDT commercially rated parts, are stress ratings only. Functional operation of the device at these or any other conditions above those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods can affect product reliability. Electrical parameters are guaranteed only over the recommended operating temperature range.

| Item                                     | Rating              |

|------------------------------------------|---------------------|

| Supply Voltage, VDD                      | 3.465V              |

| Outputs                                  | -0.5 V to VDD+0.5 V |

| ICLK                                     | 3.465V              |

| Ambient Operating Temperature (extended) | -40° to +105°C      |

| Storage Temperature                      | -65° to +150°C      |

| Junction Temperature                     | 125°C               |

| Soldering Temperature                    | 260°C               |

#### **Recommended Operation Conditions**

| Parameter                                         | Min.  | Тур. | Max.   | Units |

|---------------------------------------------------|-------|------|--------|-------|

| Ambient Operating Temperature (extended)          | -40   |      | +105   | °C    |

| Power Supply Voltage (measured in respect to GND) | +1.71 |      | +3.465 | V     |

#### **DC Electrical Characteristics**

(VDD = 1.8V, 2.5V, 3.3V)

| Parameter                | Symbol          | Conditions               | Min.    | Тур. | Max.    | Units |

|--------------------------|-----------------|--------------------------|---------|------|---------|-------|

| Operating Voltage        | VDD             |                          | 1.71    |      | 1.89    | V     |

| Input High Voltage, ICLK | V <sub>IH</sub> | Note 1                   | 0.7xVDD |      | VDD     | V     |

| Input Low Voltage, ICLK  | V <sub>IL</sub> | Note 1                   |         |      | 0.3xVDD | V     |

| Output High Voltage      | V <sub>OH</sub> | I <sub>OH</sub> = -10 mA | 1.3     |      |         | V     |

| Output Low Voltage       | V <sub>OL</sub> | I <sub>OL</sub> = 10 mA  |         |      | 0.35    | V     |

| Operating Supply Current | IDD             | No load, 135 MHz         |         | 35   |         | mA    |

| Nominal Output Impedance | Z <sub>O</sub>  |                          |         | 17   |         | Ω     |

| Input Capacitance        | C <sub>IN</sub> | ICLK                     |         | 5    |         | pF    |

VDD=1.8V ±5%, Ambient temperature -40° to +105°C, unless stated otherwise

Notes: 1. Nominal switching threshold is VDD/2

#### VDD=2.5 V ±5%, Ambient temperature -40° to +105°C, unless stated otherwise

| Parameter                | Symbol          | Conditions               | Min.    | Тур. | Max.    | Units |

|--------------------------|-----------------|--------------------------|---------|------|---------|-------|

| Operating Voltage        | VDD             |                          | 2.375   |      | 2.625   | V     |

| Input High Voltage, ICLK | V <sub>IH</sub> | Note 1                   | 0.7xVDD |      | VDD     | V     |

| Input Low Voltage, ICLK  | VIL             | Note 1                   |         |      | 0.3xVDD | V     |

| Output High Voltage      | V <sub>OH</sub> | I <sub>OH</sub> = -16 mA | 1.8     |      |         | V     |

| Output Low Voltage       | V <sub>OL</sub> | I <sub>OL</sub> = 16 mA  |         |      | 0.5     | V     |

| Operating Supply Current | IDD             | No load, 135 MHz         |         | 45   |         | mA    |

| Nominal Output Impedance | Z <sub>O</sub>  |                          |         | 17   |         | Ω     |

| Input Capacitance        | C <sub>IN</sub> | ICLK                     |         | 5    |         | pF    |

#### VDD=3.3 V $\pm$ 5% , Ambient temperature -40° to +105°C, unless stated otherwise

| Parameter                | Symbol          | Conditions               | Min.    | Тур. | Max.    | Units |

|--------------------------|-----------------|--------------------------|---------|------|---------|-------|

| Operating Voltage        | VDD             |                          | 3.15    |      | 3.45    | V     |

| Input High Voltage, ICLK | V <sub>IH</sub> | Note 1                   | 0.7xVDD |      | VDD     | V     |

| Input Low Voltage, ICLK  | V <sub>IL</sub> | Note 1                   |         |      | 0.3xVDD | V     |

| Output High Voltage      | V <sub>OH</sub> | I <sub>OH</sub> = -25 mA | 2.2     |      |         | V     |

| Output Low Voltage       | V <sub>OL</sub> | I <sub>OL</sub> = 25 mA  |         |      | 0.7     | V     |

| Operating Supply Current | IDD             | No load, 135 MHz         |         | 55   |         | mA    |

| Nominal Output Impedance | Z <sub>O</sub>  |                          |         | 17   |         | Ω     |

| Input Capacitance        | C <sub>IN</sub> | ICLK                     |         | 5    |         | pF    |

#### **AC Electrical Characteristics**

(VDD = 1.8V, 2.5V, 3.3V)

| Parameter                         | Symbol                | Conditions                                             | Min. | Тур. | Max. | Units |

|-----------------------------------|-----------------------|--------------------------------------------------------|------|------|------|-------|

| Input Frequency                   |                       |                                                        | 0    |      | 200  | MHz   |

| Output Rise Time                  | t <sub>OR</sub>       | 0.36 to 1.44 V, C <sub>L</sub> =5 pF                   |      | 1.4  | 1.9  | ns    |

| Output Fall Time                  | t <sub>OF</sub>       | 1.44 to 0.36 V, C <sub>L</sub> =5 pF                   |      | 1.4  | 1.9  | ns    |

| Propagation Delay                 |                       | Note 1                                                 | 1.5  | 2.5  | 4    | ns    |

| Buffer Additive Phase Jitter, RMS |                       | 125MHz, Integration Range: 12kHz-20MHz                 |      |      | 0.05 | ps    |

| Output to Output Skew             |                       | Rising edges at VDD/2, Note 2                          |      | 50   | 65   | ps    |

| Device to Device Skew             |                       | Rising edges at VDD/2                                  |      |      | 200  | ps    |

| Start-up Time                     | t <sub>START-UP</sub> | Part start-up time for valid outputs after VDD ramp-up |      |      | 2    | ms    |

| VDD = 2.5 V ±5%, Ambient Temperature -40° to - | +105°C, unless stated otherwise |

|------------------------------------------------|---------------------------------|

|------------------------------------------------|---------------------------------|

| Parameter                         | Symbol                | Conditions                                             | Min. | Тур. | Max. | Units |

|-----------------------------------|-----------------------|--------------------------------------------------------|------|------|------|-------|

| Input Frequency                   |                       |                                                        | 0    |      | 200  | MHz   |

| Output Rise Time                  | t <sub>OR</sub>       | 0.5 to 2.0 V, C <sub>L</sub> =5 pF                     |      | 1.0  | 1.5  | ns    |

| Output Fall Time                  | t <sub>OF</sub>       | 2.0 to 0.5 V, C <sub>L</sub> =5 pF                     |      | 1.0  | 1.5  | ns    |

| Propagation Delay                 |                       | Note 1                                                 | 1.8  | 2.5  | 4.5  | ns    |

| Buffer Additive Phase Jitter, RMS |                       | 125MHz, Integration Range: 12kHz-20MHz                 |      |      | 0.05 | ps    |

| Output to Output Skew             |                       | Rising edges at VDD/2, Note 2                          |      | 50   | 65   | ps    |

| Device to Device Skew             |                       | Rising edges at VDD/2                                  |      |      | 200  | ps    |

| Start-up Time                     | t <sub>START-UP</sub> | Part start-up time for valid outputs after VDD ramp-up |      |      | 2    | ms    |

#### VDD = 3.3 V ±5%, Ambient Temperature -40° to +105°C, unless stated otherwise

| Parameter                         | Symbol                | Conditions                                             | Min. | Тур. | Max. | Units |

|-----------------------------------|-----------------------|--------------------------------------------------------|------|------|------|-------|

| Input Frequency                   |                       |                                                        | 0    |      | 200  | MHz   |

| Output Rise Time                  | t <sub>OR</sub>       | 0.66 to 2.64 V, C <sub>L</sub> =5 pF                   |      | 0.6  | 1.0  | ns    |

| Output Fall Time                  | t <sub>OF</sub>       | 2.64 to 0.66 V, C <sub>L</sub> =5 pF                   |      | 0.6  | 1.0  | ns    |

| Propagation Delay                 |                       | Note 1                                                 | 1.5  | 2.5  | 4    | ns    |

| Buffer Additive Phase Jitter, RMS |                       | 125MHz, Integration Range: 12kHz-20MHz                 |      |      | 0.05 | ps    |

| Output to Output Skew             |                       | Rising edges at VDD/2, Note 2                          |      | 50   | 65   | ps    |

| Device to Device Skew             |                       | Rising edges at VDD/2                                  |      |      | 200  | ps    |

| Start-up Time                     | t <sub>START-UP</sub> | Part start-up time for valid outputs after VDD ramp-up |      |      | 2    | ms    |

Notes:

1. With rail to rail input clock

Between any 2 outputs with equal loading.

Duty cycle on outputs will match incoming clock duty cycle. Consult IDT for tight duty cycle clock generators.

#### **Test Load and Circuit**

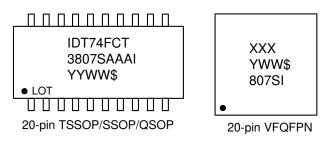

#### **Marking Diagrams**

Notes:

- 1. "LOT" denotes the lot number.

- 2. "XXX" denotes the lot number.

- 3. "YYWW" or "YWW" are the last digits of the year and week that the part was assembled.

- 4. "\$" denotes mark code.

- 5. "I" denotes extended temperature range device.

- 6. "AAA" denotes package code.

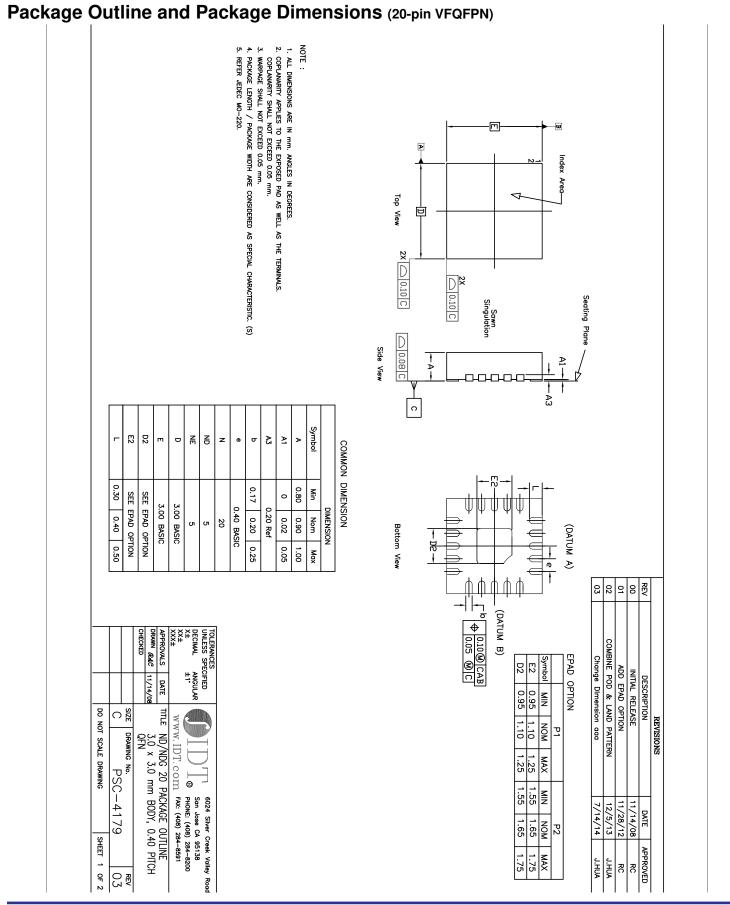

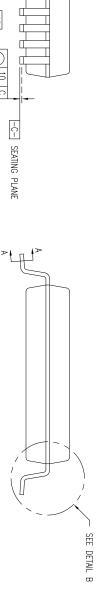

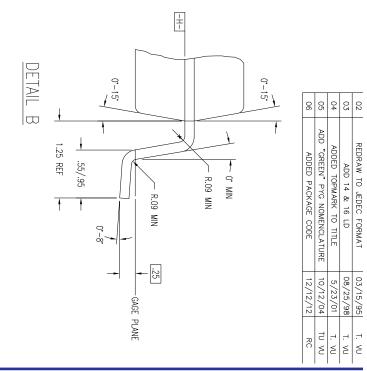

#### Package Outline and Package Dimensions, cont. (20-pin VFQFPN)

SHEET 2 OF 2

O C REV

Road

APPROVED

J.HUA I.HUA 88

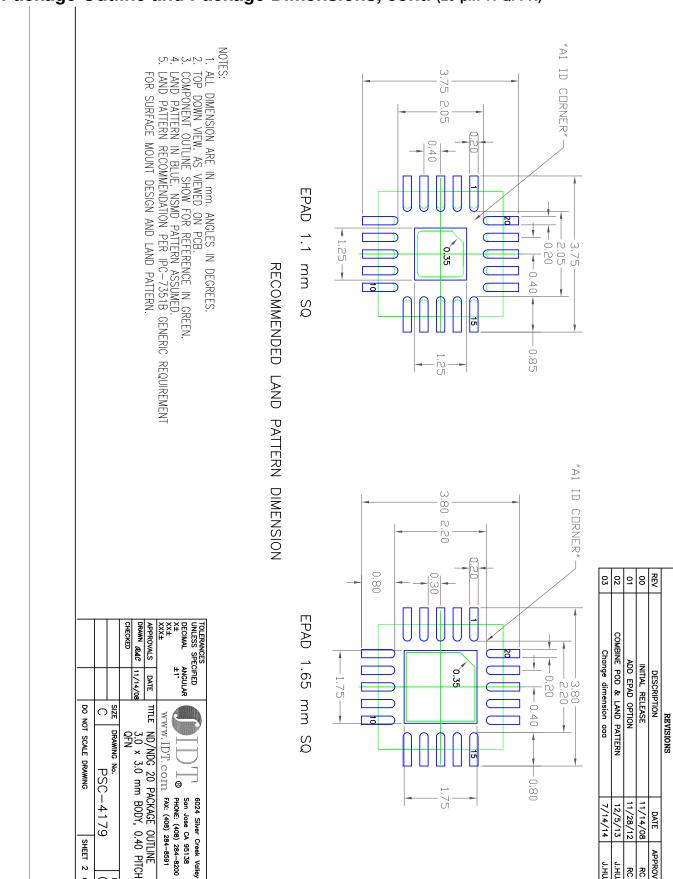

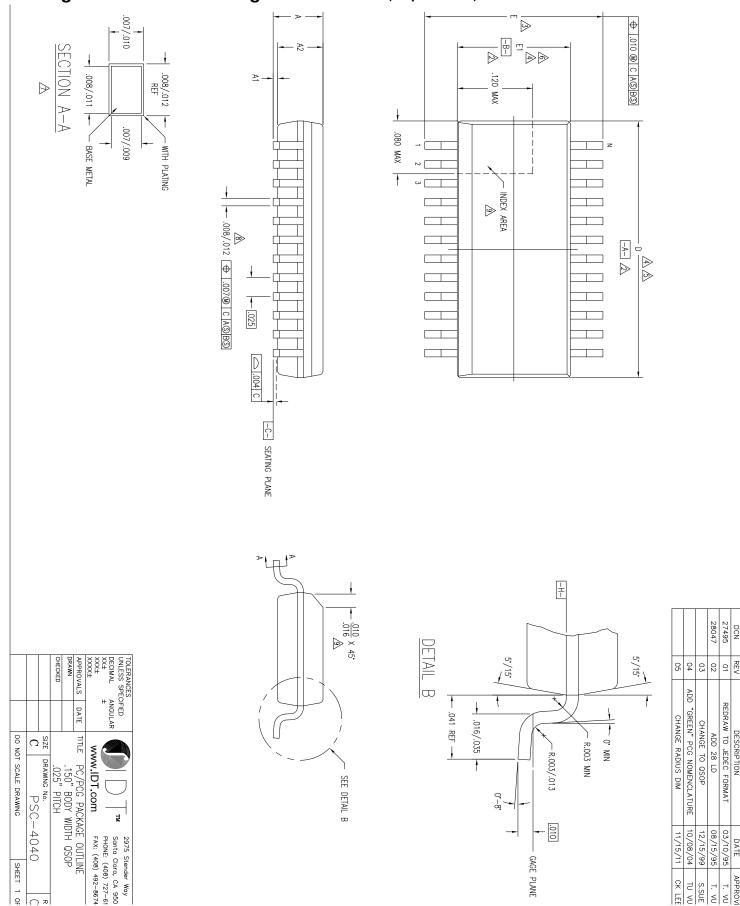

#### Package Outline and Package Dimensions (20-pin TSSOP)

mm  2975 Stender Way Santa Clara, CA 95054 PHONE: (408) 727-6116 FAX: (408) 492-8674

SHEET 2 OF 3

| 74FCT | 3807S                                                                                                     | DATA                                                                                 | SHEET                                                                                           |                                                                                                                                                                                                                                       |                                                                                         |                                                                                                                                  |                                                                                                                                               |                                                             |                                                       |                                                              |                                                              |        |           |

|-------|-----------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|-------------------------------------------------------|--------------------------------------------------------------|--------------------------------------------------------------|--------|-----------|

|       | ckag                                                                                                      | je C                                                                                 | Dutli                                                                                           | ne and                                                                                                                                                                                                                                | d Pa                                                                                    | icka                                                                                                                             | ge l                                                                                                                                          | Dir                                                         | ne                                                    | ns                                                           | ior                                                          | IS, C  | ont. (20- |

|       | =                                                                                                         | 10                                                                                   | Ø                                                                                               | ⊗                                                                                                                                                                                                                                     | $\land$                                                                                 | ♪                                                                                                                                | A                                                                                                                                             | A                                                           | A                                                     |                                                              | <u> </u>                                                     |        |           |

|       | THIS OUTLINE CONFORMS TO JEDEC PUBLICATION 95 REGISTRATION MO-153,<br>VARIATION AA, AB-1, AB, AC, AD & AE | ALL DIMENSIONS ARE IN MILLIMETERS                                                    | THESE DIMENSIONS APPLY TO THE FLAT SECTION OF THE LEAD BETWEEN .10 AND .25 mm FROM THE LEAD TIP | LEAD WIDTH DIMENSION DOES NOT INCLUDE DAMBAR PROTRUSION, ALLOWABLE<br>DAMBAR PROTRUSION IS .08 mm IN EXCESS OF THE LEAD WIDTH DIMENSION<br>AT MAXIMUM MATERIAL CONDITION. DAMBAR CANNOT BE LOCATED ON THE LOWER<br>RADIUS OR THE FOOT | detail of Pin 1 identifier is optional but must be located within<br>The zone indicated | DIMENSION E1 DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSIONS. INTERLEAD<br>FLASH OR PROTRUSIONS SHALL NOT EXCEED .25 mm PER SIDE | DIMENSION D DOES NOT INCLUDE MOLD FLASH, PROTRUSIONS OR GATE BURRS.<br>MOLD FLASH, PROTRUSIONS OR GATE BURRS SHALL NOT EXCEED .15 mm PER SIDE | DIMENSIONS D AND E1 ARE TO BE DETERMINED AT DATUM PLANE -H- | DIMENSION E TO BE DETERMINED AT SEATING PLANE $[-C-]$ | datums [_a_] and [_b_] to be determined at datum plane [_h_] | ALL DIMENSIONING AND TOLERANCING CONFORM TO ASME Y14.5M-1994 | NOTES: |           |

|       |                                                                                                           | APPROVALS DATE III-E PG/PGG PACKAGE OUTLINE<br>OREOXED 4.4 mm BODY WIDTH TSSOP 65 mm | ANGULAR<br>↓<br>WWW.IDT.com                                                                     | INLESS SPECIFIED                                                                                                                                                                                                                      |                                                                                         |                                                                                                                                  |                                                                                                                                               |                                                             |                                                       |                                                              |                                                              |        |           |

#### Pa 20-pin TSSOP)

|        | 90                 | 05                           | 04                     | 03       | 02             | REV         |           |  |

|--------|--------------------|------------------------------|------------------------|----------|----------------|-------------|-----------|--|

|        | ADDED PACKAGE CODE | ADD "GREEN" PGG NOMENCLATURE | ADDED TOPMARK TO TITLE | ADD 8 LD | ADD 14 & 16 LD | DESCRIPTION | REVISIONS |  |

| 0,1010 | 3/8/13             | 10/14/04                     | 5/23/01                | 07/10/99 | 08/25/98       | DATE        |           |  |

|        | RAC                | JU VI                        |                        | T. VU    | T. VU          | APPROVED    |           |  |

| RE     | REVISION A 03/18   |                              |                        |          |                |             |           |  |

10

4.30

4.50

4,6 ,**4**

6.40 BSC .65 BSC 4.40

Ś

.19 .19

.22

.25

Т

.80 6.40

1.00 6.50

1.05 6.60 1.20 .15

.05

I

MIN

L

I

JEDEC VARIATION AC MIN NOM MAX

m⊣oz

PG/PGG20

## Package Outline and Package Dimensions, cont. (20-pin TSSOP)

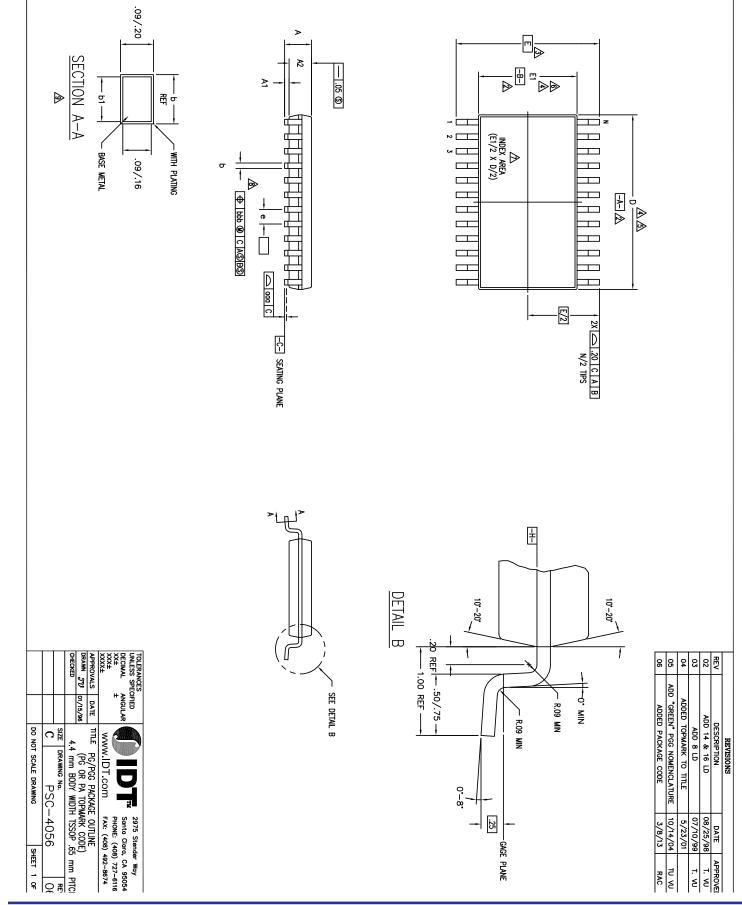

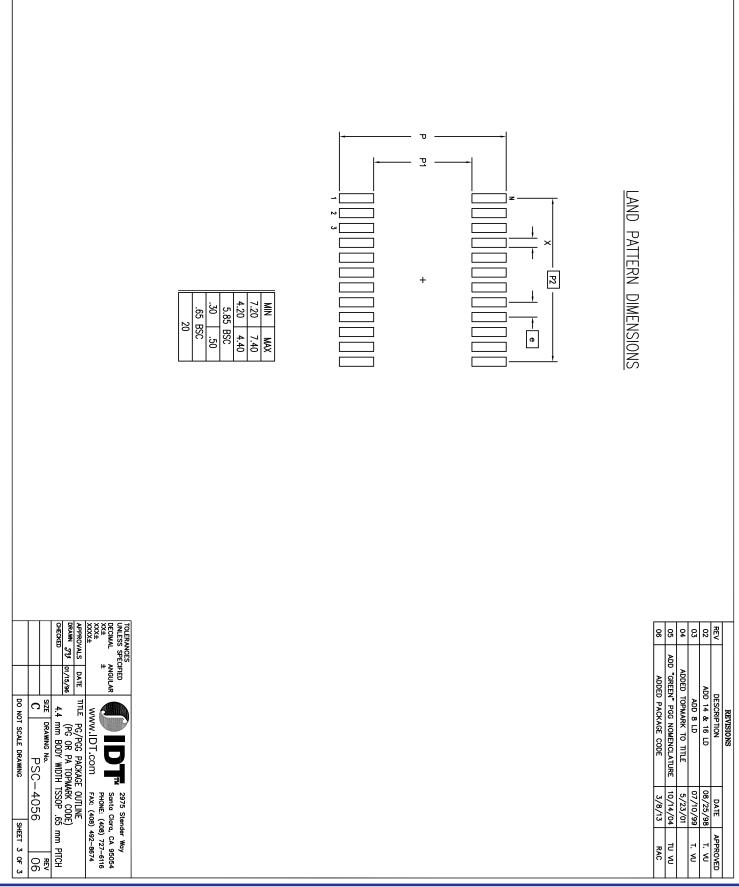

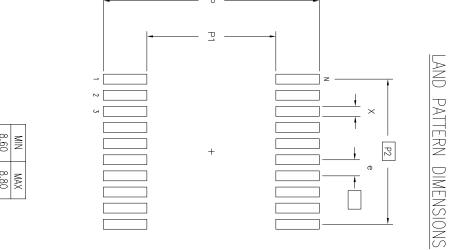

### Package Outline and Package Dimensions (20-pin QSOP)

REVISIONS

## () IDT

### Package Outline and Package Dimensions, cont. (20-pin QSOP)

| аскад                                                                 | <b>⊥</b>                                                           | -0<br>-0                            |                                                                                                                                        |                                                                                                                                                                                                                                     | Fac<br>Þ                                                                                   | kage                                                                                                                        |                                                                                                                                              |                                                             |                                                   |                                                        | ,                                                            | 0011   | L. (20-pin QSOP)                                                                                                                                                                                                                                                                                               |

|-----------------------------------------------------------------------|--------------------------------------------------------------------|-------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|---------------------------------------------------|--------------------------------------------------------|--------------------------------------------------------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VARIATION AB, AD, AE & AF. EXCEPTIONS: JEDEC DIMENSION AZ MAX IS .059 | THIS OUTLINE CONFORMS TO JEDEC PUBLICATION 95 REGISTRATION MO-137, | ALL DIMENSIONS ARE IN INCHES        | THE CHAMFER ON THE PACKAGE BODY IS OPTIONAL. IF IT IS NOT PRESENT,<br>A VISUAL INDEX FEATURE MUST BE LOCATED WITHIN THE ZONE INDICATED | LEAD WIDTH DIMENSION DOES NOT INCLUDE DAMBAR PROTRUSION, ALLOWABLE<br>DAMBAR PROTRUSION IS .004 IN EXCESS OF THE LEAD WIDTH DIMENSION<br>AT MAXIMUM MATERIAL CONDITION. DAMBAR CANNOT BE LOCATED ON THE LOWER<br>RADIUS OR THE FOOT | THESE DIMENSIONS APPLY TO THE FLAT SECTION OF THE LEAD BETWEEN .005 AND .010 FROM LEAD TIP | DIMENSION E1 DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSIONS. INTERLEAD FLASH OR PROTRUSIONS SHALL NOT EXCEED .010 PER SIDE | DIMENSION D DOES NOT INCLUDE MOLD FLASH, PROTRUSIONS OR GATE BURRS.<br>MOLD FLASH, PROTRUSIONS AND GATE BURRS SHALL NOT EXCEED .006 PER SIDE | DIMENSIONS D AND E1 ARE TO BE DETERMINED AT DATUM PLANE -H- | DIMENSION E TO BE DETERMINED AT SEATING PLANE -C- | DATUMS -A- AND -B- TO BE DETERMINED AT DATUM PLANE -H- | ALL DIMENSIONING AND TOLERANCING CONFORM TO ANSI Y14.5M-1982 | NOTES: | JEDEC         VARIATION         N           AD         T         T           .061         .064         .068           .004         .006         .010           .337         .342         .344         4.5           .150         .155         .157         4.6           20         20         4.6         4.6 |

| DO NOT SCALE DRAWING                                                  | ACKA                                                               | XX± WWW.IDT.com FAX: (408) 492-8674 |                                                                                                                                        | 20 8                                                                                                                                                                                                                                | .142 .150<br>.225 BSC<br>010 018                                                           | MIN MAX<br>.274 .282                                                                                                        | -                                                                                                                                            |                                                             |                                                   |                                                        |                                                              | +      | AND PATTERN DIMENSIONS                                                                                                                                                                                                                                                                                         |

REVISIONS

DATE

APPROVED

DCN

REV

DESCRIPTION

DATE

APPROVED

28047

02

ADD 28 LD

08/15/95

T. VU

28047

03

CHANGE TO QSOP

12/15/99

S.SUE

04

ADD "GREIN" PGC NOMENCLATURE

10/08/04

TU VU

05

CHANGE RADIUS DIM

11/15/11

CK LEE

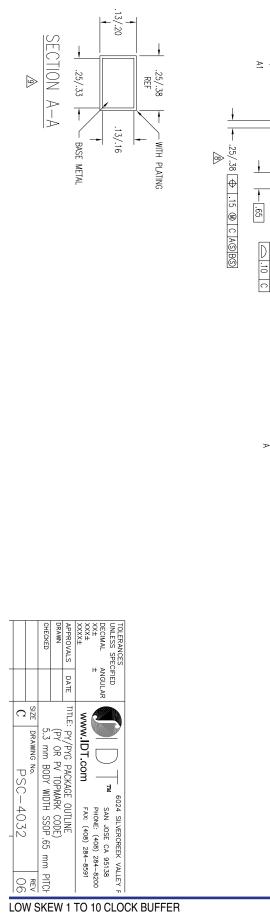

#### Package Outline and Package Dimensions (20-pin SSOP)

Π

Π

() IDT

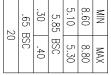

## Package Outline and Package Dimensions, cont. (20-pin SSOP)

|    | 5.20 | 7.65 | 7.07 | 1.68 | .05 | 1.73 | MIN |    | JEDEC     |          |

|----|------|------|------|------|-----|------|-----|----|-----------|----------|

| 20 | 5.30 | 7.80 | 7.20 | 1.73 | .13 | 1.86 | NON | AE | VARIATION | PY/PYG20 |

|    | 5.38 | 7.90 | 7.33 | 1.78 | .21 | 1.99 | MAX |    | ION       | G20      |

|    | 4,6  | Ы    | 4,5  |      |     |      | m   | -0 | z         |          |

## Package Outline and Package Dimensions, cont. (20-pin SSOP)

| 6                  | 05 /                         | 04                     | 03             | 02                     | 9         | 8               | REV         |                           |

|--------------------|------------------------------|------------------------|----------------|------------------------|-----------|-----------------|-------------|---------------------------|

| ADDED PACKAGE CODE | ADD "GREEN" PYG NOMENCLATURE | ADDED TOPMARK TO TITLE | ADD 14 & 16 LD | REDRAW TO JEDEC FORMAT | ADD 28 LD | INITIAL RELEASE | DESCRIPTION | A 4444 • A 444 A 44 A 144 |

| 12/12/12           | 10/12/04                     | 5/23/01                | 08/25/98       | 03/15/95               | 07/27/93  | 04/15/91        | DATE        |                           |

| RC                 | TU VU                        | T. VU                  | T. VU          | T. VU                  | T. VU     | T. VU           | APPROVED    |                           |

## Ordering Information

| Part / Order Number | Marking    | Shipping Packaging | Package       | Temperature    |

|---------------------|------------|--------------------|---------------|----------------|

| 74FCT3807SNDGI      | see page 6 | Tubes              | 20-pin VFQFPN | -40° to +105°C |

| 74FCT3807SNDGI8     |            | Tape and Reel      | 20-pin VFQFPN | -40° to +105°C |

| 74FCT3807SPGGI      |            | Tubes              | 20-pin TSSOP  | -40° to +105°C |

| 74FCT3807SPGGI8     |            | Tape and Reel      | 20-pin TSSOP  | -40° to +105°C |

| 74FCT3807SQGI       |            | Tubes              | 20-pin QSOP   | -40° to +105°C |

| 74FCT3807SQGI8      |            | Tape and Reel      | 20-pin QSOP   | -40° to +105°C |

| 74FCT3807SPYGI      |            | Tubes              | 20-pin SSOP   | -40° to +105°C |

| 74FCT3807SPYGI8     |            | Tape and Reel      | 20-pin SSOP   | -40° to +105°C |

"G" after the two-letter package code denotes Pb-Free configuration, RoHS compliant.

## **Revision History**

| Rev. | Date     | Originator   | Description of Change |

|------|----------|--------------|-----------------------|

| А    | 03/18/15 | B. Chandhoke | Initial release.      |

#### **Corporate Headquarters** 6024 Silver Creek Valley Road San Jose, CA 95138 USA

**Sales** 1-800-345-7015 or 408-284-8200 Fax: 408-284-2775 www.IDT.com Tech Support email: clocks@idt.com

DISCLAIMER Integrated Device Technology, Inc. (IDT) and its subsidiaries reserve the right to modify the products and/or specifications described herein at any time and at IDT's sole discretion. All information in this document, including descriptions of product features and performance, is subject to change without notice. Performance specifications and the operating parameters of the described products are determined in the independent state and are not guaranteed to perform the same way when installed in customer products. The information contained herein is provided without representation or warranty of any kind, whether express or implied, including, but not limited to, the suitability of IDT's products for any particular purpose, an implied warranty of merchantability, or non-infringement of the intellectual property rights of others. This document is presented only as a guide and does not convey any license under intellectual property rights of IDT or any third parties.

IDT's products are not intended for use in applications involving extreme environmental conditions or in life support systems or similar devices where the failure or malfunction of an IDT product can be reasonably expected to significantly affect the health or safety of users. Anyone using an IDT product in such a manner does so at their own risk, absent an express, written agreement by IDT.

Integrated Device Technology, IDT and the IDT logo are registered trademarks of IDT. Product specification subject to change without notice. Other trademarks and service marks used herein, including protected names, logos and designs, are the property of IDT or their respective third party owners.

Copyright ©2015 Integrated Device Technology, Inc.. All rights reserved.