Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

### INTEGRATED CIRCUITS

# DATA SHEET

For a complete data sheet, please also download:

- The IC06 74HC/HCT/HCU/HCMOS Logic Family Specifications

- The IC06 74HC/HCT/HCU/HCMOS Logic Package Information

- The IC06 74HC/HCT/HCU/HCMOS Logic Package Outlines

# **74HC/HCT191**Presettable synchronous 4-bit binary up/down counter

Product specification

File under Integrated Circuits, IC06

December 1990

### 74HC/HCT191

#### **FEATURES**

- · Synchronous reversible counting

- · Asynchronous parallel load

- · Count enable control for synchronous expansion

- Single up/down control input

- Output capability: standard

- I<sub>CC</sub> category: MSI

#### **GENERAL DESCRIPTION**

The 74HC/HCT191 are high-speed Si-gate CMOS devices and are pin compatible with low power Schottky TTL (LSTTL). They are specified in compliance with JEDEC standard no. 7A.

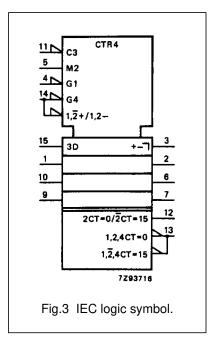

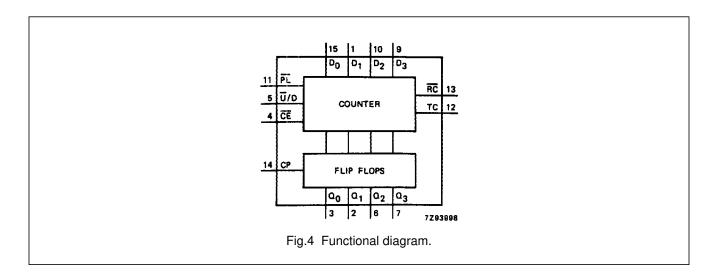

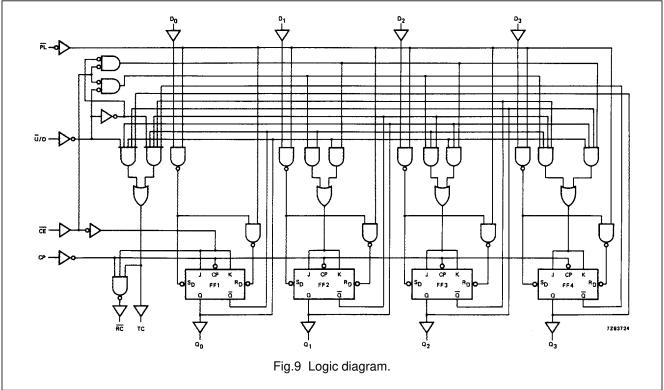

The 74HC/HCT191 are asynchronously presettable 4-bit binary up/down counters. They contain four master/slave flip-flops with internal gating and steering logic to provide asynchronous preset and synchronous count-up and count-down operation.

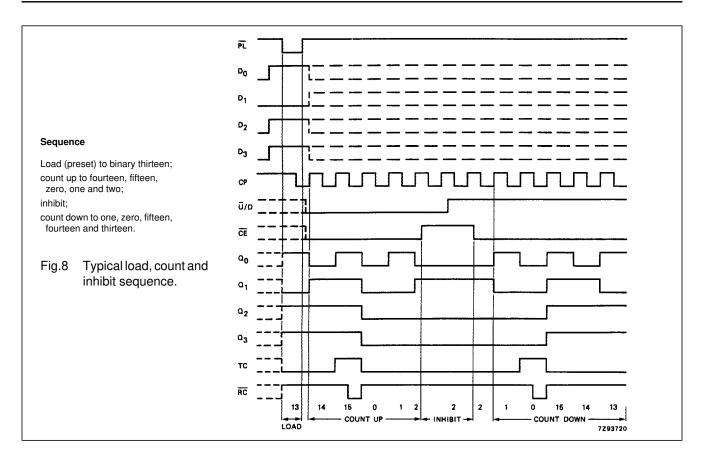

Asynchronous parallel load capability permits the counter to be preset to any desired number. Information present on the parallel data inputs ( $D_0$  to  $D_3$ ) is loaded into the counter and appears on the outputs when the parallel load ( $\overline{PL}$ ) input is LOW. As indicated in the function table, this operation overrides the counting function.

Counting is inhibited by a HIGH level on the count enable  $(\overline{CE})$  input. When  $\overline{CE}$  is LOW internal state changes are initiated synchronously by the LOW-to-HIGH transition of the clock input. The up/down  $(\overline{U}/D)$  input signal determines the direction of counting as indicated in the function table. The  $\overline{CE}$  input may go LOW when the clock is in either state, however, the LOW-to-HIGH  $\overline{CE}$  transition must occur only when the clock is HIGH. Also, the  $\overline{U}/D$  input should be changed only when either  $\overline{CE}$  or CP is HIGH.

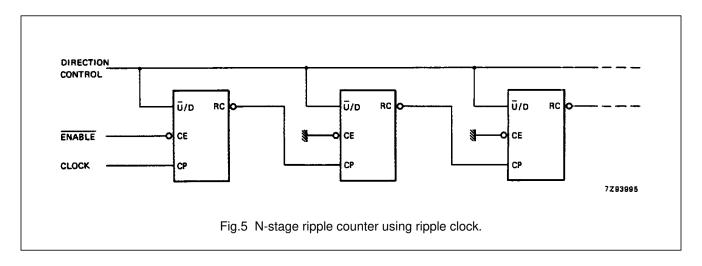

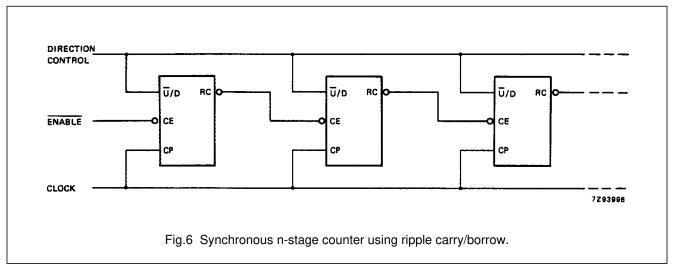

Overflow/underflow indications are provided by two types of outputs, the terminal count (TC) and ripple clock ( $\overline{RC}$ ). The TC output is normally LOW and goes HIGH when a circuit reaches zero in the count-down mode or reaches "15" in the count-up-mode. The TC output will remain HIGH until a state change occurs, either by counting or presetting, or until  $\overline{U}/D$  is changed. Do not use the TC output as a clock signal because it is subject to decoding spikes. The TC signal is used internally to enable the  $\overline{RC}$  output. When TC is HIGH and  $\overline{CE}$  is LOW, the  $\overline{RC}$  output follows the clock pulse (CP). This feature simplifies the design of multistage counters as shown in Figs 5 and 6.

In Fig.5, each  $\overline{RC}$  output is used as the clock input to the next higher stage. It is only necessary to inhibit the first stage to prevent counting in all stages, since a HIGH on  $\overline{CE}$  inhibits the  $\overline{RC}$  output pulse as indicated in the function table. The timing skew between state changes in the first and last stages is represented by the cumulative delay of the clock as it ripples through the preceding stages. This can be a disadvantage of this configuration in some applications.

Fig.6 shows a method of causing state changes to occur simultaneously in all stages. The  $\overline{RC}$  outputs propagate the carry/borrow signals in ripple fashion and all clock inputs are driven in parallel. In this configuration the duration of the clock LOW state must be long enough to allow the negative-going edge of the carry/borrow signal to ripple through to the last stage before the clock goes HIGH. Since the  $\overline{RC}$  output of any package goes HIGH shortly after its CP input goes HIGH there is no such restriction on the HIGH-state duration of the clock.

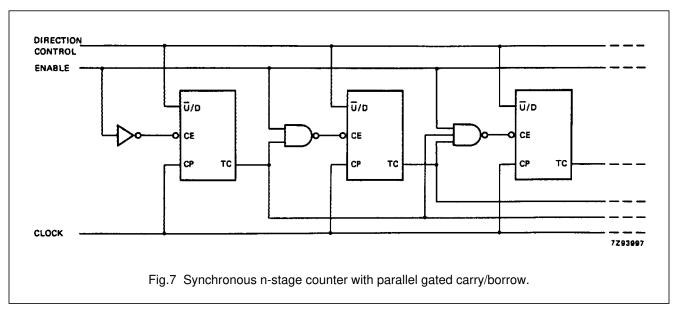

In Fig.7, the configuration shown avoids ripple delays and their associated restrictions. Combining the TC signals from all the preceding stages forms the  $\overline{\text{CE}}$  input for a given stage. An enable must be included in each carry gate in order to inhibit counting. The TC output of a given stage it not affected by its own  $\overline{\text{CE}}$  signal therefore the simple inhibit scheme of Figs 5 and 6 does not apply.

# Presettable synchronous 4-bit binary up/down counter

74HC/HCT191

### **QUICK REFERENCE DATA**

GND = 0 V;  $T_{amb}$  = 25 °C;  $t_r$  =  $t_f$  = 6 ns

| SYMBOL                              | PARAMETER                                 | CONDITIONS                                  | TYP | UNIT |      |  |

|-------------------------------------|-------------------------------------------|---------------------------------------------|-----|------|------|--|

| STWIDOL                             | PARAMETER                                 | CONDITIONS                                  | нс  | нст  | UNIT |  |

| t <sub>PHL</sub> / t <sub>PLH</sub> | propagation delay CP to Q <sub>n</sub>    | $C_L = 15 \text{ pF}; V_{CC} = 5 \text{ V}$ | 22  | 22   | ns   |  |

| f <sub>max</sub>                    | maximum clock frequency                   |                                             | 36  | 36   | MHz  |  |

| C <sub>I</sub>                      | input capacitance                         |                                             | 3.5 | 3.5  | pF   |  |

| C <sub>PD</sub>                     | power dissipation capacitance per package | notes 1 and 2                               | 31  | 33   | pF   |  |

### **Notes**

1.  $C_{PD}$  is used to determine the dynamic power dissipation ( $P_D$  in  $\mu W$ ):

$$P_D = C_{PD} \times V_{CC}{}^2 \times f_i + \sum \left( C_L \times V_{CC}{}^2 \times f_o \right)$$

where:

$f_i$  = input frequency in MHz

$f_o$  = output frequency in MHz

$\sum_{c} (C_L \times V_{CC}^2 \times f_o) = \text{sum of outputs}$   $C_L = \text{output load capacitance in pF}$

V<sub>CC</sub> = supply voltage in V

2. For HC the condition is  $V_I = \text{GND}$  to  $V_{\text{CC}}$ For HCT the condition is  $V_I$  = GND to  $V_{CC}$  –1.5 V

### **ORDERING INFORMATION**

See "74HC/HCT/HCU/HCMOS Logic Package Information".

# 74HC/HCT191

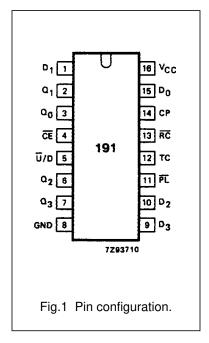

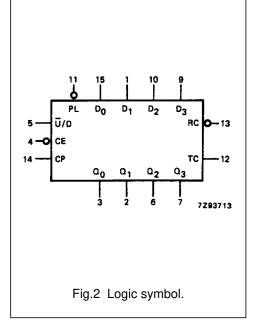

### **PIN DESCRIPTION**

| PIN NO.      | SYMBOL                           | NAME AND FUNCTION                         |

|--------------|----------------------------------|-------------------------------------------|

| 3, 2, 6, 7   | Q <sub>0</sub> to Q <sub>3</sub> | flip-flop outputs                         |

| 4            | CE                               | count enable input (active LOW)           |

| 5            | Ū/D                              | up/down input                             |

| 8            | GND                              | ground (0 V)                              |

| 11           | PL                               | parallel load input (active LOW)          |

| 12           | TC                               | terminal count output                     |

| 13           | RC                               | ripple clock output (active LOW)          |

| 14           | CP                               | clock input (LOW-to-HIGH, edge triggered) |

| 15, 1, 10, 9 | D <sub>0</sub> to D <sub>3</sub> | data inputs                               |

| 16           | V <sub>CC</sub>                  | positive supply voltage                   |

# Presettable synchronous 4-bit binary up/down counter

74HC/HCT191

### **FUNCTION TABLE**

| OPERATING MODE    |        |        | OUTPUTS |        |                |                |

|-------------------|--------|--------|---------|--------|----------------|----------------|

| OPERATING MODE    | PL     | U/D    | CE      | СР     | D <sub>n</sub> | Q <sub>n</sub> |

| parallel load     | L<br>L | X<br>X | X<br>X  | X<br>X | L<br>H         | L<br>H         |

| count up          | Н      | L      | I       | 1      | Х              | count up       |

| count down        | Н      | Н      | I       | 1      | Х              | count down     |

| hold (do nothing) | Н      | Х      | Н       | Х      | Х              | no change      |

### TC AND RC FUNCTION TABLE

|     | INPUTS |    |       | TERMINAL C     | OUTPUTS |                |          |    |

|-----|--------|----|-------|----------------|---------|----------------|----------|----|

| U/D | CE     | СР | $Q_0$ | Q <sub>1</sub> | $Q_2$   | Q <sub>3</sub> | TC       | RC |

| Н   | Н      | Х  | Н     | Н              | Н       | Н              | L        | Н  |

| L   | Н      | X  | Н     | Н              | Н       | Н              | Н        | Н  |

| L   | L      |    | Н     | Н              | Н       | Н              | <b>し</b> |    |

| L   | Н      | X  | L     | L              | L       | L              | L        | Н  |

| Н   | Н      | X  | L     | L              | L       | L              | Н        | Н  |

| Н   | L      |    | L     | L              | L       | L              | l        |    |

### **Notes**

- 1. H = HIGH voltage level

- L = LOW voltage level

- I = LOW voltage level one set-up time prior to the LOW-to-HIGH CP transition

- X = don't care

- ↑ = LOW-to-HIGH CP transition

- = one LOW level pulse

- = TC goes LOW on a LOW-to-HIGH CP transition

# Presettable synchronous 4-bit binary up/down counter

74HC/HCT191

### DC CHARACTERISTICS FOR 74HC

For the DC characteristics see "74HC/HCT/HCU/HCMOS Logic Family Specifications".

Output capability: standard

I<sub>CC</sub> category: MSI

### **AC CHARACTERISTICS FOR 74HC**

$GND = 0 V; t_r = t_f = 6 ns; C_L = 50 pF$

|                                     |                                                    |                 |                |                 | T <sub>amb</sub> (° |                 | TES             | TEST CONDITIONS |      |                        |           |  |

|-------------------------------------|----------------------------------------------------|-----------------|----------------|-----------------|---------------------|-----------------|-----------------|-----------------|------|------------------------|-----------|--|

| 0)/440.01                           | DADAMETED                                          | 74HC            |                |                 |                     |                 |                 |                 |      |                        |           |  |

| SYMBOL                              | PARAMETER                                          | +25             |                |                 | -40 to +85          |                 | -40 to +125     |                 | UNIT | V <sub>CC</sub><br>(V) | WAVEFORMS |  |

|                                     |                                                    | min.            | typ.           | max.            | min.                | max.            | min.            | max.            |      | (*)                    |           |  |

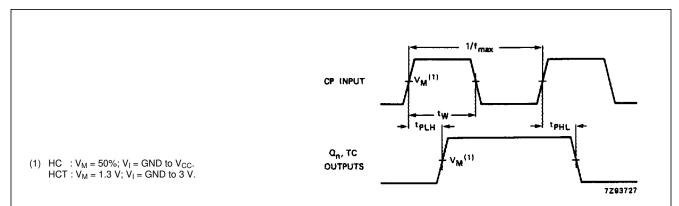

| t <sub>PHL</sub> / t <sub>PLH</sub> | propagation delay<br>CP to Q <sub>n</sub>          |                 | 72<br>26<br>21 | 220<br>44<br>37 |                     | 275<br>55<br>47 |                 | 330<br>66<br>56 | ns   | 2.0<br>4.5<br>6.0      | Fig.10    |  |

| t <sub>PHL</sub> / t <sub>PLH</sub> | propagation delay<br>CP to TC                      |                 | 83<br>30<br>24 | 255<br>51<br>43 |                     | 320<br>64<br>54 |                 | 395<br>77<br>65 | ns   | 2.0<br>4.5<br>6.0      | Fig.10    |  |

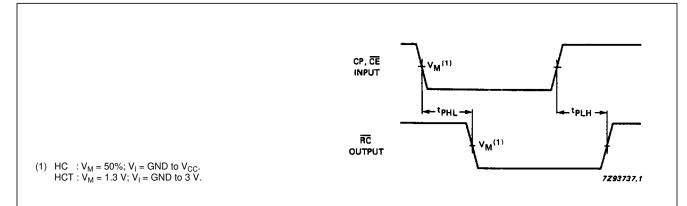

| t <sub>PHL</sub> / t <sub>PLH</sub> | propagation delay<br>CP to RC                      |                 | 47<br>17<br>14 | 150<br>30<br>26 |                     | 190<br>38<br>33 |                 | 225<br>45<br>38 | ns   | 2.0<br>4.5<br>6.0      | Fig.11    |  |

| t <sub>PHL</sub> / t <sub>PLH</sub> | propagation delay<br>CE to RC                      |                 | 33<br>12<br>10 | 130<br>26<br>22 |                     | 165<br>33<br>28 |                 | 195<br>39<br>33 | ns   | 2.0<br>4.5<br>6.0      | Fig.11    |  |

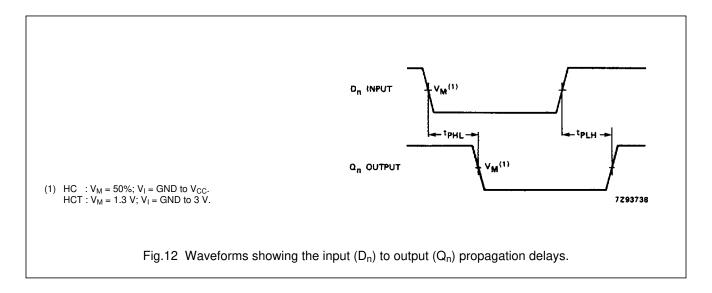

| t <sub>PHL</sub> / t <sub>PLH</sub> | propagation delay D <sub>n</sub> to Q <sub>n</sub> |                 | 61<br>22<br>18 | 220<br>44<br>37 |                     | 275<br>55<br>47 |                 | 330<br>66<br>56 | ns   | 2.0<br>4.5<br>6.0      | Fig.12    |  |

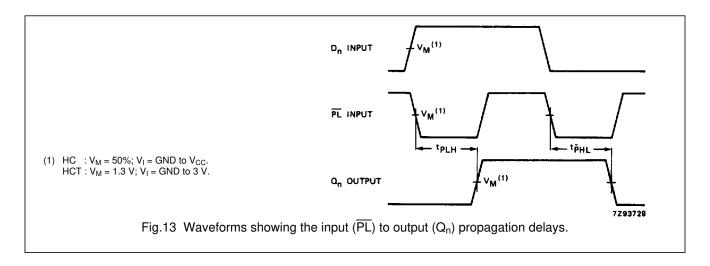

| t <sub>PHL</sub> / t <sub>PLH</sub> | propagation delay<br>PL to Q <sub>n</sub>          |                 | 61<br>22<br>18 | 220<br>44<br>37 |                     | 275<br>55<br>47 |                 | 330<br>66<br>56 | ns   | 2.0<br>4.5<br>6.0      | Fig.13    |  |

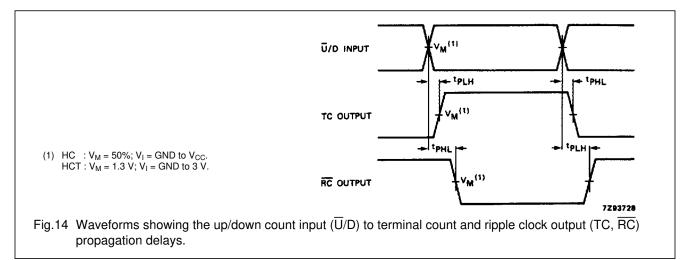

| t <sub>PHL</sub> / t <sub>PLH</sub> | propagation delay<br>U/D to TC                     |                 | 44<br>16<br>13 | 190<br>38<br>32 |                     | 240<br>48<br>41 |                 | 285<br>57<br>48 | ns   | 2.0<br>4.5<br>6.0      | Fig.14    |  |

| t <sub>PHL</sub> / t <sub>PLH</sub> | propagation delay<br>U/D to RC                     |                 | 50<br>18<br>14 | 210<br>42<br>36 |                     | 265<br>53<br>45 |                 | 315<br>63<br>54 | ns   | 2.0<br>4.5<br>6.0      | Fig.14    |  |

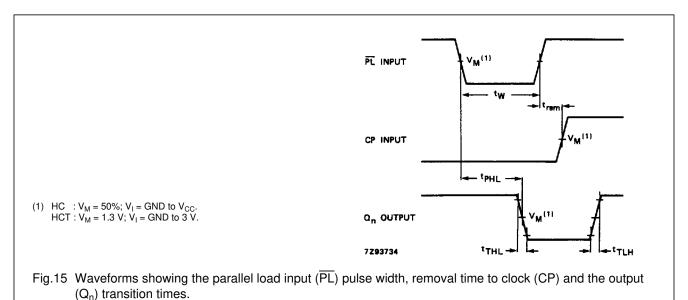

| t <sub>THL</sub> / t <sub>TLH</sub> | output transition time                             |                 | 19<br>7<br>6   | 75<br>15<br>13  |                     | 95<br>19<br>16  |                 | 110<br>22<br>19 | ns   | 2.0<br>4.5<br>6.0      | Fig.15    |  |

| t <sub>W</sub>                      | clock pulse width<br>HIGH or LOW                   | 125<br>25<br>21 | 28<br>10<br>8  |                 | 155<br>31<br>26     |                 | 195<br>39<br>33 |                 | ns   | 2.0<br>4.5<br>6.0      | Fig.10    |  |

| t <sub>W</sub>                      | parallel load pulse width<br>LOW                   | 100<br>20<br>17 | 22<br>8<br>6   |                 | 125<br>25<br>21     |                 | 150<br>30<br>26 |                 | ns   | 2.0<br>4.5<br>6.0      | Fig.15    |  |

# Presettable synchronous 4-bit binary up/down counter

|                  | 242445                              |                 |                   |      | T <sub>amb</sub> (° |      | TEST CONDITIONS |           |      |                   |           |

|------------------|-------------------------------------|-----------------|-------------------|------|---------------------|------|-----------------|-----------|------|-------------------|-----------|

| OVMBOL           |                                     |                 |                   |      | 74HC                |      |                 | WAVEFORMO |      |                   |           |

| SYMBOL           | PARAMETER                           | +25             |                   |      | -40 to +85          |      | -40 to +125     |           | UNIT | V <sub>CC</sub>   | WAVEFORMS |

|                  |                                     | min.            | typ.              | max. | min.                | max. | min.            | max.      |      | (•)               |           |

| t <sub>rem</sub> | removal time PL to CP               | 35<br>7<br>6    | 8<br>3<br>2       |      | 45<br>9<br>8        |      | 55<br>11<br>9   |           | ns   | 2.0<br>4.5<br>6.0 | Fig.15    |

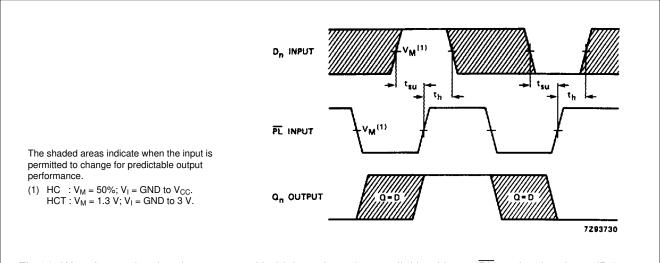

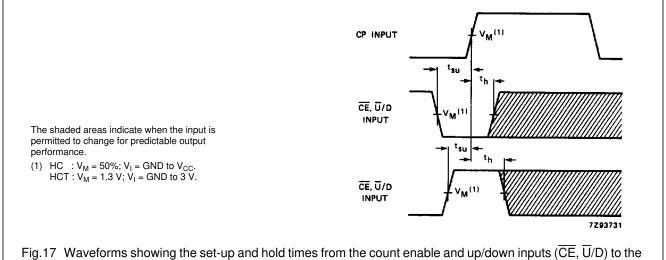

| t <sub>su</sub>  | set-up time<br>U/D to CP            | 205<br>41<br>35 | 50<br>18<br>14    |      | 255<br>51<br>43     |      | 310<br>62<br>53 |           | ns   | 2.0<br>4.5<br>6.0 | Fig.17    |

| t <sub>su</sub>  | set-up time<br>D <sub>n</sub> to PL | 100<br>20<br>17 | 19<br>7<br>6      |      | 125<br>25<br>21     |      | 150<br>30<br>26 |           | ns   | 2.0<br>4.5<br>6.0 | Fig.16    |

| t <sub>su</sub>  | set-up time<br>CE to CP             | 140<br>28<br>24 | 44<br>16<br>13    |      | 175<br>35<br>30     |      | 210<br>42<br>36 |           | ns   | 2.0<br>4.5<br>6.0 | Fig.17    |

| t <sub>h</sub>   | hold time<br>Ū/D to CP              | 0<br>0<br>0     | -39<br>-14<br>-11 |      | 0<br>0<br>0         |      | 0<br>0<br>0     |           | ns   | 2.0<br>4.5<br>6.0 | Fig.17    |

| t <sub>h</sub>   | hold time<br>D <sub>n</sub> to PL   | 0<br>0<br>0     | -11<br>-4<br>-3   |      | 0<br>0<br>0         |      | 0<br>0<br>0     |           | ns   | 2.0<br>4.5<br>6.0 | Fig.16    |

| t <sub>h</sub>   | hold time<br>CE to CP               | 0<br>0<br>0     | -28<br>-10<br>-8  |      | 0<br>0<br>0         |      | 0<br>0<br>0     |           | ns   | 2.0<br>4.5<br>6.0 | Fig.17    |

| f <sub>max</sub> | maximum clock pulse frequency       | 4.0<br>20<br>24 | 11<br>33<br>39    |      | 3.2<br>16<br>19     |      | 2.6<br>13<br>15 |           | MHz  | 2.0<br>4.5<br>6.0 | Fig.10    |

# Presettable synchronous 4-bit binary up/down counter

74HC/HCT191

### DC CHARACTERISTICS FOR 74HCT

For the DC characteristics see "74HC/HCT/HCU/HCMOS Logic Family Specifications".

Output capability: standard

I<sub>CC</sub> category: MSI

### Note to HCT types

The value of additional quiescent supply current ( $\Delta I_{CC}$ ) for a unit load of 1 is given in the family specifications. To determine  $\Delta I_{CC}$  per input, multiply this value by the unit load coefficient shown in the table below.

| INPUT          | UNIT LOAD COEFFICIENT |

|----------------|-----------------------|

| D <sub>n</sub> | 0.5                   |

| CP             | 0.65                  |

| Ū/D            | 1.15                  |

| CE, PL         | 1.5                   |

# Presettable synchronous 4-bit binary up/down counter

74HC/HCT191

### **AC CHARACTERISTICS FOR 74HCT**

$GND = 0 \ V; t_r = t_f = 6 \ ns; C_L = 50 \ pF$

|                                     |                                                    |      |      |            | T <sub>amb</sub> (° |             | TEST CONDITIONS |           |                 |           |        |

|-------------------------------------|----------------------------------------------------|------|------|------------|---------------------|-------------|-----------------|-----------|-----------------|-----------|--------|

| SYMBOL                              | PARAMETER                                          |      |      |            | 74HC                | UNIT        |                 | WAVEFORMS |                 |           |        |

| STWBOL                              | FARAMETER                                          | +25  |      | -40 to +85 |                     | -40 to +125 |                 | ONIT      | V <sub>CC</sub> | WAVEFORMS |        |

|                                     |                                                    | min. | typ. | max.       | min.                | max.        | min.            | max.      |                 | . ,       |        |

| t <sub>PHL</sub> / t <sub>PLH</sub> | propagation delay<br>CP to Q <sub>n</sub>          |      | 26   | 48         |                     | 60          |                 | 72        | ns              | 4.5       | Fig.10 |

| t <sub>PHL</sub> / t <sub>PLH</sub> | propagation delay<br>CP to TC                      |      | 32   | 51         |                     | 64          |                 | 77        | ns              | 4.5       | Fig.10 |

| t <sub>PHL</sub> / t <sub>PLH</sub> | propagation delay<br>CP to RC                      |      | 19   | 35         |                     | 44          |                 | 53        | ns              | 4.5       | Fig.11 |

| t <sub>PHL</sub> / t <sub>PLH</sub> | propagation delay<br>CE to RC                      |      | 19   | 33         |                     | 41          |                 | 50        | ns              | 4.5       | Fig.11 |

| t <sub>PHL</sub> / t <sub>PLH</sub> | propagation delay D <sub>n</sub> to Q <sub>n</sub> |      | 22   | 44         |                     | 55          |                 | 66        | ns              | 4.5       | Fig.12 |

| t <sub>PHL</sub> / t <sub>PLH</sub> | propagation delay PL to Q <sub>n</sub>             |      | 27   | 46         |                     | 58          |                 | 69        | ns              | 4.5       | Fig.13 |

| t <sub>PHL</sub> / t <sub>PLH</sub> | propagation delay<br>U/D to TC                     |      | 23   | 45         |                     | 56          |                 | 68        | ns              | 4.5       | Fig.14 |

| t <sub>PHL</sub> / t <sub>PLH</sub> | propagation delay<br>U/D to RC                     |      | 24   | 45         |                     | 56          |                 | 68        | ns              | 4.5       | Fig.14 |

| t <sub>THL</sub> / t <sub>TLH</sub> | output transition time                             |      | 7    | 15         |                     | 19          |                 | 22        | ns              | 4.5       | Fig.15 |

| t <sub>W</sub>                      | clock pulse width<br>HIGH or LOW                   | 16   | 9    |            | 20                  |             | 24              |           | ns              | 4.5       | Fig.10 |

| t <sub>W</sub>                      | parallel load pulse width LOW                      | 22   | 11   |            | 28                  |             | 33              |           | ns              | 4.5       | Fig.15 |

| t <sub>rem</sub>                    | removal time PL to CP                              | 7    | 1    |            | 9                   |             | 11              |           | ns              | 4.5       | Fig.15 |

| t <sub>su</sub>                     | set-up time<br>U/D to CP                           | 41   | 20   |            | 51                  |             | 62              |           | ns              | 4.5       | Fig.17 |

| t <sub>su</sub>                     | set-up time<br>D <sub>n</sub> to PL                | 20   | 9    |            | 25                  |             | 30              |           | ns              | 4.5       | Fig.16 |

| t <sub>su</sub>                     | set-up time<br>CE to CP                            | 30   | 18   |            | 38                  |             | 45              |           | ns              | 4.5       | Fig.17 |

| t <sub>h</sub>                      | hold time<br>U/D to CP                             | 0    | -18  |            | 0                   |             | 0               |           | ns              | 4.5       | Fig.17 |

| t <sub>h</sub>                      | hold time<br>D <sub>n</sub> to PL                  | 0    | -5   |            | 0                   |             | 0               |           | ns              | 4.5       | Fig.16 |

| t <sub>h</sub>                      | hold time<br>CE to CP                              | 0    | -10  |            | 0                   |             | 0               |           | ns              | 4.5       | Fig.17 |

| f <sub>max</sub>                    | maximum clock pulse frequency                      | 20   | 33   |            | 16                  |             | 13              |           | MHz             | 4.5       | Fig.10 |

74HC/HCT191

#### **AC WAVEFORMS**

Fig.10 Waveforms showing the clock (CP) to output (Q<sub>n</sub>) propagation delays, the clock pulse width and the maximum clock pulse frequency.

Fig.11 Waveforms showing the clock and count enable inputs (CP,  $\overline{\text{CE}}$ ) to ripple clock output ( $\overline{\text{RC}}$ ) propagation delays.

# Presettable synchronous 4-bit binary up/down counter

# Presettable synchronous 4-bit binary up/down counter

74HC/HCT191

Fig.16 Waveforms showing the set-up and hold times from the parallel load input  $(\overline{PL})$  to the data input  $(D_n)$ .

Fig.17 Waveforms showing the set-up and hold times from the count enable and up/down inputs (CE, U/D) to the clock (CP).

### **PACKAGE OUTLINES**

See "74HC/HCT/HCU/HCMOS Logic Package Outlines".