# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

4-bit x 64-word FIFO register; 3-state

Rev. 1 — 21 September 2012

**Product data sheet**

## 1. General description

The 74HC7403-Q100; 74HCT7403-Q100 is an expandable, First-In First-Out (FIFO) memory organized as 64 words by 4 bits. A guaranteed 15 MHz data-rate makes it ideal for high-speed applications. A higher data-rate can be obtained in applications where the status flags are not used (burst-mode). With separate controls for shift-in (SI) and shift-out (SO), reading and writing operations are completely independent, allowing synchronous and asynchronous data transfers. Additional controls include a master-reset input ( $\overline{MR}$ ), an output enable input ( $\overline{OE}$ ) and flags. The data-in-ready (DIR) and data-out-ready (DOR) flags indicate the status of the device. Inputs include clamp diodes that enable the use of current limiting resistors to interface inputs to voltages in excess of V<sub>CC</sub>.

This product has been qualified to the Automotive Electronics Council (AEC) standard Q100 (Grade 1) and is suitable for use in automotive applications.

## 2. Features and benefits

- Automotive product qualification in accordance with AEC-Q100 (Grade 1)

- ◆ Specified from -40 °C to +85 °C and from -40 °C to +125 °C

- Synchronous or asynchronous operation

- 30 MHz (typical) shift-in and shift-out rates

- Readily expandable in word and bit dimensions

- Pinning arranged for easy board layout: input pins directly opposite output pins

- Input levels:

- For 74HC7403-Q100: CMOS level

- For 74HCT7403-Q100: TTL level

- 3-state outputs

- Complies with JEDEC standard JESD7A

- ESD protection:

- MIL-STD-883, method 3015 exceeds 2000 V

- HBM JESD22-A114F exceeds 2000 V

- MM JESD22-A115-A exceeds 200 V (C = 200 pF, R = 0  $\Omega$ )

- Multiple package options

## 3. Applications

- High-speed disc or tape controller

- Communications buffer

4-bit x 64-word FIFO register; 3-state

## 4. Ordering information

| Table 1.         Ordering information |                   |      |                                          |          |  |  |  |  |  |  |

|---------------------------------------|-------------------|------|------------------------------------------|----------|--|--|--|--|--|--|

| Type number Package                   |                   |      |                                          |          |  |  |  |  |  |  |

|                                       | Temperature range | Name | Description                              | Version  |  |  |  |  |  |  |

| 74HC7403D-Q100                        | -40 °C to +125 °C | SO16 | plastic small outline package; 16 leads; | SOT109-1 |  |  |  |  |  |  |

| 74HCT7403D-Q100                       |                   |      | body width 3.9 mm                        |          |  |  |  |  |  |  |

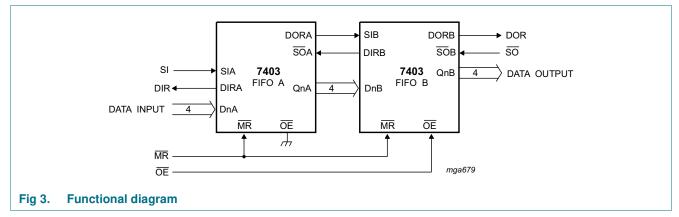

## 5. Functional diagram

NXP

Semiconductors

74HC7403-Q100;

74HCT7403-Q100

Rev. 1 ---21 September 2012

© NXP B.V. 2012. All rights reserved. 3 of 32

4-bit x 64-word FIFO register; 3-state

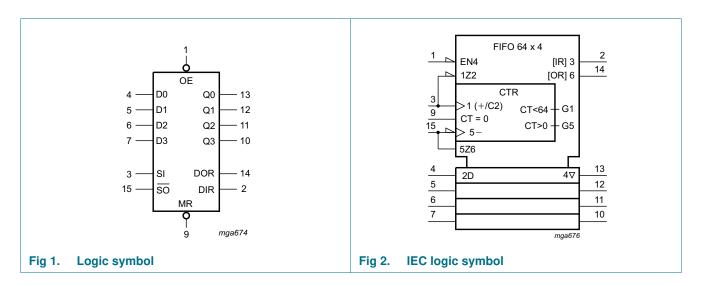

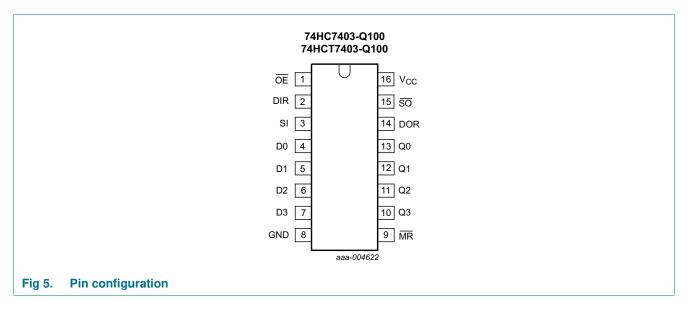

## 6. Pinning information

### 6.1 Pinning

### 6.2 Pin description

| Table 2.        | Pin description |                                              |

|-----------------|-----------------|----------------------------------------------|

| Symbol          | Pin             | Description                                  |

| OE              | 1               | output enable input (active LOW)             |

| DIR             | 2               | data-in-ready output                         |

| SI              | 3               | shift-in input (active HIGH)                 |

| D0 to D3        | 4, 5, 6, 7      | parallel data input                          |

| GND             | 8               | ground (0 V)                                 |

| MR              | 9               | asynchronous master-reset input (active LOW) |

| Q0 to Q3        | 13, 12, 11, 10  | data output                                  |

| DOR             | 14              | data-out-ready output                        |

| SO              | 15              | shift-out input (active LOW)                 |

| V <sub>CC</sub> | 16              | supply voltage                               |

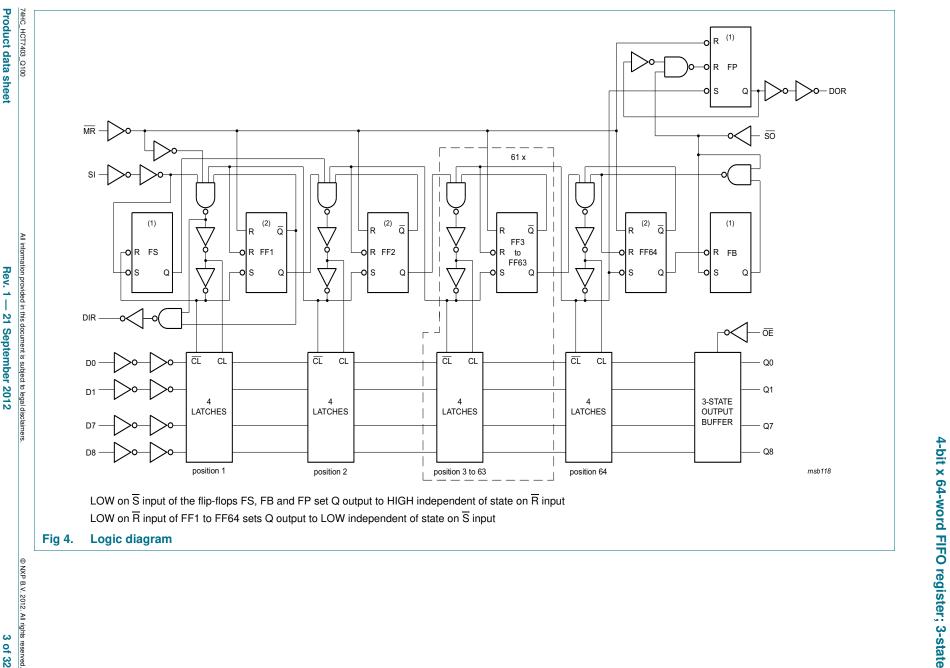

## 7. Functional description

A DIR flag indicates the input stage status, either empty and ready to receive data (DIR = HIGH) or full and busy (DIR = LOW). When DIR and SI are HIGH, data present at D0 to D3 is shifted into the input stage; once complete DIR goes LOW. When SI is set LOW, data is automatically shifted to the output stage or to the last empty location. DIR set HIGH indicates a FIFO which can receive data.

4-bit x 64-word FIFO register; 3-state

A DOR flag indicates the output stage status, either data available (DOR = HIGH) or busy (DOR = LOW). When  $\overline{SO}$  and DOR are HIGH, data is available at the outputs (Q0 to Q3). When  $\overline{SO}$  is set LOW new data may be shifted into the output stage, once complete DOR is set HIGH.

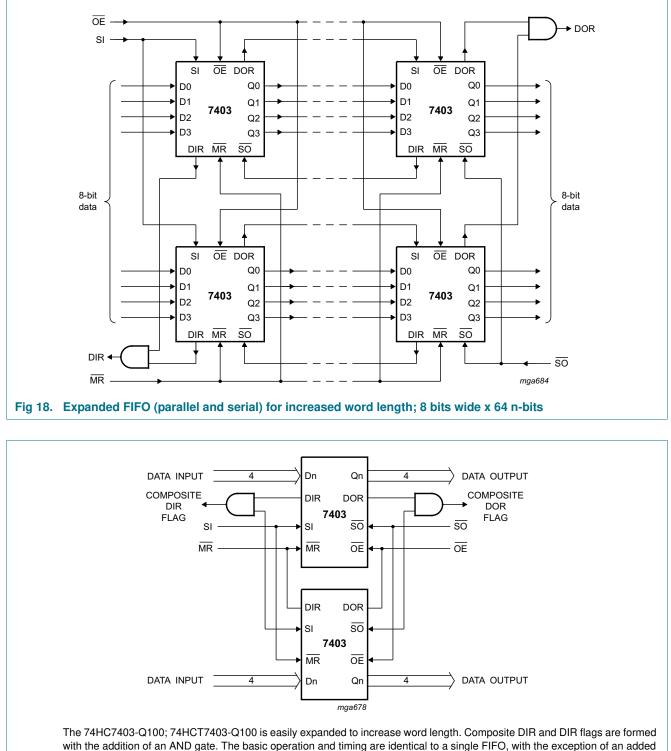

### 7.1 Expanded format

The DOR and DIR signals are used to allow the 74HC7403-Q100; 74HCT7403-Q100 to be cascaded. Both parallel and serial expansion is possible. (see Figure 18).

Serial expansion is only possible with typical devices.

### 7.1.1 Parallel expension

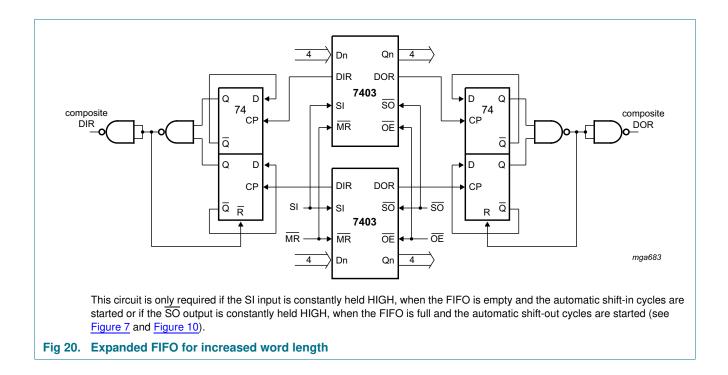

Parallel expension is accomplished by logically ANDing the DOR and DIR signals to form a composite signal.

### 7.1.2 Serial expension

Parallel expension is accomplished by:

- Tying the data outputs of the first device to the data inputs of the second device.

- Connecting the DOR pin of the first device to the SI pin of the second device.

- Connecting the SO pin of the first device to the DIR pin of the second device.

### 8. Limiting values

### Table 3.Limiting values

In accordance with the Absolute Maximum Rating System (IEC 60134). Voltages are referenced to GND (ground = 0 V).

| Symbol           | Parameter               | Conditions                                   | Min          | Max  | Unit |

|------------------|-------------------------|----------------------------------------------|--------------|------|------|

| V <sub>CC</sub>  | supply voltage          |                                              | -0.5         | +7   | V    |

| I <sub>IK</sub>  | input clamping current  | $V_{l} < -0.5$ V or $V_{l} > V_{CC}$ + 0.5 V | -            | ±20  | mA   |

| I <sub>OK</sub>  | output clamping current | $V_O < -0.5 \ V$ or $V_O > V_{CC}$ + 0.5 $V$ | -            | ±20  | mA   |

| lo               | output current          | $V_{\rm O} = -0.5$ V to (V_{\rm CC} + 0.5 V) | -            | ±35  | mA   |

| I <sub>CC</sub>  | supply current          |                                              | -            | +70  | mA   |

| I <sub>GND</sub> | ground current          |                                              | -            | -70  | mA   |

| T <sub>stg</sub> | storage temperature     |                                              | -65          | +150 | °C   |

| P <sub>tot</sub> | total power dissipation |                                              | <u>[1]</u> - | 500  | mW   |

[1] For SO16 packages: above 70 °C the value of  $P_{tot}$  derates linearly with 8 mW/K.

4-bit x 64-word FIFO register; 3-state

## 9. Recommended operating conditions

### Table 4. Recommended operating conditions

Voltages are referenced to GND (ground = 0 V)

| Symbol                | Parameter                           | Conditions 7     | 74HC7 | 74HC7403-Q100 |                 |     | 74HCT7403-Q100 |          |      |

|-----------------------|-------------------------------------|------------------|-------|---------------|-----------------|-----|----------------|----------|------|

|                       |                                     |                  | Min   | Тур           | Max             | Min | Тур            | Max      |      |

| V <sub>CC</sub>       | supply voltage                      |                  | 2.0   | 5.0           | 6.0             | 4.5 | 5.0            | 5.5      | V    |

| VI                    | input voltage                       |                  | 0     | -             | $V_{CC}$        | 0   | -              | $V_{CC}$ | V    |

| Vo                    | output voltage                      |                  | 0     | -             | V <sub>CC</sub> | 0   | -              | $V_{CC}$ | V    |

| T <sub>amb</sub>      | ambient temperature                 |                  | -40   | +25           | +125            | -40 | +25            | +125     | °C   |

| $\Delta t / \Delta V$ | input transition rise and fall rate | $V_{CC} = 2.0 V$ | -     | -             | 625             | -   | -              | -        | ns/V |

|                       |                                     | $V_{CC} = 4.5 V$ | -     | 1.67          | 139             | -   | 1.67           | 139      | ns/V |

|                       |                                     | $V_{CC} = 6.0 V$ | -     | -             | 83              | -   | -              | -        | ns/V |

## **10. Static characteristics**

### Table 5. Static characteristics

At recommended operating conditions; voltages are referenced to GND (ground = 0 V).

| Symbol          | Parameter                   | Conditions                                       |      | 25 °C |      | –40 °C t | o +85 °C | –40 °C to | o +125 °C | Unit |

|-----------------|-----------------------------|--------------------------------------------------|------|-------|------|----------|----------|-----------|-----------|------|

|                 |                             |                                                  | Min  | Тур   | Max  | Min      | Max      | Min       | Мах       |      |

| 74HC74          | 03-Q100                     |                                                  |      |       |      |          |          |           |           |      |

| V <sub>IH</sub> | HIGH-level                  | $V_{\rm CC} = 2.0 \ V$                           | 1.5  | 1.2   | -    | 1.5      | -        | 1.5       | -         | V    |

|                 | input voltage               | $V_{CC} = 4.5 V$                                 | 3.15 | 2.4   | -    | 3.15     | -        | 3.15      | -         | V    |

|                 |                             | $V_{\rm CC} = 6.0 \ {\rm V}$                     | 4.2  | 3.2   | -    | 4.2      | -        | 4.2       | -         | V    |

| V <sub>IL</sub> | LOW-level                   | V <sub>CC</sub> = 2.0 V                          | -    | 0.8   | 0.5  | -        | 0.5      | -         | 0.5       | V    |

|                 | input voltage               | $V_{CC} = 4.5 V$                                 | -    | 2.1   | 1.35 | -        | 1.35     | -         | 1.35      | V    |

|                 |                             | $V_{\rm CC} = 6.0 \ V$                           | -    | 2.8   | 1.8  | -        | 1.8      | -         | 1.8       | V    |

| V <sub>ОН</sub> | HIGH-level                  | $V_{I} = V_{IH} \text{ or } V_{IL}$              |      |       |      |          |          |           |           |      |

|                 | output voltage              | $I_{O} = -20 \ \mu A; \ V_{CC} = 2.0 \ V$        | 1.9  | 2.0   | -    | 1.9      | -        | 1.9       | -         | V    |

|                 |                             | $I_{O} = -20 \ \mu A; \ V_{CC} = 4.5 \ V$        | 4.4  | 4.5   | -    | 4.4      | -        | 4.4       | -         | V    |

|                 |                             | $I_O$ = $-20~\mu\text{A};~V_{CC}$ = 6.0 V        | 5.9  | 6.0   | -    | 5.9      | -        | 5.9       | -         | V    |

|                 |                             | $I_{O}$ = -8 mA; $V_{CC}$ = 4.5 V                | 3.98 | 4.32  | -    | 3.84     | -        | 3.7       | -         | V    |

|                 |                             | $I_{O} = -10 \text{ mA}; V_{CC} = 6.0 \text{ V}$ | 5.48 | 5.81  | -    | 5.34     | -        | 5.2       | -         | V    |

| V <sub>OL</sub> | LOW-level                   | $V_{I} = V_{IH} \text{ or } V_{IL}$              |      |       |      |          |          |           |           |      |

|                 | output voltage              | $I_O=20~\mu\text{A};V_{CC}=2.0~V$                | -    | 0     | 0.1  | -        | 0.1      | -         | 0.1       | V    |

|                 |                             | $I_O$ = 20 $\mu A;V_{CC}$ = 4.5 V                | -    | 0     | 0.1  | -        | 0.1      | -         | 0.1       | V    |

|                 |                             | $I_O=20~\mu\text{A};V_{CC}=6.0~V$                | -    | 0     | 0.1  | -        | 0.1      | -         | 0.1       | V    |

|                 |                             | $I_{O} = 8 \text{ mA}; V_{CC} = 4.5 \text{ V}$   | -    | 0.15  | 0.26 | -        | 0.33     | -         | 0.4       | V    |

|                 |                             | $I_O = 10 \text{ mA}; V_{CC} = 6.0 \text{ V}$    | -    | 0.15  | 0.26 | -        | 0.33     | -         | 0.4       | V    |

| lı              | input leakage<br>current    | $V_I = V_{CC}$ or GND;<br>$V_{CC} = 6.0 V$       | -    | -     | ±0.1 | -        | ±1.0     | -         | ±1.0      | μA   |

| oz              | OFF-state<br>output current |                                                  | -    | -     | ±0.5 | -        | ±5.0     | -         | ±10.0     | μA   |

4-bit x 64-word FIFO register; 3-state

### Table 5. Static characteristics ...continued

At recommended operating conditions; voltages are referenced to GND (ground = 0 V).

| Symbol           | Parameter                   | Conditions                                                                                                                                                                               |      | 25 °C |      | –40 °C t | o +85 °C | –40 °C to | o +125 °C | Uni |

|------------------|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|------|----------|----------|-----------|-----------|-----|

|                  |                             |                                                                                                                                                                                          | Min  | Тур   | Max  | Min      | Max      | Min       | Max       |     |

| lcc              | supply current              |                                                                                                                                                                                          | -    | -     | 50   | -        | 500      | -         | 1000      | μA  |

| Cı               | input<br>capacitance        |                                                                                                                                                                                          | -    | 3.5   | -    |          |          |           |           | pF  |

| 74HCT7           | 403-Q100                    |                                                                                                                                                                                          |      |       |      |          |          |           |           |     |

| V <sub>IH</sub>  | HIGH-level<br>input voltage | $V_{CC}$ = 4.5 V to 5.5 V                                                                                                                                                                | 2.0  | 1.6   | -    | 2.0      | -        | 2.0       | -         | V   |

| V <sub>IL</sub>  | LOW-level<br>input voltage  | $V_{CC}$ = 4.5 V to 5.5 V                                                                                                                                                                | -    | 1.2   | 0.8  | -        | 0.8      | -         | 0.8       | V   |

| V <sub>OH</sub>  | HIGH-level                  | $V_{\text{I}}$ = $V_{\text{IH}}$ or $V_{\text{IL}};$ $V_{\text{CC}}$ = 4.5 V                                                                                                             |      |       |      |          |          |           |           |     |

|                  | output voltage              | I <sub>O</sub> = -20 μA                                                                                                                                                                  | 4.4  | 4.5   | -    | 4.4      | -        | 4.4       | -         | V   |

|                  |                             | I <sub>O</sub> = -8 mA                                                                                                                                                                   | 3.98 | 4.32  | -    | 3.84     | -        | 3.7       | -         | V   |

| V <sub>OL</sub>  | LOW-level                   | $V_{I} = V_{IH} \text{ or } V_{IL}; V_{CC} = 4.5 \text{ V}$                                                                                                                              |      |       |      |          |          |           |           |     |

|                  | output voltage              | I <sub>O</sub> = 20 μA                                                                                                                                                                   | -    | 0     | 0.1  | -        | 0.1      | -         | 0.1       | V   |

|                  |                             | l <sub>O</sub> = 8 mA                                                                                                                                                                    | -    | 0.15  | 0.26 | -        | 0.33     | -         | 0.4       | V   |

| lı               | input leakage<br>current    | $V_1 = V_{CC} \text{ or GND};$<br>$V_{CC} = 5.5 \text{ V}$                                                                                                                               | -    | -     | ±0.1 | -        | ±1.0     | -         | ±1.0      | μA  |

| l <sub>oz</sub>  | OFF-state<br>output current | $      V_I = V_{IH} \text{ or } V_{IL}; V_{CC} = 5.5 \text{ V};                                   $                                                                                      | -    | -     | ±0.5 | -        | ±5.0     | -         | ±10       | μA  |

| I <sub>CC</sub>  | supply current              | $\label{eq:VI} \begin{array}{l} V_{I} = V_{CC} \text{ or } GND; \ I_{O} = 0 \ A; \\ V_{CC} = 5.5 \ V \end{array}$                                                                        | -    | -     | 50   | -        | 500      | -         | 1000      | μA  |

| ∆l <sub>CC</sub> | additional supply current   | $\label{eq:V_l} \begin{array}{l} V_l = V_{CC} - 2.1 \ V; \\ \text{other inputs at } V_{CC} \ \text{or GND}; \\ V_{CC} = 4.5 \ V \ \text{to } 5.5 \ V; \\ I_O = 0 \ \text{A} \end{array}$ |      |       |      |          |          |           |           |     |

|                  |                             | per input pin; Dn inputs                                                                                                                                                                 | -    | 75    | 270  | -        | 338      | -         | 368       | μA  |

|                  |                             | per input pin; OE input                                                                                                                                                                  | -    | 100   | 360  | -        | 450      | -         | 490       | μA  |

|                  |                             | per input pin; SI input                                                                                                                                                                  | -    | 150   | 540  | -        | 675      | -         | 735       | μA  |

|                  |                             | per input pin; MR input                                                                                                                                                                  | -    | 150   | 540  | -        | 675      | -         | 735       | μA  |

|                  |                             | per input pin; SO input                                                                                                                                                                  | -    | 150   | 540  | -        | 675      | -         | 735       | μA  |

| CI               | input<br>capacitance        |                                                                                                                                                                                          | -    | 3.5   | -    |          |          |           |           | pF  |

4-bit x 64-word FIFO register; 3-state

## **11. Dynamic characteristics**

### Table 6. Dynamic characteristics

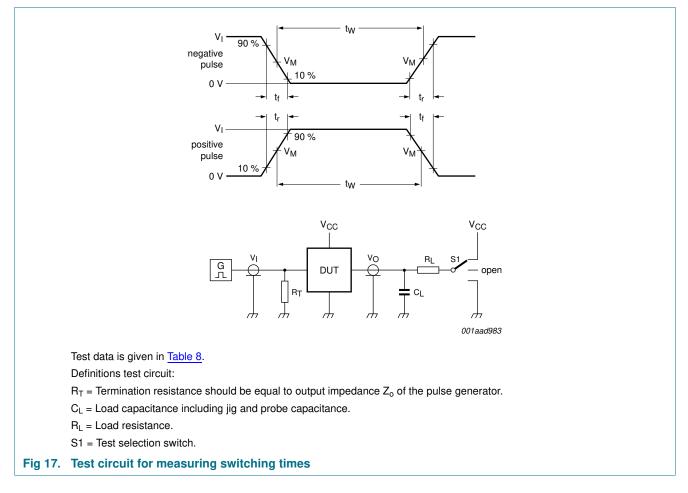

Voltages are referenced to GND (ground = 0 V);  $C_L = 50 \text{ pF}$  unless otherwise specified; for test circuit see Figure 17.

| Symbol  | Parameter            | Conditions                                            |     |     | 25 °C |     | _40 °C | to +85 °C | _40 °C 1 | to +125 °C | Uni |

|---------|----------------------|-------------------------------------------------------|-----|-----|-------|-----|--------|-----------|----------|------------|-----|

|         |                      |                                                       |     | Min | Тур   | Max | Min    | Max       | Min      | Max        |     |

| 74HC74( | 03-Q100              |                                                       |     |     |       |     |        |           |          |            |     |

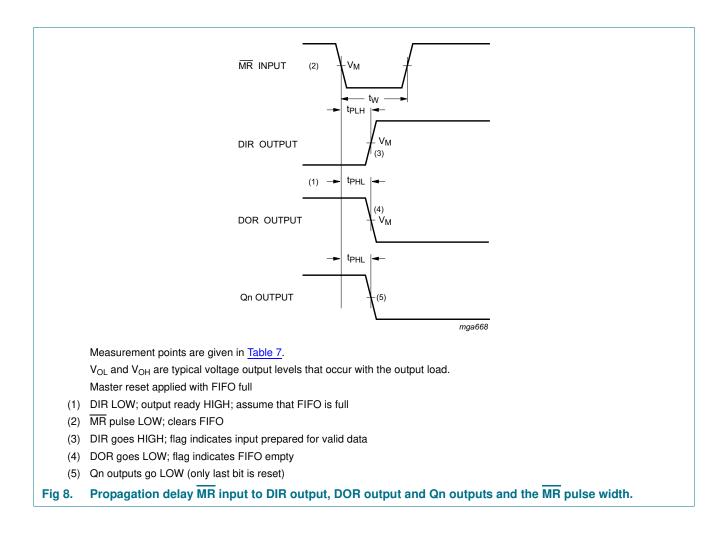

| pd      | propagation<br>delay | MR to DIR or DOR; see<br>Figure 8                     | [1] |     |       |     |        |           |          |            |     |

|         |                      | $V_{CC} = 2.0 V$                                      |     | -   | 69    | 210 | -      | 265       | -        | 315        | ns  |

|         |                      | $V_{CC} = 4.5 V$                                      |     | -   | 25    | 42  | -      | 53        | -        | 63         | ns  |

|         |                      | $V_{CC} = 6.0 V$                                      |     | -   | 20    | 36  | -      | 45        | -        | 54         | ns  |

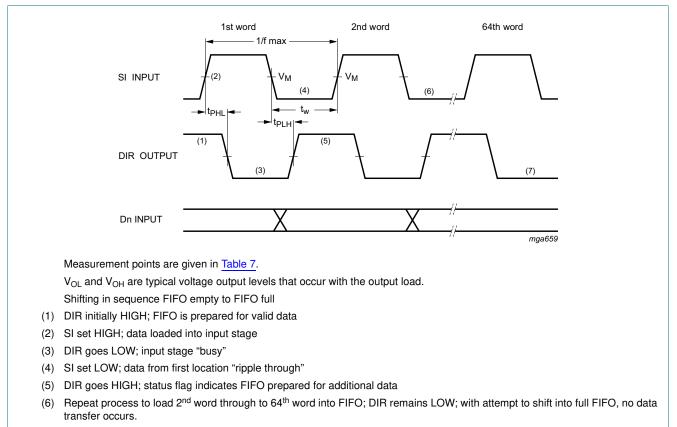

|         |                      | SI to DIR; see Figure 6                               | [1] |     |       |     |        |           |          |            |     |

|         |                      | $V_{CC} = 2.0 V$                                      |     | -   | 66    | 205 | -      | 255       | -        | 310        | ns  |

|         |                      | $V_{CC} = 4.5 V$                                      |     | -   | 24    | 41  | -      | 51        | -        | 62         | ns  |

|         |                      | $V_{CC} = 5 \text{ V}; \text{ C}_{L} = 15 \text{ pF}$ |     | -   | 15    | -   | -      | -         | -        | -          | ns  |

|         |                      | $V_{CC} = 6.0 V$                                      |     | -   | 19    | 35  | -      | 43        | -        | 53         | ns  |

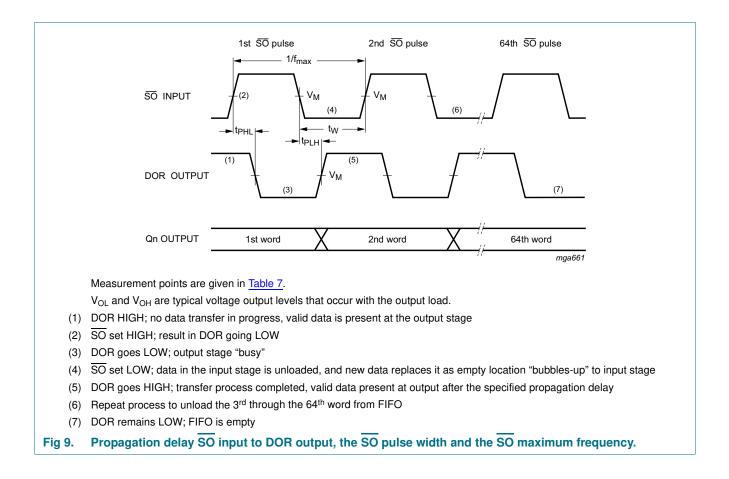

|         |                      | SO to DOR; see Figure 9                               | [1] |     |       |     |        |           |          |            |     |

|         |                      | $V_{CC} = 2.0 V$                                      |     | -   | 94    | 290 | -      | 365       | -        | 435        | ns  |

|         |                      | $V_{CC} = 4.5 V$                                      |     | -   | 34    | 58  | -      | 73        | -        | 87         | ns  |

|         |                      | V <sub>CC</sub> = 5 V; C <sub>L</sub> = 15 pF         |     | -   | 15    | -   | -      | -         | -        | -          | ns  |

|         |                      | $V_{CC} = 6.0 V$                                      |     | -   | 27    | 49  | -      | 62        | -        | 74         | ns  |

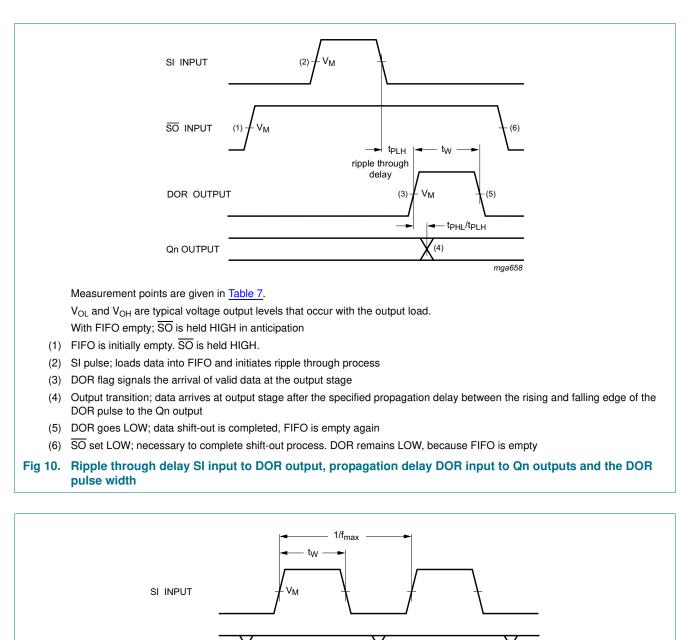

|         |                      | DOR to Qn; see Figure 10                              | [1] |     |       |     |        |           |          |            |     |

|         |                      | $V_{CC} = 2.0 V$                                      |     | -   | 11    | 35  | -      | 45        | -        | 55         | ns  |

|         |                      | $V_{CC} = 4.5 V$                                      |     | -   | 4     | 7   | -      | 9         | -        | 11         | ns  |

|         |                      | $V_{CC} = 6.0 V$                                      |     | -   | 3     | 6   | -      | 8         | -        | 9          | ns  |

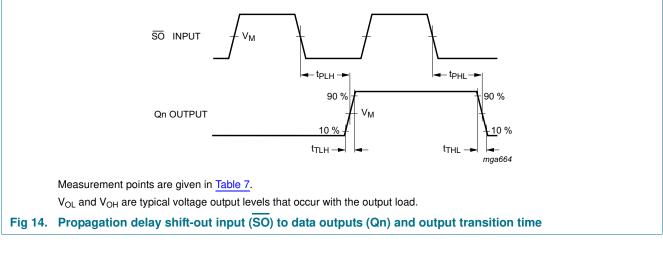

|         |                      | SO to Qn; see Figure 14                               | [1] |     |       |     |        |           |          |            |     |

|         |                      | $V_{CC} = 2.0 V$                                      |     | -   | 105   | 325 | -      | 406       | -        | 488        | ns  |

|         |                      | $V_{CC} = 4.5 V$                                      |     | -   | 38    | 65  | -      | 81        | -        | 98         | ns  |

|         |                      | $V_{CC} = 6.0 V$                                      |     | -   | 30    | 55  | -      | 69        | -        | 83         | ns  |

| PHL     | HIGH to              | MR to Qn; see Figure 8                                |     |     |       |     |        |           |          |            |     |

|         | LOW                  | $V_{CC} = 2.0 V$                                      |     | -   | 52    | 160 | -      | 200       | -        | 240        | ns  |

|         | propagation<br>delay | V <sub>CC</sub> = 4.5 V                               |     | -   | 19    | 32  | -      | 40        | -        | 48         | ns  |

|         | <b>,</b>             | $V_{CC} = 6.0 V$                                      |     | -   | 15    | 27  | -      | 34        | -        | 41         | ns  |

| PLH     | LOW to               | SI to DOR; see Figure 10                              | [5] |     |       |     |        |           |          |            |     |

|         | HIGH                 | $V_{CC} = 2.0 V$                                      |     | -   | 2.2   | 7   | -      | 8.8       | -        | 10.5       | ns  |

|         | propagation<br>delay | V <sub>CC</sub> = 4.5 V                               |     | -   | 0.8   | 1.4 | -      | 1.8       | -        | 2.1        | ns  |

|         | ,                    | $V_{CC} = 6.0 V$                                      |     | -   | 0.6   | 1.2 | -      | 1.5       | -        | 1.8        | ns  |

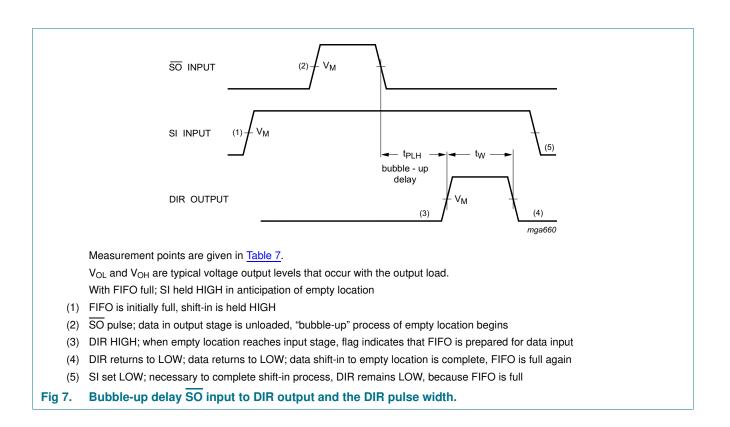

|         |                      | SO to DIR; see Figure 7                               | [6] |     |       |     |        |           |          |            |     |

|         |                      | V <sub>CC</sub> = 2.0 V                               |     | -   | 2.8   | 9   | -      | 11.2      | -        | 13.5       | ns  |

|         |                      | $V_{CC} = 4.5 V$                                      |     | -   | 1.0   | 1.8 | -      | 2.2       | -        | 2.7        | ns  |

|         |                      | $V_{CC} = 6.0 V$                                      |     | -   | 0.8   | 1.5 | -      | 1.9       | -        | 2.3        | ns  |

4-bit x 64-word FIFO register; 3-state

| Symbol | Parameter    | Conditions                             |     | 25 °C |     | –40 °C | to +85 °C | –40 °C te | o +125 °C | Uni |

|--------|--------------|----------------------------------------|-----|-------|-----|--------|-----------|-----------|-----------|-----|

|        |              |                                        | Min | Тур   | Max | Min    | Max       | Min       | Max       |     |

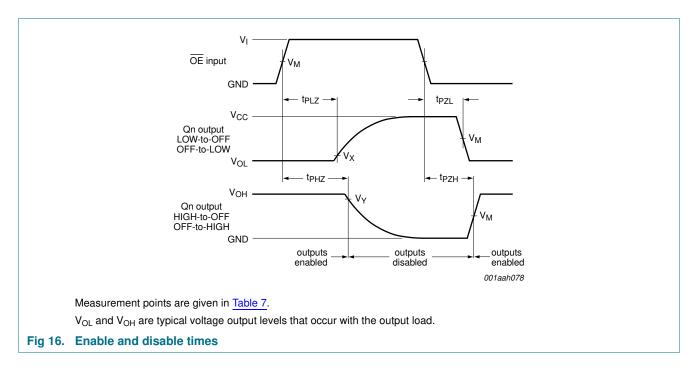

| en     | enable time  | OE to Qn; see Figure 16                | [2] |       |     |        |           |           |           |     |

|        |              | $V_{CC} = 2.0 V$                       | -   | 44    | 150 | -      | 190       | -         | 225       | ns  |

|        |              | V <sub>CC</sub> = 4.5 V                | -   | 16    | 30  | -      | 38        | -         | 45        | ns  |

|        |              | $V_{CC} = 6.0 V$                       | -   | 13    | 26  | -      | 32        | -         | 38        | ns  |

| dis    | disable time | OE to Qn; see Figure 16                | [3] |       |     |        |           |           |           |     |

|        |              | V <sub>CC</sub> = 2.0 V                | -   | 50    | 150 | -      | 190       | -         | 225       | ns  |

|        |              | V <sub>CC</sub> = 4.5 V                | -   | 18    | 30  | -      | 38        | -         | 45        | ns  |

|        |              | $V_{CC} = 6.0 V$                       | -   | 14    | 26  | -      | 33        | -         | 38        | ns  |

| t      | transition   | Qn; see Figure 14                      | [4] |       |     |        |           |           |           |     |

|        | time         | $V_{CC} = 2.0 V$                       | -   | 14    | 60  | -      | 75        | -         | 90        | ns  |

|        |              | V <sub>CC</sub> = 4.5 V                | -   | 5     | 12  | -      | 15        | -         | 18        | ns  |

|        |              | $V_{CC} = 6.0 V$                       | -   | 4     | 10  | -      | 13        | -         | 15        | ns  |

| W      | pulse width  | SI HIGH or LOW;<br>see <u>Figure 6</u> |     |       |     |        |           |           |           |     |

|        |              | $V_{CC} = 2.0 V$                       | 35  | 11    | -   | 45     | -         | 55        | -         | ns  |

|        |              | $V_{CC} = 4.5 V$                       | 7   | 4     | -   | 9      | -         | 11        | -         | ns  |

|        |              | $V_{CC} = 6.0 V$                       | 6   | 3     | -   | 8      | -         | 9         | -         | ns  |

|        |              | SO HIGH or LOW;<br>see <u>Figure 9</u> |     |       |     |        |           |           |           |     |

|        |              | $V_{CC} = 2.0 V$                       | 70  | 22    | -   | 90     | -         | 105       | -         | ns  |

|        |              | $V_{CC} = 4.5 V$                       | 14  | 8     | -   | 18     | -         | 21        | -         | ns  |

|        |              | $V_{CC} = 6.0 V$                       | 12  | 6     | -   | 15     | -         | 18        | -         | ns  |

|        |              | DIR HIGH; see Figure 7                 |     |       |     |        |           |           |           |     |

|        |              | $V_{CC} = 2.0 V$                       | 10  | 41    | 130 | 8      | 165       | 8         | 195       | ns  |

|        |              | $V_{CC} = 4.5 V$                       | 5   | 15    | 26  | 4      | 33        | 4         | 39        | ns  |

|        |              | $V_{CC} = 6.0 V$                       | 4   | 12    | 22  | 3      | 28        | 3         | 23        | ns  |

|        |              | DOR HIGH; see Figure 10                |     |       |     |        |           |           |           |     |

|        |              | $V_{CC} = 2.0 V$                       | 14  | 52    | 160 | 12     | 200       | 12        | 240       | ns  |

|        |              | $V_{CC} = 4.5 V$                       | 7   | 19    | 32  | 6      | 40        | 6         | 48        | ns  |

|        |              | $V_{CC} = 6.0 V$                       | 6   | 15    | 27  | 5      | 34        | 5         | 41        | ns  |

|        |              | MR LOW; see Figure 8                   |     |       |     |        |           |           |           |     |

|        |              | $V_{CC} = 2.0 V$                       | 120 | 39    | -   | 150    | -         | 180       | -         | ns  |

|        |              | $V_{CC} = 4.5 V$                       | 24  | 14    | -   | 30     | -         | 36        | -         | ns  |

|        |              | $V_{CC} = 6.0 V$                       | 20  | 11    | -   | 26     | -         | 31        | -         | ns  |

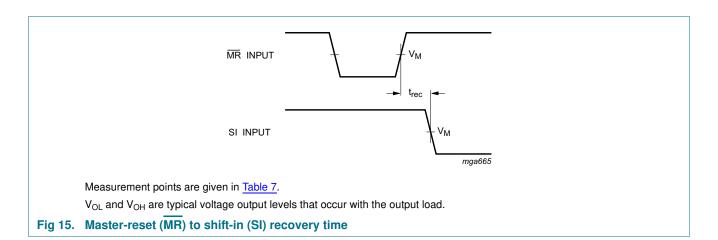

| rec    | recovery     | MR to SI; see Figure 15                |     |       |     |        |           |           |           |     |

|        | time         | V <sub>CC</sub> = 2.0 V                | 80  | 24    | -   | 100    | -         | 120       | -         | ns  |

|        |              | V <sub>CC</sub> = 4.5 V                | 16  | 8     | -   | 20     | -         | 24        | -         | ns  |

|        |              | $V_{CC} = 6.0 V$                       | 14  | 7     | -   | 17     | -         | 20        | -         | ns  |

#### Table 6. Dynamic characteristics ... continued

4-bit x 64-word FIFO register; 3-state

| Symbol | Parameter            | Conditions                                                             |              | 25 °C |     | _40 °C | to +85 °C | –40 °C 1 | o +125 °C | Uni |

|--------|----------------------|------------------------------------------------------------------------|--------------|-------|-----|--------|-----------|----------|-----------|-----|

|        |                      |                                                                        | Min          | Тур   | Max | Min    | Max       | Min      | Max       |     |

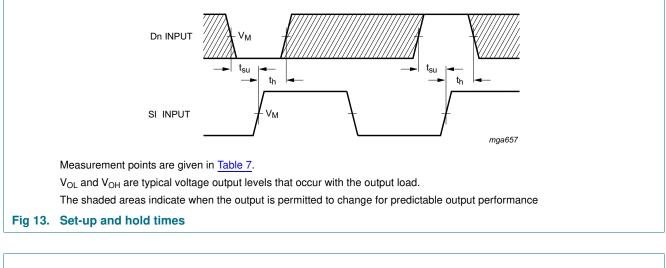

| su     | set-up time          | Dn to SI; see Figure 13                                                |              |       | •   |        |           |          |           |     |

|        |                      | $V_{CC} = 2.0 V$                                                       | -8           | -36   | -   | -6     | -         | -6       | -         | ns  |

|        |                      | $V_{CC} = 4.5 V$                                                       | -4           | -13   | -   | -3     | -         | -3       | -         | ns  |

|        |                      | $V_{CC} = 6.0 V$                                                       | -3           | -10   | -   | -3     | -         | -3       | -         | ns  |

| h      | hold time            | Dn to SI; see Figure 13                                                |              |       |     |        |           |          |           |     |

|        |                      | $V_{CC} = 2.0 V$                                                       | 135          | 44    | -   | 170    | -         | 205      | -         | ns  |

|        |                      | $V_{CC} = 4.5 V$                                                       | 27           | 16    | -   | 34     | -         | 12       | -         | ns  |

|        |                      | $V_{CC} = 6.0 V$                                                       | 5            | 13    | -   | 29     | -         | 14       | -         | ns  |

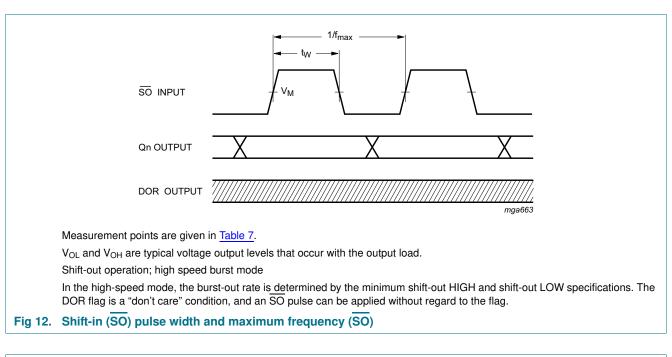

| max    | maximum<br>frequency | SI, <u>SO</u> burst mode; see<br><u>Figure 11</u> and <u>Figure 12</u> |              |       |     |        |           |          |           |     |

|        |                      | $V_{CC} = 2.0 V$                                                       | 3.6          | 9.9   | -   | 2.8    | -         | 2.4      | -         | MH  |

|        |                      | $V_{CC} = 4.5 V$                                                       | 18           | 30    | -   | 14     | -         | 12       | -         | MH  |

|        |                      | $V_{CC} = 5 \text{ V}; \text{ C}_{L} = 15 \text{ pF}$                  | -            | 30    | -   | -      | -         | -        | -         | MH  |

|        |                      | $V_{CC} = 6.0 V$                                                       | 21           | 36    | -   | 16     | -         | 14       | -         | MH  |

|        |                      | SI, <u>SO</u> using flags; see<br><u>Figure 6</u> and <u>Figure 9</u>  |              |       |     |        |           |          |           |     |

|        |                      | $V_{CC} = 2.0 V$                                                       | 3.6          | 9.9   | -   | 2.8    | -         | 2.4      | -         | MH  |

|        |                      | $V_{CC} = 4.5 V$                                                       | 18           | 30    | -   | 14     | -         | 12       | -         | MH  |

|        |                      | $V_{CC} = 5 \text{ V}; \text{ C}_{L} = 15 \text{ pF}$                  | -            | 30    | -   | -      | -         | -        | -         | MH  |

|        |                      | $V_{CC} = 6.0 V$                                                       | 21           | 36    | -   | 16     | -         | 14       | -         | MH  |

|        |                      | SI, SO cascaded; see<br>Figure 6 and Figure 9                          |              |       |     |        |           |          |           |     |

|        |                      | $V_{CC} = 2.0 V$                                                       | -            | 7.6   | -   | -      | -         | -        | -         | MH  |

|        |                      | $V_{CC} = 4.5 V$                                                       | -            | 23    | -   | -      | -         | -        | -         | MH  |

|        |                      | $V_{CC} = 6.0 V$                                                       | -            | 27    | -   | -      | -         | -        | -         | MH  |

| PD     | power<br>dissipation | $V_{I} = GND$ to $V_{CC}$                                              | <u>[7]</u> - | 475   | -   | -      | -         | -        | -         | pF  |

#### Table 6. Dynamic characteristics ... continued

4-bit x 64-word FIFO register; 3-state

| Symbol           | Parameter                   | Conditions                                            |            |     | 25 °C |     | –40 °C t | to +85 °C | –40 °C to | o +125 °C | Unit |

|------------------|-----------------------------|-------------------------------------------------------|------------|-----|-------|-----|----------|-----------|-----------|-----------|------|

|                  |                             |                                                       |            | Min | Тур   | Max | Min      | Max       | Min       | Max       |      |

| 74HCT74          | 403-Q100                    |                                                       |            |     |       |     |          |           |           |           |      |

| t <sub>pd</sub>  | propagation<br>delay        | MR to DIR or DOR; see<br>Figure 8                     | [1]        |     |       |     |          |           |           |           |      |

|                  |                             | $V_{CC} = 4.5 V$                                      |            | -   | 30    | 51  | -        | 53        | -         | 63        | ns   |

|                  |                             | SI to DIR; see Figure 6                               | <u>[1]</u> |     |       |     |          |           |           |           |      |

|                  |                             | $V_{CC} = 4.5 V$                                      |            | -   | 25    | 43  | -        | 54        | -         | 65        | ns   |

|                  |                             | V <sub>CC</sub> = 5 V; C <sub>L</sub> = 15 pF         |            | -   | 17    | -   | -        | -         | -         | -         | ns   |

|                  |                             | SO to DOR; see Figure 9                               | <u>[1]</u> |     |       |     |          |           |           |           |      |

|                  |                             | $V_{CC} = 4.5 V$                                      |            | -   | 36    | 61  | -        | 76        | -         | 92        | ns   |

|                  |                             | $V_{CC} = 5 \text{ V}; \text{ C}_{L} = 15 \text{ pF}$ |            | -   | 17    | -   | -        | -         | -         | -         | ns   |

|                  |                             | DOR to Qn; see Figure 10                              | [1]        |     |       |     |          |           |           |           |      |

|                  |                             | $V_{CC} = 4.5 V$                                      |            | -   | 7     | 12  | -        | 15        | -         | 18        | ns   |

|                  |                             | SO to Qn; see Figure 14                               | [1]        |     |       |     |          |           |           |           |      |

|                  |                             | V <sub>CC</sub> = 4.5 V                               |            | -   | 42    | 72  | -        | 90        | -         | 108       | ns   |

| t <sub>PHL</sub> | HIGH to                     | MR to Qn; see Figure 8                                |            |     |       |     |          |           |           |           |      |

|                  | LOW<br>propagation<br>delay | V <sub>CC</sub> = 4.5 V                               |            | -   | 22    | 38  | -        | 48        | -         | 57        | ns   |

| H                | LOW to                      | SI to DOR; see Figure 10                              | [5]        |     |       |     |          |           |           |           |      |

|                  | HIGH propagation            | $V_{CC} = 4.5 V$                                      |            | -   | 0.8   | 1.4 | -        | 1.75      | -         | 2.1       | ns   |

|                  | delay                       | SO to DIR; see Figure 7                               | [6]        |     |       |     |          |           |           |           |      |

|                  | ,                           | $V_{CC} = 4.5 V$                                      |            | -   | 1.0   | 1.8 | -        | 2.25      | -         | 2.7       | ns   |

| t <sub>en</sub>  | enable time                 | OE to Qn; see Figure 16                               | [2]        |     |       |     |          |           |           |           |      |

|                  |                             | $V_{CC} = 4.5 V$                                      |            | -   | 16    | 30  | -        | 38        | -         | 45        | ns   |

| t <sub>dis</sub> | disable time                | OE to Qn; see Figure 16                               | [3]        |     |       |     |          |           |           |           |      |

|                  |                             | $V_{CC} = 4.5 V$                                      |            | -   | 19    | 30  | -        | 38        | -         | 45        | ns   |

| t <sub>t</sub>   | transition                  | Qn; see Figure 14                                     | [4]        |     |       |     |          |           |           |           |      |

|                  | time                        | $V_{CC} = 4.5 V$                                      |            | -   | 5     | 12  | -        | 15        | -         | 18        | ns   |

| t <sub>W</sub>   | pulse width                 | SI HIGH or LOW;<br>see <u>Figure 6</u>                |            |     |       |     |          |           |           |           |      |

|                  |                             | $V_{CC} = 4.5 V$                                      |            | 9   | 5     | -   | 6        | -         | 8         | -         | ns   |

|                  |                             | SO HIGH or LOW;<br>see Figure 9                       |            |     |       |     |          |           |           |           |      |

|                  |                             | $V_{CC} = 4.5 V$                                      |            | 14  | 8     | -   | 18       | -         | 21        | -         | ns   |

|                  |                             | DIR HIGH; see Figure 7                                |            |     |       |     |          |           |           |           |      |

|                  |                             | V <sub>CC</sub> = 4.5 V                               |            | 5   | 17    | 29  | 4        | 36        | 4         | 44        | ns   |

|                  |                             | DOR HIGH; see Figure 10                               |            |     |       |     |          |           |           |           |      |

|                  |                             | V <sub>CC</sub> = 4.5 V                               |            | 7   | 21    | 36  | 6        | 45        | 6         | 54        | ns   |

|                  |                             | MR LOW; see Figure 8                                  |            |     |       |     |          |           |           |           |      |

|                  |                             | $V_{CC} = 4.5 V$                                      |            | 26  | 15    | -   | 33       | -         | 39        | -         | ns   |

Table 6.

Dynamic characteristics ... continued

4-bit x 64-word FIFO register; 3-state

| Symbol                                | Parameter                                                              | Conditions                                                            |              | 25 °C |     | –40 °C | to +85 °C | –40 °C t | o +125 °C | Unit |

|---------------------------------------|------------------------------------------------------------------------|-----------------------------------------------------------------------|--------------|-------|-----|--------|-----------|----------|-----------|------|

|                                       |                                                                        |                                                                       | Min          | Тур   | Max | Min    | Max       | Min      | Max       |      |

| t <sub>rec</sub>                      | recovery                                                               | MR to SI; see Figure 15                                               |              |       |     |        |           |          |           |      |

|                                       | time                                                                   | $V_{CC} = 4.5 V$                                                      | 18           | 10    | -   | 23     | -         | 27       | -         | ns   |

| t <sub>su</sub>                       | set-up time                                                            | Dn to SI; see Figure 13                                               |              |       |     |        |           |          |           |      |

|                                       |                                                                        | $V_{CC} = 4.5 V$                                                      | -5           | -16   | -   | -4     | -         | -4       | -         | ns   |

| t <sub>h</sub>                        | hold time                                                              | Dn to SI; see Figure 13                                               |              |       |     |        |           |          |           |      |

|                                       |                                                                        | $V_{CC} = 4.5 V$                                                      | 30           | 18    | -   | 38     | -         | 45       | -         | ns   |

| f <sub>max</sub> maximum<br>frequency | SI, <u>SO</u> burst mode; see<br><u>Figure 11</u> and <u>Figure 12</u> |                                                                       |              |       |     |        |           |          |           |      |

|                                       |                                                                        | $V_{CC} = 4.5 V$                                                      | 18           | 30    | -   | 14     | -         | 12       | -         | MHz  |

|                                       |                                                                        | $V_{CC} = 5 \text{ V}; \text{ C}_{L} = 15 \text{ pF}$                 | -            | 30    | -   | -      | -         | -        | -         | MHz  |

|                                       |                                                                        | SI, <u>SO</u> using flags; see<br><u>Figure 6</u> and <u>Figure 9</u> |              |       |     |        |           |          |           |      |

|                                       |                                                                        | $V_{CC} = 4.5 V$                                                      | 18           | 30    | -   | 14     | -         | 12       | -         | MHz  |

|                                       |                                                                        | $V_{CC} = 5 \text{ V}; \text{ C}_{L} = 15 \text{ pF}$                 | -            | 30    | -   | -      | -         | -        | -         | MHz  |

|                                       |                                                                        | SI, SO cascaded; see<br>Figure 6 and Figure 9                         |              |       |     |        |           |          |           |      |

|                                       |                                                                        | $V_{CC} = 4.5 V$                                                      | -            | 23    | -   | -      | -         | -        | -         | MHz  |

| C <sub>PD</sub>                       | power<br>dissipation<br>capacitance                                    | $V_I = GND$ to $V_{CC} - 1.5$ V                                       | <u>[7]</u> - | 490   | -   | -      | -         | -        | -         | pF   |

## Table 6. Dynamic characteristics ...continued

Voltages are referenced to GND (ground = 0 V);  $C_L = 50 \text{ pF}$  unless otherwise specified; for test circuit see Figure 17

[1]  $t_{pd}$  is the same as  $t_{PLH}$  and  $t_{PHL}$ .

[2]  $t_{en}$  is the same as  $t_{PZH}$  and  $t_{PZL}$ .

[3]  $t_{dis}$  is the same as  $t_{PLZ}$  and  $t_{PHZ}$ .

[4]  $t_t$  is the same as  $t_{THL}$  and  $t_{TLH}$ .

[5] This is the ripple through delay.

[6] This is the bubble-up delay.

[7]  $C_{PD}$  is used to determine the dynamic power dissipation ( $P_D$  in  $\mu W$ ).

$P_D = C_{PD} \times V_{CC}^2 \times f_i \times N + \sum (C_L \times V_{CC}^2 \times f_o)$  where:

f<sub>i</sub> = input frequency in MHz;

$f_0 = output frequency in MHz;$

$C_L$  = output load capacitance in pF;

V<sub>CC</sub> = supply voltage in V;

N = number of inputs switching;

$\Sigma(C_L \times V_{CC}^2 \times f_o)$  = sum of outputs.

4-bit x 64-word FIFO register; 3-state

## 12. Waveforms

Fig 6. Propagation delay SI input to DIR output, the SI pulse width and the SI maximum frequency

4-bit x 64-word FIFO register; 3-state

74HC\_HCT7403\_Q100

14 of 32

4-bit x 64-word FIFO register; 3-state

4-bit x 64-word FIFO register; 3-state

4-bit x 64-word FIFO register; 3-state

Dn INPUT

DIR OUTPUT

Measurement points are given in Table 7.

$V_{OL}$  and  $V_{OH}$  are typical voltage output levels that occur with the output load.

Shift-in operation; high speed burst mode

In the high-speed mode, the burst-in rate is determined by the minimum shift-in HIGH and shift-in LOW specifications. The DIR status flag is a "don't care" condition, and a shift-in pulse can be applied regardless of the flag. An SI pulse which would overflow the storage capacity of the FIFO is ignored.

### Fig 11. Shift-in (SI) pulse width and maximum frequency (SI)

74HC\_HCT7403\_Q100

mga662

4-bit x 64-word FIFO register; 3-state

4-bit x 64-word FIFO register; 3-state

### Table 7. Measurement points

| Туре           | Input              | Output             |                    |                    |  |  |  |  |

|----------------|--------------------|--------------------|--------------------|--------------------|--|--|--|--|

|                | V <sub>M</sub>     | V <sub>M</sub>     | V <sub>X</sub>     | V <sub>Y</sub>     |  |  |  |  |

| 74HC7403-Q100  | 0.5V <sub>CC</sub> | 0.5V <sub>CC</sub> | 0.1V <sub>CC</sub> | 0.9V <sub>CC</sub> |  |  |  |  |

| 74HCT7403-Q100 | 1.3 V              | 1.3 V              | 0.1V <sub>CC</sub> | 0.9V <sub>CC</sub> |  |  |  |  |

### **NXP Semiconductors**

## 74HC7403-Q100; 74HCT7403-Q100

### 4-bit x 64-word FIFO register; 3-state

### Table 8. Test data

| Туре           | Input           |                                 | Load         |      | S1 position                         |                                     |                                     |

|----------------|-----------------|---------------------------------|--------------|------|-------------------------------------|-------------------------------------|-------------------------------------|

|                | VI              | t <sub>r</sub> , t <sub>f</sub> | CL           | RL   | t <sub>PHL</sub> , t <sub>PLH</sub> | t <sub>PZH</sub> , t <sub>PHZ</sub> | t <sub>PZL</sub> , t <sub>PLZ</sub> |

| 74HC7403-Q100  | V <sub>CC</sub> | 6 ns                            | 15 pF, 50 pF | 1 kΩ | open                                | GND                                 | V <sub>CC</sub>                     |

| 74HCT7403-Q100 | 3 V             | 6 ns                            | 15 pF, 50 pF | 1 kΩ | open                                | GND                                 | V <sub>CC</sub>                     |

4-bit x 64-word FIFO register; 3-state

## **13. Application information**

gate delay on the flags.

Fig 19. Expanded FIFO for increased word length; 64 words x 10 bits

4-bit x 64-word FIFO register; 3-state

4-bit x 64-word FIFO register; 3-state

### 13.1 Expanded format

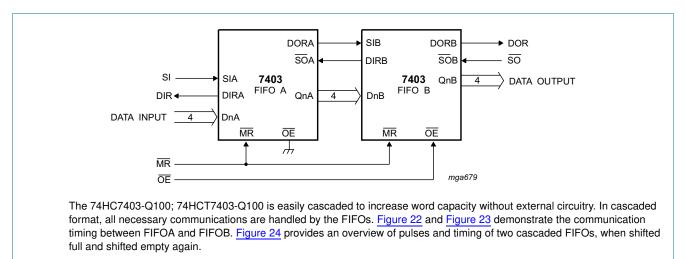

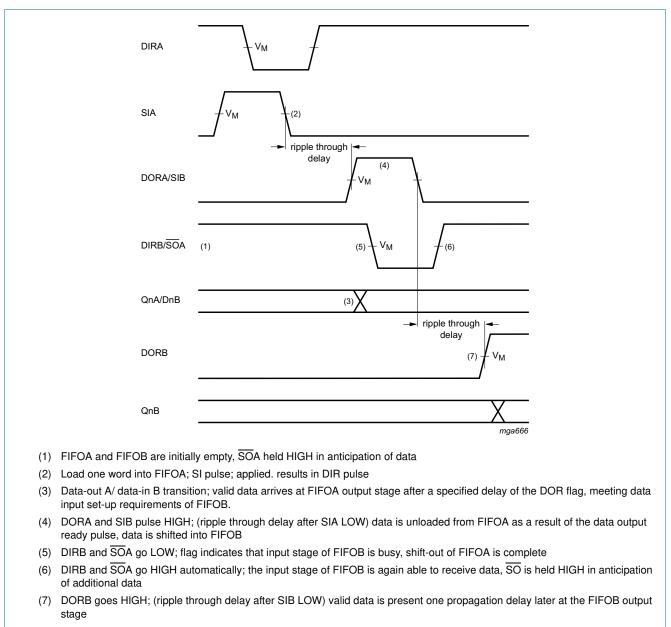

Figure 21 shows two cascaded FIFOs providing a capacity of 128 words x 4 bits. Figure 22 shows the signals on the nodes of both FIFOs after the application of the SI pulse, when both FIFOs are initially empty. After a ripple through delay, data arrives at the output of FIFOA. Due to SOA being HIGH, a DORA pulse is generated. The requirements od SIB and DnB are satisfied by the DORA pulse width and the timing between the rising edge of DORA and QnA. After a second ripple through delay data arrives at the output of FIFOB.

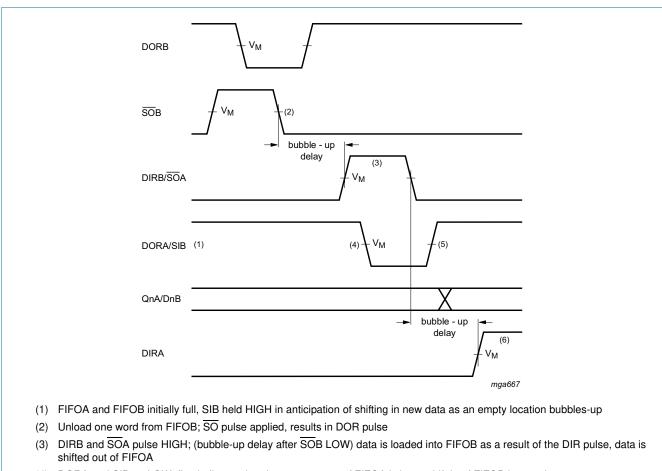

Figure 23 shows the signals on the nodes of both FIFOs after the application of the SOB pulse, when both FIFOs are initially full. After a bubble-up delay, a DIRB pulse is generated, which acts as a SOA pulse for FIFOA. One word is transferred from the output of FIFOA to the input of FIFOB. The requirements of the SOA pulse for FIFOA is satisfied by the pulse width of DORB. After a second bubble-up delay an empty space arrives at DnA, at which time DIRA goes HIGH. Figure 24 shows the waveforms at all external nodes of both FIFOs during a complete shift-in and shift-out sequence.

Fig 21. Cascading for increased word capacity; 128 words x 4 bits

### **NXP Semiconductors**

## 74HC7403-Q100; 74HCT7403-Q100

4-bit x 64-word FIFO register; 3-state

Fig 22. FIFO to FIFO communication; input timing under empty condition

### **NXP Semiconductors**

## 74HC7403-Q100; 74HCT7403-Q100

4-bit x 64-word FIFO register; 3-state

- (4) DORA and SIB go LOW; flag indicates that the output stage of FIFOA is busy, shift-in of FIFOB is complete

- (5) DORA and SIB go HIGH; flag indicates that valid data is again available at FIFOA output stage, SIB is held HIGH, awaiting bubble-up of empty location.

- (6) DIRA goes HIGH; (bubble-up delay after SOA LOW) an empty location is present at input stage of FIFOA

Fig 23. FIFO to FIFO communication; output timing under full condition