Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

#### **FEATURES**

- MityDSP-L138 Family Debug Adapter

- DSP/ARM and FPGA debug interfaces

- Compatible Critical Link System on Modules

- o MityDSP-L138

- o MityDSP-L138F

- o MityARM-1808

- o MityARM-1808F

- o MityARM-1810

- o MityARM-1810F

- o MityDSP-6748F

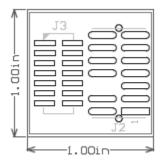

Top

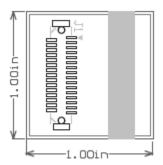

Bottom

# **DESCRIPTION**

The L138/1808/1810/6748 Debug Adapter board for the MityDSP-L138 Family of System on Modules from Critical Link allows for access to the DSP, ARM and FPGA (module dependent) debug interfaces. Each compatible System on Module includes a 31-pin Hirose connector which this adapter board connects to.

#### ABSOLUTE MAXIMUM RATINGS

#### **OPERATING CONDITIONS**

If Military/Aerospace specified cards are required, please contact the Critical Link Sales Office or unit Distributors for availability and specifications.

Ambient Temperature Range Commercial  $0^{\circ}$ C to  $70^{\circ}$ C

0 to 95%

Storage Temperature Range -40°C to 80°C

Humidity

Non-condensing

#### **DEBUG INTERFACE**

A Hirose 31 pin connector (DF9-31P-1V(32)) is provided on each compatible module to allow for the connection of this adapter board for both FPGA and OMAP-L138 processor debug. Below is the pin-out for the Hirose connector and the debug connectors on the adapter board. This adapter is available through your Critical Link representative; please see the ordering information, Table 4, below.

### **Debug Interface Connector Description (J1)**

Table 1 OMAP-L138 Hirose Connector

| Pin | I/O | Signal | Pin | I/O | Signal                  |

|-----|-----|--------|-----|-----|-------------------------|

| 1   | -   | GND    | 2   | О   | OMAP EMU1               |

| 3   | -   | GND    | 4   | О   | OMAP EMU0               |

| 5   | -   | GND    | 6   | I   | OMAP TCK                |

| 7   | -   | GND    | 8   | О   | OMAP RTCK               |

| 9   | -   | GND    | 10  | О   | OMAP TDO                |

| 11  | -   | GND    | 12  | -   | OMAP VCC / 3.3V         |

| 13  | -   | GND    | 14  | I   | OMAP TDI                |

| 15  | -   | GND    | 16  | I   | OMAP TRST               |

| 17  | -   | GND    | 18  | I   | OMAP TMS                |

| 19  | -   | GND    | 20  | -   | GND                     |

| 21  | -   | GND    | 22  | О   | NC / FPGA VREF / VCCAUX |

| 23  | -   | GND    | 24  | I   | NC / FPGA TMS           |

| 25  | -   | GND    | 26  | I   | NC / FPGA TCK           |

| 27  | =   | GND    | 28  | О   | NC / FPGA TDO           |

| 29  | -   | GND    | 30  | I   | NC / FPGA TDI           |

| 31  | -   | GND    |     |     |                         |

## **Processor JTAG Interface Description (J2)**

Connection for the processor, L138/1808/1810/6748, JTAG and emulator interfaces of a compatible System on Module from Critical Link.

Table 2 OMAP-L138 JTAG Connector Pad

| Pin | I/O | Signal          | Pin | I/O | Signal    |

|-----|-----|-----------------|-----|-----|-----------|

| 1   | I   | OMAP TMS        | 2   | I   | OMAP TRST |

| 3   | I   | OMAP TDI        | 4   | -   | GND       |

| 5   | -   | OMAP VCC / 3.3V | 6   | -   | KEY       |

| 7   | О   | OMAP TDO        | 8   | -   | GND       |

| 9   | О   | OMAP RTCK       | 10  | -   | GND       |

| 11  | I   | OMAP TCK        | 12  | -   | GND       |

| 13  | О   | OMAP EMU0       | 14  | О   | OMAP EMU1 |

## FPGA JTAG Interface Description (J3)

Connection for Xilinx FPGA JTAG interface of a compatible System on Module from Critical Link.

Table 3 FPGA JTAG Connector Pad

|     |     | =      |     |     |                    |

|-----|-----|--------|-----|-----|--------------------|

| Pin | I/O | Signal | Pin | I/O | Signal             |

| 1   | -   | GND    | 2   | О   | FPGA VREF / VCCAUX |

| 3   | -   | GND    | 4   | I   | FPGA TMS           |

| 5   | -   | GND    | 6   | I   | FPGA TCK           |

| 7   | -   | GND    | 8   | О   | FPGA TDO           |

| 9   | -   | GND    | 10  | I   | FPGA TDI           |

| 11  | -   | GND    | 12  | -   | No Connect         |

| 13  | -   | GND    | 14  | -   | No Connect         |

#### ORDERING INFORMATION

The following table lists the standard debug adapter ordering information. For shipping status, availability, and lead time please contact your Critical Link representative.

**Table 4: Standard Debug Adapter Part Number**

| Part Number |           | Description                            |  |  |

|-------------|-----------|----------------------------------------|--|--|

|             | 80-000286 | L138/1808/1810/6748 JTAG Debug Adapter |  |  |

# **MECHANICAL INTERFACE**

The mechanical outline of the Debug Adapter is illustrated in Figure 1, as shown below.

Figure 1 L138/1808/1810/6748 Debug Adapter Mechanical Outline

# **REVISION HISTORY**

| Date        | Change Description |  |  |

|-------------|--------------------|--|--|

| 27-NOV-2012 | Initial revision   |  |  |

|             |                    |  |  |

|             |                    |  |  |

|             |                    |  |  |