Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

## **DATASHEET**

## **General Description**

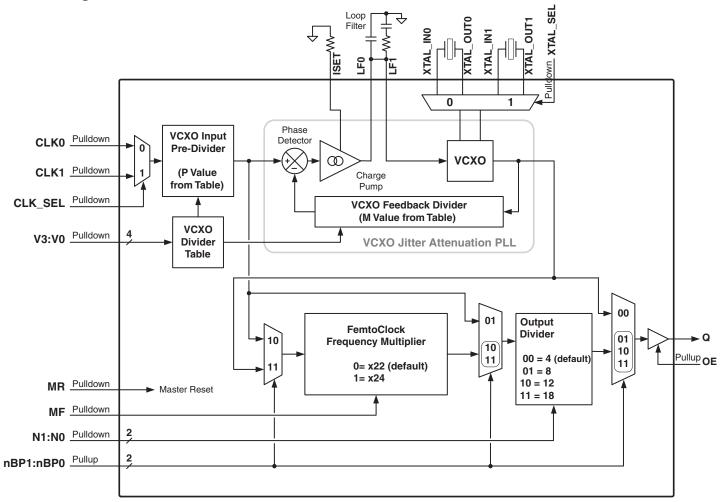

The ICS810001I-21 is a PLL based synchronous clock generator that is optimized for digital video clock jitter attenuation and frequency translation. The device contains two internal frequency multiplication stages that are cascaded in series. The first stage is a VCXO PLL that is optimized to provide reference clock jitter attenuation, and to support the complex PLL multiplication ratios needed for video rate conversion. The second stage is a FemtoClock® frequency multiplier that provides the low jitter, high frequency video output clock.

Preset multiplication ratios are selected from internal lookup tables using device input selection pins. The multiplication ratios are optimized to support most common video rates used in professional video system applications. The VCXO requires the use of an external, inexpensive pullable crystal. Two crystal connections are provided (pin selectable) so that both 60 and 59.94 base frame rates can be supported. The VCXO requires external passive loop filter components which are used to set the PLL loop bandwidth and damping characteristics.

#### **Features**

- Jitter attenuation and frequency translation of video clock signals

- Supports SMPTE 292M, ITU-R Rec. 601/656 and MPEG-transport clocks

- Support of High-Definition (HD) and Standard-Definition (SD) pixel rates

- Dual VCXO-PLL supports both 60 and 59.94Hz base frame rates in one device

- Supports both 1000/1001 and 1001/1000 rate conversions

- Dual PLL mode for high-frequency clock generation (36MHz to 148.5MHz)

- VCXO-PLL mode for low-frequency clock generation (27MHz and 26.973MHz)

- One LVCMOS/LVTTL clock output

- Two selectable LVCMOS/LVTTL clock inputs

- LVCMOS/LVTTL compatible control signals

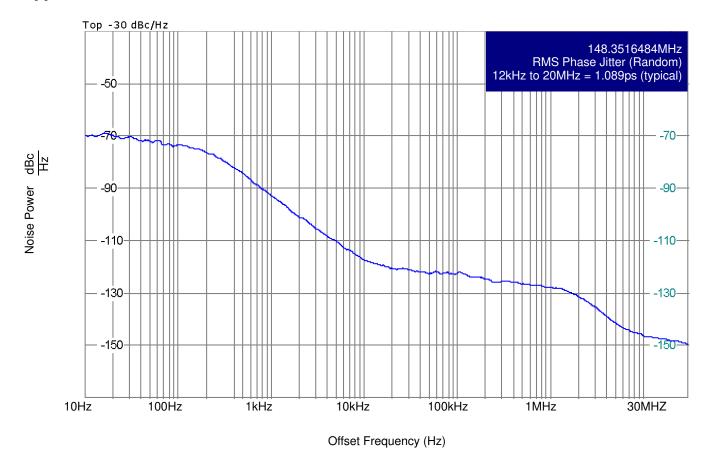

- RMS phase jitter @148.3516MHz, (12kHz 20MHz): 1.089ps (typical)

- 3.3V supply voltage

1

- -40°C to 85°C ambient operating temperature

- · Lead-free (RoHS 6) packaging

#### **Supported Input Frequencies**

| f <sub>VCXO</sub> = 27MHz | f <sub>VCXO</sub> = 26.973MHz |

|---------------------------|-------------------------------|

| 27.0000MHz                | 26.9730MHz                    |

| 27.0270MHz                | 27.0000MHz                    |

| 74.1758MHz                | 74.1016MHz                    |

| 74.3243MHz                | 74.2499MHz                    |

| 74.2500MHz                | 74.1758MHz                    |

| 27.0270MHz                | 27.0000MHz                    |

| 26.9730MHz                | 26.9461MHz                    |

| 74.1758MHz                | 74.1016kHz                    |

| 45.0000kHz                | 44.9550kHz                    |

| 33.7500kHz                | 33.7163kHz                    |

| 15.6250kHz                | 15.6094kHz                    |

| 15.7343kHz                | 15.7185kHz                    |

| 28.1250kHz                | 28.0969kHz                    |

#### **Supported Output Frequencies**

| f <sub>VCXO</sub> = 27MHz | f <sub>VCXO</sub> = 26.973MHz |

|---------------------------|-------------------------------|

| 148.5000MHz               | 148.3515MHz                   |

| 74.2500MHz                | 74.1758MHz                    |

| 49.5000MHz                | 49.4505MHz                    |

| 33.0000MHz                | 32.9670MHz                    |

| 162.0000MHz               | 161.8380MHz                   |

| 81.0000MHz                | 80.9190MHz                    |

| 54.0000MHz                | 53.9460MHz                    |

| 36.0000MHz                | 35.9640MHz                    |

| 27.0000MHz                | 26.9730MHz                    |

# **Block Diagram**

# **Pin Assignment**

ICS810001I-21

32 Lead VFQFN

5mm x 5mm x 0.925mm package body

3.15mm x 3.15mm EPad Size

K Package

Top View

# **Pin Descriptions and Characteristics**

**Table 1. Pin Descriptions**

| Number            | Name                   | Туре                   |          | Description                                                                                                                                                                                              |

|-------------------|------------------------|------------------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

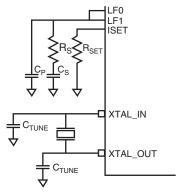

| 1, 2              | LF1, LF0               | Analog<br>Input/Output |          | Loop filter connection node pins.                                                                                                                                                                        |

| 3                 | ISET                   | Analog<br>Input/Output |          | Charge pump current setting pin.                                                                                                                                                                         |

| 4, 11, 25         | $V_{DD}$               | Power                  |          | Core supply pins.                                                                                                                                                                                        |

| 5,<br>22          | nBP0,<br>nBP1          | Input                  | Pullup   | PLL Bypass control pins. See block diagram.                                                                                                                                                              |

| 6, 20, 29         | GND                    | Power                  |          | Power supply ground.                                                                                                                                                                                     |

| 7                 | CLK_SEL                | Input                  | Pulldown | Input clock select. When HIGH selects CLK1. When LOW, selects CLK0. LVCMOS / LVTTL interface levels.                                                                                                     |

| 8, 9              | CLK1, CLK0             | Input                  | Pulldown | Single-ended clock inputs. LVCMOS/LVTTL interface levels.                                                                                                                                                |

| 10, 14,<br>15, 16 | V0, V1,<br>V2, V3      | Input                  | Pulldown | VCXO PLL divider selection pins. LVCMOS/LVTTL interface levels.                                                                                                                                          |

| 12                | MR                     | Input                  | Pulldown | Active HIGH Master Reset. When logic HIGH, the internal dividers are reset causing the output to go low. When logic LOW, the internal dividers and the output is enabled. LVCMOS/LVTTL interface levels. |

| 13                | MF                     | Input                  | Pulldown | FemtoClock multiplication factor select pin. LVCMOS/LVTTL interface levels.                                                                                                                              |

| 17                | $V_{DDA}$              | Power                  |          | Analog supply pin.                                                                                                                                                                                       |

| 18                | $V_{DDO}$              | Power                  |          | Output supply pin.                                                                                                                                                                                       |

| 19                | Q                      | Output                 |          | Single-ended VCXO PLL clock output. LVCMOS/LVTTL interface levels.                                                                                                                                       |

| 21                | OE                     | Input                  | Pullup   | Output enable. When logic LOW, the clock output is in high-impedance. When logic HIGH, the output is enabled. LVCMOS/LVTTL interface levels.                                                             |

| 23, 24            | N1, N0                 | Input                  | Pulldown | FemtoClock output divide select pins. LVCMOS/LVTTL interface levels.                                                                                                                                     |

| 26                | XTAL_SEL               | Input                  | Pulldown | Crystal select. When HIGH, selects XTAL1. When LOW, selects XTAL0. LVCMOS/LVTTL interface levels.                                                                                                        |

| 27,<br>28         | XTAL_OUT1,<br>XTAL_IN1 | Input                  |          | Crystal oscillator interface. XTAL_IN1 is the input. XTAL_OUT1 is the output.                                                                                                                            |

| 30,<br>31         | XTAL_OUT0,<br>XTAL_IN0 | Input                  |          | Crystal oscillator interface. XTAL_IN0 is the input. XTAL_OUT0 is the output.                                                                                                                            |

| 32                | $V_{DDX}$              | Power                  |          | Power supply pin for VCXO charge pump.                                                                                                                                                                   |

NOTE: Pullup and Pulldown refer to internal input resistors. See Table 2, Pin Characteristics, for typical values.

**Table 2. Pin Characteristics**

| Symbol                | Parameter                                     | Test Conditions                       | Minimum | Typical | Maximum | Units |

|-----------------------|-----------------------------------------------|---------------------------------------|---------|---------|---------|-------|

| C <sub>IN</sub>       | Input Capacitance                             |                                       |         | 4       |         | pF    |

| C <sub>PD</sub>       | Power Dissipation<br>Capacitance (per output) | $V_{DD} = V_{DDX} = V_{DDO} = 3.465V$ |         | 8.5     |         | pF    |

| R <sub>PULLUP</sub>   | Input Pullup Resistor                         |                                       |         | 51      |         | kΩ    |

| R <sub>PULLDOWN</sub> | Input Pulldown Resistor                       |                                       |         | 51      |         | kΩ    |

| R <sub>OUT</sub>      | Output Impedance                              |                                       |         | 22.5    |         | Ω     |

# **Function Tables**

Table 3A. VCXO PLL Pre- and Feedback Divider Function Table

|             | Input       |             |             | VCXO PLL C    | Configuration       |

|-------------|-------------|-------------|-------------|---------------|---------------------|

| V3          | V2          | V1          | V0          | Pre-Divider P | Feedback- Divider M |

| 0 (default) | 0 (default) | 0 (default) | 0 (default) | 1000          | 1000                |

| 0           | 0           | 0           | 1           | 1001          | 1000                |

| 0           | 0           | 1           | 0           | 11000         | 4004                |

| 0           | 0           | 1           | 1           | 11011         | 4000                |

| 0           | 1           | 0           | 0           | 11000         | 4000                |

| 0           | 1           | 0           | 1           | 4004          | 4004                |

| 0           | 1           | 1           | 0           | 4004          | 4000                |

| 0           | 1           | 1           | 1           | 1000          | 1001                |

| 1           | 0           | 0           | 0           | 250           | 91                  |

| 1           | 0           | 0           | 1           | 253           | 92                  |

| 1           | 0           | 1           | 0           | 92            | 92                  |

| 1           | 0           | 1           | 1           | 1             | 600                 |

| 1           | 1           | 0           | 0           | 1             | 800                 |

| 1           | 1           | 0           | 1           | 1             | 1728                |

| 1           | 1           | 1           | 0           | 1             | 1716                |

| 1           | 1           | 1           | 1           | 1             | 960                 |

Table 3B. Input Frequency Table

|             | In          | put         |             | Crystal Frequ | uency (f <sub>VCXO</sub> ) |

|-------------|-------------|-------------|-------------|---------------|----------------------------|

| V3          | V2          | V1          | V0          | 27MHz         | 26.973MHz                  |

| 0 (default) | 0 (default) | 0 (default) | 0 (default) | 27.0000MHz    | 26.9730MHz                 |

| 0           | 0           | 0           | 1           | 27.0270MHz    | 27.0000MHz                 |

| 0           | 0           | 1           | 0           | 74.1758MHz    | 74.1016MHz                 |

| 0           | 0           | 1           | 1           | 74.3243MHz    | 74.2499MHz                 |

| 0           | 1           | 0           | 0           | 74.2500MHz    | 74.1758MHz                 |

| 0           | 1           | 0           | 1           | 27.0000MHz    | 26.9730MHz                 |

| 0           | 1           | 1           | 0           | 27.0270MHz    | 27.0000MHz                 |

| 0           | 1           | 1           | 1           | 26.9730MHz    | 26.9461MHz                 |

| 1           | 0           | 0           | 0           | 74.1758MHz    | 74.1016MHz                 |

| 1           | 0           | 0           | 1           | 74.2500MHz    | 74.1758MHz                 |

| 1           | 0           | 1           | 0           | 27.0000MHz    | 26.9730MHz                 |

| 1           | 0           | 1           | 1           | 45.0000kHz    | 44.9550kHz                 |

| 1           | 1           | 0           | 0           | 33.7500kHz    | 33.7163kHz                 |

| 1           | 1           | 0           | 1           | 15.6250kHz    | 15.6094kHz                 |

| 1           | 1           | 1           | 0           | 15.7343kHz    | 15.7185kHz                 |

| 1           | 1           | 1           | 1           | 28.1250kHz    | 28.0969kHz                 |

Table 3C. Output Frequency Table (dual PLL Mode)

|                   | FemtoClock Look-up Table |    |    |                                       |

|-------------------|--------------------------|----|----|---------------------------------------|

| f <sub>vcxo</sub> | MF                       | N1 | N0 | Output Frequency f <sub>Q</sub> (MHz) |

|                   | 0                        | 0  | 0  | 148.5000                              |

|                   | 0                        | 0  | 1  | 74.2500                               |

|                   | 0                        | 1  | 0  | 49.5000                               |

| 27MHz             | 0                        | 1  | 1  | 33.0000                               |

| 2/IVID2           | 1                        | 0  | 0  | 162.0000                              |

|                   | 1                        | 0  | 1  | 81.0000                               |

|                   | 1                        | 1  | 0  | 54.0000                               |

|                   | 1                        | 1  | 1  | 36.0000                               |

|                   | 0                        | 0  | 0  | 148.3515                              |

|                   | 0                        | 0  | 1  | 74.1758                               |

|                   | 0                        | 1  | 0  | 49.4505                               |

| 26.973MHz         | 0                        | 1  | 1  | 32.9670                               |

| 20.973WITZ        | 1                        | 0  | 0  | 161.8380                              |

|                   | 1                        | 0  | 1  | 80.9190                               |

|                   | 1                        | 1  | 0  | 53.9460                               |

|                   | 1                        | 1  | 1  | 35.9640                               |

NOTE: Use the VCXO-PLL mode to achieve output Frequencies of 27MHz or 26.973MHz. See Table 3H.

## Table 3D. CLK\_SEL Function Table

| Input       |                                      |

|-------------|--------------------------------------|

| CLK_SEL     | Operation                            |

| 0 (default) | Selects CLK0 as PLL reference input. |

| 1           | Selects CLK1 as PLL reference input. |

#### **Table 3E. MR Master Reset Function Table**

| Input       |                                                                            |

|-------------|----------------------------------------------------------------------------|

| MR          | Operation                                                                  |

| 0 (default) | Normal operation, internal dividers and the output Q are enabled.          |

| 1           | Internal dividers are reset. Q output is in logic low state (with OE = 1). |

#### Table 3F. FemtoCLock PLL Feedback Divider Function Table

| Input       |                                                                                                         |

|-------------|---------------------------------------------------------------------------------------------------------|

| MF          | Operation                                                                                               |

| 0 (default) | Selects MF = 22. The 2nd stage PLL (FemtoClock. Multiplies the output frequency of the VCXO-PLL by 22). |

| 1           | Selects MF = 24. The 2nd stage PLL (FemtoClock. Multiplies the output frequency of the VCXO-PLL by 24). |

## Table 3G. PLL Output Divider Function Table

| Int         | out         |                        |

|-------------|-------------|------------------------|

| N1          | N0          | Operation              |

| 0 (default) | 0 (default) | Output divider N = 4.  |

| 0           | 1           | Output divider N = 8.  |

| 1           | 0           | Output divider N = 12. |

| 1           | 1           | Output divider N = 18. |

## Table 3H. PLL BYPASS Logic Function Table

| ln          | put         |                                                                                                                                                                                                                                                                       |

|-------------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| nBP1        | nBP0        | Operation                                                                                                                                                                                                                                                             |

| 0           | 0           | VCXO-PLL mode: The input reference frequency is divided by the pre-divider P and is multiplied by the VCXO-PLL. $f_{OUT} = (f_{REF} \div P) * M$ .                                                                                                                    |

| 0           | 1           | Test mode: The input reference frequency is divided by the pre-divider P and the output divider N and bypasses both PLLs. $f_{OUT} = f_{REF} \div (P * N)$ .                                                                                                          |

| 1           | 0           | FemtoClock Mode: The input reference frequency is divided by the pre-divider P multiplied by the $2^{nd}$ PLL (FemtoClock, MF). The $1^{st}$ PLL (VCXO-PLL, M) is bypassed. This mode does not support jitter attenuation. $f_{OUT} = (f_{REF} \div P) * MF \div N$ . |

| 1 (default) | 1 (default) | Dual PLL Mode: both PLLs are cascaded for jitter attenuation and frequency multiplication. $f_{OUT} = (f_{REF} \div P) * M * MF \div N.$                                                                                                                              |

# **Absolute Maximum Ratings**

NOTE: Stresses beyond those listed under *Absolute Maximum Ratings* may cause permanent damage to the device. These ratings are stress specifications only. Functional operation of product at these conditions or any conditions beyond those listed in the *DC Characteristics or AC Characteristics* is not implied. Exposure to absolute maximum rating conditions for extended periods may affect product reliability.

| Item                                        | Rating                                                   |

|---------------------------------------------|----------------------------------------------------------|

| Supply Voltage, V <sub>DD</sub>             | 4.6V                                                     |

| Inputs, V <sub>I</sub> XTAL_IN Other Inputs | 0V to V <sub>DD</sub><br>-0.5V to V <sub>DD</sub> + 0.5V |

| Outputs, V <sub>O</sub>                     | -0.5V to V <sub>DDO</sub> + 0.5V                         |

| Package Thermal Impedance, $\theta_{JA}$    | 33.1°C/W (0 mps)                                         |

| Storage Temperature, T <sub>STG</sub>       | -65°C to 150°C                                           |

### **DC Electrical Characteristics**

Table 4A. Power Supply DC Characteristics,  $V_{DD} = V_{DDX} = V_{DDO} = 3.3V \pm 5\%$ ,  $T_A = -40^{\circ}C$  to  $85^{\circ}C$

| Symbol           | Parameter                  | Test Conditions  | Minimum                | Typical | Maximum  | Units |

|------------------|----------------------------|------------------|------------------------|---------|----------|-------|

| $V_{DD}$         | Core Supply Voltage        |                  | 3.135                  | 3.3     | 3.465    | ٧     |

| $V_{DDA}$        | Analog Supply Voltage      |                  | V <sub>DD</sub> – 0.16 | 3.3     | $V_{DD}$ | ٧     |

| $V_{DDO}$        | Output Supply Voltage      |                  | 3.135                  | 3.3     | 3.465    | ٧     |

| $V_{DDX}$        | Charge Pump Supply Voltage |                  | V <sub>DD</sub> – 0.04 | 3.3     | 3.465    | ٧     |

| I <sub>DD</sub>  | Power Supply Current       |                  |                        |         | 294      | mA    |

| I <sub>DDA</sub> | Analog Supply Current      |                  |                        |         | 16       | mA    |

| I <sub>DDO</sub> | Output Supply Current      | No Load, OE = 0V |                        |         | 4        | mA    |

| I <sub>DDX</sub> | Charge Pump Supply Current |                  |                        |         | 4        | mA    |

Table 4B. LVCMOS/LVTTL DC Characteristics,  $V_{DD} = V_{DDX} = V_{DDO} = 3.3V \pm 5\%$ ,  $T_A = -40^{\circ}C$  to  $85^{\circ}C$

| Symbol          | Paramete                 | r                                                         | Test Conditions                                | Minimum | Typical | Maximum               | Units |

|-----------------|--------------------------|-----------------------------------------------------------|------------------------------------------------|---------|---------|-----------------------|-------|

| V <sub>IH</sub> | Input High               | · Voltage                                                 |                                                | 2.0     |         | V <sub>DD</sub> + 0.3 | V     |

| V <sub>IL</sub> | Input Low                | Voltage                                                   |                                                | -0.3    |         | 0.8                   | V     |

| I <sub>IH</sub> | Input<br>High<br>Current | CLK[0:1],<br>CLK_SEL, XTAL_SEL,<br>V[3:0], N[1:0], MR, MF | $V_{DD} = V_{IN} = 3.465V$                     |         |         | 150                   | μА    |

|                 | Current                  | OE, nBP0, nBP1                                            | $V_{DD} = V_{IN} = 3.465V$                     |         |         | 5                     | μΑ    |

| I <sub>IL</sub> | Input<br>Low<br>Current  | CLK[0:1],<br>CLK_SEL, XTAL_SEL,<br>V[3:0], N[1:0], MR, MF | V <sub>DD</sub> = 3.465V, V <sub>IN</sub> = 0V | -5      |         |                       | μА    |

|                 | Current                  | OE, nBP0, nBP1                                            | $V_{DD} = 3.465, V_{IN} = 0V$                  | -150    |         |                       | μΑ    |

| V <sub>OH</sub> | Output High Voltage      |                                                           | I <sub>OH</sub> = -12mA                        | 2.6     |         |                       | V     |

| V <sub>OL</sub> | Output Lo                | w Voltage                                                 | I <sub>OL</sub> = 12mA                         |         |         | 0.5                   | V     |

## **AC Electrical Characteristics**

Table 5. AC Characteristics,  $V_{DD} = V_{DDX} = V_{DDO} = 3.3V \pm 5\%$ ,  $T_A = -40$ °C to 85°C

| Symbol                            | Parameter                             | Test Conditions                                     | Minimum | Typical | Maximum | Units |

|-----------------------------------|---------------------------------------|-----------------------------------------------------|---------|---------|---------|-------|

| f <sub>OUT</sub> Output Frequency | Output Fraguency                      | nBP0, nBP1 = 00                                     | 14      |         | 35      | MHz   |

|                                   | nBP1 = 1                              | 31                                                  |         | 175     | MHz     |       |

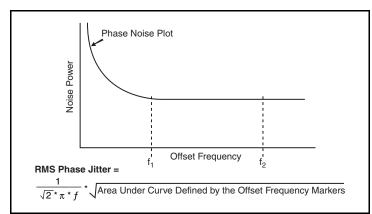

| tjit(Ø)                           | RMS Phase Jitter, (Random);<br>NOTE 1 | 148.3516MHz,<br>Integration Range:<br>12kHz – 20MHz |         | 1.089   |         | ps    |

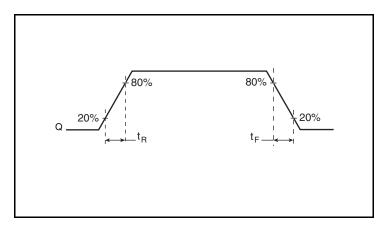

| t <sub>R</sub> / t <sub>F</sub>   | Output Rise/Fall Time                 | 20% to 80%                                          | 250     |         | 750     | ps    |

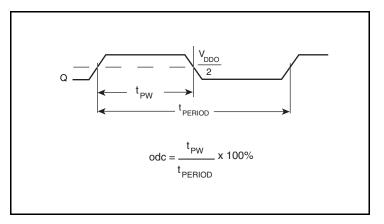

| odc                               | Output Duty Cycle                     |                                                     | 45      |         | 55      | %     |

|                                   | VCXO & FemtoClock PLL Lock            | M = 92, Bandwidth = 475Hz                           |         | 100     |         | ms    |

| <sup>t</sup> LOCK                 | Time; NOTE 2                          | M = 4004, Bandwidth = 6Hz                           |         | 25      |         | s     |

NOTE: Electrical parameters are guaranteed over the specified ambient operating temperature range, which is established when the device is mounted in a test socket with maintained transverse airflow greater than 500 lfpm. The device will meet specifications after thermal equilibrium has been reached under these conditions.

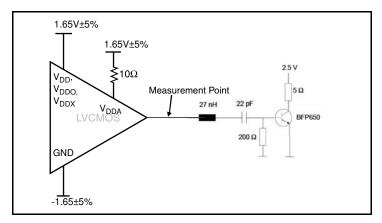

See Parameter Measurement Information Section.

NOTE 1: Refer to the Phase Noise Plot.

NOTE 2: Lock Time measured from power-up to stable output frequency.

# Typical Phase Noise at 148.3516MHz

# **Parameter Measurement Information**

3.3V Output Load AC Test Circuit

Output Duty Cycle/Pulse Width/Period

**Output Rise/Fall Time**

**Phase Jitter**

## **Applications Information**

## **Recommendations for Unused Input Pins**

### Inputs:

#### **CLK Inputs**

For applications not requiring the use of a clock input, it can be left floating. Though not required, but for additional protection, a  $1k\Omega$  resistor can be tied from the CLK input to ground.

#### **LVCMOS Control Pins**

All control pins have internal pullup or pulldown resistors; additional resistance is not required but can be added for additional protection. A  $1k\Omega$  resistor can be used.

#### **VFQFN EPAD Thermal Release Path**

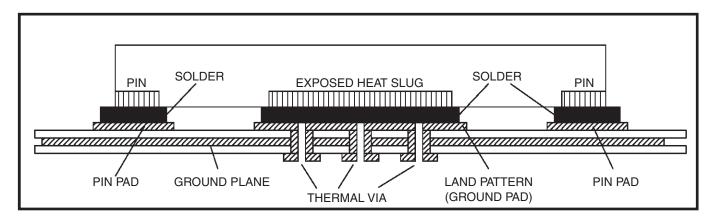

In order to maximize both the removal of heat from the package and the electrical performance, a land pattern must be incorporated on the Printed Circuit Board (PCB) within the footprint of the package corresponding to the exposed metal pad or exposed heat slug on the package, as shown in *Figure 1*. The solderable area on the PCB, as defined by the solder mask, should be at least the same size/shape as the exposed pad/slug area on the package to maximize the thermal/electrical performance. Sufficient clearance should be designed on the PCB between the outer edges of the land pattern and the inner edges of pad pattern for the leads to avoid any shorts.

While the land pattern on the PCB provides a means of heat transfer and electrical grounding from the package to the board through a solder joint, thermal vias are necessary to effectively conduct from the surface of the PCB to the ground plane(s). The land pattern must be connected to ground through these vias. The vias act as "heat pipes". The number of vias (i.e. "heat pipes") are application specific

and dependent upon the package power dissipation as well as electrical conductivity requirements. Thus, thermal and electrical analysis and/or testing are recommended to determine the minimum number needed. Maximum thermal and electrical performance is achieved when an array of vias is incorporated in the land pattern. It is recommended to use as many vias connected to ground as possible. It is also recommended that the via diameter should be 12 to 13mils (0.30 to 0.33mm) with 1oz copper via barrel plating. This is desirable to avoid any solder wicking inside the via during the soldering process which may result in voids in solder between the exposed pad/slug and the thermal land. Precautions should be taken to eliminate any solder voids between the exposed heat slug and the land pattern. Note: These recommendations are to be used as a guideline only. For further information, please refer to the Application Note on the Surface Mount Assembly of Amkor's Thermally/ Electrically Enhance Leadframe Base Package, Amkor Technology.

Figure 1. P.C. Assembly for Exposed Pad Thermal Release Path – Side View (drawing not to scale)

### Schematic Example

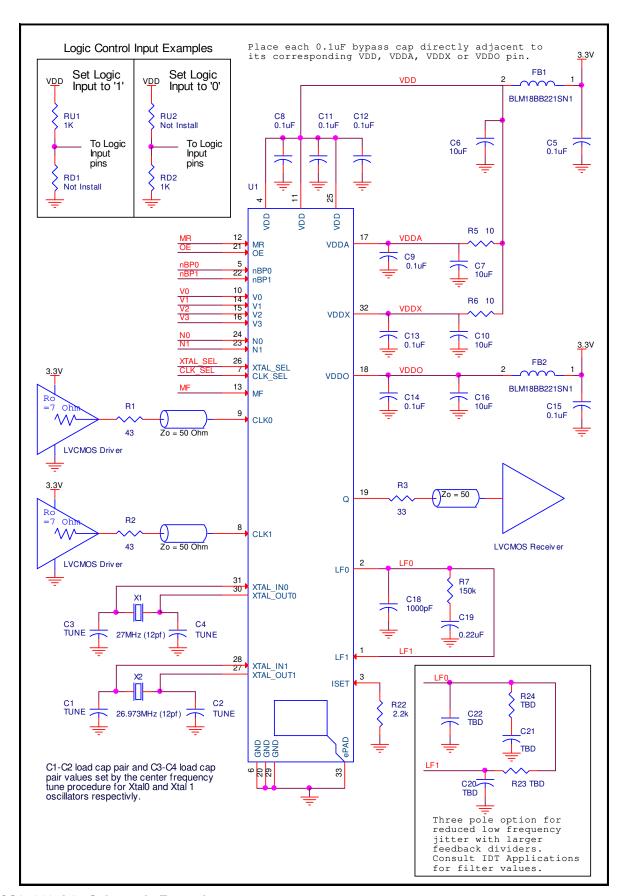

Figure 2 (next page) shows an example ICS810001I-21application schematic. This schematic example focuses on functional connections and is not configuration specific. Refer to the pin description and functional tables in the datasheet to ensure that the logic control inputs are properly set.

In this schematic, the device is operated at  $V_{DD} = V_{DDA} = V_{DDX} = V_{DDO} = 3.3V$ .

Two 12pF parallel resonant crystals can used to facilitate clock translations among common frequencies. Depending on the parasitic capacity on the crystal terminals of the printed circuit board layout, these values might require a slight adjustment to optimize the frequency accuracy. Crystals with other load capacitance specifications can be used. This will require adjusting the C1-C2 load capacitor pair to tune each oscillator's center frequency. For this device, the crystal load capacitors are required for proper operation. See the IDT application note "Crystal - Tuning VCXO" for details.

The ICS810001I-21 is packaged in a 32pin VFQFN package that incorporates an ePAD thermal spreader. The ePAD is a backside electrical contact of the package and is to be connected to the ground directly under the package. See the data sheet section "VFQFN EPAD Thermal Release Path" for details.

As with any high speed analog circuitry, the power supply pins are vulnerable to random noise. To achieve optimum jitter performance, power supply isolation is required. The ICS810001I-21provides separate power supply pins to isolate any high switching noise from coupling into the internal PLL.

In order to achieve the best possible filtering, it is recommended that the placement of the filter components be on the device side of the PCB as close to the power pins as possible. If space is limited, the  $0.1\mu F$  capacitor in each power pin filter should be placed on the device side. The other components can be on the opposite side of the PCB.

Power supply filter recommendations are a general guideline to be used for reducing external noise from coupling into the devices. The filter performance is designed for a wide range of noise frequencies. This low-pass filter starts to attenuate noise at approximately 10kHz. If a specific frequency noise component is known, such as switching power supplies frequencies, it is recommended that component values be adjusted and if required, additional filtering be added. Additionally, good general design practices for power plane voltage stability suggests adding bulk capacitance in the local area of all devices.

Figure 2. ICS810001I-21 Schematic Example

#### **VCXO-PLL EXTERNAL COMPONENTS**

Choosing the correct external components and having a proper printed circuit board (PCB) layout is a key task for quality operation of the VCXO-PLL. In choosing a crystal, special precaution must be taken with the package and load capacitance (C<sub>L</sub>). In addition, frequency, accuracy and temperature range must also be considered. Since the pulling range of a crystal also varies with the package, it is recommended that a metal-canned package like HC49 be used. Generally, a metal-canned package has a larger pulling range than a surface mounted device (SMD). For crystal selection information, refer to the *VCXO Crystal Selection Application Note*.

The crystal's load capacitance  $C_L$  characteristic determines its resonating frequency and is closely related to the VCXO tuning range. The total external capacitance seen by the crystal when installed on a board is the sum of the stray board capacitance, IC package lead capacitance, internal varactor capacitance and any installed tuning capacitors  $(C_{TUNE})$ .

If the crystal  $C_L$  is greater than the total external capacitance, the VCXO will oscillate at a higher frequency than the crystal specification. If the crystal  $C_L$  is lower than the total external capacitance, the VCXO will oscillate at a lower frequency than the crystal specification. In either case, the absolute tuning range is reduced. The correct value of  $C_L$  is dependent on the characteristics of the VCXO. The recommended  $C_L$  in the Crystal Parameter Table balances the tuning range by centering the tuning curve.

The frequency of oscillation in the third overtone mode is not necessarily at exactly three times the fundamental frequency. The mechanical properties of the quartz element dictate the position of the overtones relative to the fundamental. The oscillator circuit may excite both the fundamental and overtone modes simultaneously. This will cause a nonlinearity in the tuning curve. This potential problem is why VCXO crystals are required to be

tested for absence of any activity inside a  $\pm 200$ ppm window at three times the fundamental frequency. Refer to  $F_{L\_3OVT}$  and  $F_{L\_3OVT}$  spurs in the crystal Characteristics table.

The crystal and external loop filter components should be kept as close as possible to the device. Loop filter and crystal traces should be kept short and separated from each other. Other signal traces should be kept separate and not run underneath the device, loop filter or crystal components.

#### **VCXO Characteristics Table**

| Symbol              | Parameter                 | Typical | Units |

|---------------------|---------------------------|---------|-------|

| k <sub>VCXO</sub>   | VCXO Gain                 | 6.6     | kHz/V |

| C <sub>V_LOW</sub>  | Low Varactor Capacitance  | 15      | pF    |

| C <sub>V_HIGH</sub> | High Varactor Capacitance | 29      | pF    |

#### **VCXO-PLL Loop Bandwidth Selection Table**

| Bandwidth    | Crystal Frequency (MHz) | М    | $\mathbf{R}_{S}$ (k $\Omega$ ) | <b>C</b> <sub>S</sub> (μ <b>F</b> ) | C <sub>P</sub> (μF) | $\mathbf{R}_{SET}$ ( $\mathbf{k}\Omega$ ) |

|--------------|-------------------------|------|--------------------------------|-------------------------------------|---------------------|-------------------------------------------|

| 6Hz (Low)    | 27                      | 4004 | 175                            | 4.7                                 | 0.01                | 8.0                                       |

| 80Hz (Mid)   | 27                      | 1000 | 150                            | 0.22                                | 0.001               | 2.21                                      |

| 475Hz (High) | 27                      | 92   | 125                            | 0.1                                 | 0.0001              | 3.3                                       |

# **Crystal Characteristics**

| Symbol                          | Parameter                                     | Test Conditions | Minimum     | Typical | Maximum | Units |

|---------------------------------|-----------------------------------------------|-----------------|-------------|---------|---------|-------|

|                                 | Mode of Oscillation                           |                 | Fundamental |         |         |       |

| t                               | Fraguenay                                     |                 |             | 27      |         | MHz   |

| f <sub>N</sub>                  | Frequency                                     |                 |             | 26.973  |         | MHz   |

| f <sub>T</sub>                  | Frequency Tolerance                           |                 |             |         | ±20     | ppm   |

| f <sub>S</sub>                  | Frequency Stability                           |                 |             |         | ±20     | ppm   |

|                                 | Operating Temperature<br>Range                |                 | -40         |         | 85      | 0C    |

| C <sub>L</sub>                  | Load Capacitance                              |                 |             | 12      |         | pF    |

| C <sub>O</sub>                  | Shunt Capacitance                             |                 |             | 4       |         | pF    |

| C <sub>O</sub> / C <sub>1</sub> | Pullability Ratio                             |                 |             | 220     | 240     |       |

| F <sub>L_3OVT</sub>             | 3 <sup>RD</sup> Overtone F <sub>L</sub>       |                 | 200         |         |         | ppm   |

| F <sub>L_3OVT_spurs</sub>       | 3 <sup>RD</sup> Overtone F <sub>L</sub> Spurs |                 | 200         |         |         | ppm   |

| ESR                             | Equivalent Series Resistance                  |                 |             |         | 20      | Ω     |

|                                 | Drive Level                                   |                 |             |         | 1       | mW    |

|                                 | Aging @ 25 <sup>0</sup> C                     | First Year      |             |         | ±3      | ppm   |

|                                 | Aging @ 25 C                                  | Ten Years       |             |         | ±10     | ppm   |

### **Power Considerations**

This section provides information on power dissipation and junction temperature for the ICS810001I-21. Equations and example calculations are also provided.

#### 1. Power Dissipation.

The total power dissipation for the ICS810001I-21 is the sum of the core power plus the analog plus the power dissipation into the load. The following is the power dissipation for  $V_{DD} = 3.3V + 5\% = 3.465V$ , which gives worst case results.

- Power (core)<sub>MAX</sub> =  $3.465 * (I_{DD} + I_{DDA} + I_{DDO} + I_{DDX}) = 3.465 V * (294mA + 16mA + 4mA + 4mA) =$ **1101.87mW**

- Output Impedance  $R_{OUT}$  Power Dissipation due to Loading  $50\Omega$  to  $V_{DD}/2$  Output Current  $I_{OUT} = V_{DDO~MAX}/[2*(50\Omega + R_{OUT})] = 3.465V/[2*(50\Omega + 22.5\Omega)] = 23.9mA$

- Power Dissipation on the R<sub>OUT</sub> per LVCMOS output Power (R<sub>OUT</sub>) = R<sub>OUT</sub> \* (I<sub>OUT</sub>)<sup>2</sup> = 22.5 $\Omega$  \* (23.9mA)<sup>2</sup> = **12.9mW per output**

- Total Power (R<sub>OUT</sub>) = 12.9mW \* 1 = 12.9mW

#### **Dynamic Power Dissipation at 175MHz**

Power (175MHz) =

$$C_{PD}$$

\* Frequency \*  $(V_{DD})^2$  = 8.5pF \* 175MHz \*  $(3.465V)^2$  = **17.9mW per output** Total Power (175MHz) = 17.9mW \* 1 = **17.9mW**

#### **Total Power Dissipation**

- Total Power

- = Power (core)<sub>MAX</sub> + Power ( $R_{OUT}$ ) + Power (175MHz)

- = 1101.87 mW + 12.9 mW + 17.9 mW

- = 1133 mW

#### 2. Junction Temperature.

Junction temperature, Tj, is the temperature at the junction of the bond wire and bond pad, and directly affects the reliability of the device. The maximum recommended junction temperature is 125°C. Limiting the internal transistor junction temperature, Tj, to 125°C ensures that the bond wire and bond pad temperature remains below 125°C.

The equation for Tj is as follows: Tj =  $\theta_{JA}$  \* Pd\_total + T<sub>A</sub>

Tj = Junction Temperature

$\theta_{JA}$  = Junction-to-Ambient Thermal Resistance

Pd\_total = Total Device Power Dissipation (example calculation is in section 1 above)

T<sub>A</sub> = Ambient Temperature

In order to calculate junction temperature, the appropriate junction-to-ambient thermal resistance  $\theta_{JA}$  must be used. Assuming no air flow and a multi-layer board, the appropriate value is 33.1°C/W per Table 6 below.

Therefore, Tj for an ambient temperature of 85°C with all outputs switching is:

$$85^{\circ}\text{C} + 1.133\text{W} * 33.1^{\circ}\text{C/W} = 122.5^{\circ}\text{C}$$

. This is below the limit of  $125^{\circ}\text{C}$ .

This calculation is only an example. Tj will obviously vary depending on the number of loaded outputs, supply voltage, air flow and the type of board (single layer or multi-layer).

Table 6. Thermal Resistance  $\theta_{JA}$  for 32 Lead VFQFN, Forced Convection

| θ <sub>JA</sub> by Velocity                 |          |          |          |  |  |

|---------------------------------------------|----------|----------|----------|--|--|

| Meters per Second 0 1 3                     |          |          |          |  |  |

| Multi-Layer PCB, JEDEC Standard Test Boards | 33.1°C/W | 28.1°C/W | 25.4°C/W |  |  |

# **Reliability Information**

# Table 7. $\theta_{\text{JA}}$ vs. Air Flow Table for a 32 Lead VFQFN

| $\theta_{JA}$ vs. Air Flow                  |          |          |          |  |

|---------------------------------------------|----------|----------|----------|--|

| Meters per Second                           | 0        | 1        | 3        |  |

| Multi-Layer PCB, JEDEC Standard Test Boards | 33.1°C/W | 28.1°C/W | 25.4°C/W |  |

## **Transistor Count**

The transistor count for ICS810001I-21 is: 9365

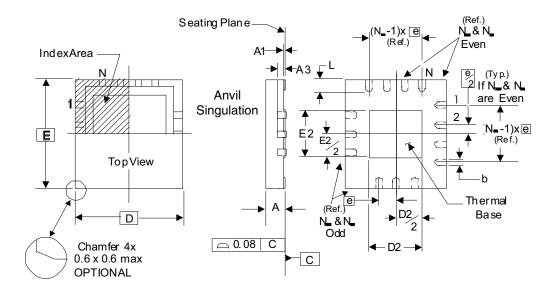

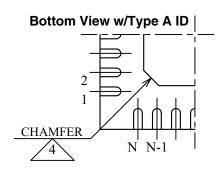

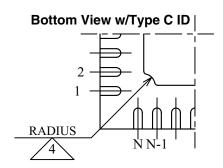

## **Package Outline and Package Dimensions**

### Package Outline - K Suffix for 32 Lead VFQFN

There are 2 methods of indicating pin 1 corner at the back of the VFQFN package:

- 1. Type A: Chamfer on the paddle (near pin 1)

- 2. Type C: Mouse bite on the paddle (near pin 1)

**Table 8. Package Dimensions**

| JEDEC Variation: VHHD-2/-4 All Dimensions in Millimeters |            |            |         |  |  |

|----------------------------------------------------------|------------|------------|---------|--|--|

| Symbol                                                   | Minimum    | Nominal    | Maximum |  |  |

| N                                                        |            | 32         |         |  |  |

| Α                                                        | 0.80       |            | 1.00    |  |  |

| A1                                                       | 0          |            | 0.05    |  |  |

| A3                                                       |            | 0.25 Ref.  |         |  |  |

| b                                                        | 0.18       | 0.25       | 0.30    |  |  |

| N <sub>D</sub> & N <sub>E</sub>                          |            |            | 8       |  |  |

| D&E                                                      |            | 5.00 Basic |         |  |  |

| D2 & E2                                                  | 3.0 3.3    |            |         |  |  |

| е                                                        | 0.50 Basic |            |         |  |  |

| L                                                        | 0.30       | 0.40       | 0.50    |  |  |

Reference Document: JEDEC Publication 95, MO-220

NOTE: The following package mechanical drawing is a generic drawing that applies to any pin count VFQFN package. This drawing is not intended to convey the actual pin count or pin layout of this device. The pin count and pinout are shown on the front page. The package dimensions are in Table 8.

# **Ordering Information**

# **Table 9. Ordering Information**

| Part/Order Number | Marking     | Package                   | Shipping Packaging | Temperature   |

|-------------------|-------------|---------------------------|--------------------|---------------|

| 810001DKI-21LF    | ICS001DI21L | "Lead-Free" 32 Lead VFQFN | Tray               | -40°C to 85°C |

| 810001DKI-21LFT   | ICS001DI21L | "Lead-Free" 32 Lead VFQFN | Tape & Reel        | -40°C to 85°C |

# We've Got Your Timing Solution

6024 Silver Creek Valley Road San Jose, California 95138 Sales

800-345-7015 (inside USA) +408-284-8200 (outside USA) Fax: 408-284-2775 www.IDT.com/go/contact IDT

cantly affect the health or safety of users. Anyone using an IDT product in such a manner does so at their own risk, absent an express, written agreement by IDT.

**Technical Support Sales**

netcom@idt.com +480-763-2056

DISCLAIMER Integrated Device Technology, Inc. (IDT) and its subsidiaries reserve the right to modify the products and/or specifications described herein at any time and at IDT's sole discretion. All information in this document, including descriptions of product features and performance, is subject to change without notice. Performance specifications and the operating parameters of the described products are determined in the independent state and are not guaranteed to perform the same way when installed in customer products. The information contained herein is provided without representation or warranty of any kind, whether express or implied, including, but not limited to, the suitability of IDT's products for any particular purpose, an implied warranty of merchantability, or non-infringement of the intellectual property rights of others. This document is presented only as a guide and does not convey any license under intellectual property rights of IDT's products for any particular purpose.

IDT's products are not intended for use in applications involving extreme environmental conditions or in life support systems or similar devices where the failure or malfunction of an IDT product can be reasonably expected to signifi-

Integrated Device Technology, IDT and the IDT logo are registered trademarks of IDT. Other trademarks and service marks used herein, including protected names, logos and designs, are the property of IDT or their respective third protected names.