Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

### Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# 16-Channel Short Haul E1 Line Interface Unit IDT82P20516

Version - December 17, 2009

6024 Silver Creek Valley Road, San Jose, California 95138

Telephone: 1-800-345-7015 or 408-284-8200• TWX: 910-338-2070 • FAX: 408-284-2775

Printed in U.S.A.

© 2009 Integrated Device Technology, Inc.

| DISCLAIMER Integrated Device Technology, Inc. reserves the right to make changes to its products or specifications at any time, without notice, in order to improve design or performance and to supply the best possible product. IDT does not assume any responsibility for use of any circuitry described other than the circuitry embodied in an IDT product. The Company makes no representations that circuitry                                                                                                                                                                                                                                                                        |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| slote product. To todes not assume any responsibility for use or any circulary described order trian the circulary enbodied in an IDT product. The Company makes no representations that circulary described herein is free from patent infringement or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent, patent rights or other rights, of Integrated Device Technology, Inc.  LIFE SUPPORT POLICY  Integrated Device Technology's products are not authorized for use as critical components in life support devices or systems unless a specific written agreement pertaining to such intended use is exe- |

| cuted between the manufacturer and an officer of IDT.  1. Life support devices or systems are devices or systems which (a) are intended for surgical implant into the body or (b) support or sustain life and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.  2. A critical component is any components of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

### **Table of Contents**

| T/ | ABLE | OF CO          | NTENTS                                                                    | 3  |

|----|------|----------------|---------------------------------------------------------------------------|----|

| LI | ST O | F TABL         | ES                                                                        | 6  |

| LI | ST O | F FIGUI        | RES                                                                       | 7  |

|    |      |                |                                                                           |    |

|    |      |                | S                                                                         |    |

|    |      |                |                                                                           |    |

|    |      |                | RAM                                                                       |    |

|    |      |                |                                                                           |    |

|    |      |                | NMENT                                                                     |    |

|    |      |                | RIPTION                                                                   |    |

| 3  |      |                | AL DESCRIPTION                                                            |    |

|    | 3.1  | E1 MO          | DE SELECTION                                                              | 19 |

|    | 3.2  | RECEI          | VE PATH                                                                   |    |

|    |      | 3.2.1          | Rx Termination                                                            |    |

|    |      |                | 3.2.1.1 Receive Differential Mode                                         |    |

|    |      | 3.2.2          | Equalizer                                                                 |    |

|    |      |                | 3.2.2.1 Line Monitor                                                      |    |

|    |      | 202            | 3.2.2.2 Receive Sensitivity                                               |    |

|    |      | 3.2.3<br>3.2.4 | SlicerRx Clock & Data Recovery                                            |    |

|    |      | 3.2.4          | Decoder                                                                   |    |

|    |      | 3.2.6          | Receive System Interface                                                  |    |

|    |      | 3.2.7          | Receiver Power Down                                                       |    |

|    | 3.3  | _              | SMIT PATH                                                                 |    |

|    |      | 3.3.1          | Transmit System Interface                                                 |    |

|    |      | 3.3.2          | Tx Clock Recovery                                                         |    |

|    |      | 3.3.3          | Encoder                                                                   | 24 |

|    |      | 3.3.4          | Waveform Shaper                                                           |    |

|    |      |                | 3.3.4.1 Preset Waveform Template                                          |    |

|    |      |                | 3.3.4.2 User-Programmable Arbitrary Waveform                              |    |

|    |      | 3.3.5          | Line Driver                                                               |    |

|    |      | 226            | 3.3.5.1 Transmit Over Current Protection                                  |    |

|    |      | 3.3.6          | Tx Termination                                                            |    |

|    |      | 3.3.7          | Transmitter Power Down                                                    |    |

|    |      | 3.3.8          | Output High-Z on TTIP and TRING                                           |    |

|    | 34   |                | R ATTENUATOR (RJA & TJA)                                                  |    |

|    |      |                | IOSTIC FACILITIES                                                         |    |

|    | 0.0  |                | Bipolar Violation (BPV) / Code Violation (CV) Detection and BPV Insertion |    |

|   |     |       | 3.5.1.1 Bipolar Violation (BPV) / Code Violation (CV) Detection |    |

|---|-----|-------|-----------------------------------------------------------------|----|

|   |     |       | 3.5.1.2 Bipolar Violation (BPV) Insertion                       |    |

|   |     | 3.5.2 | Excessive Zeroes (EXZ) Detection                                |    |

|   |     | 3.5.3 | Loss of Signal (LOS) Detection                                  |    |

|   |     |       | 3.5.3.1 Line LOS (LLOS)                                         |    |

|   |     |       | 3.5.3.2 System LOS (SLOS)                                       |    |

|   |     |       | 3.5.3.3 Transmit LOS (TLOS)                                     |    |

|   |     | 3.5.4 | Alarm Indication Signal (AIS) Detection and Generation          |    |

|   |     |       | 3.5.4.1 Alarm Indication Signal (AIS) Detection                 |    |

|   |     |       | 3.5.4.2 (Alarm Indication Signal) AIS Generation                |    |

|   |     | 3.5.5 | PRBS, QRSS, ARB and IB Pattern Generation and Detection         |    |

|   |     |       | 3.5.5.1 Pattern Generation                                      |    |

|   |     | 0.5.0 | 3.5.5.2 Pattern Detection                                       |    |

|   |     | 3.5.6 | Error Counter                                                   |    |

|   |     |       | 3.5.6.1 Automatic Error Counter Updating                        |    |

|   |     | 2 5 7 | 3.5.6.2 Manual Error Counter Updating                           |    |

|   |     | 3.5.7 | Loopback                                                        |    |

|   |     |       | 3.5.7.1 Analog Loopback                                         |    |

|   |     |       |                                                                 |    |

|   |     | 3.5.8 | 3.5.7.3 Digital Loopback                                        |    |

|   |     | 3.3.0 | 3.5.8.1 G.772 Monitoring                                        |    |

|   |     |       | 3.5.8.2 Jitter Measurement (JM)                                 |    |

|   | 36  |       | K INPUTS AND OUTPUTS                                            |    |

|   | 3.0 | 3.6.1 | Free Running Clock Outputs on CLKE1                             |    |

|   |     | 3.6.2 | MCLK, Master Clock Input                                        |    |

|   |     | 3.6.3 | XCLK, Internal Reference Clock Input                            |    |

|   | 37  |       | RUPT SUMMARY                                                    |    |

|   |     |       |                                                                 |    |

| 4 |     |       | NEOUS                                                           |    |

|   | 4.1 |       | Т                                                               |    |

|   |     | 4.1.1 |                                                                 |    |

|   |     |       | Hardware Reset                                                  | 50 |

|   |     |       |                                                                 |    |

|   | 4.0 | 4.1.4 | Per-Channel Software Reset                                      |    |

|   |     |       | DPROCESSOR INTERFACE                                            |    |

|   |     |       | R UP                                                            |    |

|   |     |       | SS PROTECTION SWITCHING (HPS) SUMMARY                           |    |

| 5 | PRO | OGRAM | IMING INFORMATION                                               | 54 |

|   | 5.1 | REGIS | STER MAP                                                        | 54 |

|   |     | 5.1.1 |                                                                 |    |

|   |     | 5.1.2 | Per-Channel Register                                            |    |

|   | 5.2 | REGIS | STER DESCRIPTION                                                |    |

|   |     | 5.2.1 | Global Register                                                 |    |

|   |     | _     | Per-Channel Register                                            | 62 |

| 6  | JTAG                                                     | 92  |

|----|----------------------------------------------------------|-----|

|    | 6.1 JTAG INSTRUCTION REGISTER (IR)                       | 92  |

|    | 6.2 JTAG DATA REGISTER                                   | 92  |

|    | 6.2.1 Device Identification Register (IDR)               | 92  |

|    | 6.2.2 Bypass Register (BYP)                              |     |

|    | 6.2.3 Boundary Scan Register (BSR)                       | 92  |

|    | 6.3 TEST ACCESS PORT (TAP) CONTROLLER                    | 92  |

| 7  | THERMAL MANAGEMENT                                       | 94  |

|    | 7.1 JUNCTION TEMPERATURE                                 | 94  |

|    | 7.2 EXAMPLE OF JUNCTION TEMPERATURE CALCULATION          | 94  |

|    | 7.3 HEATSINK EVALUATION                                  | 94  |

| 8  | PHYSICAL AND ELECTRICAL SPECIFICATIONS                   | 95  |

|    | 8.1 ABSOLUTE MAXIMUM RATINGS                             | 95  |

|    | 8.2 RECOMMENDED OPERATING CONDITIONS                     | 96  |

|    | 8.3 DEVICE POWER CONSUMPTION AND DISSIPATION (TYPICAL) 1 | 97  |

|    | 8.4 DEVICE POWER CONSUMPTION AND DISSIPATION (MAXIMUM) 1 | 98  |

|    | 8.5 D.C. CHARACTERISTICS                                 | 99  |

|    | 8.6 E1 RECEIVER ELECTRICAL CHARACTERISTICS               |     |

|    | 8.7 E1 TRANSMITTER ELECTRICAL CHARACTERISTICS            | 102 |

|    | 8.8 TRANSMITTER AND RECEIVER TIMING CHARACTERISTICS      |     |

|    | 8.9 CLKE1 TIMING CHARACTERISTICS                         | 105 |

|    | 8.10 JITTER ATTENUATION CHARACTERISTICS                  | 106 |

|    | 8.11 MICROPROCESSOR INTERFACE TIMING                     | 108 |

|    | 8.11.1 Serial Microprocessor Interface                   | 108 |

|    | 8.12 JTAG TIMING CHARACTERISTICS                         | 110 |

| GI | BLOSSARY                                                 | 111 |

| IN | NDEX                                                     | 113 |

| OI | DRDERING INFORMATION                                     | 115 |

### **List of Tables**

| Operation Mode Selection                               | 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|--------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Multiplex Pin Used in Receive System Interface         | 22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Multiplex Pin Used in Transmit System Interface        | 24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| PULS[3:0] Setting in E1 Mode                           | 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Transmit Waveform Value for E1 120 ohm                 | 26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Impedance Matching Value in Transmit Differential Mode | 27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| EXZ Definition                                         | 31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| SLOS Criteria                                          | 33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Clock Output on CLKE1                                  | 45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| After Reset Effect Summary                             | 49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                        | Operation Mode Selection Impedance Matching Value in Receive Differential Mode Multiplex Pin Used in Receive System Interface Multiplex Pin Used in Transmit System Interface PULS[3:0] Setting in E1 Mode Transmit Waveform Value for E1 75 ohm Transmit Waveform Value for E1 120 ohm Impedance Matching Value in Transmit Differential Mode EXZ Definition LLOS Criteria SLOS Criteria TLOS Detection Between Two Channels AIS Criteria Clock Output on CLKE1 Interrupt Summary After Reset Effect Summary |

### **List of Figures**

|           | Functional Block Diagram                                                                                |     |

|-----------|---------------------------------------------------------------------------------------------------------|-----|

| Figure-2  | 484-Pin Fine Pitch BGA (Top View)                                                                       | 11  |

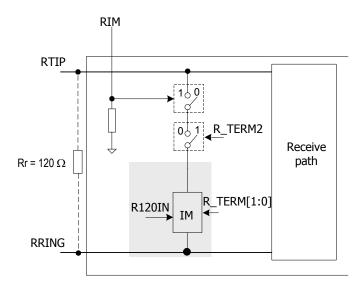

| Figure-3  | Switch between Impedance Matching Modes                                                                 | 19  |

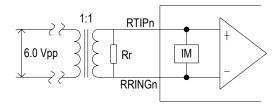

| Figure-4  | Receive Differential Line Interface with Twisted Pair Cable (with transformer)                          | 20  |

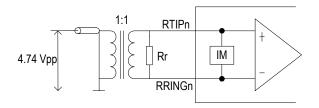

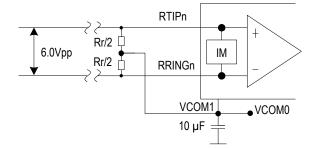

| Figure-5  | Receive Differential Line Interface with Coaxial Cable (with transformer)                               | 20  |

| Figure-6  | Receive Differential Line Interface with Twisted Pair Cable (transformer-less, non standard compliant)  | 20  |

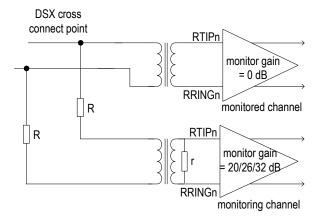

| Figure-7  | Receive Path Monitoring                                                                                 | 21  |

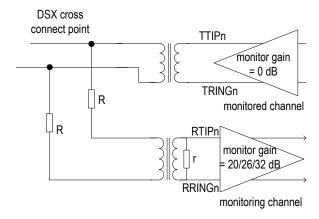

| Figure-8  | Transmit Path Monitoring                                                                                | 21  |

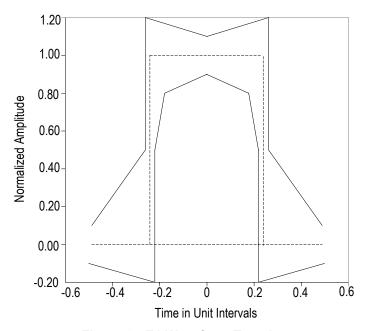

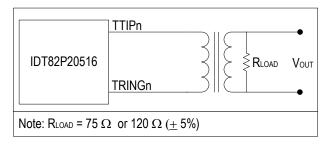

| Figure-9  | E1 Waveform Template                                                                                    | 24  |

| Figure-10 | E1 Waveform Template Measurement Circuit                                                                | 24  |

| Figure-11 | Transmit Differential Line Interface with Twisted Pair Cable (with Transformer)                         | 28  |

|           | Transmit Differential Line Interface with Coaxial Cable (with transformer)                              |     |

| Figure-13 | Transmit Differential Line Interface with Twisted Pair Cable (transformer-less, non standard compliant) | 28  |

| Figure-14 | Jitter Attenuator                                                                                       | 30  |

| Figure-15 | LLOS Indication on Pins                                                                                 | 32  |

| Figure-16 | TLOS Detection Between Two Channels                                                                     | 34  |

| Figure-17 | Pattern Generation (1)                                                                                  | 36  |

| Figure-18 | Pattern Generation (2)                                                                                  | 36  |

| Figure-19 | PRBS / ARB Detection                                                                                    | 37  |

| Figure-20 | IB Detection                                                                                            | 38  |

| Figure-21 | Automatic Error Counter Updating                                                                        | 39  |

| Figure-22 | Manual Error Counter Updating                                                                           | 39  |

| Figure-23 | Priority Of Diagnostic Facilities During Analog Loopback                                                | 40  |

| Figure-24 | Priority Of Diagnostic Facilities During Manual Remote Loopback                                         | 41  |

| Figure-25 | Priority Of Diagnostic Facilities During Digital Loopback                                               | 42  |

| Figure-26 | G.772 Monitoring                                                                                        | 43  |

| Figure-27 | Automatic JM Updating                                                                                   | 44  |

| Figure-28 | Manual JM Updating                                                                                      | 44  |

| Figure-29 | Interrupt Service Process                                                                               | 48  |

| Figure-30 | Reset                                                                                                   | 49  |

| Figure-31 | 1+1 HPS Scheme, Differential Interface (Shared Common Transformer)                                      | 51  |

|           | 1:1 HPS Scheme, Differential Interface (Individual Transformer)                                         |     |

| Figure-33 | 1+1 HPS Scheme, E1 75 ohm Single-Ended Interface (Shared Common Transformer)                            | 53  |

| Figure-34 | JTAG Architecture                                                                                       | 92  |

| Figure-35 | JTAG State Diagram                                                                                      | 93  |

| Figure-36 | Transmit Clock Timing Diagram                                                                           | 104 |

| Figure-37 | Receive Clock Timing Diagram                                                                            | 104 |

|           | CLKE1 Clock Timing Diagram                                                                              |     |

| Figure-39 | E1 Jitter Tolerance Performance                                                                         | 106 |

| •         | E1 Jitter Transfer Performance                                                                          |     |

| •         | Read Operation in Serial Microprocessor Interface                                                       |     |

| Figure-42 | Write Operation in Serial Microprocessor Interface                                                      | 108 |

| Figure-43 | Timing Diagram                                                                                          | 109 |

| Figure-44 | JTAG Timing                                                                                             | 110 |

### 16-Channel Short Haul E1 Line Interface Unit

IDT82P20516

### **FEATURES**

- Integrates 16 channels E1 short haul line interface units for 120  $\Omega$  E1 twisted pair cable and 75  $\Omega$  E1 coaxial cable applications

- ◆ Per-channel configurable Line Interface options

- Fully integrated and software selectable receive and transmit termination

- Option 1: Fully Internal Impedance Matching with integrated receive termination resistor

- Option 2: Partially Internal Impedance Matching with common external resistor for improved device power dissipation

- Option 3: External impedance Matching termination

- Supports global configuration and per-channel configuration to E1 mode

### Per-channel programmable features

- Provides E1 short haul waveform templates and userprogrammable arbitrary waveform templates

- Provides two JAs (Jitter Attenuator) for each channel of receiver and transmitter

- · Supports AMI/HDB3 (for E1) encoding and decoding

### ◆ Per-channel System Interface options

- Supports Single Rail, Dual Rail with clock or without clock and sliced system interface

- Integrated Clock Recovery for the transmit interface to recover transmit clock from system transmit data

### Per-channel system and diagnostic functions

- Provides transmit driver over-current detection and protection with optional automatic high impedance of transmit interface

- Detects and generates PRBS (Pseudo Random Bit Sequence), ARB (Arbitrary Pattern) and IB (Inband Loopback) in either receive or transmit direction

- Provides defect and alarm detection in both receive and transmit directions.

- Defects include BPV (Bipolar Violation) /CV (Code Violation) and EXZ (Excessive Zeroes)

- Alarms include LLOS (Line LOS), SLOS (System LOS), TLOS (Transmit LOS) and AIS (Alarm Indication Signal)

- Programmable LLOS detection /clear levels. Compliant with ITU and ANSI specifications

- · Various pattern, defect and alarm reporting options

- Serial hardware LLOS reporting (LLOS, LLOS0) for all 16 channels

- Register access to individual registers or 16-bit error counters

- Supports Analog Loopback, Digital Loopback and Remote Loopback

- · Supports line monitor

### ◆ Hitless Protection Switching (HPS) without external Relays

- Supports 1+1 and 1:1 hitless protection switching

- Asynchronous hardware control (OE, RIM) for fast global high impedance of receiver and transmitter (hot switching between working and backup board)

- · High impedance transmitter and receiver while powered down

- Per-channel register control for high impedance, independent for receiver and transmitter

### Clock Inputs and Outputs

- Flexible master clock (N x 1.544 MHz or N x 2.048 MHz) (1  $\leq$  N  $\leq$  8, N is an integer number)

- Integrated clock synthesizer can multiply or divide the reference clock to a wide range of frequencies: 8 KHz, 64 KHz, 2.048 MHz, 4.096 MHz, 8.192 MHz, 19.44 MHz and 32.768 MHz

### ◆ Microprocessor Interface

· Supports Serial microprocessor interface

### ◆ Other Key Features

- · IEEE1149.1 JTAG boundary scan

- Two general purpose I/O pins

- 3.3 V I/O with 5 V tolerant inputs

- 3.3 V and 1.8 V power supply

- Package: 484-pin Fine Pitch BGA (19 mm X 19 mm)

### Applicable Standards

- Bellcore TR-TSY-000009, GR-253-CORE and GR-499-CORE

- ETSI CTR12/13

- ETS 300166 and ETS 300 233

- G.703, G.735, G.736, G.742, G.772, G.775, G.783 and G.823

- 0.161

### **APPLICATIONS**

- ◆ SDH/SONET multiplexers

- ◆ Central office or PBX (Private Branch Exchange)

- ◆ Digital access cross connects

- Remote wireless modules

- ◆ Microwave transmission systems

### DESCRIPTION

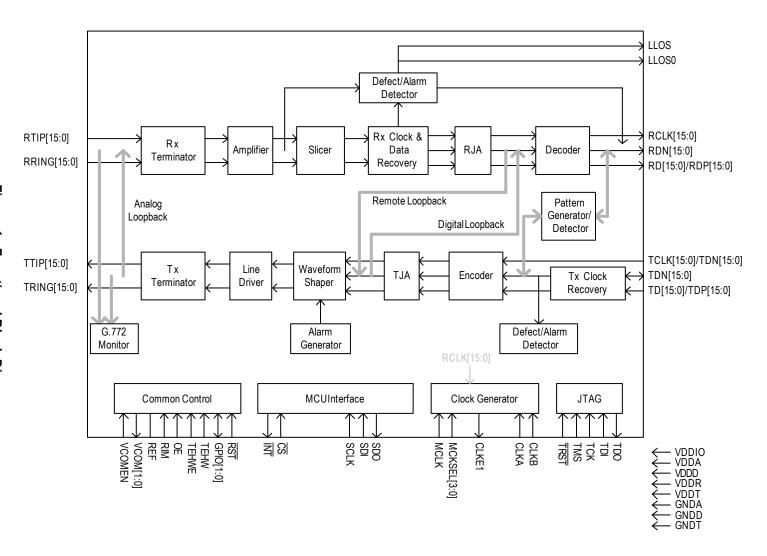

The IDT82P20516 is a 16-channel high-density E1 short haul Line Interface Unit. Each channel of the IDT82P20516 can be independently configured. The configuration is performed through a Serial microprocessor interface.

In the receive path, through a Single Ended or Differential line interface, the received signal is processed by an adaptive Equalizer and then sent to a Slicer. Clock and data are recovered from the digital pulses output from the Slicer. After passing through an enabled or disabled Receive Jitter Attenuator, the recovered data is decoded using B8ZS/

AMI/HDB3 line code rule in Single Rail NRZ Format mode and output to the system, or output to the system without decoding in Dual Rail NRZ Format mode and Dual Rail RZ Format mode.

In the transmit path, the data to be transmitted is input on TDn in Single Rail NRZ Format mode or TDPn/TDNn in Dual Rail NRZ Format mode and Dual Rail RZ Format mode, and is sampled by a transmit reference clock. The clock can be supplied externally from TCLKn or recovered from the input transmit data by an internal Clock Recovery. A selectable JA in Tx path is used to de-jitter gapped clocks. To meet E1 waveform standards, two E1 templates and one J1 template, as well as an arbitrary waveform generator are provided. The data through the Waveform Shaper, the Line Driver and the Tx Transmitter is output on TTIPn and TRINGn.

Alarms (including LOS, AIS) and defects (including BPV, EXZ) are detected in both receive line side and transmit system side. AIS alarm, PRBS, ARB and IB patterns can be generated /detected in receive / transmit direction for testing purpose. Analog Loopback, Digital Loopback and Remote Loopback are all integrated for diagnostics.

JTAG per IEEE 1149.1 is also supported by the IDT82P20516.

Applications 9 December 17, 2009

## **BLOCK DIAGRAM**

Figure-1 Functional Block Diagram

10

**Block Diagram**

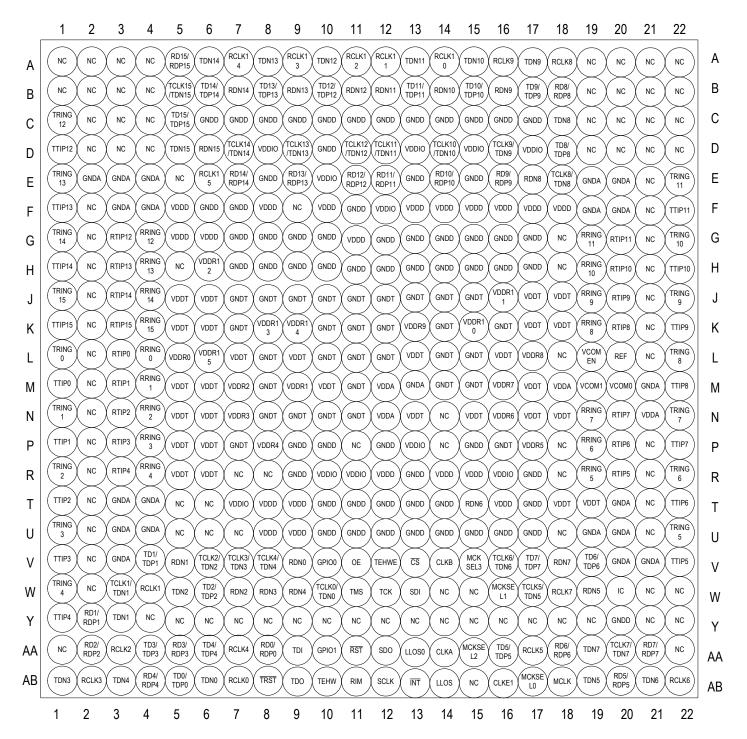

### 1 PIN ASSIGNMENT

Figure-2 484-Pin Fine Pitch BGA (Top View)

Pin Assignment 11 December 17, 2009

### **2 PIN DESCRIPTION**

| Name     | 1/0    | Pin No. <sup>1</sup>                                                     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|----------|--------|--------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          |        |                                                                          | Line Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| RTIPn    | Input  | L3, M3, N3, P3, R3, R20, P20, N20, K20, J20, H20, G20, G3, H3, J3, K3    | RTIPn / RRINGn: Receive Bipolar Tip/Ring for Channel 0 ~ 15 The receive line interface supports both Receive Differential mode and Receive Single Ended                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| RRINGn   |        | L4, M4, N4, P4, R4, R19, P19, N19,                                       | mode.  In Receive Differential mode, the received signal is coupled into RTIPn and RRINGn via a 1:1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| (n=0~15) |        | K19, J19, H19, G19, G4, H4, J4, K4                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| TTIPn    | Output | M1, P1, T1, V1, Y1, V22, T22, P22,                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| TRINGn   |        | M22, K22, H22, F22, D1, F1, H1, K1                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| (n=0~15) |        | L1, N1, R1, U1, W1, U22, R22, N22,<br>L22, J22, G22, E22, C1, E1, G1, J1 | In Transmit Differential mode, TTIPn outputs a positive differential pulse while TRINGn outputs a negative differential pulse. The pulses are coupled to the line side via a 1:2 (step up) transformer or without a transformer (transformer-less).  In Transmit Single Ended mode, TRINGn should be left open (it is shorted to ground internally). The signal presented at TTIPn is output to the line side via a 1:2 (step up) transformer. These pins will become High-Z globally or channel specific in the following conditions:  • Global High-Z:  - Connecting the OE pin to low;  - Loss of MCLK;  - During and after power-on reset, hardware reset or global software reset;  • Per-channel High-Z  - Writing '0' to the OE bit (b6, TCF0,) <sup>2</sup> ;  - Loss of TCLKn in Transmit Single Rail NRZ Format mode or Transmit Dual Rail NRZ Format mode, except that the channel is in Remote Loopback or transmit internal pattern with XCLK <sup>3</sup> ;  - Transmitter power down by writing '1' to the T_OFF bit (b5, TCF0,);  - Per-channel software reset;  - The THZ_OC bit (b4, TCF0,) is set to '1' and the transmit driver over-current is detected.  Refer to Section 3.3.8 Output High-Z on TTIP and TRING for details. |

### Note:

- 1. The pin number of the pins with the footnote 'n' is listed in order of channel (CH0  $\sim$  CH15).

- 2. The content in the brackets indicates the position and the register name of the preceding bit. After the register name, if the punctuation ',...' is followed, this bit is in a per-channel register. The addresses and details are included in Chapter 5 Programming Information.

- 3. XCLK is derived from MCLK. It is 2.048 MHz in E1 mode.

Pin Description 12 December 17, 2009

| Name                   | 1/0    | Pin No.                                                                             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|------------------------|--------|-------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                        |        |                                                                                     | System Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| RDn / RDPn<br>(n=0~15) | Output | AA8, Y2, AA2, AA5, AB4, AB20,<br>AA18, AA21, B18, E16, E14, E12,<br>E11, E9, E7, A5 | RDn: Receive Data for Channel 0 ~ 15 When the receive system interface is configured to Single Rail NRZ Format mode, this multiplex pin is used as RDn. The decoded NRZ data is updated on the active edge of RCLKn. The active level on RDn is selected by the RD_INV bit (b3, RCF1,). When the receiver is powered down, RDn will be in High-Z state or low, as selected by the RHZ bit (b6, RCF0,).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                        |        |                                                                                     | RDPn: Positive Receive Data for Channel 0 ~ 15  When the receive system interface is configured to Dual Rail NRZ Format mode, Dual Rail RZ Format mode or Dual Rail Sliced mode, this multiplex pin is used as RDPn.  In Receive Dual Rail NRZ Format mode, the un-decoded NRZ data is output on RDPn and RDNn and updated on the active edge of RCLKn.  In Receive Dual Rail RZ Format mode, the un-decoded RZ data is output on RDPn and RDNn and updated on the active edge of RCLKn.  In Receive Dual Rail Sliced mode, the raw RZ sliced data is output on RDPn and RDNn.  For Receive Differential line interface, an active level on RDPn indicates the receipt of a positive pulse on RTIPn and a negative pulse on RRINGn; while an active level on RDNn indicates the receipt of a negative pulse on RTIPn and a positive pulse on RRINGn.  For Receive Single Ended line interface, an active level on RDPn indicates the receipt of a positive pulse on RTIPn; while an active level on RDNn indicates the receipt of a negative pulse on RTIPn.  The active level on RDPn and RDNn is selected by the RD_INV bit (b3, RCF1,).  When the receiver is powered down, RDPn and RDNn will be in High-Z state or low, as selected by the RHZ bit (b6, RCF0,). |

| RDNn<br>(n=0~15)       | Output | V9, V5, W7, W8, W9, W19, T15,<br>V18, E17, B16, B14, B12, B11, B9,<br>B7, D6        | RDNn: Negative Receive Data for Channel 0 ~ 15 When the receive system interface is configured to Dual Rail NRZ Format mode, Dual Rail RZ Format mode or Dual Rail Sliced mode, this multiplex pin is used as RDNn. (Refer to the description of RDPn for details).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| RCLKn<br>(n=0~15)      | Output | AB7, W4, AA3, AB2, AA7, AA17,<br>AB22, W18, A18, A16, A14, A12,<br>A11, A9, A7, E6  | RCLKn: Receive Clock for Channel 0 ~ 15  When the receive system interface is configured to Single Rail NRZ Format mode, Dual Rail NRZ Format mode or Dual Rail RZ Format mode, this multiplex pin is used as RCLKn. RCLKn outputs a 2.048 MHz (in E1 mode) clock which is recovered from the received signal. The data output on RDPn/RDNn (in Receive Dual Rail NRZ Format mode, Receive Dual Rail RZ Format mode and Receive Dual Rail Sliced) is updated on the active edge of RCLKn. The active edge is selected by the RCK_ES bit (b4, RCF1,).  In LLOS condition, RCLKn output high or XCLK, as selected by the RCKH bit (b7, RCF0,) (refer to Section 3.5.3.1 Line LOS (LLOS) for details).  When the receiver is powered down, RCLKn will be in High-Z state or low, as selected by the RHZ bit (b6, RCF0,).                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| LLOS                   | Output | AB14                                                                                | LLOS: Receive Line Loss Of Signal  LLOS synchronizes with the output of CLKE1 and can indicate the LLOS (Line LOS) status of all 16 channels in a serial format.  When the clock output on CLKE1 is enabled, LLOS indicates the LLOS status of the 16 channels in a serial format and repeats every seventeen cycles. The start filler is positioned by LLOS0. Refer to the description of LLOS0 below for details.  LLOS is updated on the rising edge of CLKE1 and is always active high.  When the clock output of CLKE1 is disabled, LLOS will be held in High-Z state.  (Refer to Section 3.5.3.1 Line LOS (LLOS) for details.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

Pin Description 13 December 17, 2009

| Name                     | 1/0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Pin No.                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                   | Description                                      |                                  |

|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|----------------------------------|

| LLOS0                    | Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | AA13                                                                               | LLOS0 can indic<br>When the clock<br>indicate the star<br>high for one 8 k<br>outputs 2.048 M<br>seventeen 2.048<br>When the clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | cate the start posi-<br>coutput on CLKE1<br>t position on the L<br>(Hz clock cycle (1<br>Hz clock, LLOS0<br>B MHz clock cycle<br>coutput on CLKE1 | LOS pin. When CLKE1 out 25 µs) every seventeen 8 |                                  |

| TDn / TDPn<br>(n=0~15)   | TDn / TDPn Input AB5, V4, W6, AA4, AA6, AA16, V19, V17, D18, B17, B15, B13, B10, B8, B16, C5 When the transmit system interface plex pin is used as TDn. TDn accepts Single Rail NRZ dat TCLKn. The active level on TDn is select TDPn: Positive Transmit Data with the transmit system interface RZ Format mode, this multiplex In Transmit Dual Rail NRZ Format TDNn and sampled on the active In Transmit Dual Rail RZ Format TDN active Transmit Data Rail RZ Format TDNn and sampled on the active In Transmit Dual Rail RZ Format |                                                                                    | When the transmit system interface is configured to Single Rail NRZ Format mode, this multiplex pin is used as TDn.  TDn accepts Single Rail NRZ data. The data is sampled into the device on the active edge of                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                   |                                                  |                                  |

|                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                    | TDPn                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | TDNn                                                                                                                                              | Output Pulse on TTIPn                            | Output Pulse on TRINGn *         |

|                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                    | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0                                                                                                                                                 | Space                                            | Space                            |

|                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                    | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1                                                                                                                                                 | Negative Pulse                                   | Positive Pulse                   |

|                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                    | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0                                                                                                                                                 | Positive Pulse                                   | Negative Pulse                   |

|                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                    | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1                                                                                                                                                 | Space                                            | Space                            |

|                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                    | Note:<br>* For Transmit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Single Ended line in                                                                                                                              | nterface, TRINGn should be op                    | pen.                             |

|                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                    | The active level                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | on TDPn and TD                                                                                                                                    | Nn is selected by the TD_IN                      | NV bit (b3, TCF1,).              |

| TDNn<br>(n=0~15)         | Input / Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | AB6, Y3, W5, AB1, AB3, AB19,<br>AB21, AA19, C18, A17, A15, A13,<br>A10, A8, A6, D5 | When the transi<br>plex pin is used                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | mit system interfa                                                                                                                                | ·                                                | ail NRZ Format mode, this multi- |