Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

## ICS855011

Low Skew, 1-TO-2

# DIFFERENTIAL-TO-2.5V/3.3V CML FANOUT BUFFER

#### GENERAL DESCRIPTION

The ICS855011 is a low skew, high performance 1-to-2 Differential-to-2.5V/3.3V CML Fanout Buffer and a member of the HiPerClockS™family of High Performance Clock Solutions from IDT. The ICS855011

is characterized to operate from either a 2.5V or a 3.3V power supply. Guaranteed output and part-to-part skew characteristics make the ICS855011 ideal for those clock distribution applications demanding well defined performance and repeatability.

#### **F**EATURES

- Two differential 2.5V/3.3V CML outputs

- · One differential PCLK, nPCLK input pair

- PCLK, nPCLK pair can accept the following differential input levels: LVPECL, LVDS, CML, SSTL

- Output frequency: >3GHz

- Translates any single ended input signal to 3.3V LVPECL levels with resistor bias on nPCLK input

- Output skew: 5ps (typical)

- Part-to-part skew: TBD

- Propagation delay: 242ps (typical)

- Operating voltage supply range:

V<sub>CC</sub> = 2.375V to 3.8V, V<sub>FF</sub> = 0V

- -40°C to 85°C ambient operating temperature

- Available in both standard (RoHS5) and lead-free (RoHS 6) packages

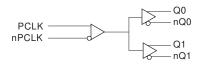

### **BLOCK DIAGRAM**

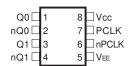

### PIN ASSIGNMENT

#### ICS855011 8-Lead TSSOP

3mm x 3mm x 0.95mm package body

G Package

Top View

The Preliminary Information presented herein represents a product in pre-production. The noted characteristics are based on initial product characterization and/or qualification. Integrated Device Technology, Incorporated (IDT) reserves the right to change any circuitry or specifications without notice.

855011AG 1 REV. A JANUARY 16, 2008

# ICS855011

# Low Skew, 1-to-2 DIFFERENTIAL-TO-2.5V/3.3V CML FANOUT BUFFER

#### TABLE 1. PIN DESCRIPTIONS

| Number | Name            | Туре   |          | Description                                     |

|--------|-----------------|--------|----------|-------------------------------------------------|

| 1, 2   | Q0, nQ0         | Output |          | Differential output pair. CML interface levels. |

| 3, 4   | Q1, nQ1         | Output |          | Differential output pair. CML interface levels. |

| 5      | $V_{EE}$        | Power  |          | Negative supply pin.                            |

| 6      | nPCLK           | Input  | Pullup   | Inverting differential LVPECL clock input.      |

| 7      | PCLK            | Input  | Pulldown | Non-inverting LVPECL differential clock input.  |

| 8      | V <sub>cc</sub> | Power  |          | Positive supply pin.                            |

NOTE: Pullup and Pulldown refer to internal input resistors. See Table 2, Pin Characteristics, for typical values.

#### Table 2. Pin Characteristics

| Symbol                | Parameter               | Test Conditions | Minimum | Typical | Maximum | Units |

|-----------------------|-------------------------|-----------------|---------|---------|---------|-------|

| R <sub>PULLDOWN</sub> | Input Pulldown Resistor |                 |         | 75      |         | kΩ    |

| R <sub>PULLUP</sub>   | Input Pullup Resistor   |                 |         | 75      |         | kΩ    |

## ICS855011

Low Skew, 1-TO-2

# DIFFERENTIAL-TO-2.5V/3.3V CML FANOUT BUFFER

#### ABSOLUTE MAXIMUM RATINGS

Supply Voltage,  $V_{CC}$  4.6V (CML mode,  $V_{EE} = 0$ )

Inputs,  $V_1$  -0.5V to  $V_{CC}$  + 0.5 V

Outputs, I<sub>O</sub>

Continuous Current 20mA Surge Current 40mA

Operating Temperature Range, TA  $-40^{\circ}$ C to  $+85^{\circ}$ C Storage Temperature, T<sub>STG</sub>  $-65^{\circ}$ C to  $150^{\circ}$ C Package Thermal Impedance,  $\theta_{JA}$  101.7°C/W (0 m/s)

(Junction-to-Ambient)

NOTE: Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These ratings are stress specifications only. Functional operation of product at these conditions or any conditions beyond those listed in the *DC Characteristics* or *AC Characteristics* is not implied. Exposure to absolute maximum rating conditions for extended periods may affect product reliability.

Table 3A. Power Supply DC Characteristics,  $V_{CC} = 2.375V$  to 3.8V;  $V_{FF} = 0V$

| Symbol          | Parameter               | Test Conditions | Minimum | Typical | Maximum | Units |

|-----------------|-------------------------|-----------------|---------|---------|---------|-------|

| V <sub>cc</sub> | Positive Supply Voltage |                 | 2.375   | 3.3     | 3.8     | V     |

| I <sub>EE</sub> | Power Supply Current    |                 |         | 50      |         | mA    |

Table 3B. LVPECL DC Characteristics,  $V_{CC} = 2.375V$  to 3.8V;  $V_{EE} = 0V$

| Symbol           | Parameter                               |       | Test Conditions              | Minimum               | Typical | Maximum         | Units |

|------------------|-----------------------------------------|-------|------------------------------|-----------------------|---------|-----------------|-------|

| I <sub>IH</sub>  | Input High Current                      | PCLK  | $V_{CC} = V_{IN} = 3.8V$     |                       |         | 150             | μΑ    |

|                  |                                         | nPCLK | $V_{CC} = V_{IN} = 3.8V$     |                       |         | 5               | μΑ    |

| I <sub>IL</sub>  | Input Low Current                       | PCLK  | $V_{CC} = 3.8V, V_{IN} = 0V$ | -5                    |         |                 | μΑ    |

|                  |                                         | nPCLK | $V_{CC} = 3.8V, V_{IN} = 0V$ | -150                  |         |                 | μΑ    |

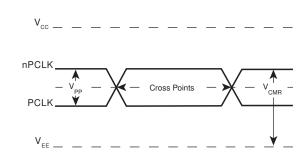

| V <sub>PP</sub>  | Peak-to-Peak Input Voltage              |       |                              | 0.3                   |         | 1               | V     |

| V <sub>CMR</sub> | Common Mode Input Voltage;<br>NOTE 1, 2 |       |                              | V <sub>EE</sub> + 1.5 |         | V <sub>cc</sub> | ٧     |

NOTE 1: Common mode voltage is defined as V<sub>III</sub>.

NOTE 2: For single ended applications, the maximum input voltage for PCLK and nPCLK is V<sub>cc</sub> + 0.3V.

Table 3C. CML DC Characteristics,  $V_{CC} = 2.375V$  to 3.8V;  $V_{EE} = 0V$

| Symbol           | Parameter                         | Conditions | Minimum                 | Typical                 | Maximum         | Units |

|------------------|-----------------------------------|------------|-------------------------|-------------------------|-----------------|-------|

| V <sub>OH</sub>  | Output High Voltage; NOTE 1       |            | V <sub>cc</sub> - 0.020 | V <sub>cc</sub> - 0.010 | V <sub>cc</sub> | V     |

| V <sub>OUT</sub> | Output Voltage Swing              |            | 325                     | 400                     |                 | mV    |

| $V_{DIFF\_OUT}$  | Differential Output Voltage Swing |            | 650                     | 800                     |                 | mV    |

| R <sub>OUT</sub> | Output Source Impedance           |            | 40                      | 50                      | 60              | Ω     |

NOTE 1: Outputs terminated with  $100\Omega$  across differential output pair.

# ICS855011

# Low Skew, 1-to-2 Differential-to-2.5V/3.3V CML Fanout Buffer

Table 4. AC Characteristics,  $V_{CC} = 0V$ ;  $V_{EE} = -3.8V$  to -2.375V or  $V_{CC} = 2.375$  to 3.8V;  $V_{EE} = 0V$

| Symbol           | Parameter                                    | Condition  | Minimum | Typical | Maximum | Units |

|------------------|----------------------------------------------|------------|---------|---------|---------|-------|

| f <sub>MAX</sub> | Output Frequency                             |            |         | >3      |         | GHz   |

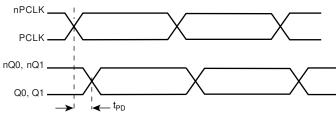

| $t_{\text{PD}}$  | Propagation Delay; (Differential);<br>NOTE 1 |            |         | 242     |         | ps    |

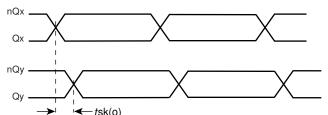

| tsk(o)           | Output Skew; NOTE 2, 4                       |            |         | 5       |         | ps    |

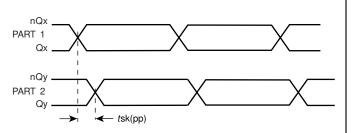

| tsk(pp)          | Part-to-Part Skew; NOTE 3, 4                 |            |         | TBD     |         | ps    |

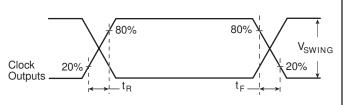

| $t_R/t_F$        | Output Rise/Fall Time                        | 20% to 80% |         | 140     |         | ps    |

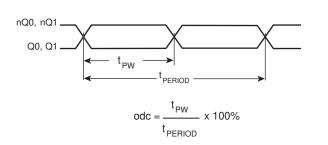

| odc              | Output Duty Cycle                            |            |         | 50      |         | ps    |

All parameters characterized at  $\leq$  1GHz unless otherwise noted.

$R_{L} = 100\Omega$  after each output pair.

NOTE 1: Measured from the differential input crossing point to the differential output crossing point.

NOTE 2: Defined as skew between outputs at the same supply voltage and with equal load conditions.

Measured at the output differential cross points.

NOTE 3: Defined as skew between outputs on different devices operating at the same supply voltages and with equal load conditions. Using the same type of inputs on each device, the outputs are measured at the differential cross points.

NOTE 4: This parameter is defined in accordance with JEDEC Standard 65.

# ICS855011

Low Skew, 1-to-2 Differential-to-2.5V/3.3V CML Fanout Buffer

# PARAMETER MEASUREMENT INFORMATION

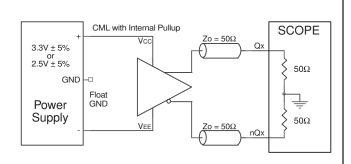

#### **OUTPUT LOAD AC TEST CIRCUIT**

#### DIFFERENTIAL INPUT LEVEL

#### PART-TO-PART SKEW

#### **OUTPUT SKEW**

#### **OUTPUT RISE/FALL TIME**

#### PROPAGATION DELAY

## OUTPUT DUTY CYCLE/PULSE WIDTH/PERIOD

# ICS855011

Low Skew, 1-to-2 Differential-to-2.5V/3.3V CML Fanout Buffer

## **APPLICATION INFORMATION**

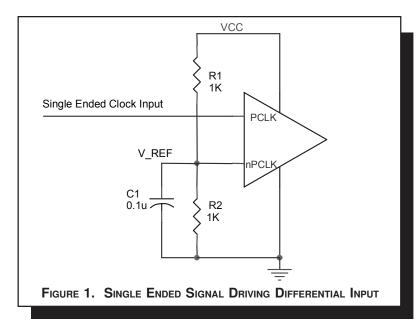

#### WIRING THE DIFFERENTIAL INPUT TO ACCEPT SINGLE ENDED LEVELS

Figure 1 shows how the differential input can be wired to accept single ended levels. The reference voltage  $V_REF = V_{cc}/2$  is generated by the bias resistors R1, R2 and C1. This bias circuit should be located as close as possible to the input pin. The ratio

of R1 and R2 might need to be adjusted to position the V\_REF in the center of the input voltage swing. For example, if the input clock swing is only 2.5V and  $V_{cc} = 3.3V$ ,  $V_{cc} = 1.25V$ and R2/R1 = 0.609.

## ICS855011

Low Skew, 1-TO-2

# DIFFERENTIAL-TO-2.5V/3.3V CML FANOUT BUFFER

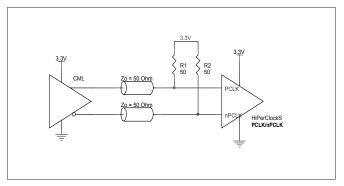

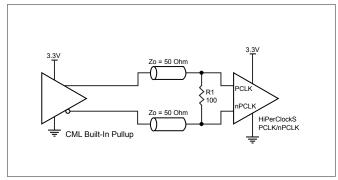

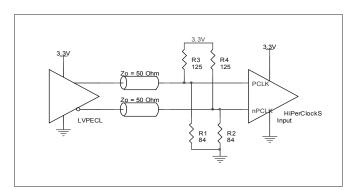

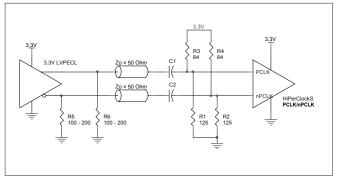

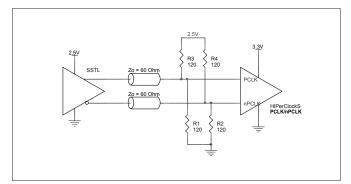

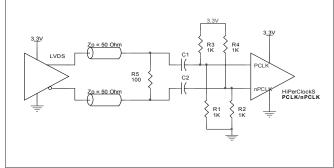

#### LVPECL CLOCK INPUT INTERFACE

The PCLK /nPCLK accepts LVPECL, CML, SSTL and other differential signals. Both  $V_{\text{SWING}}$  and  $V_{\text{OH}}$  must meet the  $V_{\text{PP}}$  and  $V_{\text{CMR}}$  input requirements. Figures 2A to 2F show interface examples for the HiPerClockS PCLK/nPCLK input driven by the most common driver types. The input interfaces suggested

here are examples only. If the driver is from another vendor, use their termination recommendation. Please consult with the vendor of the driver component to confirm the driver termination requirements.

FIGURE 2A. HIPERCLOCKS PCLK/nPCLK INPUT DRIVEN

BY AN OPEN COLLECTOR CML DRIVER

FIGURE 2B. HIPERCLOCKS PCLK/nPCLK INPUT DRIVEN

BY A BUILT-IN PULLUP CML DRIVER

FIGURE 2C. HIPERCLOCKS PCLK/nPCLK INPUT DRIVEN

BY A 3.3V LVPECL DRIVER

FIGURE 2D. HIPERCLOCKS PCLK/nPCLK INPUT DRIVEN

BY A 3.3V LVPECL DRIVER WITH AC COUPLE

FIGURE 2E. HIPERCLOCKS PCLK/nPCLK INPUT DRIVEN BY AN SSTL DRIVER

FIGURE 2F. HIPERCLOCKS PCLK/nPCLK INPUT DRIVEN BY A 3.3V LVDS DRIVER

# ICS855011

Low Skew, 1-to-2 Differential-to-2.5V/3.3V CML Fanout Buffer

# RELIABILITY INFORMATION

Table 6.  $\theta_{JA} vs.$  Air Flow Table for 8 Lead TSSOP

$\theta_{JA}$  by Velocity (Meters per Second)

0

2

Multi-Layer PCB, JEDEC Standard Test Boards

101.7°C/W

90.5°C/W

89.8°C/W

#### TRANSISTOR COUNT

The transistor count for ICS855011 is: 109

# ICS855011

Low Skew, 1-to-2 Differential-to-2.5V/3.3V CML Fanout Buffer

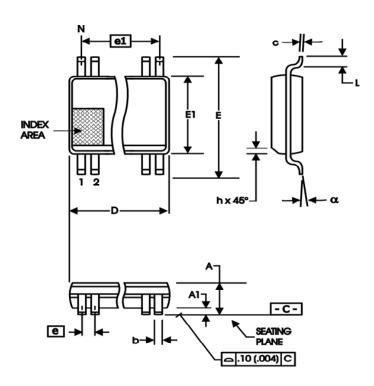

PACKAGE OUTLINE - G SUFFIX FOR 8 LEAD TSSOP

TABLE 7. PACKAGE DIMENSIONS

| SYMBOL | Millin     | neters  |  |  |

|--------|------------|---------|--|--|

| STWBOL | Minimum    | Maximum |  |  |

| N      | 3          | 3       |  |  |

| A      |            | 1.10    |  |  |

| A1     | 0          | 0.15    |  |  |

| A2     | 0.79       | 0.97    |  |  |

| b      | 0.22       | 0.38    |  |  |

| С      | 0.08       | 0.23    |  |  |

| D      | 3.00 BASIC |         |  |  |

| E      | 4.90 E     | BASIC   |  |  |

| E1     | 3.00 BASIC |         |  |  |

| е      | 0.65 BASIC |         |  |  |

| e1     | 1.95 BASIC |         |  |  |

| L      | 0.40       | 0.80    |  |  |

| α      | 0°         | 8°      |  |  |

| aaa    | 0.10       |         |  |  |

Reference Document: JEDEC Publication 95, MO-187

# ICS855011

# Low Skew, 1-to-2 Differential-to-2.5V/3.3V CML Fanout Buffer

TABLE 8. ORDERING INFORMATION

| Part/Order Number | Marking | Package                  | Shipping Packaging | Temperature   |

|-------------------|---------|--------------------------|--------------------|---------------|

| ICS855011AG       | 011A    | 8 lead TSSOP             | tube               | -40°C to 85°C |

| ICS855011AGT      | 011A    | 8 lead TSSOP             | 2500 tape & reel   | -40°C to 85°C |

| ICS855011AGLF     | 11AL    | 8 lead "Lead-Free" TSSOP | tube               | -40°C to 85°C |

| ICS855011AGLFT    | 11AL    | 8 lead "Lead-Free" TSSOP | 2500 tape & reel   | -40°C to 85°C |

NOTE: Parts that are ordered with an "LF" suffix to the part number are the Pb-Free configuration and are RoHS compliant.