# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

## Features

- 80C51 Core

- 12 or 6 Clocks per Instruction (X1 and X2 Modes)

- 256 Bytes Scratchpad RAM

- Dual Data Pointer

- Two 16-bit Timer/Counters: T0 and T1

- T83C5121 with 16 Kbytes Mask ROM

- T85C5121 with 16 Kbytes Code RAM

- T89C5121 with 16 Kbytes Code RAM and 16 Kbytes EEPROM

- On-chip Expanded RAM (XRAM): 256 Bytes

- Versatile Host Serial Interface

- Full-duplex Enhanced UART (EUART) with Dedicated Baud Rate Generator (BRG): Most Standard Speeds up to 230K bits/s at 7.36 MHz

- Output Enable Input

- Multiple Logic Level Shifters Options (1.8V to V<sub>cc</sub>)

- Automatic Level Shifter Option

- Multi-protocol Smart Card Interface

- Certified with Dedicated Firmware According to ISO 7816, EMV2000, GIE-CB, GSM 11.12V and WHQL Standards

- Asynchronous Protocols T = 0 and T = 1 with Direct and Inverse Modes

- Baud Rate Generator Supporting All ISO7816 Speeds up to D = 32/F = 372

- Parity Error Detection and Indication

- Automatic Character Repetition on Parity Errors

- Programmable Timeout Detection

- Card Clock Stop High or Low for Card Power-down Mode

- Support Synchronous Card with C4 and C8 Programmable Outputs

- Card Detection and Automatic De-activation Sequence

- Step-up/down Converter with Programmable Voltage Output: 5V, 3V (± 8% at 60 mA) and 1.8V (±8% at 20 mA)

- Direct Connection to Smart Card Terminals: Short Circuit Current Limitation

- Logic Level Shifters

- 4 kV ESD Protection (MIL/STD 833 Class 3)

- Alternate Card Support with CLK, I/O and RST According to GSM 11.12V Standard

- 2x I/O Ports: 6 I/O Port1 and 8 I/O Port3

- 2x LED Outputs with Programmable Current Sources: 2, 4, or 10 mA

- Hardware Watchdog

- · Reset Output Includes

- Hardware Watchdog Reset

- Power-on Reset (POR)

- Power-fail Detector (PFD)

- 4-level Priority Interrupt System with 7 Sources

- 7.36 to 16 MHz On-chip Oscillator with Clock Prescaler

- Absolute CPU Maximal Frequency: 16 MHz in X1 mode, 8MHz in X2 mode

- Idle and Power-down Modes

- Voltage Operation: 2.85V to 5.4V

- Low Power Consumption

- 8 mA Operating Current (at 5.4V and 3.68 MHz)

- 150 mA Maximum Current with Smart Card Power-on (at 16 MHz X1 Mode)

- 30  $\mu\text{A}$  Maximum Power-down Current at 3.0V (without Smart Card)

- 100  $\mu\text{A}$  Maximum Power-down Current at 5.4V (without Smart Card)

- Temperature Range

- Commercial: 0 to +70°C Operating Temperature

- Industrial: -40 to +85°C Operating Temperature

- Packages

- SSOP24

- QFN32

- PLCC52

8-bit Microcontroller with Multiprotocol Smart Card Interface

T83C5121 T85C5121 T89C5121 AT83C5121 AT85C5121 AT85C5121

## Description

T8xC5121 is a high performance CMOS ROM/CRAM derivative of the 80C51 CMOS single chip 8-bit microcontrollers.

T8xC5121 retains the features of the Atmel 80C51 with extended ROM capacity (16 Kbytes), 512 bytes of internal RAM, a 4-level interrupt system, two 16-bit timer/counters (T0/T1), a full duplex enhanced UART (EUART) with baud rate generator (BRG) and an on-chip oscillator.

In addition, the T8xC5121 have, a Multi protocol Smart Card Interface, a dual data pointer, 2 programmable LED current sources (2-4-10 mA) and a hardware Watchdog.

T89C5121 Flash RAM version and T85C5121 Code RAM version can be loaded by In-System Programming (ISP) software residing in the on-chip ROM from a low-cost external serial EEPROM or from R232 interface.

T8xC5121 have 2 software-selectable modes of reduced activity for further reduction in power consumption.

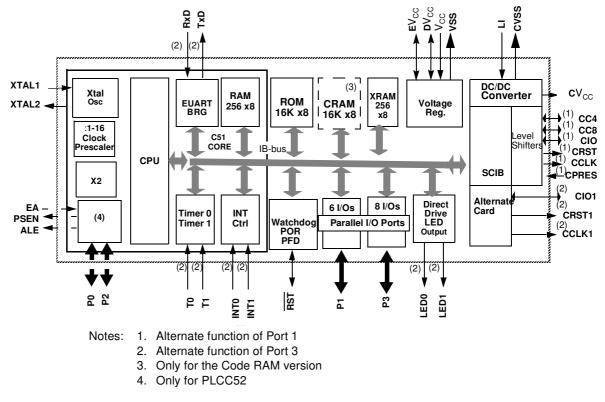

## **Block Diagram**

Figure 1. Block Diagram

2

## **Pin Description**

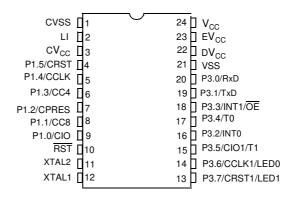

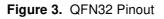

Figure 2. 24-pin SSOP Pinout

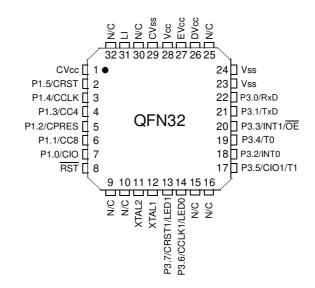

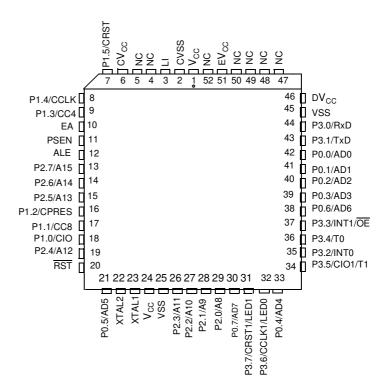

Figure 4. PLCC52 Pinout

4

## A/T8xC5121

## Signals

All the T8xC5121 signals are detailed in Table 1.

The port structure is described in Section "Port Structure Description".

#### Table 1. Ports Description

|      | Ports Des |           | Internal         |      |      |                                                                                                                                         |

|------|-----------|-----------|------------------|------|------|-----------------------------------------------------------------------------------------------------------------------------------------|

|      | Signal    |           | Power            | 505  | -    |                                                                                                                                         |

| Port | Name      | Alternate | Supply           | ESD  | Туре | Description                                                                                                                             |

| P1.0 | CIO       |           | CV <sub>CC</sub> | 4 kV | I/O  | Smart card interface function<br>Card I/O.                                                                                              |

|      |           |           |                  |      | I/O  | Input/Output function<br>P1.0 is a bi-directional I/O port .                                                                            |

|      |           |           |                  |      | I    | Reset configuration<br>Input .                                                                                                          |

| P1.1 | CC8       |           | cv <sub>cc</sub> | 4 kV | 0    | Smart card interface function<br>Card contact 8                                                                                         |

|      |           |           |                  |      | 0    | Output function<br>P1.1 is a Push-pull port.                                                                                            |

|      |           |           |                  |      | I    | Reset configuration Input                                                                                                               |

| P1.2 | CPRES     |           | V <sub>cc</sub>  | 4 kV | I    | Smart card interface function<br>Card presence                                                                                          |

|      |           |           |                  |      | I/O  | Input/Output function<br>P1.2 is a bi-directional I/O port with internal pull-ups- (External Pull-up<br>configuration can be selected). |

|      |           |           |                  |      | I    | Reset configuration<br>Input (high level due to internal pull-up)                                                                       |

| P1.3 | CC4       |           | CV <sub>CC</sub> | 4 kV | 0    | Smart card interface function<br>Card contact 4                                                                                         |

|      |           |           |                  |      | 0    | Output function<br>P1.3 is a Push-pull port.                                                                                            |

|      |           |           |                  |      | I    | Reset configuration<br>Input (high level due to internal pull-up)                                                                       |

| P1.4 | CCLK      |           | CV <sub>CC</sub> | 4 kV | 0    | Smart card interface function<br>Card clock                                                                                             |

|      |           |           |                  |      | I/O  | Input/Output function<br>P1.4 is a a Push-pull port.                                                                                    |

|      |           |           |                  |      | ο    | Reset configuration<br>Output at low level                                                                                              |

| P1.5 | CRST      |           | cv <sub>cc</sub> | 4 kV | 0    | Smart card interface function<br>Card reset                                                                                             |

|      |           |           |                  |      | I/O  | Input/Output function<br>P1.5 is a a Push-pull port.                                                                                    |

|      |           |           |                  |      | 0    | Reset configuration<br>Output at low level                                                                                              |

#### Table 1. Ports Description (Continued)

|      |                | scription (Co | Internal<br>Power |     |      |                                                                                                                                                                                                                                                               |  |  |  |

|------|----------------|---------------|-------------------|-----|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Port | Signal<br>Name | Alternate     | Supply            | ESD | Туре | Description                                                                                                                                                                                                                                                   |  |  |  |

| P3.0 | RxD            |               | EV <sub>CC</sub>  |     | I    | UART function<br>Receive data input                                                                                                                                                                                                                           |  |  |  |

|      |                |               |                   |     | I/O  | Input/Output function<br>P3.0 is a bi-directional I/O port with internal pull-ups.                                                                                                                                                                            |  |  |  |

|      |                |               |                   |     | I    | Reset configuration<br>Input (high level)                                                                                                                                                                                                                     |  |  |  |

| P3.1 | TxD            |               | EV <sub>CC</sub>  |     | 0    | UART function<br>Transmit data output<br>OE active at low or high level depending of PMSOEN bits in SIOCON Reg                                                                                                                                                |  |  |  |

|      |                |               |                   |     | I/O  | Input/Output function<br>P3.1 is a bi-directional I/O port with internal pull-ups.                                                                                                                                                                            |  |  |  |

|      |                |               |                   |     | z    | Reset configuration<br>High impedance due to PMOS switched OFF                                                                                                                                                                                                |  |  |  |

| P3.2 | INT0           |               | DV <sub>CC</sub>  |     | I    | <b>External interrupt 0</b><br>INTO input set IE0 in the TCON register. If bit IT0 in this register is set, bits are set by a falling edge on INT0. If bit IT0 is cleared, bits IE0 is set by a level on INT0.                                                |  |  |  |

|      |                |               |                   |     | I/O  | Input/Output function<br>P3.2 is a bi-directional I/O port with internal pull-ups.                                                                                                                                                                            |  |  |  |

|      |                |               |                   |     | I    | Timer 0: Gate input<br>INT0 serves as external run control for Timer 0 when<br>selected in TCON register.                                                                                                                                                     |  |  |  |

|      |                |               |                   |     | I    | Reset configuration<br>Input (high level)                                                                                                                                                                                                                     |  |  |  |

| P3.3 | INT1           | OE            | EV <sub>cc</sub>  |     | I    | External Interrupt 1<br>INT1 input set OEIT in ISEL Register, IE1 in the TCON register.<br>If bit IT1 in this register is set, bits OEIT and IE1 are set by a falling edge on<br>INT1. If bit IT1 is cleared, bits OEIT and IE1 is set by a low level on INT1 |  |  |  |

|      |                |               |                   |     | I    | <b>UART function</b><br>Output enable. A low or high level (depending OELEV bit in<br>ISEL Register) on this pin disables the PMOS transistors of TxD<br>(P3.1) and T0 (P3.4). This function can be disabled by software                                      |  |  |  |

|      |                |               |                   |     | I/O  | Input/Output function<br>P3.3 is a bi-directional I/O port with internal pull-ups.                                                                                                                                                                            |  |  |  |

|      |                |               |                   |     | I    | Timer 1 function: Gate input<br>INT1 serves as external run control for Timer 1 when<br>selected in TCON register.                                                                                                                                            |  |  |  |

|      |                |               |                   |     | I    | Reset configuration<br>Input (high level)                                                                                                                                                                                                                     |  |  |  |

| P3.4 |                | ТО            | EV <sub>CC</sub>  |     | 0    | UART function<br>OE active at low or high level depending of PMSOEN<br>bits in SIOCON Reg.                                                                                                                                                                    |  |  |  |

#### Table 1. Ports Description (Continued)

| Port | Signal<br>Name | Alternate | Internal<br>Power<br>Supply | ESD | Туре | Description                                                                                                                                                                                                                                    |  |  |  |

|------|----------------|-----------|-----------------------------|-----|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|      |                |           |                             | -   | I/O  | Input/Output function<br>P3.4 is a bi-directional I/O port with internal pull-ups.                                                                                                                                                             |  |  |  |

|      |                |           |                             |     | I    | Timer 0 function: External clock input<br>When Timer 0 operates as a counter, a falling edge on the T0 pin<br>increments the count.                                                                                                            |  |  |  |

|      |                |           |                             |     | Z    | Reset configuration<br>High impedance due to PMOS switched OFF                                                                                                                                                                                 |  |  |  |

| P3.5 | CIO1           |           | DV <sub>CC</sub>            |     | I/O  | Alternate card function<br>Card I/O                                                                                                                                                                                                            |  |  |  |

|      |                |           |                             |     | I/O  | Input/Output function<br>P3.5 is a bi-directional I/O port with internal pull-ups.                                                                                                                                                             |  |  |  |

|      |                |           |                             |     | I    | Timer 1 function: External clock input<br>When Timer 1 operates as a counter, a falling edge on the T1 pin<br>increments the count.                                                                                                            |  |  |  |

|      |                |           |                             |     | I    | Reset configuration<br>Input (high level due to internal pull-up)                                                                                                                                                                              |  |  |  |

| P3.6 | CCLK1          | LED0      | DV <sub>CC</sub>            |     | 0    | Alternate card function<br>Card clock                                                                                                                                                                                                          |  |  |  |

|      |                |           |                             |     | 0    | LED function<br>These pins can be directly connected to the cathode of standard<br>LED without external current limiting resistors. The typical current<br>of each output can be programmed by software to 2, 4 or 10 mA<br>(LEDCON register). |  |  |  |

|      |                |           |                             |     | I/O  | Input/Output function<br>P3.6 is a LED port.                                                                                                                                                                                                   |  |  |  |

|      |                |           |                             |     | I    | Reset configuration<br>Input at high level                                                                                                                                                                                                     |  |  |  |

| P3.7 | CRST1          |           | DV <sub>CC</sub>            |     | 0    | Alternate card function<br>Card reset                                                                                                                                                                                                          |  |  |  |

| P3.7 | CRST1          | LED1      | DV <sub>CC</sub>            |     | 0    | LED function<br>These pins can be directly connected to the cathode of standard<br>LED without external current limiting resistors. The typical current<br>of each output can be programmed by software to 2, 4 or 10 mA<br>(LEDCON register). |  |  |  |

|      |                |           |                             |     | I/O  | Input/Output function<br>P3.7 is a a LED port.                                                                                                                                                                                                 |  |  |  |

|      |                |           |                             |     | I    | Reset configuration<br>Input at high level                                                                                                                                                                                                     |  |  |  |

#### Table 1. Ports Description (Continued)

| Port             | Signal<br>Name | Alternate | Internal<br>Power<br>Supply | ESD | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|------------------|----------------|-----------|-----------------------------|-----|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RST              |                |           | V <sub>cc</sub>             |     | I/O  | Reset inputHolding this pin low for 64 oscillator periods while the oscillatoris running resets the device. The Port pins are driven to their resetconditions when a voltage lower than $V_{IL}$ is applied, whether ornot the oscillator is running.This pin has an internal pull-up resistor which allows the device to be reset byconnecting a capacitor between this pin and VSS. This capacitor is optionalthanks to the internal POR which output a Reset as long as Vcc has notreached the POR threshold levelAsserting $\overline{RST}$ when the chip is in Idle mode or Power-down modereturns the chip to normal operation.The output is active for at least 12 oscillator periods when an internalreset occurs. |

| XTAL1            |                |           | V <sub>cc</sub>             |     | I    | Input to the on-chip inverting oscillator amplifier<br>To use the internal oscillator, a crystal/resonator circuit is connected<br>to this pin.<br>If an external oscillator is used, its output is connected to this pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| XTAL2            |                |           | V <sub>cc</sub>             |     | 0    | Output of the on-chip inverting oscillator amplifier<br>To use the internal oscillator, a crystal/resonator circuit is connected<br>to this pin.<br>If an external oscillator is used, XTAL2 may be left unconnected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| V <sub>cc</sub>  |                |           |                             |     | PWR  | Supply voltage $V_{CC}$ is used to power the internal voltage regulators and internal I/O's.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| LI               |                |           |                             |     | PWR  | <b>DC/DC input</b><br>LI must be tied to $V_{CC}$ through an external coil (typically 4, 7 $\mu$ H) and provide the current for the pump charge of the DC/DC converter.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| CV <sub>CC</sub> |                |           |                             |     | PWR  | <b>Card Supply voltage</b><br>CV <sub>CC</sub> is the programmable voltage output for the Card interface.<br>It must be connected to an external decoupling capacitor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| DV <sub>CC</sub> |                |           |                             |     | PWR  | <b>Digital Supply voltage</b><br>DV <sub>CC</sub> is used to supply the digital core and internal I/Os. It is<br>internally connected to the output of a 3V regulator and must be connected to<br>an external decoupling capacitor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| EV <sub>CC</sub> |                |           | V <sub>cc</sub>             |     | PWR  | <b>Extra supply voltage</b><br>EV <sub>CC</sub> is used to supply the level shifters of UART interface I/O<br>pins. It must be connected to an external decoupling capacitor.<br>This reference voltage is generated internally (automatically or not),<br>or it can be connected to an external voltage reference.                                                                                                                                                                                                                                                                                                                                                                                                        |

| CVSS             |                |           |                             |     | GND  | <b>DC/DC ground</b><br>CVSS is used to sink high shunt currents from the external coil.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| VSS              |                |           |                             |     | GND  | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

## A/T8xC5121

Table 1. Ports Description (Continued)

| Port     | Signal<br>Name | Alternate | Internal<br>Power<br>Supply | ESD      | Туре | Description                                                                                                                                                                                                                                                                                         |

|----------|----------------|-----------|-----------------------------|----------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DNLY FOF | PLCC52 v       | ersion    |                             | <u> </u> |      |                                                                                                                                                                                                                                                                                                     |

| P0[7:0]  | AD[7:0]        |           | V <sub>cc</sub>             |          | I/O  | <b>Input/Output function Port 0</b><br>P0 is an 8-bit open-drain bi-directional I/O port. Port 0 pins that<br>have 1s written to them float and can be used as high impedance<br>inputs. To avoid any parasitic current consumption, Floating P0<br>inputs must be pulled to $V_{CC}$ or $V_{SS}$ . |

|          |                |           |                             |          | I/O  | Address/Data low<br>Mutiplexed Address/Data LSB for external access                                                                                                                                                                                                                                 |

| P2[7:0]  | A[15:8]        |           | V <sub>CC</sub>             |          | I/O  | Input/Output function Port 2<br>P2 is an 8-bit open-drain bi-directional I/O port with internal pull-ups                                                                                                                                                                                            |

|          |                |           |                             |          | 0    | Address high<br>Address Bus MSB for external access                                                                                                                                                                                                                                                 |

| P3.6     | WR             |           | DV <sub>CC</sub>            |          | 0    | Write signal<br>Write signal asserted during external data memory write operation                                                                                                                                                                                                                   |

| P3.7     | RD             |           | DV <sub>CC</sub>            |          | I    | Read signal<br>Read signal asserted during external data memory read operation                                                                                                                                                                                                                      |

| ALE      |                |           | V <sub>cc</sub>             |          | 0    | Address latch enable output<br>The falling edge of ALE strobes the address into external latch                                                                                                                                                                                                      |

| PSEN     | PSEN           |           | V <sub>CC</sub>             |          | 0    | Program strobe enable                                                                                                                                                                                                                                                                               |

| EA       | EA             |           | V <sub>cc</sub>             |          | I    | External access enable<br>This pin must be held low to force the device to fetch code from<br>external program memory starting at address 0000h. It is latched<br>during reset and cannot be dynamically changed during operation.                                                                  |

## Port Structure Description

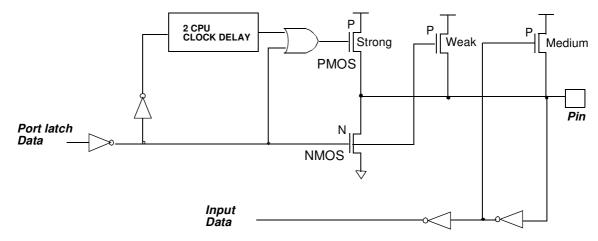

Quasi Bi-directional Output Configuration

The different ports structures are described as follows.

The default port output configuration for standard I/O ports is the quasi bi-directional output that is common on the 80C51 and most of its derivatives. This output type can be used as both an input and output without the need to reconfigure the port. This is possible because when the port outputs a logic high, it is weakly driven, allowing an external device to pull the pin low. When the port outputs a logic low state, it is driven strongly and able to sink a fairly large current. These features are somewhat similar to an open drain output except that there are three pull-up transistors in the guasi bi-directional output that serve different purposes. One of these pull-ups, called the weak pull-up, is turned on whenever the port latch for the pin contains a logic 1. The weak pull-up sources a very small current that will pull the pin high if it is left floating. A second pullup, called the medium pull-up, is turned on when the port latch for the pin contains a logic 1 and the pin itself is also at a logic 1 level. This pull-up provides the primary source current for a quasi bi-directional pin that is outputting a 1. If a pin that has a logic 1 on it is pulled low by an external device, the medium pull-up turns off, and only the weak pull-up remains on. In order to pull the pin low under these conditions, the external device has to sink enough current to overpower the medium pull-up and take the voltage on the port pin below its input threshold.

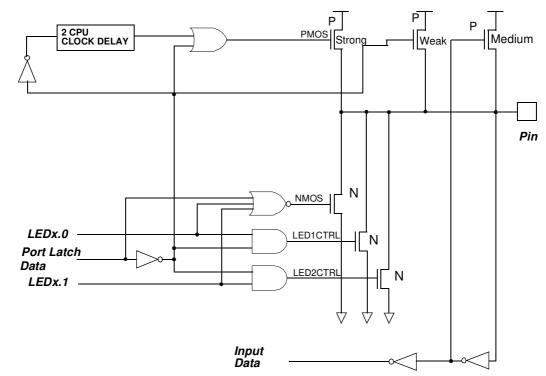

#### Figure 5. Quasi Bi-directional Output Configuration

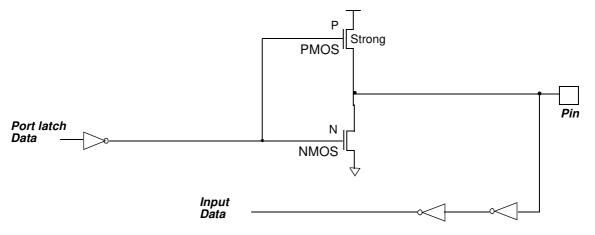

#### Push-pull Output Configuration

The Push-pull output configuration has the same pull-down structure as the quasi bidirectional output modes, but provides a continuous strong pull-up when the port latch contains a logic 1. The Push-pull mode may be used when more source current is needed from a port output. The Push-pull port configuration is shown in Figure 5.

Figure 6. Push-pull Output Configuration

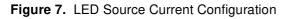

**LED Output Configuration** The input only configuration is shown in Figure 7.

Note: The port can be configured in quasi bi-directional mode and the level of current can be programmed by means of LEDCON0 and LEDCON1 registers before switching the led on by writing a logical 0 in Port latch.

## SFR Mapping

The Special Function Registers (SFR) of the T8xC5121 belongs to the following categories:

- C51 core registers: ACC, B, DPH, DPL, PSW, SP

- I/O port registers: P0, P1, P2, P3

- Timer 0 registers: TCON, TH0, TH1, TMOD, TL0, TL1

- Serial I/O port registers: SADDR, SADEN, SBUF, SCON, BRL, BDRCON

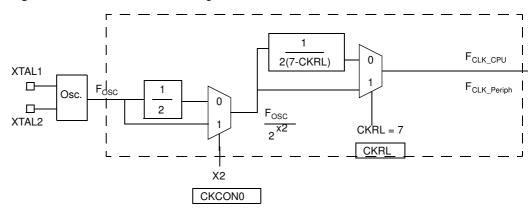

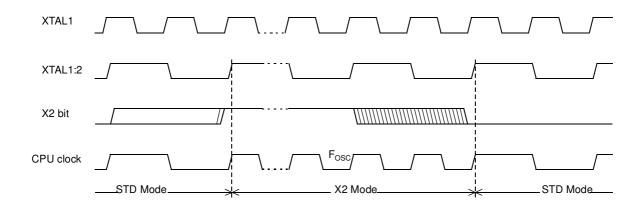

- Power and clock control registers: PCON, CKRL, CKCON0, CKCON1, DCCKPS

- Interrupt system registers: IE0, IPL0, IPH0, IE1, IPL1, IPH1, ISEL

- Watchdog Timer 0: WDTRST, WDTPRG

- Others: AUXR, AUXR1, RCON

- Smart Card Interface: SCSR, SCCON/SCETU0, SCISR/SCETU1, SCIER/SCIIR, SCTBUF/SCRBUF, SCGT0/SCWT0, SCGT1/SCWT1, SCICR/SCWT2

- Port configuration: SIOCON, LEDCON

Table 2. SFR Addresses and Reset Values

|     | 0/8               | 1/9                                     | 2/A                  | 3/B                                     |   | 4/C                  |   | 5/D                  |   | 6/E                  | 7/F                  |     |

|-----|-------------------|-----------------------------------------|----------------------|-----------------------------------------|---|----------------------|---|----------------------|---|----------------------|----------------------|-----|

| F8h |                   |                                         |                      |                                         |   |                      |   |                      |   |                      |                      | FFh |

| F0h | B<br>0000 0000    | LEDCON<br>XXXX 0000                     |                      |                                         |   |                      |   |                      |   |                      |                      | F7h |

| E8h |                   |                                         |                      |                                         |   |                      |   |                      |   |                      |                      | EFh |

| E0h | ACC<br>0000 0000  |                                         |                      |                                         |   |                      |   |                      |   |                      |                      | E7h |

| D8h |                   |                                         |                      |                                         |   |                      |   |                      |   |                      |                      | DFh |

| D0h | PSW<br>0000 0000  | RCON<br>XXXX OXXX                       |                      |                                         |   |                      |   |                      |   |                      |                      | D7h |

| C8h |                   |                                         |                      |                                         |   |                      |   |                      |   |                      |                      | CFh |

| C0h |                   |                                         |                      |                                         |   |                      |   |                      |   |                      |                      | C7h |

| B8h | IPL0<br>XXX0 0000 | SADEN<br>0000 0000                      | ISEL<br>0000 0100    |                                         |   |                      |   |                      |   |                      | DCCKPS<br>XXXX XX11  | BFh |

| B0h | P3<br>1111 1111   | IE1<br>XXXX 0XXX                        | IPL1<br>XXXX 0XXX    | IPH1<br>XXXX 0XXX                       | 0 | SCWT0 *<br>1000 0000 | 0 | SCWT1 *<br>0010 0101 | 0 | SCWT2 *<br>0000 0000 | IPH0<br>XXX0 0000    | B7h |

|     |                   | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, | 1000000000           | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, | 1 | SCGT0 *<br>0000 1100 | 1 | SCGT1*<br>0000 0000  | 1 | SCICR *<br>0000 0000 |                      |     |

| A8h | IE0<br>0XX0 0000  | SADDR<br>0000 0000                      | SCTBUF*<br>0000 0000 | SCSR<br>XXX0 1000                       | 0 | SCCON *<br>0X000     | 0 | SCISR*<br>10X0 0000  | 0 | SCIIR*<br>0X00 0000  | CKCON1<br>XXXX 0XXX  | AFh |

|     |                   |                                         | SCRBUF<br>0000 000   |                                         | 1 | SCETU0<br>0111 0100  | 1 | SCETU1<br>0XXX       | 1 | SCIER *<br>0X00 0000 |                      |     |

| A0h | P2<br>1111 1111   |                                         | AUXR1<br>XXX XXX0    |                                         |   |                      |   |                      |   | WDTRST<br>XXXX XXXX  | WDTPRG<br>XXXX X0000 | A7h |

| 98h | SCON<br>XXX0 0000 | SBUF<br>XXXX XXXX                       | BRL<br>0000 0000     | BDRCON<br>XXX0 0000                     |   |                      |   |                      |   |                      |                      | 9Fh |

| 90h | P1<br>XX11 1111   | SIOCON<br>00XX 0000                     |                      |                                         |   |                      |   |                      |   |                      | CKRL<br>XXXX 111X    | 97h |

| 88h | TCON<br>0000 0000 | TMOD<br>0000 0000                       | TL0<br>0000 0000     | TL1<br>0000 0000                        |   | TH0<br>0000 0000     |   | TH1<br>0000 0000     |   | AUXR<br>00XX XX00    | CKCON0<br>X0X0 X000  | 8Fh |

| 80h | P0<br>1111 1111   | SP<br>0000 0111                         | DPL<br>0000 0000     | DPH<br>0000 0000                        |   | 20                   |   |                      |   |                      | PCON<br>00XX XX00    | 87h |

|     | 0/8               | 1/9                                     | 2/A                  | 3/B                                     |   | 4/C                  |   | 5/D                  |   | 6/E                  | 7/F                  |     |

Reserved

| SCRS Bit (SCSR.0) | (*)       |  |  |  |  |

|-------------------|-----------|--|--|--|--|

| 0                 | SFR value |  |  |  |  |

| 1                 | SFR value |  |  |  |  |

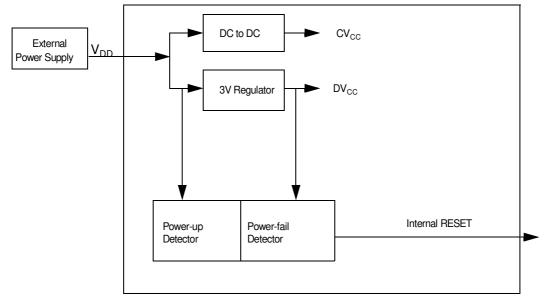

## PowerMonitor

The PowerMonitor function supervises the evolution of the voltages feeding the microcontroller, and if needed, suspends its activity when the detected value is out of specification.

It is guaranteed to start up properly when T8xC5121 is powered up and prevents code execution errors when the power supply becomes lower than the functional threshold.

This section describes the functions of the PowerMonitor.

**Description** In order to start up and to properly maintain the microcontroller operation, V<sub>DD</sub> has to be stabilized in the V<sub>DD</sub> operating range and the oscillator has to be stabilised with a nominal amplitude compatible with logic threshold.

This control is carried out during three phases which are the power-up, normal operation and stop. It complies with the following requirements:

- It guarantees an operational Reset when the microcontroller is powered

- and a protection if the power supply goes out from the functional range of the microcontroller.

Figure 8. PowerMonitor Block Diagram

#### **PowerMonitor Diagram**

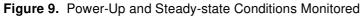

The target of the PowerMonitor is to survey the power supply in order to detect any voltage drops which are not in the target specification. This PowerMonitor block checks two kind of situations that occur:

- During the power-up condition, when V<sub>DD</sub> is reaching the product specification

- During a steady-state condition, when V<sub>DD</sub> is stable but disturbed by any undesirable voltage drops.

Figure 9 shows some configurations that can be met by the PowerMonitor.

Such device when it is integrated in a microcontroller, forces the CPU in reset mode when  $V_{\text{DD}}$  reaches a voltage condition which is out of the specification.

The thresholds and their functions are:

- V<sub>PFDP</sub>: the output voltage of the regulator has reached a minimum functional value at the power-up. The circuit leaves the RESET mode.

- V<sub>PFDM</sub>: the output voltage of the regulator has reached a low threshold functional value for the microcontroller. An internal RESET is set.

Glitch filtering prevents the system from RESET when short duration glitches are carried on  $V_{DD}$  power supply.

The electrical parameters  $V_{\text{PFDP}},\,V_{\text{PFDM}},\,t_{\text{rise}},\,t_{\text{fall}},\,t_{\text{G}}$  are specified in the DCparameters section.

| Power Monitoring<br>and Clock | For applications where power consumption is a critical factor, three power modes are provided:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Management                    | Idle mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                               | Power-down mode     Okach Management (XO facture and Okach Brazzalar)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                               | Clock Management (X2 feature and Clock Prescaler)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                               | 3V Regulator Modes (pulsed or not pulsed)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Idle Mode                     | An instruction that sets PCON.0 causes the last instruction to be executed before going into the Idle mode. In the Idle mode, the internal clock signal is gated off to the CPU, but not to the interrupt, Timer 0, and Serial Port functions. The CPU status is preserved in its entirety: the Stack Pointer, Program Counter, Program Status Word, Accumulator and all other registers maintain their data during Idle. The port pins hold the logical states they had at the time Idle was activated. ALE and PSEN hold at logic high levels.                                                                  |

|                               | There are two ways to terminate the Idle. Activation of any enabled interrupt will cause PCON.0 to be cleared by hardware, terminating the Idle mode. The interrupt will be serviced, and following RETI the next instruction to be executed will be the one following the instruction that put the device into idle.                                                                                                                                                                                                                                                                                             |

|                               | The flag bit GF0 can be used to give an indication if an interrupt occurred during normal operation or during an Idle. For example, an instruction that activates Idle can also set one or both flag bits. When Idle is terminated by an interrupt, the interrupt service routine can examine the flag bits.                                                                                                                                                                                                                                                                                                      |

|                               | The other way of terminating the Idle mode is with a hardware reset. Since the clock oscillator is still running, the hardware reset needs to be held active for only two machine cycles (24 oscillator periods) to complete the reset.                                                                                                                                                                                                                                                                                                                                                                           |

| Power-down Mode               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Entering Power-down Mode      | To save maximum power, a Power-down mode can be invoked by software (refer to Table 3, PCON register).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                               | In Power-down mode, the oscillator is stopped and the instruction that invoked Power-<br>down mode is the last instruction executed. The internal RAM and SFRs retain their<br>value until the Power-down mode is terminated. $v_{cc}$ can be lowered to save further<br>power. Either a hardware reset or an external interrupt can cause an exit from Power-<br>down. To properly terminate Power-down, the reset or external interrupt should not be<br>executed before $v_{cc}$ is restored to its normal operating level and must be held active<br>long enough for the oscillator to restart and stabilize. |

|                               | Only external interrupts INT0 and INT1 are useful to exit from Power-down. For that, interrupt must be enabled and configured as level or edge sensitive interrupt input.                                                                                                                                                                                                                                                                                                                                                                                                                                         |

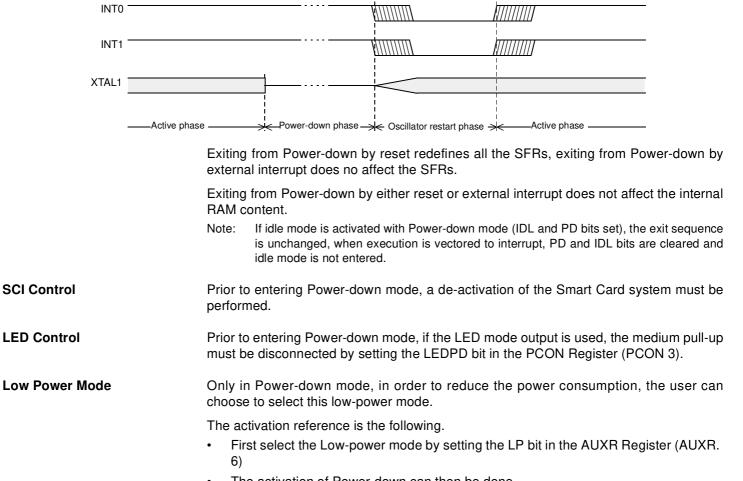

|                               | Holding the pin low restarts the oscillator but bringing the pin high completes the exit as detailed in Figure 10. When both interrupts are enabled, the oscillator restarts as soon as one of the two inputs is held low and Power-Down exit will be completed when the first input will be released. In this case the higher priority interrupt service routine is executed.                                                                                                                                                                                                                                    |

|                               | Once the interrupt is serviced, the next instruction to be executed after RETI will be the one following the instruction that put it into Power-down mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Exit from Power-down Mode     | Exiting from Power-down by external interrupt does not affect the SFRs and the internal RAM content.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

The ports status under Power-down is the status which was valid before entering this mode.

The INT1 interrupt is a multiplexed input (see Interrupt paragraph) with CPRES (Card detection) and Rxd (UART Rx). So these three inputs can be used to exit from Power-down mode. The configurations which must be set are detailed below:

- Rxd input:

- RXEN (ISEL.0) must be set

- EX1 (IE0.2) must be set

- A low level detected during more than 100 microseconds exit from Powerdown

- CPRES input:

- PRSEN (ISEL.1) must be set

- EX1 (IEO.2) must be set

- EA (IE0.7) must be set

- In the INT1 interrupt vector, the CPLEV Bit (ISEL.7) must be inverted and PRESIT Bit (ISEL.5) must be reset.

#### Figure 10. Power-down Exit Waveform

#### **Reduced EMI Mode**

The ALE signal is used to demultiplex address and data buses on port 0 when used with external program or data memory. Nevertheless, during internal code execution, ALE signal is still generated.

Only in case of PLCC52 version, in order to reduce EMI, ALE signal can be disabled by setting AO bit.

The AO bit is located in AUXR register at bit location 0 (See Table 4). As soon as AO is set, ALE is no longer output but remains active during MOVX and MOVC instructions and external fetches. During ALE disabling, ALE pin is weakly pulled high.

#### Power Modes Control Registers

Table 3. PCON Register

PCON (S:87h) Power Configuration Register

| 7             | 6               | 5                                                                                                                                                                         | 4                                                                                                                                                                                                                                                                                      | 3               | 2             | 1              | 0          |  |  |  |  |

|---------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|---------------|----------------|------------|--|--|--|--|

| SMOD1         | SMOD0           | -                                                                                                                                                                         | -                                                                                                                                                                                                                                                                                      | LEDPD           | GF0           | PD             | IDL        |  |  |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                                                                                                                                                               |                                                                                                                                                                                                                                                                                        |                 |               |                |            |  |  |  |  |

| 7             | SMOD1           |                                                                                                                                                                           | <b>Double Baud Rate bit</b><br>Set to double the Baud Rate when Timer 1 is used and mode 1, 2 or 3 is selected in<br>SCON register.                                                                                                                                                    |                 |               |                |            |  |  |  |  |

| 6             | SMOD0           | When cleared,<br>accesses to SC<br>When set, read                                                                                                                         | SCON Select bit<br>When cleared, read/write accesses to SCON.7 are to SM0 bit and read/write<br>accesses to SCON.6 are to SM1 bit.<br>When set, read/write accesses to SCON.7 are to FE bit and read/write accesses to<br>SCON.6 are to OVR bit. SCON is Serial Port Control register. |                 |               |                |            |  |  |  |  |

| 5             |                 | Reserved                                                                                                                                                                  | Reserved                                                                                                                                                                                                                                                                               |                 |               |                |            |  |  |  |  |

| 4             |                 | Reserved                                                                                                                                                                  |                                                                                                                                                                                                                                                                                        |                 |               |                |            |  |  |  |  |

| 3             | LEDPD           | LED Control P<br>When cleaned<br>medium pull-up                                                                                                                           | the I/O pull-up                                                                                                                                                                                                                                                                        | o is the standa | rd C51 pull-u | o control. Whe | en set the |  |  |  |  |

| 2             | GF0             | One use is to in                                                                                                                                                          | <b>General-purpose flag 0</b><br>One use is to indicate wether an interrupt occurred during normal operation or during Idle mode.                                                                                                                                                      |                 |               |                |            |  |  |  |  |

| 1             | PD              | Power-down Mode bit<br>Cleared by hardware when an interrupt or reset occurs.<br>Set to activate the Power-down mode.<br>If IDL and PD are both set, PD takes precedence. |                                                                                                                                                                                                                                                                                        |                 |               |                |            |  |  |  |  |

| 0             | IDL             | Idle Mode bit<br>Cleared by hard<br>Set to activate<br>If IDL and PD a                                                                                                    | he Idle mode                                                                                                                                                                                                                                                                           |                 |               |                |            |  |  |  |  |

Reset Value = X0XX XX00b

#### Table 4. AUXR Register

AUXR (S:8Eh) Auxiliary Register

| 7             | 6               | 5                            | 4                                                                                                                                                               | 3                | 2             | 1                | 0  |  |  |  |  |

|---------------|-----------------|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|---------------|------------------|----|--|--|--|--|

| -             | LP              | -                            | -                                                                                                                                                               | -                | -             | EXTRAM           | AO |  |  |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Descriptio                   | Description                                                                                                                                                     |                  |               |                  |    |  |  |  |  |

| 7             | -               | <b>Reserved</b><br>The value | Reserved<br>The value read from this bit is indeterminate. Do not set this bit.                                                                                 |                  |               |                  |    |  |  |  |  |

| 6             | LP              | Clear to se                  | Low Power mode selection<br>Clear to select standard mode<br>Set to select low consumption mode                                                                 |                  |               |                  |    |  |  |  |  |

| 5             | -               |                              | Reserved<br>The value read from this bit is indeterminate. Do not set this bit.                                                                                 |                  |               |                  |    |  |  |  |  |

| 4             | -               |                              | Reserved<br>The value read from this bit is indeterminate. Do not set this bit.                                                                                 |                  |               |                  |    |  |  |  |  |

| 3             | -               | Reserved<br>The value        | read from this                                                                                                                                                  | s bit is indeter | minate. Do no | ot set this bit. |    |  |  |  |  |

| 2             | -               | Reserved<br>The value        |                                                                                                                                                                 | s bit is indeter | minate. Do no | ot set this bit. |    |  |  |  |  |

| 1             | EXTRAM          | (ONLY for<br>Clear to m      | EXTRAM select<br>(ONLY for PLCC52 version)<br>Clear to map XRAM datas in internal XRAM memory.<br>Set to map XRAM datas in external XRAM memory.                |                  |               |                  |    |  |  |  |  |

| 0             | AO              | (ONLY for<br>Clear to re     | ALE Output bit<br>(ONLY for PLCC52 version)<br>Clear to restore ALE operation during internal fetches.<br>Set to disable ALE operation during internal fetches. |                  |               |                  |    |  |  |  |  |

Reset Value = 00XX XX00b

## Table 5. IE0 Register

IE0

Interrupt Enable Register (A8h)

| 7             | 6               | 5                                         | 4                                                                                                                                                                                                                         | 3                                                                                                                                                                                                                                                     | 2      | 1   | 0   |  |  |  |  |

|---------------|-----------------|-------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-----|-----|--|--|--|--|

| EA            | -               | -                                         | ES                                                                                                                                                                                                                        | ET1                                                                                                                                                                                                                                                   | EX1    | ET0 | EX0 |  |  |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Descriptio                                | Description                                                                                                                                                                                                               |                                                                                                                                                                                                                                                       |        |     |     |  |  |  |  |

| 7             | EA              | Clear to di<br>Set to ena<br>If EA = 1, e | Enable All interrupt bit<br>Clear to disable all interrupts.<br>Set to enable all interrupts.<br>If EA = 1, each interrupt source is individually enabled or disabled by setting or<br>clearing its interrupt enable bit. |                                                                                                                                                                                                                                                       |        |     |     |  |  |  |  |

| 6             | -               |                                           | Reserved<br>The value read from this bit is indeterminate. Do not set this bit.                                                                                                                                           |                                                                                                                                                                                                                                                       |        |     |     |  |  |  |  |

| 5             | -               |                                           | Reserved<br>The value read from this bit is indeterminate. Do not set this bit.                                                                                                                                           |                                                                                                                                                                                                                                                       |        |     |     |  |  |  |  |

| 4             | ES              | Clear to di                               | Serial port Enable bit<br>Clear to disable serial port interrupt.<br>Set to enable serial port interrupt.                                                                                                                 |                                                                                                                                                                                                                                                       |        |     |     |  |  |  |  |

| 3             | ET1             | Clear to di                               | isable Timer 1                                                                                                                                                                                                            | rupt Enable to<br>overflow intervention of the second second<br>second second | rrupt. |     |     |  |  |  |  |

| 2             | EX1             | Clear to di                               | External interrupt 1 Enable bit<br>Clear to disable external interrupt 1.<br>Set to enable external interrupt 1.                                                                                                          |                                                                                                                                                                                                                                                       |        |     |     |  |  |  |  |

| 1             | ET0             | Clear to di                               | <b>Timer 0 overflow interrupt Enable bit</b><br>Clear to disable Timer 0 overflow interrupt.<br>Set to enable Timer 0 overflow interrupt.                                                                                 |                                                                                                                                                                                                                                                       |        |     |     |  |  |  |  |

| 0             | EX0             | Clear to di                               | External interrupt 0 Enable bit<br>Clear to disable external interrupt 0.<br>Set to enable external interrupt 0.                                                                                                          |                                                                                                                                                                                                                                                       |        |     |     |  |  |  |  |

Reset Value = 0XX0 0000b

A/T8xC5121

### Table 6. ISEL Register

ISEL (S:BAh) Interrupt Enable Register

| 7             | 6               | 5                                     | 4                                                                                                                                                                                                 | 3                                                   | 2    | 1    | 0      |  |  |  |  |

|---------------|-----------------|---------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|------|------|--------|--|--|--|--|

| CPLEV         | -               | RXIT                                  | PRESIT                                                                                                                                                                                            | OELEV                                               | OEEN | RXEN | PRESEN |  |  |  |  |