Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: [info@chipsmall.com](mailto:info@chipsmall.com) Web: [www.chipsmall.com](http://www.chipsmall.com)

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# Channel NPI

8V19N490 FemtoClock® NG Jitter Attenuator and Clock Synthesizer

8V79S680 JESD204B-compliant Fanout Buffer and Divider

February 2018

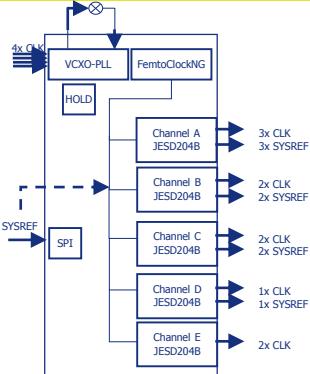

# 8V19N490 Overview

# Low Phase Noise Clock Generation for 5G New Radio

# Features

- High clock frequency generation

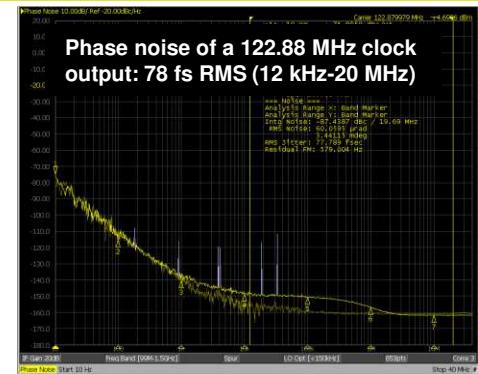

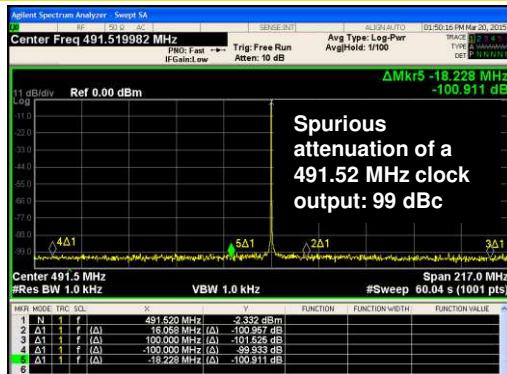

- Low phase noise <80fs RMS and high spurious attenuation of 90dBc

- Synchronized 18 outputs with deterministic I/O latency

- Phase stability over temperature

- Build-in SYSREF generation

# Benefits

- Supports RF-DAC clocks up to 2.94912GHz

- Supports best EVM radio designs

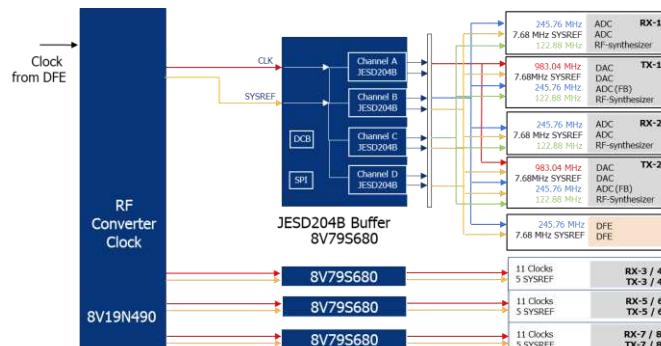

- Single chip solution for 4T4R-16T16R

- 64T64R and higher: 8V79S680 or cascaded PLL operation

- Best for clock generation in AAS and MIMO systems

- JESD204B subclass 0/1 converter synchronization

# Applications

- 5G Radio clock jitter attenuation, frequency generation and clock/SYSREF distribution

- JESD204B ADC/DAC converter clocking

## Supports New Radio Designs with Lowest Phase Noise Clock Signals

# 8V79S680 Overview

# *JESD204B-compliant Clock/SYREF Distribution for 5G New Radio*

# Features

- High clock/SYSREF signal fanout

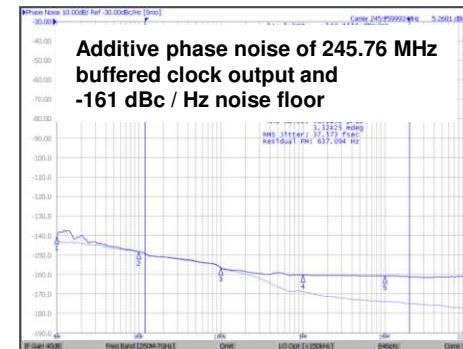

- Low additive phase noise <100fs RMS and low noise floor <-160dBc/Hz

- Synchronized 16 outputs with deterministic I/O latency

- Additional fanout for 8V19N490

- Phase stability over temperature

- High clock frequency <3 GHz

# Benefits

- Solution for 64T64R and higher

- Supports best EVM radio designs

- Best for clock generation in AAS and MIMO systems

- JESD204B subclass 0/1 converter synchronization

- Supports RF-DAC clocks up to 2.94912 GHz

## Applications

- 5G Radio clock/SYSREF signal distribution

- JESD204B ADC/DAC converter clocking

## Supports New Radio Designs with High Fanout Clock Distribution

# Thank You

Analog Mixed Signal Product

Leadership in Growth Markets