Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

### K8 Clock Chip for Serverworks GC-HT 2-Way Servers

**Recommended Application:**Serverworks GC-HT systems using AMD K8 processors

#### **Output Features:**

- 4 Pairs of AMD K8 clocks

- 1 Pair of SRC/PCI Express\* clock

- 2 14.318 MHz REF clocks

- 2 USB 48MHz clocks

- 4 HyperTransport 66 MHz clocks

- 4 PCI 33 MHz clocks

#### Features:

- Spread Spectrum for EMI reduction

- Outputs may be disabled via SMBus

- M/N programming via SMBus

### **Pin Configuration**

48-SSOP, TSSOP

#### **Power Groups**

| Pin N    | Number   | Description                 |

|----------|----------|-----------------------------|

| VDD      | GND      | Description                 |

| 3        | 6        | 48MHz                       |

| 9        | 14       | 66MHz HTT Clocks            |

| 15       | 20       | 33 MHz PCI Clocks           |

| 22       | 23       | IREF, Analog Core           |

| 27       | 28       | SRC PLL, SRCCLK             |

| 33,37,41 | 32,36,40 | K8 CPU Clocks, CPU PLL      |

| 48       | 44       | REF Clocks, Xtal Oscillator |

#### **Functionality**

| FS2 | FS1       | FS0 | CPU    | HTT          | PCI   |

|-----|-----------|-----|--------|--------------|-------|

| F32 | F52   F51 |     | MHz    | MHz          | MHz   |

| 0   | 0         | 0   | Hi-Z   | Hi-Z         | Hi-Z  |

| 0   | 0         | 1   | Χ      | X/3          | X/6   |

| 0   | 1         | 0   | 180.00 | 180.00 60.00 |       |

| 0   | 1         | 1   | 220.00 | 73.12        | 36.56 |

| 1   | 0         | 0   | 100.00 | 66.66        | 33.33 |

| 1   | 0         | 1   | 133.33 | 66.66        | 33.33 |

| 1   | 1         | 0   | 166.67 | 66.66        | 33.33 |

| 1   | 1         | 1   | 200.00 | 66.66        | 33.33 |

### **Pin Descriptions**

| PIN#     | PIN NAME               | PIN TYPE   | DESCRIPTION                                                                                     |

|----------|------------------------|------------|-------------------------------------------------------------------------------------------------|

| 1        | X1                     | IN         | Crystal input, Nominally 14.318MHz.                                                             |

| 2        | X2                     | OUT        | Crystal output, Nominally 14.318MHz                                                             |

| 3        | VDD48                  | PWR        | Power pin for the 48MHz output.3.3V                                                             |

| 4        | 48MHz_0                | OUT        | 48MHz clock output.                                                                             |

| 5        | 48MHz_1                | OUT        | 48MHz clock output.                                                                             |

| 6        | GND                    | PWR        | Ground pin.                                                                                     |

| 7        | SCLK                   | I/O        | Clock pin of SMBus circuitry, 5V tolerant.                                                      |

| 8        | SDATA                  | I/O        | Data pin for SMBus circuitry, 5V tolerant.                                                      |

| 9        | VDDHTT                 | PWR        | Supply for HTT clocks, nominal 3.3V.                                                            |

| 10       | HTTCLK0                | OUT        | 3.3V Hyper Transport output                                                                     |

| 11       | HTTCLK1                | OUT        | 3.3V Hyper Transport output                                                                     |

| 12       | HTTCLK2                | OUT        | 3.3V Hyper Transport output                                                                     |

| 13       | HTTCLK3                | OUT        | 3.3V Hyper Transport output                                                                     |

| 14       | GNDHTT                 | PWR        | Ground pin for the HTT outputs                                                                  |

| 15       | VDDPCI                 | PWR        | Power supply for PCI clocks, nominal 3.3V                                                       |

| 16       | PCICLK0                | OUT        | PCI clock output.                                                                               |

| 17       | PCICLK1                | OUT        | PCI clock output.                                                                               |

| 18       | PCICLK2                | OUT        | PCI clock output.                                                                               |

| 19       | PCICLK3                | OUT        | PCI clock output.                                                                               |

| 20       | GNDPCI                 | PWR        | Ground pin for the PCI outputs                                                                  |

| 21       | PD#                    | IN         | Asynchronous active low input pin used to power down the device. The internal                   |

|          |                        | 114        | clocks are disabled and the VCO and the crystal are stopped.                                    |

| 22       | VDDA                   | PWR        | 3.3V power for the PLL core.                                                                    |

| 23       | GNDA                   | OUT        | Ground pin for the PLL core.                                                                    |

|          |                        |            | This pin establishes the reference current for the differential current-mode output             |

| 24       | IREF                   | OUT        | pairs. This pin requires a fixed precision resistor tied to ground in order to establish        |

|          |                        |            | the appropriate current. 475 ohms is the standard value.                                        |

| 25       | SRCCLKC0               | OUT        | Complement clock of differential SRC clock pair.                                                |

| 26       | SRCCLKT0               | OUT        | True clock of differential SRC clock pair.                                                      |

| 27       | VDDSRC                 | PWR        | Supply for SRC clocks, 3.3V nominal                                                             |

| 28       | GNDSRC                 | PWR        | Ground pin for the SRC outputs                                                                  |

| 29       | SPREAD_EN              | IN         | Asynchronous, active high input to enable spread spectrum functionality.                        |

| 30       | CPUCLK8C3              | OUT        | Complementary clock of differential 3.3V push-pull K8 pair.                                     |

| 31       | CPUCLK8T3              | OUT        | True clock of differential 3.3V push-pull K8 pair.                                              |

| 32       | GNDCPU                 | PWR        | Ground pin for the CPU outputs                                                                  |

| 33<br>34 | VDDCPU                 | PWR        | Supply for CPU clocks, 3.3V nominal                                                             |

|          | CPUCLK8C2<br>CPUCLK8T2 | OUT        | Complementary clock of differential 3.3V push-pull K8 pair.                                     |

| 35       |                        | OUT        | True clock of differential 3.3V push-pull K8 pair.                                              |

| 36       | GNDCPU                 | PWR<br>PWR | Ground pin for the CPU outputs                                                                  |

| 37       | VDDCPU                 |            | Supply for CPU clocks, 3.3V nominal Complementary clock of differential 3.3V push-pull K8 pair. |

| 38<br>39 | CPUCLK8C1<br>CPUCLK8T1 | OUT        | True clock of differential 3.3V push-pull K8 pair.                                              |

| 40       | GNDCPU                 | PWR        | Ground pin for the CPU outputs                                                                  |

| 41       | VDDCPU                 | PWR        | Supply for CPU clocks, 3.3V nominal                                                             |

| 42       | CPUCLK8C0              | OUT        | Complementary clock of differential 3.3V push-pull K8 pair.                                     |

| 43       | CPUCLK8T0              | OUT        | True clock of differential 3.3V push-pull K8 pair.                                              |

| 44       | GND                    | PWR        | Ground pin.                                                                                     |

| 45       | FS2                    | IN         | Frequency select pin.                                                                           |

| 46       | FS1/REF1               | I/O        | Frequency select pin.  Frequency select latch input pin / 14.318 MHz reference clock.           |

| 47       | FS0/REF0               | I/O        | Frequency select latch input pin / 14.318 MHz reference clock.                                  |

| 48       | VDDREF                 | PWR        | Ref, XTAL power supply, nominal 3.3V                                                            |

| ŦŪ       | 1 2 D I IL I           | 1 4411     | rior, Attac power ouppry, norminal olov                                                         |

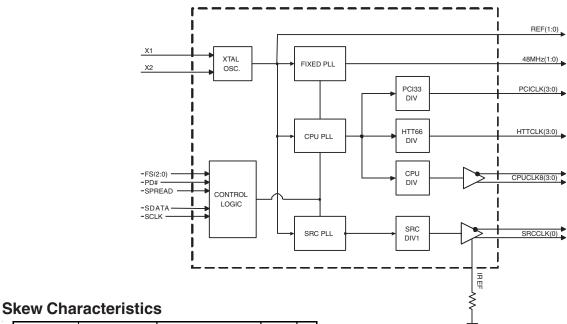

#### **General Description**

The ICS932S801 is a main clock synthesizer chip that, when paired with ICS9DB108, provides all clocks required by Serverworks GC-HT-based servers.

An SMBus interface allows full control of the device.

### **Block Diagram**

| 5                | kew Cha        | racteristics       | 5                                                                     |                |      |

|------------------|----------------|--------------------|-----------------------------------------------------------------------|----------------|------|

|                  | Parameter      | Description        | Test Conditions                                                       | Skew<br>Window | Unit |

| T<br>i<br>m<br>e | Tsk_CPU_CPU    | CPU to CPU Skew    | Measured at crossing points of CPUCLKT rising edges                   | 250            | ps   |

| I<br>n<br>d      | Tsk_CPU_PCI    | CPU to PCI skew    | Meastured at crossing point<br>for CPUCLKT and 1.5V for<br>PCI clock  | 2000           | ps   |

| e<br>p<br>e      | Tsk_PCl33-HT66 | PCI33 to HT66 skew | Measured between rising edges at 1.5V                                 | 500            | ps   |

| n<br>e<br>n<br>t | Tsk_CPU_HT66   | CPU to HT66 skew   | Meastured at crossing point<br>for CPUCLKT and 1.5V for<br>HT66 clock | 2000           | ps   |

| T<br>i           | Tsk_CPU_CPU    | CPU to CPU Skew    | Measured at crossing points of CPUCLKT rising edges                   | 200            | ps   |

| m<br>e<br>V      | Tsk_CPU_PCI    | CPU to PCI skew    | Meastured at crossing point<br>for CPUCLKT and 1.5V for<br>PCI clock  | 200            | ps   |

| a<br>r<br>i<br>a | Tsk_PCl33-HT66 | PCI33 to HT66 skew | Measured between rising edges at 1.5V                                 | 200            | ps   |

| n<br>t           | Tsk_CPU_HT66   | CPU to HT66 skew   | Meastured at crossing point<br>for CPUCLKT and 1.5V for<br>HT66 clock | 200            | ps   |

**Table1: SRC Frequency Selection Table**

|                |                | .,              |

|----------------|----------------|-----------------|

| SRCFS1<br>B5b3 | SRCFS0<br>B5b2 | SRCCLK<br>(MHz) |

| 0              | 0              | 100.00          |

| 0              | 1              | 101.00          |

| 1              | 0              | 102.00          |

| 1              | 1              | 104.00          |

**Table 2: CPU Divider Ratios**

|         | Divider (3:2) |         |     |         |     |         |     |         |     |  |  |

|---------|---------------|---------|-----|---------|-----|---------|-----|---------|-----|--|--|

|         | Bit           | 00      |     | 01      |     | 10      |     | 11      | MSB |  |  |

| (1:0)   | 00            | 0000    | 2   | 0100    | 4   | 1000    | 8   | 1100    | 16  |  |  |

|         | 01            | 0001    | 3   | 0101    | 6   | 1001    | 12  | 1101    | 24  |  |  |

| ide     | 10            | 0010    | 5   | 0110    | 10  | 1010    | 20  | 1110    | 40  |  |  |

| Divider | 11            | 0011    | 15  | 0111    | 30  | 1011    | 60  | 1111    | 120 |  |  |

|         | LSB           | Address | Div | Address | Div | Address | Div | Address | Div |  |  |

**Table 3: HTT Divider Ratios**

|         | Divider (3:2) |         |     |         |     |         |     |         |     |  |

|---------|---------------|---------|-----|---------|-----|---------|-----|---------|-----|--|

| )       | Bit           | 00      |     | 01      |     | 10      |     | 11      | MSB |  |

| (1:0)   | 00            | 0000    | 4   | 0100    | 8   | 1000    | 16  | 1100    | 32  |  |

|         | 01            | 0001    | 3   | 0101    | 6   | 1001    | 12  | 1101    | 24  |  |

| Divider | 10            | 0010    | 5   | 0110    | 10  | 1010    | 20  | 1110    | 40  |  |

| Ņ       | 11            | 0011    | 15  | 0111    | 30  | 1011    | 60  | 1111    | 120 |  |

|         | LSB           | Address | Div | Address | Div | Address | Div | Address | Div |  |

**Table 4: SRC Divider Ratios**

|         |     |         |     |         | Divider (3:2 | 2)      |     |         |     |

|---------|-----|---------|-----|---------|--------------|---------|-----|---------|-----|

| (       | Bit | 00      |     | 01      |              | 10      |     | 11      | MSB |

| (1:0)   | 00  | 0000    | 2   | 0100    | 4            | 1000    | 8   | 1100    | 16  |

|         | 01  | 0001    | 3   | 0101    | 6            | 1001    | 12  | 1101    | 24  |

| ide     | 10  | 0010    | 5   | 0110    | 10           | 1010    | 20  | 1110    | 40  |

| Divider | 11  | 0011    | 7   | 0111    | 14           | 1011    | 28  | 1111    | 56  |

| ]       | LSB | Address | Div | Address | Div          | Address | Div | Address | Div |

### **Absolute Maximum Ratings**

Logic Inputs . . . . . . . . . . . . GND –0.5 V to  $\,$  V  $_{DD}$  +3.8 V

ESD Protection ...... Input ESD protection usung human body model > 1KV

Stresses above those listed under *Absolute Maximum Ratings* may cause permanent damage to the device. These ratings are stress specifications only and functional operation of the device at these or any other conditions above those listed in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect product reliability.

#### **Electrical Characteristics - Input/Supply/Common Output Parameters**

$T_A = 0 - 70$ °C; Supply Voltage  $V_{DD} = 3.3 \text{ V +/-5}\%$

| PARAMETER                                       | SYMBOL               | CONDITIONS                                                        | MIN                   | TYP      | MAX                   | UNITS | NOTES |

|-------------------------------------------------|----------------------|-------------------------------------------------------------------|-----------------------|----------|-----------------------|-------|-------|

| Input High Voltage                              | V <sub>IH</sub>      | 3.3 V +/-5%                                                       | 2                     |          | V <sub>DD</sub> + 0.3 | >     | 1     |

| Input Low Voltage                               | V <sub>IL</sub>      | 3.3 V +/-5%                                                       | V <sub>SS</sub> - 0.3 |          | 0.8                   | ٧     | 1     |

| Input High Current                              | I <sub>IH</sub>      | $V_{IN} = V_{DD}$                                                 | -5                    |          | 5                     | uA    | 1     |

| Input Low Current                               | I <sub>IL1</sub>     | V <sub>IN</sub> = 0 V; Inputs with no pull-up resistors           | -5                    |          |                       | uA    | 1     |

| mpat zow danoni                                 | I <sub>IL2</sub>     | V <sub>IN</sub> = 0 V; Inputs with pull-up resistors              | -200                  |          |                       | uA    | 1     |

| Operating Current                               | I <sub>DD3.3OP</sub> | all outputs driven                                                |                       |          | 325                   | mA    |       |

| Powerdown Current                               | I <sub>DD3.3PD</sub> |                                                                   |                       |          | 100                   | mA    |       |

| Input Frequency <sup>3</sup>                    | Fi                   | $V_{DD} = 3.3 \text{ V}$                                          |                       | 14.31818 |                       | MHz   | 3     |

| Pin Inductance <sup>1</sup>                     | $L_{pin}$            |                                                                   |                       |          | 7                     | nΗ    | 1     |

|                                                 | C <sub>IN</sub>      | Logic Inputs                                                      |                       |          | 5                     | pF    | 1     |

| Input Capacitance <sup>1</sup>                  | C <sub>OUT</sub>     | Output pin capacitance                                            |                       |          | 6                     | pF    | 1     |

|                                                 | C <sub>INX</sub>     | X1 & X2 pins                                                      |                       |          | 5                     | pF    | 1     |

| Clk Stabilization <sup>1,2</sup>                | T <sub>STAB</sub>    | From V <sub>DD</sub> Power-Up or de-assertion of PD# to 1st clock |                       |          | 3                     | ms    | 1,2   |

| Modulation Frequency                            |                      | Triangular Modulation                                             | 30                    |          | 33                    | kHz   | 1     |

| SMBus Voltage                                   | $V_{DD}$             |                                                                   | 2.7                   |          | 5.5                   | >     | 1     |

| Low-level Output Voltage                        | $V_{OL}$             | @ I <sub>PULLUP</sub>                                             |                       |          | 0.4                   | ٧     | 1     |

| Current sinking at V <sub>OL</sub> = 0.4 V      | I <sub>PULLUP</sub>  |                                                                   | 4                     |          |                       | mA    | 1     |

| SCLK/SDATA<br>Clock/Data Rise Time <sup>3</sup> | T <sub>RI2C</sub>    | (Max VIL - 0.15) to (Min VIH + 0.15)                              |                       |          | 1000                  | ns    | 1     |

| SCLK/SDATA<br>Clock/Data Fall Time <sup>3</sup> | T <sub>FI2C</sub>    | (Min VIH + 0.15) to (Max VIL - 0.15)                              |                       |          | 300                   | ns    | 1     |

<sup>&</sup>lt;sup>1</sup>Guaranteed by design and characterization, not 100% tested in production.

<sup>&</sup>lt;sup>2</sup>See timing diagrams for timing requirements.

<sup>&</sup>lt;sup>3</sup> Input frequency should be measured at the REFOUT pin and tuned to ideal 14.31818MHz to meet ppm frequency accuracy on PLL outputs.

#### **Electrical Characteristics - K8 Push Pull Differential Pair**

$T_A = 0 - 70$ °C;  $V_{DD} = 3.3 \text{ V +/-5\%}$ ;  $C_L = AMD64 \text{ Processor Test Load}$

| PARAMETER                                   | SYMBOL                | CONDITIONS                                                                                                                                                          | MIN   | TYP  | MAX  | UNITS | NOTES |

|---------------------------------------------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|------|-------|-------|

| Rising Edge Rate                            | $\delta V/\delta t$   | Measured at the AMD64 processor's test load. 0 V +/- 400 mV (differential                                                                                           | 2     |      | 10   | V/ns  | 1     |

| Falling Edge Rate                           | $\delta V/\delta t$   | measurement)                                                                                                                                                        | 2     |      | 10   | V/ns  | 1     |

| Differential Voltage                        | $V_{DIFF}$            |                                                                                                                                                                     | 0.4   | 1.25 | 2.3  | V     | 1     |

| Change in V <sub>DIFF_DC</sub><br>Magnitude | $\Delta V_{DIFF}$     | Measured at the AMD64 processor's                                                                                                                                   | -150  |      | 150  | mV    | 1     |

| Common Mode Voltage                         | $V_{CM}$              | test load. (single-ended measurement)                                                                                                                               | 1.05  | 1.25 | 1.45 | V     | 1     |

| Change in Common<br>Mode Voltage            | $\Delta V_{CM}$       |                                                                                                                                                                     | -200  |      | 200  | mV    | 1     |

| Jitter, Cycle to cycle                      | t <sub>jcyc-cyc</sub> | Measurement from differential wavefrom. Maximum difference of cycle time between 2 adjacent cycles.                                                                 | 0     | 100  | 200  | ps    | 1     |

| Jitter, Accumulated                         | t <sub>ja</sub>       | Measured using the JIT2 software package with a Tek 7404 scope. TIE (Time Interval Error) measurement technique: Sample resolution = 50 ps, Sample Duration = 10 µs | -1000 |      | 1000 |       | 1,2,3 |

| Duty Cycle                                  | d <sub>t3</sub>       | Measurement from differential wavefrom                                                                                                                              | 45    |      | 53   | %     | 1     |

| Output Impedance                            | R <sub>ON</sub>       | Average value during switching transition. Used for determining series termination value.                                                                           | 15    | 35   | 55   | Ω     | 1     |

| Group Skew                                  | t <sub>src-skew</sub> | Measurement from differential wavefrom                                                                                                                              |       |      | 250  | ps    | 1     |

<sup>&</sup>lt;sup>1</sup>Guaranteed by design and characterization, not 100% tested in production.

<sup>&</sup>lt;sup>2</sup> All accumulated jitter specifications are guaranteed assuming that REF is at 14.31818MHz

<sup>&</sup>lt;sup>3</sup> Spread Spectrum is off

#### **Electrical Characteristics - SRC 0.7V Current Mode Differential Pair**

$T_{A} = 0 - 70^{\circ}C; \ V_{DD} = 3.3 \ V \ + / -5\%; \ C_{L} = 2pF, \ R_{S} = 33.2\Omega, \ R_{P} = 49.9\Omega, \ I_{REF} = 475\Omega$

| , , ,                           | 1                         | LDI , 115-00.222, 115-40.022, 1REF = 1                   | 1      |         |         |       |       |

|---------------------------------|---------------------------|----------------------------------------------------------|--------|---------|---------|-------|-------|

| PARAMETER                       | SYMBOL                    | CONDITIONS                                               | MIN    | TYP     | MAX     | UNITS | NOTES |

| Current Source Output Impedance | Zo                        | $V_O = V_x$                                              | 3000   |         |         | Ω     | 1     |

| Voltage High                    | VHigh                     | Statistical measurement on                               | 660    |         | 850     | mV    | 1,3   |

| Voltage Low                     | VLow                      | single ended signal using oscilloscope math function.    | -150   |         | 150     | IIIV  | 1,3   |

| Max Voltage                     | Vovs                      | Measurement on single ended                              |        |         | 1150    | \/    | 1     |

| Min Voltage                     | Vuds                      | signal using absolute value.                             | -300   |         |         | mV    | 1     |

| Crossing Voltage (abs)          | Vcross(abs)               |                                                          | 250    | 350     | 550     | mV    | 1     |

| Crossing Voltage (var)          | d-Vcross                  | Variation of crossing over all edges                     |        | 12      | 140     | mV    | 1     |

| Long Accuracy                   | ppm                       | see Tperiod min-max values                               | -300   |         | 300     | ppm   | 1,2   |

| Average period                  | Tperiod                   | 100.00 MHz nominal                                       | 9.9970 | 10.0000 | 10.0030 | ns    | 2     |

| Average period                  | rpenou                    | 100.00 MHz spread                                        | 9.9970 |         | 10.0530 | ns    | 2     |

| Absolute min period             | Tabsmin                   | @100.00MHz nominal/spread                                | 9.8720 |         |         | ns    | 1,2   |

| Rise Time                       | t <sub>r</sub>            | $V_{OL} = 0.175V, V_{OH} = 0.525V$                       | 175    |         | 700     | ps    | 1     |

| Fall Time                       | t <sub>f</sub>            | $V_{OH} = 0.525 V V_{OL} = 0.175 V$                      | 175    |         | 700     | ps    | 1     |

| Rise Time Variation             | d-t <sub>r</sub>          |                                                          |        | 30      | 125     | ps    | 1     |

| Fall Time Variation             | d-t <sub>f</sub>          |                                                          |        | 30      | 125     | ps    | 1     |

| Duty Cycle                      | d <sub>t3</sub>           | Measurement from differential wavefrom                   | 45     |         | 55      | %     | 1     |

| Group Skew                      | t <sub>src-skew</sub>     | Measurement from differential wavefrom                   |        |         | N/A     | ps    |       |

| Jitter, Phase                   | t                         | PCI Express Gen 1 phase jitter<br>CPU=200MHz, Spread off |        | 38      | 86      | ps    | 1, 4  |

| Jillei, Filase                  | <sup>t</sup> jphase-pcie1 | PCI Express Gen 1 phase jitter<br>CPU=200MHz, Spread on  |        | 52      | 86      | ps    | 1, 4  |

| Jitter, Cycle to cycle          | t <sub>jcyc-cyc</sub>     | Measurement from differential wavefrom                   |        |         | 100     | ps    | 1     |

<sup>&</sup>lt;sup>1</sup>Guaranteed by design and characterization, not 100% tested in production.

<sup>&</sup>lt;sup>2</sup> All Long Term Accuracy and Clock Period specifications are guaranteed assuming that REF is at 14.31818MHz

$<sup>^{3}</sup>I_{REF} = V_{DD}/(3xR_{R}). \ \, \text{For} \, R_{R} = 475\Omega \, (1\%), \, I_{REF} = 2.32\text{mA}. \, \, I_{OH} = 6 \, x \, I_{REF} \, \text{and} \, \, V_{OH} = 0.7V \, \, \text{@} \, \, Z_{O} = 50\Omega.$

<sup>&</sup>lt;sup>4</sup>Per PCI SIG method for PCI Express Gen 1. Visit http://www.pcisig.com for details.

#### Electrical Characteristics - PCICLK 33 MHz, HTTCLK 66 MHz Clocks

$T_A = 0 - 70$ °C; VDD=3.3V +/-5%;  $C_L = 20$  pF (unless otherwise specified)

| PARAMETER              | SYMBOL                | CONDITIONS                      | MIN     | TYP | MAX     | UNITS | Notes |

|------------------------|-----------------------|---------------------------------|---------|-----|---------|-------|-------|

| Long Accuracy          | ppm                   | see Tperiod min-max values      | -300    |     | 300     | ppm   | 1,2   |

| PCI33 Clock period     | $T_{period}$          | 33.33MHz output nominal         | 29.9910 |     | 30.0090 | ns    | 2     |

| 1 0100 Clock period    | ' period              | 33.33MHz output spread          | 29.9910 |     | 30.1598 | ns    | 2     |

| HTT66 Clock period     | $T_{period}$          | 66.67MHz output nominal         | 14.9955 |     | 15.0045 | ns    | 2     |

| 111 Too Clock period   | period .              | 66.67MHz output spread          | 14.9955 |     | 15.0799 | ns    | 2     |

| Output High Voltage    | V <sub>OH</sub>       | $I_{OH} = -1 \text{ mA}$        | 2.4     |     |         | ٧     | 1     |

| Output Low Voltage     | $V_{OL}$              | I <sub>OL</sub> = 1 mA          |         |     | 0.55    | V     | 1     |

| Output High Current    |                       | V <sub>OH</sub> @MIN = 1.0 V    | -33     |     |         | mA    | 1     |

| Output High Current    | I <sub>OH</sub>       | V <sub>OH</sub> @ MAX = 3.135 V |         |     | -33     | mA    | 1     |

| Output Low Current     | L                     | V <sub>OL</sub> @ MIN = 1.95 V  | 30      |     |         | mA    | 1     |

| Output Low Gurrent     | I <sub>OL</sub>       | $V_{OL}$ @ MAX = 0.4 V          |         |     | 38      | mA    | 1     |

| Edge Rate              | $\delta V/\delta t$   | Rising edge rate                | 1       |     | 4       | V/ns  | 1     |

| Edge Rate              | $\delta V/\delta t$   | Falling edge rate               | 1       |     | 4       | V/ns  | 1     |

| Duty Cycle             | d <sub>t1</sub>       | $V_T = 1.5 \text{ V}$           | 45      |     | 55      | %     | 1     |

| Skew                   | t <sub>sk1</sub>      | $V_{T} = 1.5 \text{ V}$         |         |     | 200     | ps    | 1     |

| Jitter, Cycle to cycle | t <sub>jcyc-cyc</sub> | V <sub>T</sub> = 1.5 V          |         |     | 250     | ps    | 1     |

<sup>&</sup>lt;sup>1</sup>Guaranteed by design and characterization, not 100% tested in production.

#### **Electrical Characteristics - 48MHz**

$T_A = 0 - 70$ °C;  $V_{DD} = 3.3 \text{ V +/-5\%}$ ;  $C_L = 20 \text{ pF}$  (unless otherwise specified)

| PARAMETER              | SYMBOL                | CONDITIONS                      | MIN     | TYP | MAX     | UNITS    | Notes |

|------------------------|-----------------------|---------------------------------|---------|-----|---------|----------|-------|

| Long Accuracy          | ppm                   | see Tperiod min-max values      | -100    |     | 100     | ppm      | 1,2   |

| Clock period           | $T_{period}$          | 48.00MHz output nominal         | 20.8257 |     | 20.8340 | ns       | 2     |

| Output High Voltage    | $V_{OH}$              | $I_{OH} = -1 \text{ mA}$        | 2.4     |     |         | <b>V</b> | 1     |

| Output Low Voltage     | $V_{OL}$              | $I_{OL} = 1 \text{ mA}$         |         |     | 0.55    | V        | 1     |

| Output High Current    |                       | V <sub>OH</sub> @ MIN = 1.0 V   | -33     |     |         | mA       | 1     |

| Output High Current    | Іон                   | V <sub>OH</sub> @ MAX = 3.135 V |         |     | -33     | mA       | 1     |

| Outrout Law Commant    | -                     | V <sub>OL</sub> @MIN = 1.95 V   | 30      |     |         | mA       | 1     |

| Output Low Current     | I <sub>OL</sub>       | V <sub>OL</sub> @ MAX = 0.4 V   |         |     | 38      | mA       | 1     |

| Edge Rate              | $\delta V/\delta t$   | Rising edge rate                | 1       |     | 4       | V/ns     | 1     |

| Edge Rate              | $\delta V/\delta t$   | Falling edge rate               | 1       |     | 4       | V/ns     | 1     |

| Duty Cycle             | d <sub>t1</sub>       | V <sub>T</sub> = 1.5 V          | 45      |     | 55      | %        | 1     |

| Skew                   | t <sub>sk1</sub>      | $V_{T} = 1.5 \text{ V}$         |         |     | 50      | ps       | 1     |

| Jitter, Cycle to cycle | t <sub>jcyc-cyc</sub> | $V_{T} = 1.5 \text{ V}$         |         |     | 200     | ps       | 1     |

<sup>&</sup>lt;sup>1</sup>Guaranteed by design and characterization, not 100% tested in production.

<sup>&</sup>lt;sup>2</sup> All Long Term Accuracy and Clock Period specifications are guaranteed with the assumption that REF is at 14.31818MHz

<sup>&</sup>lt;sup>2</sup> All Long Term Accuracy and Clock Period specifications are guaranteed with the assumption that REF is at 14.31818MHz

#### **Electrical Characteristics - REF-14.318MHz**

$T_A = 0 - 70$ °C;  $V_{DD} = 3.3 \text{ V +/-5\%}$ ;  $C_L = 27 \text{ pF}$  (unless otherwise specified)

| 7 00                   |                       | . ,                                              |         |     |         |       |       |

|------------------------|-----------------------|--------------------------------------------------|---------|-----|---------|-------|-------|

| PARAMETER              | SYMBOL                | CONDITIONS                                       | MIN     | TYP | MAX     | UNITS | Notes |

| Long Accuracy          | ppm                   | see Tperiod min-max values                       | -300    |     | 300     | ppm   | 1     |

| Clock period           | $T_{period}$          | 14.318MHz output nominal                         | 69.8270 |     | 69.8550 | ns    | 2     |

| Output High Voltage    | V <sub>OH</sub>       | $I_{OH} = -1 \text{ mA}$                         | 2.4     |     |         | V     | 1     |

| Output Low Voltage     | $V_{OL}$              | $I_{OL} = 1 \text{ mA}$                          |         |     | 0.4     | V     | 1     |

| Output High Current    | I <sub>OH</sub>       | $V_{OH}$ @ MIN = 1.0 V, $V_{OH}$ @ MAX = 3.135 V | -29     |     | -23     | mA    | 1     |

| Output Low Current     | I <sub>OL</sub>       | $V_{OL}$ @MIN = 1.95 V,<br>$V_{OL}$ @MAX = 0.4 V | 29      |     | 27      | mA    | 1     |

| Edge Rate              | $\delta V/\delta t$   | Rising edge rate                                 | 1       |     | 2       | V/ns  | 1     |

| Edge Rate              | $\delta V/\delta t$   | Falling edge rate                                | 1       |     | 2       | V/ns  | 1     |

| Duty Cycle             | d <sub>t1</sub>       | $V_{T} = 1.5 V$                                  | 45      |     | 55      | %     | 1     |

| Skew                   | t <sub>sk1</sub>      | $V_{T} = 1.5 V$                                  |         |     | 50      | ps    | 1     |

| Jitter, Cycle to cycle | t <sub>icyc-cyc</sub> | $V_{T} = 1.5 \text{ V}$                          |         |     | 1000    | ps    | 1     |

<sup>&</sup>lt;sup>1</sup>Guaranteed by design and characterization, not 100% tested in production.

<sup>&</sup>lt;sup>2</sup> All Long Term Accuracy and Clock Period specifications are guaranteed with the assumption that REF is at 14.31818MHz

#### General SMBus serial interface information

#### **How to Write:**

- · Controller (host) sends a start bit.

- Controller (host) sends the write address D2 (H)

- ICS clock will acknowledge

- Controller (host) sends the begining byte location = N

- ICS clock will acknowledge

- Controller (host) sends the data byte count = X

- ICS clock will acknowledge

- Controller (host) starts sending Byte N through Byte N + X -1 (see Note 2)

- ICS clock will acknowledge each byte one at a time

- · Controller (host) sends a Stop bit

| Inc   | dex Block V                 | ۷rit     | e Operation          |

|-------|-----------------------------|----------|----------------------|

| Cor   | ntroller (Host)             |          | ICS (Slave/Receiver) |

| T     | starT bit                   |          |                      |

| Slav  | e Address D2 <sub>(H)</sub> |          |                      |

| WR    | WRite                       |          |                      |

|       |                             |          | ACK                  |

| Begi  | inning Byte = N             |          |                      |

|       |                             |          | ACK                  |

| Data  | Byte Count = X              |          |                      |

|       |                             |          | ACK                  |

| Begir | nning Byte N                |          |                      |

|       |                             |          | ACK                  |

|       | 0                           | ţ        |                      |

|       | 0                           | X Byte   | 0                    |

|       | 0                           | $\times$ | 0                    |

|       |                             |          | 0                    |

| Byte  | e N + X - 1                 |          |                      |

|       |                             |          | ACK                  |

| Р     | stoP bit                    |          |                      |

#### How to Read:

- · Controller (host) will send start bit.

- Controller (host) sends the write address D2 (H)

- ICS clock will acknowledge

- Controller (host) sends the begining byte location = N

- ICS clock will acknowledge

- Controller (host) will send a separate start bit.

- Controller (host) sends the read address D3 (H)

- ICS clock will acknowledge

- ICS clock will send the data byte count = X

- ICS clock sends Byte N + X -1

- ICS clock sends Byte 0 through byte X (if X<sub>(H)</sub> was written to byte 8).

- · Controller (host) will need to acknowledge each byte

- · Controllor (host) will send a not acknowledge bit

- · Controller (host) will send a stop bit

| In    | dex Block Rea               | ad     | Operation          |

|-------|-----------------------------|--------|--------------------|

| Cor   | troller (Host)              | IC     | S (Slave/Receiver) |

| T     | starT bit                   |        |                    |

|       | e Address D2 <sub>(H)</sub> |        |                    |

| WR    | WRite                       |        |                    |

|       |                             |        | ACK                |

| Begi  | nning Byte = N              |        |                    |

|       | -                           |        | ACK                |

| RT    | Repeat starT                |        |                    |

| Slave | e Address D3 <sub>(H)</sub> |        |                    |

| RD    | ReaD                        |        |                    |

|       |                             |        | ACK                |

|       |                             |        |                    |

|       |                             |        | ata Byte Count = X |

|       | ACK                         |        |                    |

|       |                             |        | Beginning Byte N   |

|       | ACK                         |        |                    |

|       |                             | X Byte | 0                  |

|       | 0                           | B      | 0                  |

|       | 0                           | ×      | 0                  |

|       | . 0                         |        |                    |

|       |                             |        | Byte N + X - 1     |

| N     | Not acknowledge             |        |                    |

| Р     | stoP bit                    |        |                    |

**SMBus Table: Frequency Select and Spread Control Register**

| Byt   |          | Pin # | Name      | Control Function                                              | Туре | 0                 | 1             | PWD     |

|-------|----------|-------|-----------|---------------------------------------------------------------|------|-------------------|---------------|---------|

| Bit 7 | <u> </u> | -     | FS Source | Latched Input or SMBus<br>Frequency Select                    |      | Latched<br>Inputs | SMBus         | 0       |

| Bit 6 |          | -     | CPU SS_EN | Spread Enable for CPU and SRC PLLs. Setting SPREAD EN to '1', | RW   | OFF               | ON            | 0       |

| Bit 5 |          | -     | SRC SS_EN | forces Spread ON for both PLLs.                               | RW   | OFF               | ON            | 0       |

| Bit 4 |          | -     | Reserved  | Reserved                                                      | RW   | Reserved          | Reserved      | 0       |

| Bit 3 |          | -     | FS3       | Freq Select Bit 3                                             | RW   |                   |               | 0       |

| Bit 2 |          | -     | FS2       | Freq Select Bit 2                                             | RW   | See Functiona     | lity Table on | Latched |

| Bit 1 |          | -     | FS1       | Freq Select Bit 1                                             | RW   | Page              | e 1           | Latched |

| Bit 0 |          | -     | FS0       | Freq Select Bit 0                                             | RW   |                   |               | Latched |

**SMBus Table: Output Control Register**

| CIVIDA | o i abi | c. Outpe | it control ricgist | <u>Ci</u>        |      |               |        |     |

|--------|---------|----------|--------------------|------------------|------|---------------|--------|-----|

| Byt    | e 1     | Pin #    | Name               | Control Function | Type | 0             | 1      | PWD |

| Bit 7  |         |          | PCICLK3            | Output Enable    | RW   | Disable (Low) | Enable | 1   |

| Bit 6  |         |          | PCICLK2            | Output Enable    | RW   | Disable (Low) | Enable | 1   |

| Bit 5  |         |          | PCICLK1            | Output Enable    | RW   | Disable (Low) | Enable | 1   |

| Bit 4  |         |          | PCICLK0            | Output Enable    | RW   | Disable (Low) | Enable | 1   |

| Bit 3  |         |          | HTTCLK3            | Output Enable    | RW   | Disable (Low) | Enable | 1   |

| Bit 2  |         |          | HTTCLK2            | Output Enable    | RW   | Disable (Low) | Enable | 1   |

| Bit 1  |         |          | HTTCLK1            | Output Enable    | RW   | Disable (Low) | Enable | 1   |

| Bit 0  |         |          | HTTCLK0            | Output Enable    | RW   | Disable (Low) | Enable | 1   |

**SMBus Table: Output Control Register**

|       | <del> </del> |       | at contact ricgist | <b>V</b> .       |      |               |        |     |

|-------|--------------|-------|--------------------|------------------|------|---------------|--------|-----|

| By    | te 2         | Pin # | Name               | Control Function | Туре | 0             | 1      | PWD |

| Bit 7 |              |       | 48MHz_1            | Output Enable    | RW   | Disable (Low) | Enable | 1   |

| Bit 6 |              |       | 48MHz_0            | Output Enable    | RW   | Disable (Low) | Enable | 1   |

| Bit 5 |              |       | REF1               | Output Enable    | RW   | Disable (Low) | Enable | 1   |

| Bit 4 |              |       | REF0               | Output Enable    | RW   | Disable (Low) | Enable | 1   |

| Bit 3 |              |       | CPUCLK8(3)         | Output Enable    | RW   | Disable       | Enable | 1   |

| Bit 2 |              |       | CPUCLK8(2)         | When Disabled    | RW   | Disable       | Enable | 1   |

| Bit 1 |              | ·     | CPUCLK8(1)         | CPUCLKT = 0      | RW   | Disable       | Enable | 1   |

| Bit 0 |              | ·     | CPUCLK8(0)         | CPUCLKC = 1      | RW   | Disable       | Enable | 1   |

SMBus Table: SRCCLK(0) Output Control Register

| By    | te 3 | Pin # | Name       | Control Function                | Туре | 0              | 1        | PWD |

|-------|------|-------|------------|---------------------------------|------|----------------|----------|-----|

| Bit 7 |      | -     | Reserved   | Reserved                        | RW   | Reserved       | Reserved | 0   |

| Bit 6 |      | -     | Reserved   | Reserved                        | RW   | Reserved       | Reserved | 0   |

| Bit 5 |      | -     | Reserved   | Reserved                        | RW   | Reserved       | Reserved | 0   |

| Bit 4 |      | -     | Reserved   | Reserved                        | RW   | Reserved       | Reserved | 0   |

| Bit 3 |      | -     | Reserved   | Reserved                        | RW   | Reserved       | Reserved | 0   |

| Bit 2 |      | -     | Reserved   | Reserved                        | RW   | Reserved       | Reserved | 0   |

| Bit 1 |      | -     | SRCCLK0 PD | SRCCLK Power Down<br>Drive Mode | RW   | Driven         | Hi-Z     | 0   |

| Bit 0 |      |       | SRCCLK0    | Output Enable                   | RW   | Disable (Hi-Z) | Enable   | 1   |

SMBus Table: 48MHz Drive Strength Control Register

| Byt   | te 4 | Pin # | Name       | Control Function       | Туре | 0        | 1        | PWD |

|-------|------|-------|------------|------------------------|------|----------|----------|-----|

| Bit 7 |      | -     | Reserved   | Reserved               | RW   | Reserved | Reserved | 0   |

| Bit 6 |      | -     | Reserved   | Reserved               | RW   | Reserved | Reserved | 0   |

| Bit 5 |      | -     | Reserved   | Reserved               | RW   | Reserved | Reserved | 0   |

| Bit 4 |      | -     | Reserved   | Reserved               | RW   | Reserved | Reserved | 0   |

| Bit 3 |      | -     | Reserved   | Reserved               | RW   | Reserved | Reserved | 0   |

| Bit 2 |      | -     | Reserved   | Reserved               | RW   | Reserved | Reserved | 0   |

| Bit 1 |      | 5     | 48MHz_1 DS | Drive Strength Control | RW   | 1X       | 2X       | 0   |

| Bit 0 |      | 4     | 48MHz_0 DS | Drive Strength Control | RW   | 1X       | 2X       | 0   |

SMBus Table: SRC Frequency Select Register

| By    | te 5 | Pin # | Name     | Control Function | Type | 0                 | 1          | PWD |

|-------|------|-------|----------|------------------|------|-------------------|------------|-----|

| Bit 7 |      | -     | Reserved | Reserved         | RW   | Reserved          | Reserved   | 0   |

| Bit 6 |      | -     | Reserved | Reserved         | RW   | Reserved          | Reserved   | 0   |

| Bit 5 |      | -     | Reserved | Reserved         | RW   | Reserved Reserved |            | 0   |

| Bit 4 |      | -     | Reserved | Reserved         | RW   | Reserved          | Reserved   | 0   |

| Bit 3 |      | -     | SRCFS1   | SRC FS bit 1     | RW   | See Tal           | ble 1:     | 0   |

| Bit 2 |      | -     | SRCFS0   | SRC FS bit 0     | RW   | SRC Freque        | ncy Select | 0   |

| Bit 1 |      | -     | Reserved | Reserved         | RW   | Reserved          | Reserved   | 0   |

| Bit 0 |      | -     | Reserved | Reserved         | RW   | Reserved          | Reserved   | 0   |

**SMBus Table: Device ID Register**

| 01111111 | , . a.b.o. |       | TID Hegiotei |                  |      |   |   |     |

|----------|------------|-------|--------------|------------------|------|---|---|-----|

| Byt      | te 6       | Pin # | Name         | Control Function | Туре | 0 | 1 | PWD |

| Bit 7    | -          |       | DevID 7      | Device ID MSB    | R    | - | - | 1   |

| Bit 6    | -          |       | DevID 6      | Device ID 6      | R    | - | - | 0   |

| Bit 5    | -          |       | DevID 5      | Device ID 5      | R    | - | - | 0   |

| Bit 4    | -          |       | DevID 4      | Device ID4       | R    | - | - | 0   |

| Bit 3    | -          |       | DevID 3      | Device ID3       | R    | - | - | 0   |

| Bit 2    | -          |       | DevID 2      | Device ID2       | R    | - | - | 0   |

| Bit 1    | -          |       | DevID 1      | Device ID1       | R    | - | - | 0   |

| Bit 0    | -          | _     | DevID 0      | Device ID LSB    | R    | - | - | 1   |

**SMBus Table: Vendor ID Register**

| Byt   |   | # Nam |          | Control Function | Туре | 0 | 1 | PWD |

|-------|---|-------|----------|------------------|------|---|---|-----|

| Bit 7 | - | RID   | 3        |                  | R    | - | - | Χ   |

| Bit 6 | - | RID2  | 2        | Revision ID      | R    | - | - | Χ   |

| Bit 5 | - | RID1  |          | nevision ib      | R    | - | - | Χ   |

| Bit 4 | - | RIDO  | )        |                  | R    | - | - | Χ   |

| Bit 3 | - | VID3  | }        |                  | R    | - | - | 0   |

| Bit 2 | - | VID2  | <u> </u> | VENDOR ID        | R    | - | - | 0   |

| Bit 1 | - | VID1  |          | (0001 = ICS)     | R    | - | - | 0   |

| Bit 0 | - | VIDO  | )        |                  | R    | - | - | 1   |

**SMBus Table: Byte Count Register**

| Byt   | te 8 | Pin # | Name | Control Function       | Туре | 0               | 1              | PWD |

|-------|------|-------|------|------------------------|------|-----------------|----------------|-----|

| Bit 7 |      | -     | BC7  |                        | RW   |                 |                | 0   |

| Bit 6 |      | -     | BC6  |                        | RW   |                 |                | 0   |

| Bit 5 |      | -     | BC5  |                        | RW   | Writing to this | register will  | 0   |

| Bit 4 |      | -     | BC4  | Byte Count Programming | RW   | configure how   | many bytes     | 0   |

| Bit 3 |      | -     | BC3  | b(7:0)                 | RW   | will be read ba | ck, default is | 1   |

| Bit 2 |      | -     | BC2  |                        | RW   | 9 byt           | es.            | 0   |

| Bit 1 |      | -     | BC1  |                        | RW   | •               |                | 0   |

| Bit 0 |      | -     | BC0  |                        | RW   |                 |                | 1   |

**SMBus Table: Reserved Register**

| <u> </u> |      |       | tou mogiotoi |                  |      |          |          |     |

|----------|------|-------|--------------|------------------|------|----------|----------|-----|

| By       | te 9 | Pin # | Name         | Control Function | Type | 0        | 1        | PWD |

| Bit 7    |      | -     | Reserved     | Reserved         | RW   | Reserved | Reserved | 0   |

| Bit 6    |      | -     | Reserved     | Reserved         | RW   | Reserved | Reserved | 0   |

| Bit 5    |      | -     | Reserved     | Reserved         | RW   | Reserved | Reserved | 0   |

| Bit 4    |      | •     | Reserved     | Reserved         | RW   | Reserved | Reserved | 0   |

| Bit 3    |      | -     | Reserved     | Reserved         | RW   | Reserved | Reserved | 0   |

| Bit 2    |      | -     | Reserved     | Reserved         | RW   | Reserved | Reserved | 0   |

| Bit 1    |      | -     | Reserved     | Reserved         | RW   | Reserved | Reserved | 0   |

| Bit 0    |      | -     | Reserved     | Reserved         | RW   | Reserved | Reserved | 0   |

SMBus Table: M/N Programming Enable

| Byte  | e 10 | Pin # | Name     | Control Function                       | Туре | 0       | 1      | PWD |

|-------|------|-------|----------|----------------------------------------|------|---------|--------|-----|

| Bit 7 |      | =     | M/N_EN   | CPU and SRC PLL M/N Programming Enable | RW   | Disable | Enable | 0   |

| Bit 6 |      | -     | Reserved | Reserved                               | RW   | •       | -      | 0   |

| Bit 5 |      | -     | Reserved | Reserved                               | RW   | •       | -      | 0   |

| Bit 4 |      | -     | Reserved | Reserved                               | RW   | •       | -      | 0   |

| Bit 3 |      | -     | Reserved | Reserved                               | RW   | •       | -      | 0   |

| Bit 2 |      | -     | Reserved | Reserved                               | RW   | •       | -      | 0   |

| Bit 1 |      | -     | Reserved | Reserved                               | RW   | •       | -      | 0   |

| Bit 0 |      | -     | Reserved | Reserved                               | RW   | -       | -      | 0   |

**SMBus Table: CPU Frequency Control Register**

| Byte  | e 11 | Pin # | Name   | Control Function      | Туре | 0                         | 1             | PWD |

|-------|------|-------|--------|-----------------------|------|---------------------------|---------------|-----|

| Bit 7 |      | -     | N Div8 | N Divider Prog bit 8  | RW   | The decimal representatio |               | Χ   |

| Bit 6 |      | -     | N Div9 | N Divider Prog bit 9  | RW   | of M and N Di             | vier in Byte  | Χ   |

| Bit 5 |      |       | M Div5 |                       | RW   | 11 and 12 will configure  |               | Χ   |

| Bit 4 |      |       | M Div4 |                       | RW   | the CPU VCO frequency.    |               | Χ   |

| Bit 3 |      |       | M Div3 | M Dividos December    | RW   | Default at power          | er up = latch | Χ   |

| Bit 2 |      | -     | M Div2 | M Divider Programming | RW   | in or Byte 0 F            | Rom table.    | Χ   |

| Bit 1 |      | -     | M Div1 | bit (5:0)             | RW   | VCO Frequency = 14.318    |               | Χ   |

| Bit 0 |      | -     | M Div0 |                       | RW   | x [NDiv(9:<br>[MDiv(5:    | , <u>-</u>    | Х   |

SMBus Table: CPU Frequency Control Register

| Byte  | e 12 | Pin # | Name    | Control Function      | Туре | 0                          | 1             | PWD |

|-------|------|-------|---------|-----------------------|------|----------------------------|---------------|-----|

| Bit 7 |      | -     | N Div7  |                       | RW   | The decimal representation |               | Χ   |

| Bit 6 |      | -     | N Div6  |                       | RW   | of M and N Di              | vier in Byte  | Χ   |

| Bit 5 |      | -     | N Div5  |                       | RW   | 11 and 12 wil              | I configure   | Χ   |

| Bit 4 |      | -     | N Div4  | N Divider Programming | RW   | the CPU VCO                | frequency.    | Χ   |

| Bit 3 |      | -     | N Div3  | Byte12 bit(7:0) and   | RW   | Default at power           | er up = latch | Χ   |

| Bit 2 |      | -     | N Div2  | Byte11 bit(7:6)       | RW   | in or Byte 0 f             | Rom table.    | Χ   |

| Bit 1 |      | -     | N Div1  | . ,                   | RW   | VCO Frequency = 14.318     |               | Χ   |

| Bit 0 |      |       | N Div0  |                       | RW   | x [NDiv(9:0)+8] /          |               | Х   |

| DIL U |      |       | טאום או |                       | ΠVV  | [MDiv(5:                   | :0)+2]        | ^   |

SMBus Table: CPU Spread Spectrum Control Register

| Byte  | e 13 | Pin # | Name | Control Function     | Type | 0               | 1           | PWD |

|-------|------|-------|------|----------------------|------|-----------------|-------------|-----|

| Bit 7 |      | -     | SSP7 |                      | RW   |                 |             | Χ   |

| Bit 6 |      | -     | SSP6 |                      | RW   |                 |             | Χ   |

| Bit 5 |      | -     | SSP5 |                      | RW   | These Spread    | d Spectrum  | Χ   |

| Bit 4 |      | -     | SSP4 | Spread Spectrum      | RW   | bits in Byte 13 | and 14 will | Χ   |

| Bit 3 |      | -     | SSP3 | Programming bit(7:0) | RW   | program the     | e spread    | Χ   |

| Bit 2 |      | -     | SSP2 |                      | RW   | pecentage       | of CPU      | Χ   |

| Bit 1 |      | -     | SSP1 |                      | RW   |                 |             | Χ   |

| Bit 0 | ·    | -     | SSP0 |                      | RW   |                 |             | Χ   |

SMBus Table: CPU Spread Spectrum Control Register

| ombus rable. Of a opicar opecarin control register |      |       |          |                                       |      |                                                                                       |            |     |  |  |

|----------------------------------------------------|------|-------|----------|---------------------------------------|------|---------------------------------------------------------------------------------------|------------|-----|--|--|

| Byte                                               | e 14 | Pin # | Name     | Control Function                      | Type | 0 1                                                                                   |            | PWD |  |  |

| Bit 7                                              |      |       | Reserved | Reserved                              | R    | •                                                                                     | 1          | 0   |  |  |

| Bit 6                                              |      | -     | SSP14    |                                       | RW   |                                                                                       |            | Χ   |  |  |

| Bit 5                                              |      | -     | SSP13    |                                       | RW   | Thosa Caroo                                                                           | l Coootrum | Х   |  |  |

| Bit 4                                              |      | -     | SSP12    | Carood Cacatrum                       | RW   | These Spread Spectrum bits in Byte 13 and 14 will program the spread pecentage of CPU |            | Χ   |  |  |

| Bit 3                                              |      | -     | SSP11    | Spread Spectrum Programming bit(14:8) | RW   |                                                                                       |            | Χ   |  |  |

| Bit 2                                              |      | -     | SSP10    | Flogramming bit (14.6)                | RW   |                                                                                       |            | Χ   |  |  |

| Bit 1                                              |      | -     | SSP9     |                                       | RW   |                                                                                       |            | Х   |  |  |

| Bit 0                                              |      | -     | SSP8     |                                       | RW   |                                                                                       |            | Χ   |  |  |

SMBus Table: SRC Frequency Control Register

| Byte  | e 15 | Pin # | Name   | Control Function      | Type | 0                      | 1             | PWD |

|-------|------|-------|--------|-----------------------|------|------------------------|---------------|-----|

| Bit 7 |      | -     | N Div8 | N Divider Prog bit 8  | RW   | The decimal re         | presentation  | Χ   |

| Bit 6 |      | -     | N Div9 | N Divider Prog bit 9  | RW   | of M and N Di          |               | Χ   |

| Bit 5 |      | -     | M Div5 |                       | RW   | 15 and 16 wi           | Il configure  | Χ   |

| Bit 4 |      | -     | M Div4 |                       | RW   | the SRC VCO frequency. |               | Χ   |

| Bit 3 |      | -     | M Div3 | M Divides December    | RW   | Default at pow         | er up = latch | Χ   |

| Bit 2 |      | -     | M Div2 | M Divider Programming | RW   | in or Byte 0 I         | Rom table.    | Χ   |

| Bit 1 |      | -     | M Div1 | bits                  | RW   | VCO Frequen            |               | Χ   |

| Bit 0 |      | -     | M Div0 |                       | RW   | x [NDiv(9<br>[MDiv(5   | , <u>-</u>    | Χ   |

**SMBus Table: SRC Frequency Control Register**

|       |      |       | roquonoy conta- | <u>-</u>              |      |                           |               |     |

|-------|------|-------|-----------------|-----------------------|------|---------------------------|---------------|-----|

| Byte  | e 16 | Pin # | Name            | Control Function      | Type | 0                         | 1             | PWD |

| Bit 7 |      | -     | N Div7          |                       | RW   | The decimal re            | presentation  | Χ   |

| Bit 6 |      | -     | N Div6          |                       | RW   | of M and N Divier in Byte |               | Χ   |

| Bit 5 |      | -     | N Div5          |                       | RW   | 15 and 16 will configure  |               | Χ   |

| Bit 4 |      | -     | N Div4          | N. Dividor Drawsania  | RW   | the SRC VCO frequency.    |               | Χ   |

| Bit 3 |      | -     | N Div3          | N Divider Programming | RW   | Default at power          | er up = latch | Χ   |

| Bit 2 |      | -     | N Div2          | b(7:0)                | RW   | in or Byte 0 I            | Rom table.    | Χ   |

| Bit 1 |      |       | N Div1          |                       | RW   | VCO Frequency = 14.318    |               | Χ   |

| Bit 0 |      | -     | N Div0          |                       | RW   | x [NDiv(9<br>[MDiv(5      | , <u>-</u>    | X   |

SMBus Table: SRC Spread Spectrum Control Register

| <u> Unibut</u> | asic | . 0110 | oprodu opodudii | i oonii oi riegistei |      |                 |             |     |

|----------------|------|--------|-----------------|----------------------|------|-----------------|-------------|-----|

| Byte           | e 17 | Pin #  | Name            | Control Function     | Type | 0               | 1           | PWD |

| Bit 7          |      | -      | SSP7            |                      | RW   |                 |             | Χ   |

| Bit 6          |      | -      | SSP6            |                      | RW   |                 |             | Χ   |

| Bit 5          |      | -      | SSP5            |                      | RW   | These Spread    | d Spectrum  | Χ   |

| Bit 4          |      | -      | SSP4            | Spread Spectrum      | RW   | bits in Byte 17 | and 18 will | Χ   |

| Bit 3          |      | -      | SSP3            | Programming b(7:0)   | RW   | program th      | e spread    | Χ   |

| Bit 2          |      | -      | SSP2            |                      | RW   | pecentage       | of SRC      | Χ   |

| Bit 1          |      | -      | SSP1            |                      | RW   |                 |             | Χ   |

| Bit 0          |      | =      | SSP0            |                      | RW   |                 |             | Χ   |

SMBus Table: SRC Spread Spectrum Control Register

| SIVIDUS | s rabic | . onc | Spread Speciful | i Control negister  |      |                                                                      |            |     |

|---------|---------|-------|-----------------|---------------------|------|----------------------------------------------------------------------|------------|-----|

| Byte    | e 18    | Pin # | Name            | Control Function    | Type | 0                                                                    | 1          | PWD |

| Bit 7   |         | -     | Reserved        | Reserved            | R    | -                                                                    | -          | 0   |

| Bit 6   |         | -     | SSP14           |                     | RW   |                                                                      |            | Х   |

| Bit 5   |         | -     | SSP13           |                     | RW   | Thosa Caroo                                                          | d Chaotrum | Х   |

| Bit 4   |         | -     | SSP12           | Coread Coastrum     | RW   | These Spread Spectrum bits in Byte 17 and 18 will program the spread |            | Х   |

| Bit 3   |         | -     | SSP11           | Spread Spectrum     | RW   |                                                                      |            | Х   |

| Bit 2   |         | -     | SSP10           | Programming b(14:8) | RW   |                                                                      | •          | Χ   |

| Bit 1   |         | -     | SSP9            |                     | RW   | pecentage of SRC                                                     |            | Х   |

| Bit 0   |         | _     | SSP8            |                     | RW   |                                                                      |            | Х   |

**SMBus Table: Programmable Output Divider Register**

| Byte  | e 19 | Pin # | Name    | Control Function          | Туре | 0          | 1         | PWD |

|-------|------|-------|---------|---------------------------|------|------------|-----------|-----|

| Bit 7 |      | -     | CPUDiv3 |                           | RW   |            |           | Х   |

| Bit 6 |      | -     | CPUDiv2 | CPU Divider Ratio         | RW   | See Tal    | ole 2:    | Х   |

| Bit 5 |      | -     | CPUDiv1 | Programming Bits          | RW   | CPU Divide | er Ratios | Х   |

| Bit 4 |      | -     | CPUDiv0 |                           | RW   |            |           | Χ   |

| Bit 3 |      | -     | HTTDiv3 | HTT Divider Ratio         | RW   |            |           | Х   |

| Bit 2 |      | -     | HTTDiv2 | Programming Bits (PCI     | RW   | See Tal    | ole 3:    | Χ   |

| Bit 1 |      | -     | HTTDiv1 | divider is always 2x the  | RW   | HTT Divide | er Ratios | Χ   |

| Bit 0 |      | -     | HTTDiv0 | HTT divider or 1/2 freq.) | RW   |            |           | Χ   |

**SMBus Table: Programmable Output Divider Register**

| Byte  | e 20 | Pin # | Name     | Control Function   | Туре | 0                  | 1 | PWD |

|-------|------|-------|----------|--------------------|------|--------------------|---|-----|

| Bit 7 |      |       | Reserved | Reserved           | R    | -                  | - | Χ   |

| Bit 6 |      | -     | Reserved | Reserved           | R    | -                  | - | Χ   |

| Bit 5 |      | -     | Reserved | Reserved           | R    | -                  | - | Χ   |

| Bit 4 |      | -     | Reserved | Reserved           | R    | -                  | - | Χ   |

| Bit 3 |      | -     | SRC_Div3 |                    | RW   |                    |   | Х   |

| Bit 2 |      | -     | SRC_Div2 | SRC_ Divider Ratio | RW   | See Table 4:       |   | Х   |

| Bit 1 |      | -     | SRC_Div1 | Programming Bits   | RW   | SRC Divider Ratios |   | Χ   |

| Bit 0 |      | -     | SRC_Div0 |                    | RW   |                    |   | Χ   |

SMBusTable: Test Byte Register

| ombus rubic. Test byte riegister |      |               |      |             |     |  |

|----------------------------------|------|---------------|------|-------------|-----|--|

| Byte 21                          | Test | Test Function | Type | Test Result | PWD |  |

| Bit 7                            | `    | ICS ONLY TEST | RW   | Reserved    | 0   |  |

| Bit 6                            |      | ICS ONLY TEST | RW   | Reserved    | 0   |  |

| Bit 5                            |      | ICS ONLY TEST | RW   | Reserved    | 0   |  |

| Bit 4                            |      | ICS ONLY TEST | RW   | Reserved    | 0   |  |

| Bit 3                            |      | ICS ONLY TEST | RW   | Reserved    | 0   |  |

| Bit 2                            |      | ICS ONLY TEST | RW   | Reserved    | 0   |  |

| Bit 1                            |      | ICS ONLY TEST | RW   | Reserved    | 0   |  |

| Bit 0                            |      | ICS ONLY TEST | RW   | Reserved    | 0   |  |

# Shared Pin Operation - Input/Output Pins

The I/O pins designated by (input/output) on the ICS932S801 serve as dual signal functions to the device. During initial power-up, they act as input pins. The logic level (voltage) that is present on these pins at this time is read and stored into a 5-bit internal data latch. At the end of Power-On reset, (see AC characteristics for timing values), the device changes the mode of operations for these pins to an output function. In this mode the pins produce the specified buffered clocks to external loads.

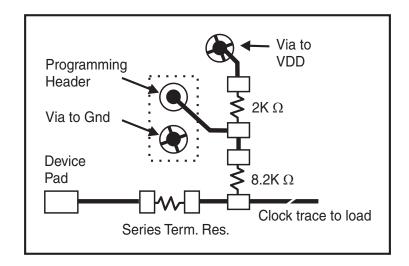

To program (load) the internal configuration register for these pins, a resistor is connected to either the VDD (logic 1) power supply or the GND (logic 0) voltage potential. A 10 Kilohm (10K) resistor is used to provide both the solid CMOS programming voltage needed during the power-up programming period and to provide an insignificant load on the output clock during the subsequent operating period.

Figure 1 shows a means of implementing this function when a switch or 2 pin header is used. With no jumper is installed the pin will be pulled high. With the jumper in place the pin will be pulled low. If programmability is not necessary, than only a single resistor is necessary. The programming resistors should be located close to the series termination resistor to minimize the current loop area. It is more important to locate the series termination resistor close to the driver than the programming resistor.

Fig. 1

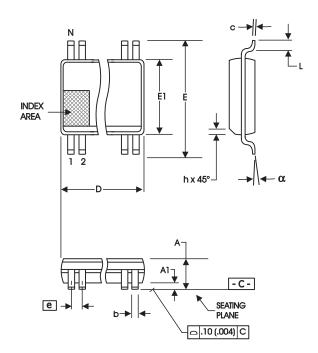

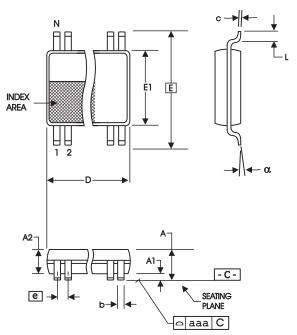

300 mil SSOP

|        | In Milli       | meters    | In Inches         |       |  |

|--------|----------------|-----------|-------------------|-------|--|

| SYMBOL | COMMON D       | IMENSIONS | COMMON DIMENSIONS |       |  |

|        | MIN            | MAX       | MIN               | MAX   |  |

| Α      | 2.41           | 2.80      | .095              | .110  |  |

| A1     | 0.20           | 0.40      | .008              | .016  |  |

| b      | 0.20           | 0.34      | .008              | .0135 |  |

| С      | 0.13           | 0.25      | .005              | .010  |  |

| D      | SEE VAF        | RIATIONS  | SEE VARIATIONS    |       |  |

| E      | 10.03          | 10.68     | .395              | .420  |  |

| E1     | 7.40           | 7.60      | .291              | .299  |  |

| е      | 0.635          | BASIC     | 0.025 BASIC       |       |  |

| h      | 0.38           | 0.64      | .015              | .025  |  |

| L      | 0.50           | 1.02      | .020              | .040  |  |

| N      | SEE VARIATIONS |           | SEE VARIATIONS    |       |  |

| а      | 0°             | 8°        | 0°                | 8°    |  |

#### **VARIATIONS**

| N  | Dn    | nm.   | D (inch) |      |  |

|----|-------|-------|----------|------|--|

| N  | MIN   | MAX   | MIN      | MAX  |  |

| 48 | 15.75 | 16.00 | .620     | .630 |  |

Reference Doc.: JEDEC Publication 95, MO-118

10-0034

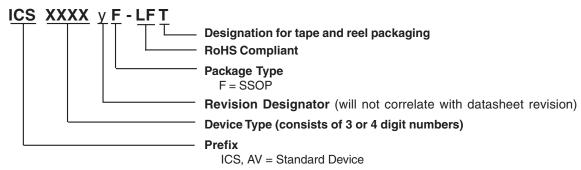

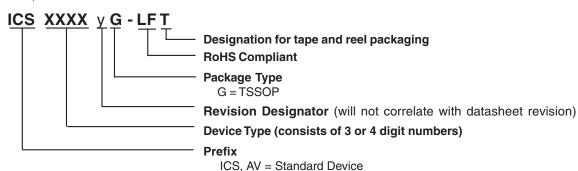

### **Ordering Information**

ICS932S801yFLFT

Example:

| (240 mil) (20 mil) |                |          |                |                  |  |

|--------------------|----------------|----------|----------------|------------------|--|

|                    | In Millir      | neters   | In Inches      |                  |  |

| SYMBOL             | COMMON DI      | MENSIONS | COMMON D       | <b>IMENSIONS</b> |  |

|                    | MIN            | MAX      | MIN            | MAX              |  |

| Α                  |                | 1.20     |                | .047             |  |

| A1                 | 0.05           | 0.15     | .002           | .006             |  |

| A2                 | 0.80           | 1.05     | .032           | .041             |  |

| b                  | 0.17           | 0.27     | .007           | .011             |  |

| С                  | 0.09           | 0.20     | .0035          | .008             |  |

| D                  | SEE VAR        | IATIONS  | SEE VARIATIONS |                  |  |

| E                  | 8.10 B         | ASIC     | 0.319 BASIC    |                  |  |

| E1                 | 6.00           | 6.20     | .236           | .244             |  |

| е                  | 0.50 BASIC     |          | 0.020 BASIC    |                  |  |

| L                  | 0.45           | 0.75     | .018           | .030             |  |

| N                  | SEE VARIATIONS |          | SEE VARIATIONS |                  |  |

| а                  | 0°             | 8°       | 0°             | 8°               |  |

| aaa                |                | 0.10     |                | .004             |  |

#### **VARIATIONS**

| Ν  | D m   | ım.   | D (inch) |      |  |

|----|-------|-------|----------|------|--|

| IN | MIN   | MAX   | MIN      | MAX  |  |

| 48 | 12.40 | 12.60 | .488     | .496 |  |

Reference Doc.: JEDEC Publication 95, MO-153

10-0039

### **Ordering Information**

ICS932S801yGLFT

Example:

**Revision History**

|      |            | · J                                                                                 |        |

|------|------------|-------------------------------------------------------------------------------------|--------|

| Rev. | Issue Date | Description                                                                         | Page # |

|      |            | Updated Electrical Characteristics Tables:                                          |        |

|      |            | i) Changed SRC jitter from 125ps to 100ps;                                          |        |

|      |            | ii) Changed PCI/HTT Skew from 500ps to 200ps;                                       |        |

|      |            | iii) Added USB Skew, 50ps.                                                          |        |

|      |            | iv) Change REF Skew from 500ps to 50ps.                                             | 14-16  |

| В    | 5/18/2005  | 2. Updated LF Ordering Information from "Lead Free" to "RoHS Compliant".            | 18-19  |

|      |            | 1. Correct pin description of PD# (Pin 21). It does not contain a pull up resistor. |        |

| С    | 3/13/2006  | 2. Added PCIe Gen 1 phase noise numbers to SRC output characterisitics              | 2, 7   |