Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# Low Power Clock Chip for Serverworks HT2400 Servers

#### **Recommended Application:**

Serverworks HT2400-based systems using AMD Opteron processors

#### **Output Features:**

- 7 Pairs of AMD Low Power K8 Greyhound compliant clocks

- 7 Pair of SRC/PCI Express\* Gen 2 clocks

- 3 14.318 MHz REF clocks including 1 free-running

- 2 48MHz clocks

- 2 PCI 33 MHz clocks

- 2 25MHz clocks

#### Features:

- Spread Spectrum for EMI reduction

- Outputs may be disabled via SMBus

- M/N programming via SMBus

- PCIe clocks meet PCIe Gen 2.

- Low Power differential outputs

## **Functionality**

| FS2 | FS1 | FS0 | CPU<br>(MHz) |

|-----|-----|-----|--------------|

| 0   | 0   | 0   | Hi-Z         |

| 0   | 0   | 1   | X/6          |

| 0   | 1   | 0   | 180.00       |

| 0   | 1   | 1   | 220.00       |

| 1   | 0   | 0   | 100.00       |

| 1   | 0   | 1   | 133.33       |

| 1   | 1   | 0   | Reserved     |

| 1   | 1   | 1   | 200.00       |

# **Power Groups**

| Pin N  | umber  | Description           |

|--------|--------|-----------------------|

| VDD    | GND    | -                     |

| 8      | 11     | 48MHz Clocks          |

| 64     | 61     | 25MHz Clocks          |

| 14     | 17     | 33 MHz PCI Clocks     |

| 20     | 21     | Analog Core           |

| 36, 28 | 35, 27 | PCIe clocks           |

| 55, 47 | 54, 46 | K8G CPU Clocks        |

| 3      | 7      | REF Clocks, Xtal Osc. |

#### **Pin Configuration**

| _            |    |                        |                  |

|--------------|----|------------------------|------------------|

| X1           | 1  | 6                      | 4 VDD25MHz       |

| X2           | 2  | 6                      | 3 FS0/25MHz_0_2x |

| VDDREF_STB   | 3  | 6                      | 2 25MHz_1_2x     |

| REF0_RUN_2x  | 4  | 6                      | 1 GND25MHz       |

| FS1/REF1_2x  | 5  | 6                      | 0 SPREAD_EN      |

| FS2/REF2_2x  | 6  | 5                      | 9 CPUK8GT_L6     |

| GNDREF       | 7  | 5                      | 8 CPUK8GC_L6     |

| VDD48        | 8  | 5                      | 7 CPUK8GT_L5     |

| 48MHz_0_2x   | 9  | 5                      | 6 CPUK8GC_L5     |

| 48MHz_1_2x   | 10 | 5                      | 5 VDDCPU         |

| GND48        | 11 | 5                      | 4 GND            |

| SCLK         | 12 | 5                      | 3 CPUK8GT_L4     |

| SDATA        | 13 | 5                      | 2 CPUK8GC_L4     |

| VDDPCI       | 14 | 5                      | 1 CPUK8GT_L3     |

| PCICLK0_2x   | 15 | 5<br>ک                 | 0 CPUK8GC_L3     |

| PCICLK1_2x   | 16 | 55<br>4<br>4<br>4<br>4 | 9 CPUK8GT_L2     |

| GNDPCI       | 17 | <b>ਨ</b> 4             | 8 CPUK8GC_L2     |

| CLKPWRGD/PD# | 18 | <b>E</b> 4             | 7 VDDCPU         |

| GND          | 19 | 4                      | 6 GND            |

| VDDA         | 20 | 4                      | 5 CPUK8GT_L1     |

| GNDA         | 21 | 4                      | 4 CPUK8GC_L1     |

| GND          | 22 | 4                      | 3 CPUK8GT_L0     |

| PCIeT_L0     | 23 | 4                      | 2 CPUK8GC_L0     |

| PCIeC_L0     | 24 | 4                      | 1 GND            |

| PCleT_L1     | 25 |                        | 0 PCIeT_L6       |

| PCIeC_L1     | 26 |                        | 9 PCIeC_L6       |

| GND          | 27 |                        | 8 PCIeT_L5       |

| VDDPCle      | 28 | 3                      | 7 PCIeC_L5       |

| PCleT_L2     |    | -                      | 6 VDDPCle        |

| PCIeC_L2     |    |                        | 5 GND            |

| PCIeT_L3     |    |                        | 4 PCIeT_L4       |

| PCIeC_L3     | 32 | 3                      | 3 PCIeC_L4       |

|              | C4 | TCCOD                  |                  |

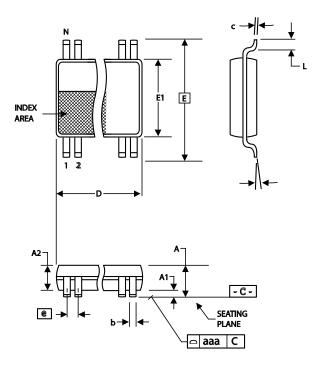

64-TSSOP

**Pin Description**

| PIN# | escription  PIN NAME | TYPE | DESCRIPTION                                                                                                                                         |

|------|----------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | X1                   | IN   | Crystal input, Nominally 14.318MHz.                                                                                                                 |

| 2    | X2                   | OUT  | Crystal output, Nominally 14.318MHz                                                                                                                 |

| 3    | VDDREF_STB           | PWR  | Ref, XTAL power supply, nominal 3.3V standby power                                                                                                  |

| 4    | REF0_RUN_2x          | OUT  | 14.318MHz Free Running XTAL Output. This output runs as long as                                                                                     |

| 4    | NEI U_NOIN_ZX        | 001  | standby VDD is applied to the part. Default drive is 2 loads.                                                                                       |

| 5    | FS1/REF1_2x          | I/O  | Frequency select latch input pin / 14.318 MHz reference clock. Default 2                                                                            |

|      |                      |      | load drive.  Frequency select latch input pin / 14.318 MHz reference clock. Default 2                                                               |

| 6    | FS2/REF2_2x          | I/O  | load drive.                                                                                                                                         |

| 7    | GNDREF               | PWR  | Ground pin for the REF outputs.                                                                                                                     |

| 8    | VDD48                | PWR  | Power pin for the 48MHz output.3.3V                                                                                                                 |

| 9    | 48MHz_0_2x           | OUT  | 48MHz clock output. Default 2 load drive strength                                                                                                   |

| 10   | 48MHz_1_2x           | OUT  | 48MHz clock output. Default 2 load drive strength                                                                                                   |

| 11   | GND48                | PWR  | Ground pin for the 48MHz outputs                                                                                                                    |

| 12   | SCLK                 | IN   | Clock pin of SMBus circuitry, 5V tolerant.                                                                                                          |

| 13   | SDATA                | I/O  | Data pin for SMBus circuitry, 3.3V tolerant.                                                                                                        |

| 14   | VDDPCI               | PWR  | Power supply for PCI clocks, nominal 3.3V                                                                                                           |

| 15   | PCICLK0_2x           | OUT  | 3.3V PCI clock output. Default 2 load drive strength.                                                                                               |

| 16   | PCICLK1_2x           | OUT  | 3.3V PCI clock output. Default 2 load drive strength.                                                                                               |

| 17   | GNDPCI               | PWR  | Ground pin for the PCI outputs                                                                                                                      |

|      |                      |      | This 3.3V LVTTL input is a level sensitive strobe used to determine when latch inputs are valid and are ready to be sampled. This is an active high |

| 18   | CLKPWRGD/PD#         | IN   | input. / Asynchronous active low input pin used to power down the device                                                                            |

|      |                      |      | into a low power state.                                                                                                                             |

| 19   | GND                  | PWR  | Ground pin.                                                                                                                                         |

| 20   | VDDA                 | PWR  | 3.3V power for the PLL core.                                                                                                                        |

| 21   | GNDA                 | PWR  | Ground pin for the PLL core.                                                                                                                        |

| 22   | GND                  | PWR  | Ground pin.                                                                                                                                         |

| 23   | PCleT_L0             | OUT  | True clock of 0.8V differential push-pull PCI_Express pair (no 50ohm                                                                                |

|      |                      |      | resistor to GND needed)  Complement clock of 0.8V differential push-pull PCI_Express pair. (no                                                      |

| 24   | PCIeC_L0             | OUT  | 50ohm resistor to GND needed)                                                                                                                       |

| 25   | PCleT_L1             | OUT  | True clock of 0.8V differential push-pull PCI_Express pair (no 50ohm                                                                                |

| 25   | role1_L1             | 001  | resistor to GND needed)                                                                                                                             |

| 26   | PCleC_L1             | OUT  | Complement clock of 0.8V differential push-pull PCI_Express pair. (no                                                                               |

| 27   | GND                  | PWR  | 50ohm resistor to GND needed) Ground pin.                                                                                                           |

| 28   | VDDPCle              | PWR  | Power supply for PCI Express clocks, nominal 3.3V                                                                                                   |

|      |                      |      | True clock of 0.8V differential push-pull PCI_Express pair (no 50ohm                                                                                |

| 29   | PCleT_L2             | OUT  | resistor to GND needed)                                                                                                                             |

| 30   | PCIeC_L2             | OUT  | Complement clock of 0.8V differential push-pull PCI_Express pair. (no                                                                               |

|      |                      |      | 50ohm resistor to GND needed)                                                                                                                       |

| 31   | PCleT_L3             | OUT  | True clock of 0.8V differential push-pull PCI_Express pair (no 50ohm resistor to GND needed)                                                        |

|      |                      | _    | Complement clock of 0.8V differential push-pull PCI_Express pair. (no                                                                               |

| 32   | PCleC_L3             | OUT  | 50ohm resistor to GND needed)                                                                                                                       |

**Pin Description (continued)**

|      | Description (continued) |      |                                                                                                     |  |  |  |  |  |  |  |  |

|------|-------------------------|------|-----------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| PIN# | PIN NAME                | TYPE | DESCRIPTION                                                                                         |  |  |  |  |  |  |  |  |

| 33   | PCIeC_L4                | OUT  | Complement clock of 0.8V differential push-pull PCI_Express pair. (no 500hm resistor to GND needed) |  |  |  |  |  |  |  |  |

| 34   | PCIeT_L4                | OUT  | True clock of 0.8V differential push-pull PCI_Express pair (no 50ohm resistor to GND needed)        |  |  |  |  |  |  |  |  |

| 35   | GND                     | PWR  | Ground pin.                                                                                         |  |  |  |  |  |  |  |  |

| 36   | VDDPCle                 | PWR  | Power supply for PCI Express clocks, nominal 3.3V                                                   |  |  |  |  |  |  |  |  |

| 37   | PCIeC_L5                | OUT  | Complement clock of 0.8V differential push-pull PCI_Express pair. (no 500hm resistor to GND needed) |  |  |  |  |  |  |  |  |

| 38   | PCIeT_L5                | OUT  | True clock of 0.8V differential push-pull PCI_Express pair (no 50ohm resistor to GND needed)        |  |  |  |  |  |  |  |  |

| 39   | PCIeC_L6                | OUT  | Complement clock of 0.8V differential push-pull PCI_Express pair. (no 50ohm resistor to GND needed) |  |  |  |  |  |  |  |  |

| 40   | PCIeT_L6                | OUT  | True clock of 0.8V differential push-pull PCI_Express pair (no 50ohm resistor to GND needed)        |  |  |  |  |  |  |  |  |

| 41   | GND                     | PWR  | Ground pin.                                                                                         |  |  |  |  |  |  |  |  |

| 42   | CPUK8GC_L0              | OUT  | Complementary signal of low-power differential push-pull AMD K8 "Greyhound" clock                   |  |  |  |  |  |  |  |  |

| 43   | CPUK8GT_L0              | OUT  | True signal of low-power differential push-pull AMD K8 "Greyhound" clock                            |  |  |  |  |  |  |  |  |

| 44   | CPUK8GC_L1              | OUT  | Complementary signal of low-power differential push-pull AMD K8 "Greyhound" clock                   |  |  |  |  |  |  |  |  |

| 45   | CPUK8GT_L1              | OUT  | True signal of low-power differential push-pull AMD K8 "Greyhound" clock                            |  |  |  |  |  |  |  |  |

| 46   | GND                     | PWR  | Ground pin.                                                                                         |  |  |  |  |  |  |  |  |

| 47   | VDDCPU                  | PWR  | Supply for CPU clocks, 3.3V nominal                                                                 |  |  |  |  |  |  |  |  |

| 48   | CPUK8GC_L2              | OUT  | Complementary signal of low-power differential push-pull AMD K8 "Greyhound" clock                   |  |  |  |  |  |  |  |  |

| 49   | CPUK8GT_L2              | OUT  | True signal of low-power differential push-pull AMD K8 "Greyhound" clock                            |  |  |  |  |  |  |  |  |

| 50   | CPUK8GC_L3              | OUT  | Complementary signal of low-power differential push-pull AMD K8 "Greyhound" clock                   |  |  |  |  |  |  |  |  |

| 51   | CPUK8GT_L3              | OUT  | True signal of low-power differential push-pull AMD K8 "Greyhound" clock                            |  |  |  |  |  |  |  |  |

| 52   | CPUK8GC_L4              | OUT  | Complementary signal of low-power differential push-pull AMD K8 "Greyhound" clock                   |  |  |  |  |  |  |  |  |

| 53   | CPUK8GT_L4              | OUT  | True signal of low-power differential push-pull AMD K8 "Greyhound" clock                            |  |  |  |  |  |  |  |  |

| 54   | GND                     | PWR  | Ground pin.                                                                                         |  |  |  |  |  |  |  |  |

| 55   | VDDCPU                  | PWR  | Supply for CPU clocks, 3.3V nominal                                                                 |  |  |  |  |  |  |  |  |

| 56   | CPUK8GC_L5              | OUT  | Complementary signal of low-power differential push-pull AMD K8 "Greyhound" clock                   |  |  |  |  |  |  |  |  |

| 57   | CPUK8GT_L5              | OUT  | True signal of low-power differential push-pull AMD K8 "Greyhound" clock                            |  |  |  |  |  |  |  |  |

| 58   | CPUK8GC_L6              | OUT  | Complementary signal of low-power differential push-pull AMD K8 "Greyhound" clock                   |  |  |  |  |  |  |  |  |

| 59   | CPUK8GT_L6              | OUT  | True signal of low-power differential push-pull AMD K8 "Greyhound" clock                            |  |  |  |  |  |  |  |  |

| 60   | SPREAD_EN               | IN   | Asynchronous, active high input to enable spread spectrum functionality.                            |  |  |  |  |  |  |  |  |

| 61   | GND25MHz                | PWR  | Ground pin for the 25Mhz outputs                                                                    |  |  |  |  |  |  |  |  |

| 62   | 25MHz_1_2x              | OUT  | 25MHz clock output, 3.3V. Default 2 load drive                                                      |  |  |  |  |  |  |  |  |

| 63   | FS0/25MHz_0_2x          | I/O  | Frequency select latch input pin / Fixed 25MHz 3.3V clock output. Default 2 load drive              |  |  |  |  |  |  |  |  |

| 64   | VDD25MHz                | PWR  | Power supply for 25MHz clocks, 3.3V nominal.                                                        |  |  |  |  |  |  |  |  |

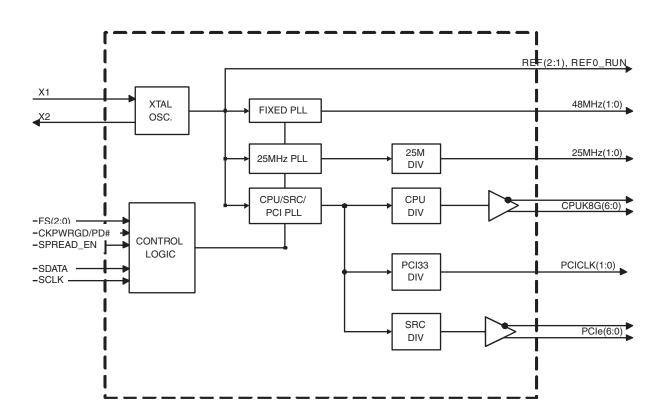

# **General Description**

The ICS932S825 is a main clock synthesizer chip that all clocks required by Serverworks HT2400-based servers. An SMBus interface allows full control of the device.

# **Block Diagram**

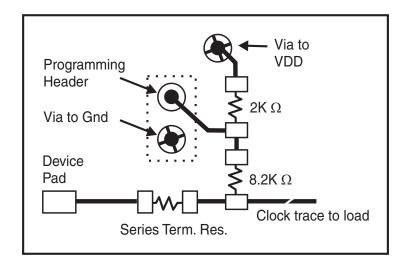

# Single-ended Terminations (All Single-Ended Outputs)

| Single-ended    | Number of      | Series Resistor for Proper Termination |

|-----------------|----------------|----------------------------------------|

| Output Strength | Loads on Board | Zo = 50 ohms                           |

| 1 Load          | 1              | 33                                     |

| 2 Load          | 1              | 39                                     |

| (Default)       | 2              | 22                                     |

#### **Differential Terminations**

| Differential | Number of      | Series Resistor for Proper Termination |

|--------------|----------------|----------------------------------------|

| Output       | Loads on Board | Zo = 50 ohms                           |

| CPUK8Gx      | 1              | 33                                     |

| PCIe_Lx      | 1              | 33                                     |

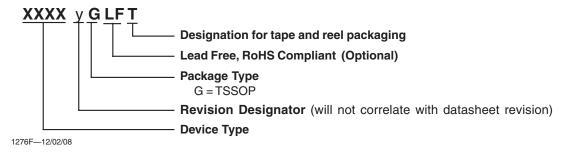

1276F—12/02/08

**Frequency Selection Table**

| Frequen        |              | ection<br>rte 0 | 1 I ab      | ie          |              |              |              |             |                     |

|----------------|--------------|-----------------|-------------|-------------|--------------|--------------|--------------|-------------|---------------------|

| Bit 4<br>SS_EN | Bit 3<br>FS3 | Bit2<br>FS2     | Bit1<br>FS1 | Bit0<br>FS0 | CPU<br>(MHz) | SRC<br>(MHz) | PCI<br>(MHz) | Spread<br>% | OverClock<br>Amount |

| 0              | 0            | 0               | 0           | 0           | Hi-Z         | Hi-Z         | Hi-Z         | N/A         | N/A                 |

| 0              | 0            | 0               | 0           | 1           | X/4          | X/8          | x/24         | N/A         | N/A                 |

| 0              | 0            | 0               | 1           | 0           | 180.00       | 90.00        | 30.00        | 0           | 0.90                |

| 0              | 0            | 0               | 1           | 1           | 220.00       | 110.00       | 36.67        | 0           | 1.10                |

| 0              | 0            | 1               | 0           | 0           | 100.00       | 100.00       | 33.33        | 0           | 1.00                |

| 0              | 0            | 1               | 0           | 1           | 133.33       | 100.00       | 33.33        | 0           | 1.00                |

| 0              | 0            | 1               | 1           | 0           |              |              | Reserved     | l           |                     |

| 0              | 0            | 1               | 1           | 1           | 200.00       | 100.00       | 33.33        | 0           | 1.00                |

| 0              | 1            | 0               | 0           | 0           | 184.00       | 92.00        | 30.67        | 0           | 0.92                |

| 0              | 1            | 0               | 0           | 1           | 188.00       | 94.00        | 31.33        | 0           | 0.94                |

| 0              | 1            | 0               | 1           | 0           | 192.00       | 96.00        | 32.00        | 0           | 0.96                |

| 0              | 1            | 0               | 1           | 1           | 196.00       | 98.00        | 32.67        | 0           | 0.98                |

| 0              | 1            | 1               | 0           | 0           | 204.00       | 102.00       | 34.00        | 0           | 1.02                |

| 0              | 1            | 1               | 0           | 1           | 208.00       | 104.00       | 34.67        | 0           | 1.04                |

| 0              | 1            | 1               | 1           | 0           | 212.00       | 106.00       | 35.33        | 0           | 1.06                |

| 0              | 1            | 1               | 1           | 1           | 216.00       | 108.00       | 36.00        | 0           | 1.08                |

| 1              | 0            | 0               | 0           | 0           | Hi-Z         | Hi-Z         | Hi-Z         | N/A         | N/A                 |

| 1              | 0            | 0               | 0           | 1           | X/4          | X/8          | x/24         | N/A         | N/A                 |

| 1              | 0            | 0               | 1           | 0           | 180.00       | 90.00        | 30.00        | -0.5%       | 1.00                |

| 1              | 0            | 0               | 1           | 1           | 220.00       | 110.00       | 36.67        | -0.5%       | 1.00                |

| 1              | 0            | 1               | 0           | 0           | 100.00       | 100.00       | 33.33        | -0.5%       | 1.00                |

| 1              | 0            | 1               | 0           | 1           | 133.33       | 100.00       | 33.33        | -0.5%       | 1.00                |

| 1              | 0            | 1               | 1           | 0           |              |              | Reserved     | ŀ           |                     |

| 1              | 0            | 1               | 1           | 1           | 200.00       | 100.00       | 33.33        | -0.5%       | 1.00                |

| 1              | 1            | 0               | 0           | 0           | 184.00       | 92.00        | 30.67        | -0.5%       | 0.92                |

| 1              | 1            | 0               | 0           | 1           | 188.00       | 94.00        | 31.33        | -0.5%       | 0.94                |

| 1              | 1            | 0               | 1           | 0           | 192.00       | 96.00        | 32.00        | -0.5%       | 0.96                |

| 1              | 1            | 0               | 1           | 1           | 196.00       | 98.00        | 32.67        | -0.5%       | 0.98                |

| 1              | 1            | 1               | 0           | 0           | 204.00       | 102.00       | 34.00        | -0.5%       | 1.02                |

| 1              | 1            | 1               | 0           | 1           | 208.00       | 104.00       | 34.67        | -0.5%       | 1.04                |

| 1              | 1            | 1               | 1           | 0           | 212.00       | 106.00       | 35.33        | -0.5%       | 1.06                |

| 1              | 1            | 1               | 1           | 1           | 216.00       | 108.00       | 36.00        | -0.5%       | 1.08                |

# **CPU Divider Ratios**

|         |     | Divider (3:2) |     |         |     |         |     |         |     |  |  |  |

|---------|-----|---------------|-----|---------|-----|---------|-----|---------|-----|--|--|--|

|         | Bit | 00            |     | 01      |     | 10      |     | 11      | MSB |  |  |  |

| (1:0)   | 00  | 0000          | 2   | 0100    | 4   | 1000    | 8   | 1100    | 16  |  |  |  |

|         | 01  | 0001          | 3   | 0101    | 6   | 1001    | 12  | 1101    | 24  |  |  |  |

| ide     | 10  | 0010          | 5   | 0110    | 10  | 1010    | 20  | 1110    | 40  |  |  |  |

| Divider | 11  | 0011          | 15  | 0111    | 30  | 1011    | 60  | 1111    | 120 |  |  |  |

| _       | LSB | Address       | Div | Address | Div | Address | Div | Address | Div |  |  |  |

## **PCI Divider Ratios**

|         |     | Divider (3:2) |     |         |     |         |     |         |     |  |  |  |

|---------|-----|---------------|-----|---------|-----|---------|-----|---------|-----|--|--|--|

| (       | Bit | 00            |     | 01      |     | 10      |     | 11      | MSB |  |  |  |

| (1:0)   | 00  | 0000          | 4   | 0100    | 8   | 1000    | 16  | 1100    | 32  |  |  |  |

|         | 01  | 0001          | 3   | 0101    | 6   | 1001    | 12  | 1101    | 24  |  |  |  |

| Divider | 10  | 0010          | 5   | 0110    | 10  | 1010    | 20  | 1110    | 40  |  |  |  |

| )iV     | 11  | 0011          | 15  | 0111    | 30  | 1011    | 60  | 1111    | 120 |  |  |  |

|         | LSB | Address       | Div | Address | Div | Address | Div | Address | Div |  |  |  |

# **SRC Divider Ratios**

|         |     | Divider (3:2) |     |         |     |         |     |         |     |  |  |  |

|---------|-----|---------------|-----|---------|-----|---------|-----|---------|-----|--|--|--|

|         | Bit | 00            |     | 01      |     | 10      |     | 11      | MSB |  |  |  |

| (1:0)   | 00  | 0000          | 2   | 0100    | 4   | 1000    | 8   | 1100    | 16  |  |  |  |

|         | 01  | 0001          | 3   | 0101    | 6   | 1001    | 12  | 1101    | 24  |  |  |  |

| ig      | 10  | 0010          | 5   | 0110    | 10  | 1010    | 20  | 1110    | 40  |  |  |  |

| Divider | 11  | 0011          | 7   | 0111    | 14  | 1011    | 28  | 1111    | 56  |  |  |  |

|         | LSB | Address       | Div | Address | Div | Address | Div | Address | Div |  |  |  |

**Absolute Maximum Ratings**

| Parameter                             | Symbol   | Min  | Max        | Units | Notes |

|---------------------------------------|----------|------|------------|-------|-------|

| 3.3V Core Supply Voltage              | VDDA     |      | GND + 4.5V | ٧     | 1     |

| 3.3V Logic Input Supply Voltage       | VDD      |      | GND +4.5V  | ٧     | 1     |

| Storage Temperature                   | Ts       | -50  | 150        | °C    |       |

| Ambient Operating Temp                | Tambient | 0    | 70         | °C    |       |

| Input ESD protection human body model | ESD prot | 2000 |            | V     | 1     |

<sup>&</sup>lt;sup>1</sup>Operation at these extremes is neither implied nor guaranteed

# **Electrical Characteristics - Input/Supply/Common Output Parameters**

$T_A = 0 - 70^{\circ}C$ ; Supply Voltage  $V_{DD} = 3.3 \text{ V} + /-5\%$

| $T_A = 0 - 70 \text{ G}$ , Supply Voltage $V_{DD} = 3.3 \text{ V} + 7-3\%$ |                      |                                                                   |                       |        |                |       |       |  |  |  |

|----------------------------------------------------------------------------|----------------------|-------------------------------------------------------------------|-----------------------|--------|----------------|-------|-------|--|--|--|

| PARAMETER                                                                  | SYMBOL               | Conditions                                                        | MIN                   | TYP    | MAX            | UNITS | NOTES |  |  |  |

| Input High Voltage                                                         | $V_{IH}$             |                                                                   | 2                     |        | $V_{DD} + 0.3$ | V     | 1     |  |  |  |

| Input Low Voltage                                                          | V <sub>IL</sub>      |                                                                   | V <sub>SS</sub> - 0.3 |        | 0.8            | V     | 1     |  |  |  |

| Input High Current                                                         | I <sub>IH</sub>      | $V_{IN} = V_{DD}$                                                 | -5                    |        | 5              | uA    | 1     |  |  |  |

| Input Low Current                                                          | I <sub>IL1</sub>     | V <sub>IN</sub> = 0 V; Inputs with no pull-up resistors           | -5                    |        |                | uA    | 1     |  |  |  |

| input Low Gurrent                                                          | I <sub>IL2</sub>     | V <sub>IN</sub> = 0 V; Inputs with pull-up resistors              | -200                  |        |                | uA    | 1     |  |  |  |

| Operating Current                                                          | I <sub>DD3.3OP</sub> | all outputs driven                                                |                       |        | 250            | mA    |       |  |  |  |

| Powerdown Current                                                          | I <sub>DD3.3PD</sub> | all diff pairs Low/Low                                            |                       |        | 15             | mA    |       |  |  |  |

| Input Frequency <sup>3</sup>                                               | $F_i$                | $V_{DD} = 3.3 \text{ V}$                                          |                       | 14.318 |                | MHz   | 3     |  |  |  |

| Pin Inductance <sup>1</sup>                                                | $L_{pin}$            |                                                                   |                       |        | 7              | nΗ    | 1     |  |  |  |

|                                                                            | C <sub>IN</sub>      | Logic Inputs                                                      |                       |        | 5              | pF    | 1     |  |  |  |

| Input Capacitance <sup>1</sup>                                             | $C_OUT$              | Output pin capacitance                                            |                       |        | 6              | pF    | 1     |  |  |  |

|                                                                            | $C_{INX}$            | X1 & X2 pins                                                      |                       |        | 5              | pF    | 1     |  |  |  |

| Clk Stabilization <sup>1,2</sup>                                           | $T_{STAB}$           | From V <sub>DD</sub> Power-Up or de-assertion of PD# to 1st clock |                       |        | 3              | ms    | 1,2   |  |  |  |

| Modulation Frequency                                                       |                      | Triangular Modulation                                             | 30                    |        | 33             | kHz   | 1     |  |  |  |

| SMBus Voltage                                                              | $V_{DD}$             |                                                                   | 2.7                   |        | 5.5            | V     | 1     |  |  |  |

| Low-level Output Voltage                                                   | $V_{OL}$             | @ I <sub>PULLUP</sub>                                             |                       |        | 0.4            | V     | 1     |  |  |  |

| Current sinking at $V_{OL} = 0.4 \text{ V}$                                | I <sub>PULLUP</sub>  |                                                                   | 4                     |        |                | mA    | 1     |  |  |  |

| SCLK/SDATA<br>Clock/Data Rise Time <sup>3</sup>                            | T <sub>RI2C</sub>    | (Max VIL - 0.15) to<br>(Min VIH + 0.15)                           |                       |        | 1000           | ns    | 1     |  |  |  |

| SCLK/SDATA<br>Clock/Data Fall Time <sup>3</sup>                            | T <sub>FI2C</sub>    | (Min VIH + 0.15) to<br>(Max VIL - 0.15)                           |                       |        | 300            | ns    | 1     |  |  |  |

<sup>&</sup>lt;sup>1</sup>Guaranteed by design and characterization, not 100% tested in production.

<sup>&</sup>lt;sup>2</sup>See timing diagrams for timing requirements.

<sup>&</sup>lt;sup>3</sup> Input frequency should be measured at the REFOUT pin and tuned to ideal 14.31818MHz to meet ppm frequency accuracy on PLL outputs.

## **AC Electrical Characteristics - Low Power Differential PCIe Outputs**

$T_A = 0 - 70^{\circ}C$ ;  $V_{DD} = 3.3 \text{ V +/-5\%}$ ;  $C_L = 2pF$ ,  $R_S = 33.2\Omega$

| 1 <sub>A</sub> = 0 - 70 C, V <sub>DD</sub> = 3.3 V +7-3/8, C <sub>L</sub> =2pr, n <sub>S</sub> =33.232 |                      |                          |      |     |      |       |       |  |  |

|--------------------------------------------------------------------------------------------------------|----------------------|--------------------------|------|-----|------|-------|-------|--|--|

| PARAMETER                                                                                              | SYMBOL               | CONDITIONS               | MIN  | TYP | MAX  | UNITS | NOTES |  |  |

| Rising Edge Slew Rate                                                                                  | t <sub>SLR</sub>     | Differential Measurement | 0.5  |     | 2    | V/ns  | 1,2   |  |  |

| Falling Edge Slew Rate                                                                                 | t <sub>FLR</sub>     | Differential Measurement | 0.5  |     | 2    | V/ns  | 1,2   |  |  |

| Slew Rate Variation                                                                                    | t <sub>SLVAR</sub>   | Single-ended Measurement |      |     | 20   | %     | 1     |  |  |

| Maximum Output<br>Voltage                                                                              | $V_{HIGH}$           | Includes overshoot       |      |     | 1150 | mV    | 1     |  |  |

| Minimum Output Voltage                                                                                 | $V_{LOW}$            | Includes undershoot      | -300 |     |      | mV    | 1     |  |  |

| Differential Voltage<br>Swing                                                                          | $V_{SWING}$          | Differential Measurement | 400  |     |      | mV    | 1     |  |  |

| Crossing Point Voltage                                                                                 | $V_{XABS}$           | Single-ended Measurement | 300  |     | 550  | mV    | 1,3,4 |  |  |

| Crossing Point Variation                                                                               | $V_{XABSVAR}$        | Single-ended Measurement |      |     | 140  | mV    | 1,3,5 |  |  |

| Duty Cycle                                                                                             | D <sub>CYC</sub>     | Differential Measurement | 45   |     | 55   | %     | 1     |  |  |

| PCIe Jitter - Cycle to<br>Cycle                                                                        | PCleJ <sub>C2C</sub> | Differential Measurement |      |     | 125  | ps    | 1     |  |  |

| PCIe[6:0] Skew                                                                                         | PCIe <sub>SKEW</sub> | Differential Measurement |      |     | 250  | ps    | 1     |  |  |

#### **Notes on Electrical Characteristics:**

## **PCIe Phase Jitter Impact**

| 1 Old I Hadd dittol III                 | .puot            |                                                                 |     |         |     |           |         |

|-----------------------------------------|------------------|-----------------------------------------------------------------|-----|---------|-----|-----------|---------|

| Parameter                               |                  | Conditions                                                      | Min | Typical | Max | Units     | Notes   |

| Output phase jitter impact – PCIe* Gen1 | $\theta_{PCle1}$ | (including PLL BW 1.5-22 MHz, z = 0.54, Td=10 ns, Ftrk=1.5 MHz) | 0   |         | 108 | ps        | 1,2,3,4 |

| Output phase jitter impact - PCIe Gen2  | $\theta_{PCle2}$ | (including PLL BW5-16 MHz,<br>8 – 16 MHz, z = 0.54, Td=10 ns)   | 0   |         | 3.1 | ps<br>RMS | 1,2,3,4 |

#### NOTES:

- 1. Post processed evaluation through Intel supplied Matlab scripts.

- 2. PCle\* Gen2 filter characteristics are subject to final ratification by PC ISIG. Please check the PCl\* SIG for the latest specification.

- 3. These jitter numbers are defined for a BER of 1E-12. Measured numbers at a smaller sample size have to be extrapolated to this BER target.

- 4. Guaranteed by design and characterization, not 100% tested in production.

<sup>&</sup>lt;sup>1</sup>Guaranteed by design and characterization, not 100% tested in production.

<sup>&</sup>lt;sup>2</sup> Slew rate measured through Vswing centered around differential zero

<sup>&</sup>lt;sup>3</sup> Vxabs is defined as the voltage where CLK = CLK#

<sup>&</sup>lt;sup>4</sup> Only applies to the differential rising edge (CLK rising and CLK# falling)

$<sup>^{\</sup>rm 5}$  Defined as the total variation of all crossing voltages of CLK rising and CLK# falling.

<sup>&</sup>lt;sup>6</sup> All Long Term Accuracy and Clock Period specifications are guaranteed assuming that REFOUT is at 14.31818MHz

## **AC Electrical Characteristics - Low Power Differential CPU Outputs**

$T_{\Delta} = 0 - 70^{\circ}\text{C}$ ;  $V_{DD} = 3.3 \text{ V} + /-5\%$ ;  $C_{L} = \text{AMD64 Processor Test Load}$

| $I_A = 0 \cdot 70  \text{C},  V_{DD} = 3.3  \text{V}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | T/-3 /0, OL -/ IVI       | DUT I TUCESSUI TESI LUAU                      |       |     |      |       |       |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|-----------------------------------------------|-------|-----|------|-------|-------|--|--|--|

| PARAMETER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | SYMBOL                   | CONDITIONS                                    | MIN   | TYP | MAX  | UNITS | NOTES |  |  |  |

| Crossing Point Variation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | $\Delta V_{	ext{CROSS}}$ | Single-ended Measurement                      |       |     | 140  | mV    | 1     |  |  |  |

| Frequency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | f                        |                                               | 198.8 |     | 200  | MHz   | 2     |  |  |  |

| Long Term Accuracy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ppm                      |                                               | -300  |     | 300  | ppm   | 3     |  |  |  |

| Rising Edge Slew Rate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | t <sub>SLR</sub>         | Differential Measurement                      | 0.5   |     | 10   | V/ns  | 4,5   |  |  |  |

| Falling Edge Slew Rate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | $t_{FLR}$                | Differential Measurement                      | 0.5   |     | 10   | V/ns  | 4,5   |  |  |  |

| CPU Jitter - Cycle to<br>Cycle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | CPUJ <sub>C2C</sub>      | Differential Measurement                      |       |     | 150  | ps    | 6     |  |  |  |

| CPU Jitter - Accumulated                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | CPUJ <sub>ACC</sub>      | Over a 10 uS period                           | -1    |     | 1    | ns    | 7     |  |  |  |

| Maximum Output Voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | $V_{HIGH}$               | Includes overshoot, single-ended measurement  |       |     | 1150 | mV    | 1     |  |  |  |

| Minimum Output Voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | $V_{LOW}$                | Includes undershoot, single-ended measurement | -300  |     |      | mV    | 1     |  |  |  |

| Differential Voltage Swing<br>Peak-to-Peak                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | $V_{DPK-PK}$             | Differential Measurement                      | 400   |     | 2400 | mV    | 8     |  |  |  |

| Differential Voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | $V_D$                    | Differential Measurement                      | 200   |     | 1200 | mV    | 9     |  |  |  |

| Change in V <sub>D</sub> DC cycle-to-<br>cycle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | $\Delta V_D$             | Single-ended Measurement                      | -75   |     | 75   | mV    | 10    |  |  |  |

| Duty Cycle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | $D_{CYC}$                | Differential Measurement                      | 45    |     | 55   | %     | 11    |  |  |  |

| CPU[6:0] Skew                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | CPU <sub>SKEW10</sub>    | Differential Measurement                      |       |     | 250  | ps    |       |  |  |  |

| Laborate Florida Characteristics (Occupants of the Action and absorbed in the 100% total discuss of the Company |                          |                                               |       |     |      |       |       |  |  |  |

Notes on Electrical Characteristics (Guaranteed by design and characterization, not 100% tested in production):

<sup>&</sup>lt;sup>1</sup>Single-ended measurement at crossing point. Value is max-min over all time. DC value of common mode is not important due to the blocking cap.

<sup>&</sup>lt;sup>2</sup> Minimum frequency results from 0.5% down spread.

<sup>&</sup>lt;sup>3</sup> Measured with spread spectrum off.

<sup>&</sup>lt;sup>4</sup> This parameter is intended to give guidance for simulation.

<sup>&</sup>lt;sup>5</sup> Differential measurement through the range of +/-100mV

<sup>&</sup>lt;sup>6</sup> Between any two adjacent cycles.

<sup>&</sup>lt;sup>7</sup> Accumulated over a 10 uS time periode, measured with JIT2 TIE at 50ps interval.

<sup>&</sup>lt;sup>8</sup> V<sub>DPK-PK</sub> is the overall magnitude of the differential signal.