Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

#### RD890 SYSTEM CLOCK FOR AMD-BASED SERVERS

932S890C

## **General Description**

The 932S890C is a main clock synthesizer chip for SR5690/SR5670 AMD Servers. An SMBus interface allows full control of the device.

## **Recommended Application**

SR5690/SR5670 AMD-based Servers

## **Output Features**

- Low power differential outputs with integrated series resistors for Zo=50ohm systems

- · 4 -Differential 200MHz CPU pairs

- 2 Differential 100MHz HT3 pairs

- 14 Differential PCIe Gen2 SRC pairs

- 1 Differential non-spread SATA clock

- 2 48MHz USB clocks (180 degrees out of phase for EMI reduction)

- 2 SIO clocks (selectable 48MHz or 24MHz). 180 degrees out of phase for EMI reduction

- 2 14.318MHz REF clock outputs

#### Features/Benefits

- · Spread Spectrum; EMI reduction

- Outputs may be disabled via SMBus; saves power

- External crystal load capacitors; maximum frequency accuracy

### **Key Specifications**

- CPU output cycle-to-cycle jitter <100ps

- SRC output cycle-to-cycle jitter <125ps

- 48MHz output cycle-to-cycle jitter <130ps

- SIO output cycle-to-cycle jitter <150ps</li>

- SRC output phase jitter <3.1ps rms (PCle Gen2)

- +/- 50ppm frequency accuracy on all clocks, assuming REF is trimmed to 0 ppm)

#### Table 1: 932 S890 Functionality

| CPU    | HTT    | SRC    | SATA   | REF    | SIO   | USB   | DOT   |

|--------|--------|--------|--------|--------|-------|-------|-------|

| MHz    | MHz    | MHz    | SAIA   | MHz    | 310   | MHz   | MHz   |

| 200.00 | 100.00 | 100.00 | 100.00 | 14.318 | 24/48 | 48.00 | 96.00 |

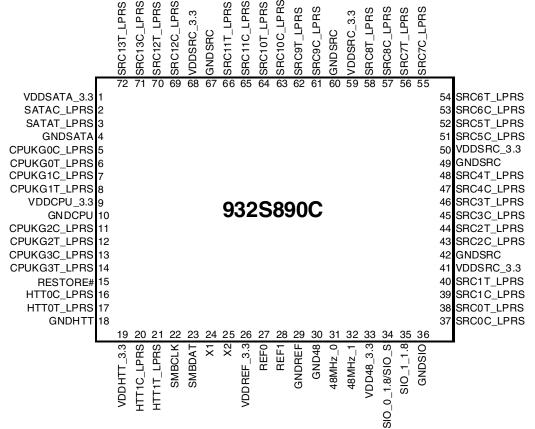

## **Pin Configuration**

<sup>\*</sup> Indicates that pin has 120Kohm internal pullup resistor.

# **Pin Descriptions**

| PIN # | PIN NAME          | PIN TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                             |

|-------|-------------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | VDDSATA_3.3       | PWR      | Power supply for SATA core logic, nominal 3.3V                                                                                                                                                                                                                                                                                          |

| 2     | SATAC_LPRS        | OUT      | Complement clock of low power differential SATA clock pair. (no 50 ohm shunt resistor to GND and no 33 ohm series resistor needed)                                                                                                                                                                                                      |

| 3     | SATAT_LPRS        | OUT      | True clock of low power differential SATA clock pair. (no 50 ohm shunt resistor to GND and no 33 ohm series resistor needed)                                                                                                                                                                                                            |

| 4     | GNDSATA           | GND      | Ground pin for the SATA output                                                                                                                                                                                                                                                                                                          |

| 5     | CPUKG0C_LPRS      | OUT      | Complementary signal of low-power differential push-pull AMD "Greyhound" clock with integrated series resistor. (no 33 ohm series resistor needed and no 50 ohm pull down resistor needed)                                                                                                                                              |

| 6     | CPUKG0T_LPRS      | OUT      | True signal of low-power differential push-pull AMD "Greyhound" CPU clock with integrated series resistor(no 33 ohm series resistor needed and no 50 ohm pull down resistor needed)                                                                                                                                                     |

| 7     | CPUKG1C_LPRS      | OUT      | Complementary signal of low-power differential push-pull AMD "Greyhound" CPU clock with integrated series resistor. (no 33 ohm series resistor needed and no 50 ohm pull down resistor needed)                                                                                                                                          |

| 8     | CPUKG1T_LPRS      | OUT      | True signal of low-power differential push-pull AMD "Greyhound" CPU clock with integrated series resistor(no 33 ohm series resistor needed and no 50 ohm pull down resistor needed)                                                                                                                                                     |

| 9     | VDDCPU_3.3        | PWR      | Supply for CPU core and outputs, 3.3V nominal                                                                                                                                                                                                                                                                                           |

| 10    | GNDCPU            | GND      | Ground pin for the CPU outputs                                                                                                                                                                                                                                                                                                          |

| 11    | CPUKG2C_LPRS      | OUT      | Complementary signal of low-power differential push-pull AMD "Greyhound" CPU clock with integrated series resistor. (no 33 ohm series resistor needed and no 50 ohm pull down resistor needed)                                                                                                                                          |

| 12    | CPUKG2T_LPRS      | OUT      | True signal of low-power differential push-pull AMD "Greyhound" CPU clock with integrated series resistor(no 33 ohm series resistor needed and no 50 ohm pull down resistor needed)                                                                                                                                                     |

| 13    | CPUKG3C_LPRS      | OUT      | Complementary signal of low-power differential push-pull AMD "Greyhound" CPU clock with integrated series resistor. (no 33 ohm series resistor needed and no 50 ohm pull down resistor needed)                                                                                                                                          |

| 14    | CPUKG3T_LPRS      | OUT      | True signal of low-power differential push-pull AMD "Greyhound" CPU clock with integrated series resistor(no 33 ohm series resistor needed and no 50 ohm pull down resistor needed)                                                                                                                                                     |

| 15    | RESTORE#          | I/O      | Open Drain I/O. As an input it restores the PLL's to power up default state. As an output, this signal is driven low when the internal watchdog hardware timer expires. It is cleared when the internal watchdog hardware timer is reset or disabled. The input is falling edge triggered.  0 = Restore Settings, 1 = normal operation. |

| 16    | HTT0C_LPRS        | OUT      | Complementary signal of low-power differential push-pull Hypertransport 3 clock with integrated series resistor. (no 50 ohm shunt resistor to GND and no 33 ohm series resistor needed)                                                                                                                                                 |

| 17    | HTT0T_LPRS        | OUT      | True signal of low-power differential push-pull Hypertransport 3 clock with integrated series resistor. (no 50 ohm shunt resistor to GND and no 33 ohm series resistor needed)                                                                                                                                                          |

| 18    | GNDHTT            | PWR      | Ground pin for the HTT outputs                                                                                                                                                                                                                                                                                                          |

| 19    | VDDHTT_3.3        | PWR      | Supply for HTT clocks, nominal 3.3V.                                                                                                                                                                                                                                                                                                    |

| 20    | HTT1C_LPRS        | OUT      | Complementary signal of low-power differential push-pull Hypertransport 3 clock with integrated series resistor. (no 50 ohm shunt resistor to GND and no 33 ohm series resistor needed)                                                                                                                                                 |

| 21    | HTT1T_LPRS        | OUT      | True signal of low-power differential push-pull Hypertransport 3 clock with integrated series resistor. (no 50 ohm shunt resistor to GND and no 33 ohm series resistor needed)                                                                                                                                                          |

| 22    | SMBCLK            | IN       | Clock pin of SMBus circuitry, 5V tolerant.                                                                                                                                                                                                                                                                                              |

| 23    | SMBDAT            | I/O      | Data pin for SMBus circuitry, 5V tolerant.                                                                                                                                                                                                                                                                                              |

| 24    | X1                | IN       | Crystal input, nominally 14.318MHz                                                                                                                                                                                                                                                                                                      |

| 25    | X2                | OUT      | Crystal output, nominally 14.318MHz                                                                                                                                                                                                                                                                                                     |

| 26    | VDDREF_3.3        | PWR      | Ref, XTAL power supply, nominal 3.3V                                                                                                                                                                                                                                                                                                    |

|       | REF0              | OUT      | 14.318 MHz reference clock, 3.3V                                                                                                                                                                                                                                                                                                        |

| 28    | REF1              | OUT      | 14.318 MHz reference clock, 3.3V                                                                                                                                                                                                                                                                                                        |

| 29    | GNDREF            | GND      | Ground pin for the REF outputs.                                                                                                                                                                                                                                                                                                         |

|       | GND48             | GND      | Ground pin for the 48MHz outputs                                                                                                                                                                                                                                                                                                        |

| 31    | 48MHz_0           | OUT      | 48MHz clock output.                                                                                                                                                                                                                                                                                                                     |

| 32    | 48MHz_1           | OUT      | 48MHz clock output. (180 degrees out of phase with 48MHz_0)                                                                                                                                                                                                                                                                             |

| 33    | VDD48_3.3         | PWR      | Power pin for the 48MHz and SIO outputs and core. 3.3V                                                                                                                                                                                                                                                                                  |

| 34    | SIO_0_1.8/SIO_SEL | I/O      | Selectable 48MHz or 24MHz output/SIO Select Latched Input<br>0 = 24MHz, 1 = 48MHz.                                                                                                                                                                                                                                                      |

|       | SIO_1_1.8         | OUT      | Selectable 48MHz or 24MHz output. (180 out of phase with SIO 0. Selected by SIO latched input. 0 = 24MHz, 1 = 48MHz.                                                                                                                                                                                                                    |

| 36    | GNDSIO            | GND      | Ground pin for the SIO outputs                                                                                                                                                                                                                                                                                                          |

# **Pin Descriptions (cont.)**

| PIN # PIN TYPE |             | PIN TYPE | DESCRIPTION                                                                                                                        |

|----------------|-------------|----------|------------------------------------------------------------------------------------------------------------------------------------|

|                |             |          | Complement clock of low power differential SRC clock pair. (no 50 ohm shunt resistor to GND and no 33 ohm                          |

| 37             | SRC0C_LPRS  | OUT      | series resistor needed)                                                                                                            |

|                |             |          | True clock of low power differential SRC clock pair. (no 50 ohm shunt resistor to GND and no 33 ohm series                         |

| 38             | SRC0T_LPRS  | OUT      | resistor needed)                                                                                                                   |

|                |             |          | Complement clock of low power differential SRC clock pair. (no 50 ohm shunt resistor to GND and no 33 ohm                          |

| 39             | SRC1C_LPRS  | OUT      | series resistor needed)                                                                                                            |

|                |             | +        | True clock of low power differential SRC clock pair. (no 50 ohm shunt resistor to GND and no 33 ohm series                         |

| 40             | SRC1T_LPRS  | OUT      | resistor needed)                                                                                                                   |

| 41             | VDDSRC_3.3  | PWR      | Supply for SRC core and outputs, 3.3V nominal                                                                                      |

|                | GNDSRC      | GND      | Ground pin for the SRC outputs                                                                                                     |

|                |             |          | Complement clock of low power differential SRC clock pair. (no 50 ohm shunt resistor to GND and no 33 ohm                          |

| 43             | SRC2C_LPRS  | OUT      | series resistor needed)                                                                                                            |

|                |             | +        | True clock of low power differential SRC clock pair. (no 50 ohm shunt resistor to GND and no 33 ohm series                         |

| 44             | SRC2T_LPRS  | OUT      | resistor needed)                                                                                                                   |

|                |             | +        | Complement clock of low power differential SRC clock pair. (no 50 ohm shunt resistor to GND and no 33 ohm                          |

| 45             | SRC3C_LPRS  | OUT      | series resistor needed)                                                                                                            |

|                |             |          | True clock of low power differential SRC clock pair. (no 50 ohm shunt resistor to GND and no 33 ohm series                         |

| 46             | SRC3T_LPRS  | OUT      | resistor needed)                                                                                                                   |

|                |             | _        | Complement clock of low power differential SRC clock pair. (no 50 ohm shunt resistor to GND and no 33 ohm                          |

| 47             | SRC4C_LPRS  | OUT      | series resistor needed)                                                                                                            |

|                | 000151555   |          | True clock of low power differential SRC clock pair. (no 50 ohm shunt resistor to GND and no 33 ohm series                         |

| 48             | SRC4T_LPRS  | OUT      | resistor needed)                                                                                                                   |

| 49             | GNDSRC      | GND      | Ground pin for the SRC outputs                                                                                                     |

| 50             | VDDSRC_3.3  | PWR      | Supply for SRC core and outputs, 3.3V nominal                                                                                      |

|                |             |          | Complement clock of low power differential SRC clock pair. (no 50 ohm shunt resistor to GND and no 33 ohm                          |

| 51             | SRC5C_LPRS  | OUT      | series resistor needed)                                                                                                            |

|                |             | a        | True clock of low power differential SRC clock pair. (no 50 ohm shunt resistor to GND and no 33 ohm series                         |

| 52             | SRC5T_LPRS  | OUT      | resistor needed)                                                                                                                   |

|                | 00000 1000  | OUT      | Complement clock of low power differential SRC clock pair. (no 50 ohm shunt resistor to GND and no 33 ohm                          |

| 53             | SRC6C_LPRS  | OUT      | series resistor needed)                                                                                                            |

|                | CDCCT L DDC | OUT      | True clock of low power differential SRC clock pair. (no 50 ohm shunt resistor to GND and no 33 ohm series                         |

| 54             | SRC6T_LPRS  | OUT      | resistor needed)                                                                                                                   |

| 55             | SRC7C_LPRS  | OUT      | Complement clock of low power differential SRC clock pair. (no 50 ohm shunt resistor to GND and no 33 ohm                          |

| 55             | ShC/C_LFhS  | 001      | series resistor needed)                                                                                                            |

| 56             | SRC7T_LPRS  | OUT      | True clock of low power differential SRC clock pair. (no 50 ohm shunt resistor to GND and no 33 ohm series                         |

| 30             | SHO71_LFHS  | 001      | resistor needed)                                                                                                                   |

| 57             | SRC8C_LPRS  | OUT      | Complement clock of low power differential SRC clock pair. (no 50 ohm shunt resistor to GND and no 33 ohm                          |

|                | CHOOC_LITTO | 001      | series resistor needed)                                                                                                            |

| 58             | SRC8T_LPRS  | OUT      | True clock of low power differential SRC clock pair. (no 50 ohm shunt resistor to GND and no 33 ohm series                         |

|                |             |          | resistor needed)                                                                                                                   |

| 59             | VDDSRC_3.3  | PWR      | Supply for SRC core and outputs, 3.3V nominal                                                                                      |

| 60             | GNDSRC      | GND      | Ground pin for the SRC outputs                                                                                                     |

| 61             | SRC9C_LPRS  | OUT      | Complement clock of low power differential SRC clock pair. (no 50 ohm shunt resistor to GND and no 33 ohm                          |

| <u> </u>       |             | +        | series resistor needed)                                                                                                            |

| 62             | SRC9T_LPRS  | OUT      | True clock of low power differential SRC clock pair. (no 50 ohm shunt resistor to GND and no 33 ohm series                         |

|                |             | +        | resistor needed)                                                                                                                   |

| 63             | SRC10C_LPRS | OUT      | Complement clock of low power differential SRC clock pair. (no 50 ohm shunt resistor to GND and no 33 ohm                          |

| -              |             | +        | series resistor needed) True clock of low power differential SRC clock pair. (no 50 ohm shunt resistor to GND and no 33 ohm series |

| 64             | SRC10T_LPRS | OUT      | resistor needed)                                                                                                                   |

| -              |             | +        | Complement clock of low power differential SRC clock pair. (no 50 ohm shunt resistor to GND and no 33 ohm                          |

| 65             | SRC11C_LPRS | OUT      | series resistor needed)                                                                                                            |

|                |             | +        | True clock of low power differential SRC clock pair. (no 50 ohm shunt resistor to GND and no 33 ohm series                         |

| 66             | SRC11T_LPRS | OUT      | resistor needed)                                                                                                                   |

| 67             | GNDSRC      | GND      | Ground pin for the SRC outputs                                                                                                     |

| 68             | VDDSRC_3.3  | PWR      | Supply for SRC core and outputs, 3.3V nominal                                                                                      |

|                |             |          | Complement clock of low power differential SRC clock pair. (no 50 ohm shunt resistor to GND and no 33 ohm                          |

| 69             | SRC12C_LPRS | OUT      | series resistor needed)                                                                                                            |

|                |             | 1 .      | True clock of low power differential SRC clock pair. (no 50 ohm shunt resistor to GND and no 33 ohm series                         |

| 70             | SRC12T_LPRS | OUT      | resistor needed)                                                                                                                   |

|                |             | 1 -      | Complement clock of low power differential SRC clock pair. (no 50 ohm shunt resistor to GND and no 33 ohm                          |

| 71             | SRC13C_LPRS | OUT      | series resistor needed)                                                                                                            |

|                |             | 1 .      | True clock of low power differential SRC clock pair. (no 50 ohm shunt resistor to GND and no 33 ohm series                         |

| 72             | SRC13T_LPRS | OUT      | resistor needed)                                                                                                                   |

|                | ·           |          |                                                                                                                                    |

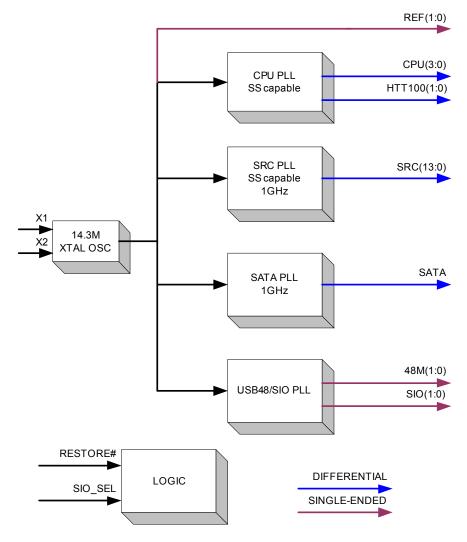

# **Block Diagram**

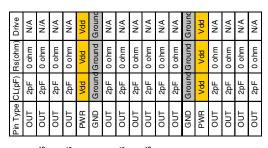

932S890 Power Hookup

| Pin No      | umber       | Description              |

|-------------|-------------|--------------------------|

| VDD         | GND         | Description              |

| 1 4         |             | SATA PLL and output      |

| 9 10        |             | CPU PLL and outputs      |

| 19          | 18          | HTT outputs              |

| 26          | 29          | XTAL Osc and REF outputs |

| 33          | 30          | 48MHz PLL and Outputs    |

| 33 36       |             | SIO Outputs              |

| 41, 50, 59, | 42, 49, 60, | SRC PLL and Outputs      |

| 68          | 67          | Sho PLL and Outputs      |

Table 2: IO\_Vout select table

| B5b2 | B5b1 | B5b0 | IO_Vout |

|------|------|------|---------|

| 0    | 0    | 0    | 0.3V    |

| 0    | 0    | 1    | 0.4V    |

| 0    | 1    | 0    | 0.5V    |

| 0    | 1    | 1    | 0.6V    |

| 1    | 0    | 0    | 0.7V    |

| 1    | 0    | 1    | 0.8V    |

| 1    | 1    | 0    | 0.9V    |

| 1    | 1    | 1    | 1.0V    |

### **CPU Frequency Selection Table**

|      | CPU FS4 | CPU FS3 |         |         |         |          |          |            |

|------|---------|---------|---------|---------|---------|----------|----------|------------|

|      | Byte 3, | Byte 3, | CPU FS2 | CPU FS1 | CPU FS0 | CPU      | HTT      |            |

| Line | bit 4   | bit 3   | Byte3,  | Byte3,  | Byte3,  | Speed    | Speed    | Spread     |

|      | (Spread | (DN/CTR | bit2    | bit1    | bit0    | (MHz)    | (MHz)    | %          |

|      | Enable) | Spread) | DILE    | Dit i   | Bit 0   | (111112) | (111112) |            |

| 0    | 0       | 0       | 0       | 0       | 0       | 184.47   | 92.24    |            |

| 1    | 0       | 0       | 0       | 0       | 1       | 188.24   | 94.12    |            |

| 2    | 0       | 0       | 0       | 1       | 0       | 192.08   | 96.04    |            |

| 3    | 0       | 0       | 0       | 1       | 1       | 196.00   | 98.00    | SSOFF      |

| 4    | 0       | 0       | 1       | 0       | 0       | 200.00   | 100.00   | 0%         |

| 5    | 0       | 0       | 1       | 0       | 1       | 204.00   | 102.00   |            |

| 6    | 0       | 0       | 1       | 1       | 0       | 208.08   | 104.04   |            |

| 7    | 0       | 0       | 1       | 1       | 1       | 212.24   | 106.12   |            |

| 8    | 0       | 1       | 0       | 0       | 0       | 184.47   | 92.24    |            |

| 9    | 0       | 1       | 0       | 0       | 1       | 188.24   | 94.12    |            |

| 10   | 0       | 1       | 0       | 1       | 0       | 192.08   | 96.04    |            |

| 11   | 0       | 1       | 0       | 1       | 1       | 196.00   | 98.00    | SS OFF     |

| 12   | 0       | 1       | 1       | 0       | 0       | 200.00   | 100.00   | 0%         |

| 13   | 0       | 1       | 1       | 0       | 1       | 204.00   | 102.00   |            |

| 14   | 0       | 1       | 1       | 1       | 0       | 208.08   | 104.04   |            |

| 15   | 0       | 1       | 1       | 1       | 1       | 212.24   | 106.12   |            |

| 16   | 1       | 0       | 0       | 0       | 0       | 184.47   | 92.24    |            |

| 17   | 1       | 0       | 0       | 0       | 1       | 188.24   | 94.12    |            |

| 18   | 1       | 0       | 0       | 1       | 0       | 192.08   | 96.04    | DOWN       |

| 19   | 1       | 0       | 0       | 1       | 1       | 196.00   | 98.00    | SPREAD'-   |

| 20   | 1       | 0       | 1       | 0       | 0       | 200.00   | 100.00   | 0.5%       |

| 21   | 1       | 0       | 1       | 0       | 1       | 204.00   | 102.00   | 0.5%       |

| 22   | 1       | 0       | 1       | 1       | 0       | 208.08   | 104.04   |            |

| 23   | 1       | 0       | 1       | 1       | 1       | 212.24   | 106.12   |            |

| 24   | 1       | 1       | 0       | 0       | 0       | 184.47   | 92.24    |            |

| 25   | 1       | 1       | 0       | 0       | 1       | 188.24   | 94.12    |            |

| 26   | 1       | 1       | 0       | 1       | 0       | 192.08   | 96.04    | CENTER     |

| 27   | 1       | 1       | 0       | 1       | 1       | 196.00   | 98.00    | SPREAD     |

| 28   | 1       | 1       | 1       | 0       | 0       | 200.00   | 100.00   | '+/-0.25%  |

| 29   | 1       | 1       | 1       | 0       | 1       | 204.00   | 102.00   | +/ 0.23 /0 |

| 30   | 1       | 1       | 1       | 1       | 0       | 208.08   | 104.04   |            |

| 31   | 1       | 1       | 1       | 1       | 1       | 212.24   | 106.12   |            |

**SRC Frequency Selection Table**

|      | SRC FS4 | SRC FS3  | e       | 000 504 | 000 500 |        |                     |  |

|------|---------|----------|---------|---------|---------|--------|---------------------|--|

|      | Byte 4, | Byte 4,  | SRC FS2 | SRC FS1 | SRC FS0 | SRC    | Sprd                |  |

|      | bit 4   | bit 3    | Byte 4, | Byte 4, | Byte 4, | (MHz)  | %                   |  |

| Lina | (Spread | (DWN/CTR | bit2    | bit1    | bit0    | , ,    |                     |  |

| Line | Enable) | Spread)  |         |         |         |        |                     |  |

| 0    | 0       | 0        | 0       | 0       | 0       | 92.24  |                     |  |

| 1    | 0       | 0        | 0       | 0       | 1       | 94.12  |                     |  |

| 2    | 0       | 0        | 0       | 1       | 0       | 96.04  | 00.055              |  |

| 3    | 0       | 0        | 0       | 1       | 1       | 98.00  | SS OFF              |  |

| 4    | 0       | 0        | 1       | 0       | 0       | 100.00 | 0%                  |  |

| 5    | 0       | 0        | 1       | 0       | 1       | 102.00 |                     |  |

| 6    | 0       | 0        | 1       | 1       | 0       | 104.04 | l I                 |  |

| 7    | 0       | 0        | 1       | 1       | 1       | 106.12 |                     |  |

| 8    | 0       | 1        | 0       | 0       | 0       | 92.24  |                     |  |

| 9    | 0       | 1        | 0       | 0       | 1       | 94.12  |                     |  |

| 10   | 0       | 1        | 0       | 1       | 0       | 96.04  |                     |  |

| 11   | 0       | 1        | 0       | 1       | 1       | 98.00  | SS OFF<br>0%        |  |

| 12   | 0       | 1        | 1       | 0       | 0       | 100.00 |                     |  |

| 13   | 0       | 1        | 1       | 0       | 1       | 102.00 |                     |  |

| 14   | 0       | 1        | 1       | 1       | 0       | 104.04 |                     |  |

| 15   | 0       | 1        | 1       | 1       | 1       | 106.12 |                     |  |

| 16   | 1       | 0        | 0       | 0       | 0       | 92.24  |                     |  |

| 17   | 1       | 0        | 0       | 0       | 1       | 94.12  | 1                   |  |

| 18   | 1       | 0        | 0       | 1       | 0       | 96.04  | DOMAL               |  |

| 19   | 1       | 0        | 0       | 1       | 1       | 98.00  | DOWN                |  |

| 20   | 1       | 0        | 1       | 0       | 0       | 100.00 | SPREAD'-            |  |

| 21   | 1       | 0        | 1       | 0       | 1       | 102.00 | 0.5%                |  |

| 22   | 1       | 0        | 1       | 1       | 0       | 104.04 |                     |  |

| 23   | 1       | 0        | 1       | 1       | 1       | 106.12 | 1                   |  |

| 24   | 1       | 1        | 0       | 0       | 0       | 92.24  |                     |  |

| 25   | 1       | 1        | 0       | 0       | 1       | 94.12  |                     |  |

| 26   | 1       | 1        | 0       | 1       | 0       | 96.04  | OFNITES             |  |

| 27   | 1       | 1        | 0       | 1       | 1       | 98.00  | CENTER              |  |

| 28   | 1       | 1        | 1       | 0       | 0       | 100.00 | SPREAD<br>'+/-0.25% |  |

| 29   | 1       | 1        | 1       | 0       | 1       | 102.00 |                     |  |

| 30   | 1       | 1        | 1       | 1       | 0       | 104.04 | 1                   |  |

| 31   | 1       | 1        | 1       | 1       | 1       | 106.12 |                     |  |

## **Absolute Maximum Ratings**

Stresses above the ratings listed below can cause permanent damage to the 932S890C. These ratings, which are standard values for IDT commercially rated parts, are stress ratings only. Functional operation of the device at these or any other conditions above those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods can affect product reliability. Electrical parameters are guaranteed only over the recommended operating temperature range.

| PARAMETER                | SYMBOL   | CONDITIONS | MIN  | TYP | MAX        | UNITS | Notes |

|--------------------------|----------|------------|------|-----|------------|-------|-------|

| 3.3V Core Supply Voltage | VDDxxx   | -          |      | 3.3 | GND + 3.9V | ٧     | 1     |

| Storage Temperature      | Ts       | -          | -65  |     | 150        | °C    | 1     |

| Ambient Operating Temp   | Tambient | -          | 0    |     | 70         | °C    | 1     |

| Case Temperature         | Tcase    | -          |      |     | 115        | °C    | 1     |

| Input ESD protection HBM | ESD prot | -          | 2000 |     |            | V     | 1     |

<sup>&</sup>lt;sup>1</sup>Guaranteed by design and characterization, not 100% tested in production.

## **Electrical Characteristics-Input/Supply/Common Output Parameters**

| PARAMETER                                  | SYMBOL                 | CONDITIONS*                                             | MIN                   | TYP      | MAX            | UNITS | Notes |

|--------------------------------------------|------------------------|---------------------------------------------------------|-----------------------|----------|----------------|-------|-------|

| 3.3V Core Supply Voltage                   | VDDxxx                 | -                                                       | 3.135                 | 3.3      | 3.465          | V     | 1     |

| Input High Voltage                         | $V_{IH}$               | VDD = 3.3 V +/-5%                                       | 2                     |          | $V_{DD} + 0.3$ | V     | 1     |

| Input Low Voltage                          | V <sub>IL</sub>        | VDD = 3.3 V +/-5%                                       | V <sub>SS</sub> - 0.3 |          | 0.8            | ٧     | 1     |

| Input High Current                         | I <sub>H</sub>         | $V_{IN} = V_{DD}$                                       | -5                    |          | 5              | uA    | 1     |

| Input Low Current                          | I <sub>IL1</sub>       | V <sub>IN</sub> = 0 V; Inputs with no pull-up resistors | -5                    |          |                | uA    | 1     |

| mpat Low Current                           | l <sub>IL2</sub>       | V <sub>IN</sub> = 0 V; Inputs with pull-up resistors    | -200                  |          |                | uA    | 1     |

| Operating Current                          | I <sub>DD3.3OP</sub>   | all outputs driven                                      |                       |          | 250            | mA    | 1     |

| Input Frequency                            | Fi                     | VDD = 3.3 V +/-5%                                       |                       | 14.31818 |                | MHz   | 2     |

| Pin Inductance                             | $L_{pin}$              |                                                         |                       |          | 7              | nΗ    | 1     |

|                                            | C <sub>IN</sub>        | Logic Inputs                                            |                       |          | 5              | pF    | 1     |

| Input Capacitance                          | C <sub>OUT</sub>       | Output pin capacitance                                  |                       |          | 6              | pF    | 1     |

|                                            | C <sub>INX</sub>       | X1 & X2 pins                                            |                       |          | 5              | pF    | 1     |

| Clk Stabilization                          | T <sub>STAB</sub>      | From VDD Power-Up to 1st clock                          |                       |          | 1.8            | ms    | 1     |

| Modulation Frequency                       |                        | Triangular Modulation                                   | 30                    |          | 33             | kHz   | 1     |

| SMBus Voltage                              | $V_{DDSMB}$            |                                                         | 2.7                   |          | 5.5            | V     | 1     |

| Low-level Output Voltage                   | $V_{OLSMB}$            | @ I <sub>PULLUP</sub>                                   |                       |          | 0.4            | V     | 1     |

| Current sinking at V <sub>OL</sub> = 0.4 V | I <sub>PULLUPSMB</sub> |                                                         | 4                     | 6        |                | mA    | 1     |

| SMBCLK/SMBDAT<br>Clock/Data Rise Time      | T <sub>RSMB</sub>      | (Max V IL - 0.15) to<br>(Min VIH + 0.15)                |                       |          | 1000           | ns    | 1     |

| SMBCLK/SMBDAT Clock/Data Fall Time         | $T_{FSMB}$             | (Min VIH + 0.15) to<br>(Max VIL - 0.15)                 |                       |          | 300            | ns    | 1     |

<sup>\*</sup>TA = 0 - 70°C; Supply Voltage VDD = 3.3 V + /-5%

<sup>&</sup>lt;sup>1</sup>Guaranteed by design and characterization, not 100% tested in production.

<sup>&</sup>lt;sup>2</sup> Input frequency should be measured at the REF pin and tuned to ideal 14.31818MHz to meet ppm frequency accuracy on PLL outputs.

# AC Electrical Characteristics-Low-Power DIF Outputs: CPUKG and HTT

| PARAMETER                                     | SYMBOL                | CONDITIONS                        | MIN   | TYP | MAX  | UNITS | NOTES |

|-----------------------------------------------|-----------------------|-----------------------------------|-------|-----|------|-------|-------|

| Crossing Point Variation                      | $\Delta V_{CROSS}$    | Single-ended Measurement          |       |     | 140  | mV    | 1,2,5 |

| CPU Frequency<br>(HTT = 1/2 of CPU Frequency) | f <sub>CPU</sub>      | Spread Specturm On                | 198.8 |     | 200  | MHz   | 1,3   |

| Long Term Accuracy                            | ppm                   | Spread Specturm Off               | -50   |     | +50  | ppm   | 1,11  |

| Rising Edge Slew Rate                         | S <sub>RISE</sub>     | Differential Measurement          | 0.5   |     | 10   | V/ns  | 1,4   |

| Falling Edge Slew Rate                        | S <sub>FALL</sub>     | Differential Measurement          | 0.5   |     | 10   | V/ns  | 1,4   |

| Slew Rate Variation                           | t <sub>SLVAR</sub>    | Single-ended Measurement          |       |     | 20   | %     | 1     |

| CPU, DIF HTT Jitter - Cycle to Cycle          | CPUJ <sub>C2C</sub>   | Differential Measurement          |       |     | 150  | ps    | 1,6   |

| Accumulated Jitter                            | t <sub>JACC</sub>     | See Notes                         |       |     | 1    | ns    | 1,7   |

| Peak to Peak Differential  Voltage            | $V_{D(PK-PK)}$        | Differential Measurement          | 400   |     | 2400 | mV    | 1,8   |

| Differential Voltage                          | $V_D$                 | Differential Measurement          | 200   |     | 1200 | mV    | 1,9   |

| Duty Cycle                                    | D <sub>CYC</sub>      | Differential Measurement          | 45    |     | 55   | %     | 1     |

| Amplitude Variation                           | ΔV <sub>D</sub>       | Change in $V_D$ DC cycle to cycle | -75   |     | 75   | mV    | 1,10  |

| CPU[3:0] Skew                                 | CPU <sub>SKEW30</sub> | Differential Measurement          |       |     | 200  | ps    | 1     |

| HTT[1:0] Skew                                 | HTT <sub>SKEW10</sub> | Differential Measurement          |       |     | 100  | ps    | 1     |

<sup>&</sup>lt;sup>1</sup> Guaranteed by design and characterization, not 100% tested in production.

<sup>&</sup>lt;sup>2</sup> Single-ended measurement at crossing point. Value is maximum – minimum over all time. DC value of common mode is not important due to the blocking cap.

<sup>&</sup>lt;sup>3</sup> Minimum Frequency is a result of 0.5% down spread spectrum

$<sup>^4</sup>$  Differential measurement through the range of  $\pm 100$  mV, differential signal must remain monotonic and within slew rate spec when crossing through this region.

<sup>&</sup>lt;sup>5</sup> Defined as the total variation of all crossing voltages of CLK rising and CLK# falling. Matching applies to rising edge rate of CLK and falling edge of CLK#. It is measured using a +/-75mV window centered on the average cross point where CLK meets CLK#.

$<sup>^{\</sup>widehat{\text{6}}}\text{Max}$  difference of  $t_{\text{CYCLE}}$  between any two adjacent cycles.

<sup>&</sup>lt;sup>7</sup> Accumulated tjc over a 10 µs time period, measured with JIT2 TIE at 50ps interval.

<sup>&</sup>lt;sup>8</sup> VD(PK-PK) is the overall magnitude of the differential signal.

<sup>&</sup>lt;sup>9</sup> VD(min) is the amplitude of the ring-back differential measurement, guaranteed by design, that ring-back will not cross 0V VD. VD(max) is the largest amplitude allowed.

<sup>&</sup>lt;sup>10</sup> The difference in magnitude of two adjacent VD\_DC measurements. VD\_DC is the stable post overshoot and ring-back part of the signal.

<sup>11</sup> All Long Term Accuracy and Clock Period specifications are guaranteed assuming that REFOUT is at 14.31818MHz

# AC Electrical Characteristics-Low-Power DIF Outputs: SRC, SATA

| PARAMETER                   | SYMBOL                 | CONDITIONS                                                                | MIN  | TYP  | MAX  | UNITS  | NOTES |

|-----------------------------|------------------------|---------------------------------------------------------------------------|------|------|------|--------|-------|

| SRC/SATA Frequency          | f <sub>SRC_SATA</sub>  | Spread Specturm Off                                                       |      | 100  |      | MHz    | 1,6   |

| Long Term Accuracy          | ppm                    | Spread Specturm Off                                                       | -50  |      | +50  | ppm    | 1,6   |

| Rising Edge Slew Rate       | t <sub>SLR</sub>       | Differential Measurement                                                  | 2.5  |      | 8    | V/ns   | 1,2   |

| Falling Edge Slew Rate      | t <sub>FLR</sub>       | Differential Measurement                                                  | 2.5  |      | 8    | V/ns   | 1,2   |

| Slew Rate Variation         | t <sub>SLVAR</sub>     | Single-ended Measurement                                                  |      |      | 20   | %      | 1     |

| Maximum Output Voltage      | $V_{HIGH}$             | Includes overshoot                                                        |      |      | 1150 | mV     | 1     |

| Minimum Output Voltage      | $V_{LOW}$              | Includes undershoot                                                       | -300 |      |      | mV     | 1     |

| Differential Voltage Swing  | $V_{SWING}$            | Differential Measurement                                                  | 300  |      |      | mV     | 1     |

| Crossing Point Voltage      | $V_{XABS}$             | Single-ended Measurement                                                  | 300  |      | 550  | mV     | 1,3,4 |

| Crossing Point Variation    | $V_{XABSVAR}$          | Single-ended Measurement                                                  |      |      | 140  | mV     | 1,3,5 |

| Duty Cycle                  | D <sub>CYC</sub>       | Differential Measurement                                                  | 45   |      | 55   | %      | 1     |

| Jitter - Cycle to Cycle     | SRCJ <sub>C2C</sub>    | Differential Measurement                                                  |      |      | 125  | ps     | 1     |

| SRC[13:0] Skew Even Outputs | SRC <sub>SKEW_E</sub>  | Differential Measurement                                                  |      |      | 200  | ps     | 1,8   |

| SRC[13:0] Skew Odd Outputs  | SRC <sub>SKEW_O</sub>  | Differential Measurement                                                  |      |      | 200  | ps     | 1,8   |

| SRC[13:0] Even to Odd Skew  | SRC <sub>SKEW</sub>    | Differential Measurement                                                  | 1275 | 1375 | 1475 | ps     | 1,8   |

|                             |                        | PCle Gen 1 specs<br>(1.5 - 22 MHz)                                        |      | 40   | 86   | ps     | 1, 7  |

| Jitter, Phase               | <sup>t</sup> jphaseSRC | PCIe Gen 2 (8-16 MHz, 5-16 MHz)<br>Lo-band content<br>(10kHz to 1.5MHz)   |      | 1.6  | 3    | ps rms | 1, 7  |

|                             |                        | PCIe Gen 2 (8-16 MHz, 5-16 MHz)<br>Hi-band content<br>(1.5MHz to Nyquist) |      | 2.6  | 3.1  | ps rms | 1, 7  |

<sup>&</sup>lt;sup>1</sup>Guaranteed by design and characterization, not 100% tested in production.

<sup>&</sup>lt;sup>2</sup> Slew rate measured through V swing centered around differential zero

<sup>&</sup>lt;sup>3</sup> Vxabs is defined as the voltage where CLK = CLK#

<sup>&</sup>lt;sup>4</sup> Only applies to the differential rising edge (CLK rising and CLK# falling)

<sup>&</sup>lt;sup>5</sup> Defined as the total variation of all crossing voltages of CLK rising and CLK# falling. Matching applies to rising edge rate of CLK and falling edge of CLK#. It is measured using a +/-75mV window centered on the average cross point where CLK meets CLK#.

<sup>&</sup>lt;sup>6</sup> All Long Term Accuracy and Clock Period specifications are guaranteed assuming that REFOUT is at 14.31818MHz

<sup>&</sup>lt;sup>7</sup> Applicable to all SRC outputs. See http://www.pcisig.com for complete specs. Guaranteed by design and characterization, not tested in production.

<sup>&</sup>lt;sup>8</sup> SRC outputs are divided into two banks, odd and even. The odd bank skew window is 200 ps. The even bank skew window is 200ps. The skew between the even and odd banks is intentionally set at 1375ps.

# Electrical Characteristics-USB - 48MHz, SIO 48/24MHz

| PARAMETER              | SYMBOL                 | CONDITIONS*                                    | MIN    | TYP    | MAX    | UNITS | NOTES |

|------------------------|------------------------|------------------------------------------------|--------|--------|--------|-------|-------|

| Long Accuracy          | ppm                    | see Tperiod min-max values                     | -50    |        | +50    | ppm   | 1,2   |

| Clock period           | T <sub>PERIOD</sub>    | USB output nominal                             | 20.702 | 20.833 | 20.964 | ns    | 3,5   |

| Clock Low Time         | $T_{LOW}$              | Measure from < 0.6V                            | 9.375  |        | 11.458 | ns    | 3     |

| Clock High Time        | T <sub>HIGH</sub>      | Measure from > 2.0V                            | 9.375  |        | 11.458 | ns    | 3     |

| Rise Time              | t <sub>r_USB</sub>     | $V_{OL}$ = 20% of Voh,<br>$V_{OH}$ = 80%of Voh | 0.5    |        | 3      | ns    | 1     |

| Fall Time              | t <sub>f_USB</sub>     | $V_{OL}$ = 20% of Voh,<br>$V_{OH}$ = 80%of Voh | 0.5    |        | 3      | ns    | 1     |

| Output High Voltage    | V <sub>OHUSB</sub>     | I <sub>OH</sub> = -1 mA                        | 2.4    |        |        | V     | 1,3   |

| Output Low Voltage     | V <sub>OLUSB</sub>     | I <sub>OL</sub> = 1 mA                         |        |        | 0.4    | V     | 1,3   |

| Output High Voltage    | V <sub>OHSIO</sub>     | I <sub>OH</sub> = -0.2 mA                      | 1.8    | 2      | 2.2    | V     | 1,4   |

| Output Low Voltage     | V <sub>OLSIO</sub>     | I <sub>OL</sub> = 0.2 mA                       |        |        | 0.4    | V     | 1,4   |

| Duty Cycle             | d <sub>CYCUSB</sub>    | V <sub>T</sub> = 1.5 V                         | 45     |        | 55     | %     | 1,3   |

| Skew                   | t <sub>SKEW</sub>      | V <sub>T</sub> = 1.5 V                         |        |        | 250    | ps    | 1     |

| Jitter, Cycle to cycle | ţ <sub>j</sub> cyc-cyc | V <sub>T</sub> = 1.5 V                         |        |        | 130    | ps    | 1,3   |

<sup>\*</sup>TA = 0 -  $70^{\circ}$ C; Supply Voltage VDD = 3.3 V + /-5%

### **Electrical Characteristics—REF-14.318MHz**

| PARAMETER              | SYMBOL                | CONDITIONS                                                                                                                                               | MIN     | TYP     | MAX     | UNITS | Notes |

|------------------------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|---------|---------|---------|-------|-------|

| Long Accuracy          | ppm                   | see Tperiod min-max values                                                                                                                               | -50     |         | +50     | ppm   | 1,2   |

| Long Term Jitter       | t <sub>jLT</sub>      | @ 1us                                                                                                                                                    |         |         | 500     | ps    | 1,2   |

| Clock period           | T <sub>PERIOD</sub>   | 14.318MHz output nominal                                                                                                                                 | 69.6378 | 69.8413 | 70.0448 | ns    | 2,3   |

| Clock Low Time         | $T_{LOW}$             | Measure from $V_T = 50\%$                                                                                                                                | 2       |         |         | ns    | 2     |

| Clock High Time        | T <sub>HIGH</sub>     | Measure from $V_T = 50\%$                                                                                                                                | 2       |         |         | ns    | 2     |

| Output High Voltage    | V <sub>OH</sub>       | I <sub>OH</sub> = -1 mA                                                                                                                                  | 2.4     | 2.8     | 3.3     | V     | 1     |

| Output Low Voltage     | $V_{OL}$              | I <sub>OL</sub> = 1 mA                                                                                                                                   | 0       |         | 0.4     | V     | 1     |

| Rise Time              | t <sub>R</sub>        | $V_{OL} = 20\%$ of $V_{OH}$ ,<br>$V_{OH} = 80\%$ of $V_{OH}$                                                                                             |         |         | 1.5     | ns    | 1     |

| Fall Time              | t <sub>F</sub>        | $V_{OL} = 20\%$ of $V_{OH}$ ,<br>$V_{OH} = 80\%$ of $V_{OH}$                                                                                             |         |         | 1.5     | ns    | 1     |

| Skew                   | t <sub>SKEW</sub>     | Measure from $V_T = 50\%$                                                                                                                                |         |         | 250     | ps    | 1     |

| Duty Cycle             | d <sub>t1</sub>       | $V_T = V_{OH}/2$                                                                                                                                         | 45      |         | 55      | %     | 1     |

| Jitter, Cycle to Cycle | t <sub>jcyc-cyc</sub> | Measure from $V_T = 50\%$                                                                                                                                |         |         | 200     | ps    | 1     |

| Jitter, Peak to Peak   | t <sub>jPK-PK</sub>   | $\begin{aligned} &\text{Measure from V}_T = 50\% \text{ (0.9V)} \\ &t_{jpk-pk} = &[ t_{jcyc\text{-cyc}}max  +  t_{jcyc\text{-cyc}}min ]/2 \end{aligned}$ |         |         | 200     | ps    | 1     |

<sup>\*</sup>TA = 0 - 70°C; Supply Voltage VDD = 3.3 V + /-5%

<sup>&</sup>lt;sup>1</sup>Guaranteed by design and characterization, not 100% tested in production.

<sup>&</sup>lt;sup>2</sup>IDT recommended and/or chipset vendor layout guidelines must be followed to meet this specification

<sup>&</sup>lt;sup>3</sup>Applies to USB outputs only

<sup>&</sup>lt;sup>4</sup>Applies to SIO outputs only

<sup>&</sup>lt;sup>5</sup>SIO 24MHz outputs are 1/2 of USB48MHz frequency (twice the period). Includes cycle to cycle jitter.

<sup>&</sup>lt;sup>1</sup>Guaranteed by design and characterization, not 100% tested in production.

<sup>&</sup>lt;sup>2</sup> All Long Term Accuracy and Clock Period specifications are guaranteed assuming that REFOUT is at 14.31818MHz

<sup>&</sup>lt;sup>3</sup> Includes cycle to cycle jitter.

# Clock Periods-Differential Outputs with Spread Spectrum Enabled

| Measuren    | nent Window | 1 Clock                       | 1us                           | 0.1s                          | 0.1s     | 0.1s                 | 1us                   | 1 Clock  |       |       |

|-------------|-------------|-------------------------------|-------------------------------|-------------------------------|----------|----------------------|-----------------------|----------|-------|-------|

| Sy          | rmbol       | Lg-                           | -SSC                          | -ppm error                    | 0ppm     | + ppm error          | +SSC                  | Lg+      |       |       |

| Definition  |             | Absolute<br>Period            | Short-term<br>Average         | Long-Term<br>Average          | Period   | Long-Term<br>Average | Short-term<br>Average | Period   |       |       |

|             |             | Minimum<br>Absolute<br>Period | Minimum<br>Absolute<br>Period | Minimum<br>Absolute<br>Period | Nominal  | Maxim um             | Maximum               | Maximum  | Units | Notes |

| Signal Nama | HTT/SRC 100 | 9.87456                       | 9.99956                       | 10.02456                      | 10.02506 | 10.02556             | 10.05056              | 10.17556 | ns    | 1,2   |

| Signal Name | CPU 200     | 4.84978                       | 4.99978                       | 5.01228                       | 5.01253  | 5.01278              | 5.02528               | 5.17528  | ns    | 1,2   |

# Clock Periods-Differential Outputs with Spread Spectrum Disabled

| Measurem    | nent Window | 1 Clock                       | 1us                           | 0.1s                          | 0.1s     | 0.1s                 | 1us                   | 1 Clock  |       |       |

|-------------|-------------|-------------------------------|-------------------------------|-------------------------------|----------|----------------------|-----------------------|----------|-------|-------|

| Sy          | mbol        | Lg-                           | -ssc                          | -ppm error                    | 0ppm     | + ppm error          | +SSC                  | Lg+      |       |       |

| Definition  |             | Absolute<br>Period            | Short-term<br>Average         | Long-Term<br>Average          | Period   | Long-Term<br>Average | Short-term<br>Average | Period   |       |       |

|             |             | Minimum<br>Absolute<br>Period | Minimum<br>Absolute<br>Period | Minimum<br>Absolute<br>Period | Nominal  | Maxim um             | Maximum               | Maximum  | Units | Notes |

|             | SRC 100     | 9.87450                       |                               | 9.99950                       | 10.00000 | 10.00050             |                       | 10.12550 | ns    | 1,2   |

| Signal Name | SATA 100    | 9.87450                       |                               | 9.99950                       | 10.00000 | 10.00050             |                       | 10.12550 | ns    | 1,2   |

|             | CPU 200     | 4.84975                       |                               | 4.99975                       | 5.00000  | 5.00025              |                       | 5.15025  | ns    | 1,2   |

<sup>&</sup>lt;sup>1</sup>Guaranteed by design and characterization, not 100% tested in production.

<sup>&</sup>lt;sup>2</sup> All Long Term Accuracy and Clock Period specifications are guaranteed assuming that REFOUT is at 14.31818MHz

### **General SMBus Serial Interface Information**

#### **How to Write**

- · Controller (host) sends a start bit

- · Controller (host) sends the write address

- IDT clock will acknowledge

- Controller (host) sends the beginning byte location = N

- IDT clock will acknowledge

- Controller (host) sends the byte count = X

- · IDT clock will acknowledge

- Controller (host) starts sending Byte N through Byte N+X-1

- IDT clock will acknowledge each byte one at a time

- · Controller (host) sends a Stop bit

|           | Index Block Write Operation |        |                      |  |  |  |  |  |  |

|-----------|-----------------------------|--------|----------------------|--|--|--|--|--|--|

| Controll  | er (Host)                   |        | IDT (Slave/Receiver) |  |  |  |  |  |  |

| Т         | starT bit                   |        |                      |  |  |  |  |  |  |

| Slave A   | Address                     |        |                      |  |  |  |  |  |  |

| WR        | WRite                       |        |                      |  |  |  |  |  |  |

|           |                             |        | ACK                  |  |  |  |  |  |  |

| Beginning | g Byte = N                  |        |                      |  |  |  |  |  |  |

|           |                             |        | ACK                  |  |  |  |  |  |  |

| Data Byte | Count = X                   |        |                      |  |  |  |  |  |  |

|           |                             |        | ACK                  |  |  |  |  |  |  |

| Beginnin  | ig Byte N                   |        |                      |  |  |  |  |  |  |

|           |                             |        | ACK                  |  |  |  |  |  |  |

| 0         |                             | ×      |                      |  |  |  |  |  |  |

| 0         |                             | X Byte | 0                    |  |  |  |  |  |  |

| 0         |                             | Ф      | 0                    |  |  |  |  |  |  |

|           |                             |        | 0                    |  |  |  |  |  |  |

| Byte N    | Byte N + X - 1              |        |                      |  |  |  |  |  |  |

|           |                             |        | ACK                  |  |  |  |  |  |  |

| Р         | stoP bit                    |        |                      |  |  |  |  |  |  |

| Read Address      | Write Address     |

|-------------------|-------------------|

| D3 <sub>(H)</sub> | D2 <sub>(H)</sub> |

#### **How to Read**

- · Controller (host) will send a start bit

- Controller (host) sends the write address

- IDT clock will acknowledge

- Controller (host) sends the beginning byte location = N

- IDT clock will acknowledge

- · Controller (host) will send a separate start bit

- · Controller (host) sends the read address

- IDT clock will acknowledge

- IDT clock will send the data byte count = X

- IDT clock sends Byte N+X-1

- IDT clock sends Byte 0 through Byte X (if X<sub>(H)</sub> was written to Byte 8)

- · Controller (host) will need to acknowledge each byte

- Controller (host) will send a not acknowledge bit

- · Controller (host) will send a stop bit

|      | Index Block Read Operation |        |                      |  |  |  |  |  |

|------|----------------------------|--------|----------------------|--|--|--|--|--|

| Cor  | ntroller (Host)            |        | IDT (Slave/Receiver) |  |  |  |  |  |

| Т    | starT bit                  |        |                      |  |  |  |  |  |

| SI   | ave Address                |        |                      |  |  |  |  |  |

| WR   | WRite                      |        |                      |  |  |  |  |  |

|      |                            |        | ACK                  |  |  |  |  |  |

| Begi | nning Byte = N             |        |                      |  |  |  |  |  |

|      |                            |        | ACK                  |  |  |  |  |  |

| RT   | Repeat starT               |        |                      |  |  |  |  |  |

| SI   | ave Address                |        |                      |  |  |  |  |  |

| RD   | ReaD                       |        |                      |  |  |  |  |  |

|      |                            |        | ACK                  |  |  |  |  |  |

|      |                            |        |                      |  |  |  |  |  |

|      | •                          |        | Data Byte Count=X    |  |  |  |  |  |

|      | ACK                        |        |                      |  |  |  |  |  |

|      |                            |        | Beginning Byte N     |  |  |  |  |  |

|      | ACK                        |        |                      |  |  |  |  |  |

|      |                            | ē      | 0                    |  |  |  |  |  |

|      | 0                          | X Byte | 0                    |  |  |  |  |  |

|      | 0                          | ×      | 0                    |  |  |  |  |  |

|      | 0                          |        |                      |  |  |  |  |  |

|      |                            |        | Byte N + X - 1       |  |  |  |  |  |

| N    | Not acknowledge            |        |                      |  |  |  |  |  |

| Р    | stoP bit                   |        |                      |  |  |  |  |  |

| SMBus Table: | Output | Enable | Control | Register |

|--------------|--------|--------|---------|----------|

|--------------|--------|--------|---------|----------|

| Byte | 0     | Name       | Description   | Туре | 0       | 1       | Default |

|------|-------|------------|---------------|------|---------|---------|---------|

|      | Bit 7 | HTT1_OE    | Output Enable | RW   | Low/Low | Enabled | 1       |

|      | Bit 6 | HTT0_OE    | Output Enable | RW   | Low/Low | Enabled | 1       |

|      | Bit 5 | REF0_OE    | Output Enable | RW   | Low     | Enabled | 1       |

|      | Bit 4 | REF1_OE    | Output Enable | RW   | Low     | Enabled | 1       |

|      | Bit 3 | SIO_0_OE   | Output Enable | RW   | Hi-Z    | Enabled | 1       |

|      | Bit 2 | SIO_1_OE   | Output Enable | RW   | Low     | Enabled | 1       |

|      | Bit 1 | 48MHz_1_OE | Output Enable | RW   | Low     | Enabled | 1       |

|      | Bit 0 | 48MHz_0_OE | Output Enable | RW   | Low     | Enabled | 1       |

SMBus Table:Output Enable Control Register

| Byte | 1     | Name     | Control Function | Type | 0       | 1       | Default |

|------|-------|----------|------------------|------|---------|---------|---------|

| _    | Bit 7 | SRC13_OE | Output Enable    | RW   | Low/Low | Enabled | 1       |

|      | Bit 6 | SRC12_OE | Output Enable    | RW   | Low/Low | Enabled | 1       |

|      | Bit 5 | SRC11_OE | Output Enable    | RW   | Low/Low | Enabled | 1       |

|      | Bit 4 | SRC10_OE | Output Enable    | RW   | Low/Low | Enabled | 1       |

|      | Bit 3 | SRC9_OE  | Output Enable    | RW   | Low/Low | Enabled | 1       |

|      | Bit 2 | SRC8_OE  | Output Enable    | RW   | Low/Low | Enabled | 1       |

|      | Bit 1 | SRC7_OE  | Output Enable    | RW   | Low/Low | Enabled | 1       |

|      | Bit 0 | SRC6_OE  | Output Enable    | RW   | Low/Low | Enabled | 1       |

SMBus Table: Output Enable Control Register

| Byte | 2     | Name    | Control Function | Туре | 0       | 1       | Default |

|------|-------|---------|------------------|------|---------|---------|---------|

|      | Bit 7 | SRC5_OE | Output Enable    | RW   | Low/Low | Enabled | 1       |

|      | Bit 6 | SRC4_OE | Output Enable    | RW   | Low/Low | Enabled | 1       |

|      | Bit 5 | SRC3_OE | Output Enable    | RW   | Low/Low | Enabled | 1       |

|      | Bit 4 | SRC2_OE | Output Enable    | RW   | Low/Low | Enabled | 1       |

|      | Bit 3 | SRC1_OE | Output Enable    | RW   | Low/Low | Enabled | 1       |

|      | Bit 2 | SRC0_OE | Output Enable    | RW   | Low/Low | Enabled | 1       |

|      | Bit 1 | SATA_OE | Output Enable    | RW   | Low/Low | Enabled | 1       |

|      | Bit 0 | CPU0_OE | Output Enable    | RW   | Low/Low | Enabled | 1       |

SMBus Table: CPU/HTT Frequency and Output Enable Control Register

| Byte | 3     | Name            | Control Function         | Туре | 0                                                                                                                   | 1                                | Default |

|------|-------|-----------------|--------------------------|------|---------------------------------------------------------------------------------------------------------------------|----------------------------------|---------|

|      | Bit 7 | CPU3_OE         | Output enable            | RW   | Low/Low                                                                                                             | Enabled                          | 1       |

|      | Bit 6 | CPU2_OE         | Output enable            | RW   | Low/Low                                                                                                             | Enabled                          | 1       |

|      | Bit 5 | CPU1_OE         | Output enable            | RW   | Low/Low                                                                                                             | Enabled                          | 1       |

|      | Bit 4 | CPU SS Enable   | Spread Enable            | RW   | SS Off                                                                                                              | SS On                            | 0       |

|      | Bit 3 | CPU Spread Type | Down or Center Spread    | RW   | 0.5% Down Spread                                                                                                    | 0.5% Center Spread<br>(+/-0.25%) | 0       |

|      | Bit 2 | CPU_FS2         | CPU Frequency Select     | RW   | •                                                                                                                   | ency Select Table                | 1       |

|      | Bit 1 | CPU_FS1         | CPU Frequency Select     | RW   | Default value corresponds to 200MHz.  Note that HTT frequency tracks the CPU frequency and is equal to 1/2 for CPU. |                                  | 0       |

|      | Bit 0 | CPU_FS0         | CPU Frequency Select LSB | RW   |                                                                                                                     |                                  | 0       |

SMBus Table: SRC Frequency Control Register

| Byte | 4     | Name            | Control Function         | Type    | 0                                                             | 1                  | Default |

|------|-------|-----------------|--------------------------|---------|---------------------------------------------------------------|--------------------|---------|

|      | Bit 7 |                 | R                        | eserved |                                                               |                    | 0       |

|      | Bit 6 |                 | R                        | eserved |                                                               |                    | 0       |

|      | Bit 5 |                 | R                        | eserved |                                                               |                    | 0       |

|      | Bit 4 | SRC SS Enable   | Spread Enable            | RW      | SS Off                                                        | SS On              | 0       |

|      | Bit 3 | SRC Spread Type | Down or Center Spread    | RW      | 0.5% Down Spread                                              | 0.5% Center Spread | 0       |

|      | Bit 2 | SRC_FS2         | SRC Frequency Select     | RW      | Soo SDC Frogue                                                | anov Sologt Table  | 1       |

|      | Bit 1 | SRC_FS1         | SRC Frequency Select     | RW      | See SRC Frequency Select Table Default Corresponds to 100 MHz |                    | 0       |

|      | Bit 0 | SRC_FS0         | SRC Frequency Select LSB | RW      | Default Corresp                                               | 0                  |         |

SMBus Table: N-Step Select and SIO Readback Register

| Byte | 5     | Name       | Control Function                                    | Туре    | 0                           | 1                    | Default |

|------|-------|------------|-----------------------------------------------------|---------|-----------------------------|----------------------|---------|

|      | Bit 7 | SIO_SEL    | Selects 24MHz or 48MHz                              | R       | 24MHz                       | 48MHz                | Latch   |

|      | Bit 6 | CPU M/N En | CPU PLL M/N Prog. Enable                            | RW      | M/N Prog. Disabled          | M/N Prog. Enabled    | 0       |

|      | Bit 5 | SRC M/N En | SRC M/N Prog.Enable                                 | RW      | M/N Prog. Disabled          | M/N Prog. Enabled    | 0       |

|      | Bit 4 | Test_Sel   | Selects Test Mode                                   | RW      | Normal mode                 | All ouputs are REF/N | 0       |

|      | Bit 3 | Bit 3      |                                                     | eserved |                             |                      | 0       |

|      | Bit 2 | IO_VOUT2   | IO Output Voltage Select<br>(Most Significant Bit)  | RW      | See Table 2: V IO Selection |                      | 1       |

|      | Bit 1 | IO_VOUT1   |                                                     | RW      |                             | is 0.8V)             | 0       |

|      | Bit 0 | IO_VOUT0   | IO Output Voltage Select<br>(Least Significant Bit) | RW      | (Delauli                    | . is 0.0v j          | 1       |

SMBus Table: Byte Count Register

| Byte | 6     | Name | Control Function       | Туре     | 0                        | 1                           | Default |  |

|------|-------|------|------------------------|----------|--------------------------|-----------------------------|---------|--|

|      | Bit 7 |      | F                      | Reserve  | ı                        |                             | 0       |  |

|      | Bit 6 |      | F                      | Reservec | i                        |                             | 0       |  |

|      | Bit 5 | BC5  | Byte Count bit 5 (MSB) | RW       |                          |                             |         |  |

|      | Bit 4 | BC4  | Byte Count bit 4       | RW       |                          |                             | 0       |  |

|      | Bit 3 | BC3  | Byte Count bit 3       | RW       | Determines the number of | of bytes that are read back | 1       |  |