Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

## **DDR Phase Lock Loop Clock Driver**

#### **Recommended Application:**

**DDR Clock Driver**

- Low skew, low jitter PLL clock driver

- External feedback pins for input to output synchronization

- Spread Spectrum tolerant inputs

- With bypass mode mux

- Operating frequency 60 to 170 MHz

- Operating Temperature –45°C to +85°C

- CYCLE CYCLE jitter:<75ps

- OUTPUT OUTPUT skew: <60ps

- Output Rise and Fall Time: 650ps 950ps

## Pin Configuration

| GND     | 1  |          |    | DDRC4   |

|---------|----|----------|----|---------|

| DDRC0   | 2  |          | 27 | DDRT4   |

| DDRT0   | 3  |          | 26 | VDD2.5  |

| VDD2.5  | 4  |          | 25 | GND     |

| CLK_INT | 5  | 2        | 24 | FB_OUTO |

| CLK_INC | 6  | 85.      | 23 | FB_OUTT |

| AVDD2.5 | 7  |          | 22 | VDD2.5  |

| AGND    | 8  | 93V      | 21 | FB_INT  |

| GND     | 9  | S        | 20 | FB_INC  |

| DDRC1   | 10 | <u>5</u> | 19 | GND     |

| DDRT1   | 11 |          | 18 | VDD2.5  |

| VDD2.5  | 12 |          | 17 | DDRT3   |

| DDRT2   | 13 |          | 16 | DDRC3   |

| DDRC2   | 14 |          | 15 | GND     |

|         |    |          |    | l       |

28-Pin 4.4mm TSSOP

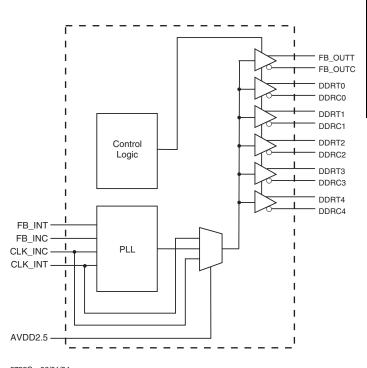

### **Block Diagram**

## **Functionality**

| INPUTS        |         |         |      | PLL State |         |         |              |  |

|---------------|---------|---------|------|-----------|---------|---------|--------------|--|

| AVDD          | CLK_INT | CLK_INC | DDRT | DDRC      | FB_OUTT | FB_OUTC | PLL State    |  |

| GND           | L       | Н       | Г    | Н         | L       | Н       | Bypassed/Off |  |

| GND           | Н       | L       | Н    | L         | Н       | L       | Bypassed/Off |  |

| 2.5V<br>(nom) | L       | Н       | L    | H         | L       | н       | On           |  |

| 2.5V<br>(nom) | Н       | ٦       | н    | L         | Н       | L       | On           |  |

| 2.5V<br>(nom) | <20 MHz | <20 MHz | Hi-Z | Hi-Z      | Hi-Z    | Hi-Z    | Off          |  |

0783C-06/01/04

## ICS93V855I

# **Pin Descriptions**

| PIN# | PIN NAME | PIN TYPE | DESCRIPTION                                                                                                                                                          |

|------|----------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | GND      | PWR      | Ground pin.                                                                                                                                                          |

| 2    | DDRC0    | OUT      | "Complimentary" Clock of differential pair output.                                                                                                                   |

| 3    | DDRT0    | OUT      | "True" Clock of differential pair output.                                                                                                                            |

| 4    | VDD2.5   | PWR      | Power supply, nominal 2.5V                                                                                                                                           |

| 5    | CLK_INT  | IN       | "True" reference clock input.                                                                                                                                        |

| 6    | CLK_INC  | IN       | "Complimentary" reference clock input.                                                                                                                               |

| 7    | AVDD2.5  | PWR      | 2.5V Analog Power pin for Core PLL                                                                                                                                   |

| 8    | AGND     | PWR      | Analog Ground pin for Core PLL                                                                                                                                       |

| 9    | GND      | PWR      | Ground pin.                                                                                                                                                          |

| 10   | DDRC1    | OUT      | "Complimentary" Clock of differential pair output.                                                                                                                   |

| 11   | DDRT1    | OUT      | "True" Clock of differential pair output.                                                                                                                            |

| 12   | VDD2.5   | PWR      | Power supply, nominal 2.5V                                                                                                                                           |

| 13   | DDRT2    | OUT      | "True" Clock of differential pair output.                                                                                                                            |

| 14   | DDRC2    | OUT      | "Complimentary" Clock of differential pair output.                                                                                                                   |

| 15   | GND      | PWR      | Ground pin.                                                                                                                                                          |

| 16   | DDRC3    | OUT      | "Complimentary" Clock of differential pair output.                                                                                                                   |

| 17   | DDRT3    | OUT      | "True" Clock of differential pair output.                                                                                                                            |

| 18   | VDD2.5   | PWR      | Power supply, nominal 2.5V                                                                                                                                           |

| 19   | GND      | PWR      | Ground pin.                                                                                                                                                          |

| 20   | FB_INC   | IN       | Complement single-ended feedback input, provides feedback signal to internal PLL for synchronization with CLK_INT to eliminate phase error.                          |

| 21   | FB_INT   | IN       | True single-ended feedback input, provides feedback signal to internal PLL for synchronization with CLK_INT to eliminate phase error.                                |

| 22   | VDD2.5   | PWR      | Power supply, nominal 2.5V                                                                                                                                           |

| 23   | FB_OUTT  | OUT      | True single-ended feedback output, dedicated external feedback. It switches at the same frequency as other DDR outputs, This output must be connect to FB_INT.       |

| 24   | FB_OUTC  | OUT      | Complement single-ended feedback output, dedicated external feedback. It switches at the same frequency as other DDR outputs, This output must be connect to FB_INC. |

| 25   | GND      | PWR      | Ground pin.                                                                                                                                                          |

| 26   | VDD2.5   | PWR      | Power supply, nominal 2.5V                                                                                                                                           |

| 27   | DDRT4    | OUT      | "True" Clock of differential pair output.                                                                                                                            |

| 28   | DDRC4    | OUT      | "Complimentary" Clock of differential pair output.                                                                                                                   |

### **Absolute Maximum Ratings**

Supply Voltage: (VDD & AVDD) .....--0.5V to 3.6V

(VDDI).....--0.5V to 4.6V

Input clamp current: IIK (VI < 0 or VI > VDD) +/- 50mA

Output clamp current: IOK (VO < 0 or VO > VDD) +/- 50mA

Continuous output current: IO (VO = 0 to VDD) +/- 50mA

Stresses above those listed under *Absolute Maximum Ratings* may cause permanent damage to the device. These ratings are stress specifications only and functional operation of the device at these or any other conditions above those listed in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect product reliability.

#### **Electrical Characteristics - Input/Supply/Common Output Parameters**

TA = -45°C to +85°C; Supply Voltage AVDD, VDD = 2.5 V +/- 0.2V (unless otherwise stated)

| PARAMETER                        | SYMBOL             | CONDITIONS                                         | MIN                   | TYP | MAX  | UNITS |

|----------------------------------|--------------------|----------------------------------------------------|-----------------------|-----|------|-------|

| Input High Current               | I <sub>IH</sub>    | $V_I = V_{DD}$ or GND                              | 5                     |     |      | μΑ    |

| Input Low Current                | I <sub>IL</sub>    | $V_I = V_{DD}$ or GND                              |                       |     | 5    | μA    |

| Operating Supply                 | I <sub>DD2.5</sub> | $C_L = 0pf, R_L = 120 ohms$                        |                       |     | 250  | mA    |

| Current                          | I <sub>DDPD</sub>  | $C_L = 0pf, R_L = 120 ohms$                        |                       |     | 100  | μΑ    |

| Output High Current              | I <sub>OH</sub>    | $V_{DD} = 2.3V, V_{OUT} = 1V$                      | -18                   |     |      | mA    |

| Output Low Current               | I <sub>OL</sub>    | $V_{DD} = 2.3V, V_{OUT} = 1.2V$                    | 26                    |     |      | mA    |

| High Impedance<br>Output Current | I <sub>OZ</sub>    | V <sub>DD</sub> =2.7V, Vout=V <sub>DD</sub> or GND |                       |     | ±10  | μΑ    |

| Input Clamp Voltage              | $V_{IK}$           | lin = -18mA                                        |                       |     | -1.2 | V     |

| High-level output voltage        | W                  | $V_{DD}$ = min to max,<br>$I_{OH}$ = -1 mA         | V <sub>DD</sub> - 0.1 |     |      | V     |

|                                  | V <sub>OH</sub>    | $V_{DD} = 2.3V$ ,<br>$I_{OH} = -12 \text{ mA}$     | 1.7                   |     |      | V     |

| Low-level output voltage         | V <sub>OL</sub>    | $V_{DD}$ = min to max<br>$I_{OL}$ =1 mA            |                       |     | 0.1  |       |

|                                  | VOL                | $V_{DD} = 2.3V$<br>$I_{OH} = 12 \text{ mA}$        |                       |     | 0.6  | V     |

| Input Capacitance <sup>1</sup>   | C <sub>IN</sub>    | VI = V <sub>DD</sub> or GND                        |                       | 3   |      | pF    |

| Output Capacitance <sup>1</sup>  | C <sub>OUT</sub>   | VI = V <sub>DD</sub> or GND                        |                       | 3   |      | pF    |

<sup>&</sup>lt;sup>1</sup>Guaranteed by design and characterization, not 100% tested in production.

### ICS93V855I

#### **DC Electrical Characteristics**

$T_A = -45$  °C to +85 °C; Supply Voltage AVDD, VDD = 2.5 V +/- 0.2V (unless otherwise stated)

| PARAMETER                                      | SYMBOL                | CONDITIONS                               | MIN                       | TYP                | MAX                       | UNITS |

|------------------------------------------------|-----------------------|------------------------------------------|---------------------------|--------------------|---------------------------|-------|

| Supply Voltage                                 | $V_{DDQ}$ , $A_{VDD}$ |                                          | 2.3                       | 2.5                | 2.7                       | V     |

| Low level input voltage                        | V <sub>IL</sub>       | CLK_INT, CLK_INC, FB_INC, FB_INT         |                           | 0.4                | V <sub>DD</sub> /2 - 0.18 | V     |

| High level input voltage                       | V <sub>IH</sub>       | CLK_INT, CLK_INC, FB_INC, FB_INT         | $V_{DD}/2 + 0.18$         | 2.1                |                           | V     |

| DC input signal voltage (note 2)               | V <sub>IN</sub>       |                                          | -0.3                      |                    | V <sub>DD</sub> + 0.3     | V     |

| Differential input signal                      | V <sub>ID</sub>       | DC - CLK_INT, CLK_INC,<br>FB_INC, FB_INT | 0.36                      |                    | V <sub>DD</sub> + 0.6     | V     |

| voltage (note 3)                               | VID                   | AC - CLK_INT, CLK_INC,<br>FB_INC, FB_INT | 0.7                       |                    | V <sub>DD</sub> + 0.6     | V     |

| Output differential cross-<br>voltage (note 4) | V <sub>ox</sub>       |                                          | V <sub>DD</sub> /2 - 0.15 |                    | $V_{DD}/2 + 0.15$         | V     |

| Input differential cross-<br>voltage (note 4)  | $V_{IX}$              |                                          | V <sub>DD</sub> /2 - 0.2  | V <sub>DD</sub> /2 | $V_{DD}/2 + 0.2$          | V     |

| Operating free-air temperature                 | $T_A$                 |                                          | -45                       |                    | 85                        | °C    |

#### Notes:

- 1 Unused inputs must be held high or low to prevent them from floating.

- 2 DC input signal voltage specifies the allowable DC excursion of differential input.

- 3 Differential inputs signal voltages specifies the differential voltage [VT-VCP] required for switching, where VTR is the true input level and VCP is the complementary input level.

- 4 Differential cross-point voltage is expected to track variations of VDD and is the voltage at which the differential signal must be crossing.

#### **Switching Characteristics**

$T_A = -45$  °C to +85 °C; Supply Voltage AVDD, VDD = 2.5 V +/- 0.2V (unless otherwise stated)

| PARAMETER                                   | SYMBOL                          | CONDITION            | MIN  | TYP | MAX | UNITS |

|---------------------------------------------|---------------------------------|----------------------|------|-----|-----|-------|

| Max clock frequency <sup>3</sup>            | freq <sub>op</sub>              |                      | 33   |     | 233 | MHz   |

| Application Frequency<br>Range <sup>3</sup> | freq <sub>App</sub>             |                      | 60   |     | 170 | MHz   |

| Input clock duty cycle                      | $d_{tin}$                       |                      | 40   |     | 60  | %     |

| Output clock slew rate                      | t <sub>sl(o)</sub>              |                      | 1    |     | 2   | v/ns  |

| CLK stabilization                           | T <sub>STAB</sub>               |                      |      |     | 100 | μs    |

| Low-to high level propagation delay time    | t <sub>PLH</sub>                | CLK_IN to any output |      | 5.5 |     | ns    |

| High-to low level propagation delay time    | t <sub>PHL</sub> 1              | CLK_IN to any output |      | 5.5 |     | ns    |

| Output enable time                          | t <sub>en</sub>                 | PD# to any output    |      | 5   |     | ns    |

| Output disable time                         | $t_{dis}$                       | PD# to any output    |      | 5   |     | ns    |

| Period jitter                               | t <sub>jit (per)</sub>          |                      | -75  |     | 75  | ps    |

| Half-period jitter                          | t <sub>jit(hper)</sub>          |                      | -100 |     | 100 | ps    |

| Input clock slew rate                       | t <sub>sl(I)</sub>              | Over the application | 1    |     | 2   | v/ns  |

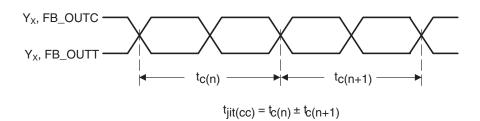

| Cycle to Cycle Jitter                       | $t_{\rm cyc}$ - $t_{\rm cyc}$   | frequency range      | -75  |     | 75  | ps    |

| Phase error <sup>4</sup>                    | t <sub>(phase error)</sub>      |                      | -50  |     | 50  | ps    |

| Output to Output Skew                       | $t_{skew}$                      |                      |      | 40  | 60  | ps    |

| Rise Time, Fall Time                        | t <sub>r</sub> , t <sub>f</sub> | Load = 120\psi/16pF  | 650  | 800 | 950 | ps    |

#### Notes:

- 1. Refers to transition on noninverting output in PLL bypass mode.

- 2. While the pulse skew is almost constant over frequency, the duty cycle error increases at higher frequencies. This is due to the formula: duty cycle=twH/tc, were the cycle (tc) decreases as the frequency goes up.

- 3. Switching characteristics are guaranteed for application frequency range. The PLL Locks over the Max Clock Frequency range, but the device doe not necessarily meet other timing parameters.

- 4. Does not include jitter.

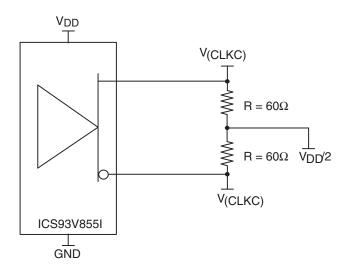

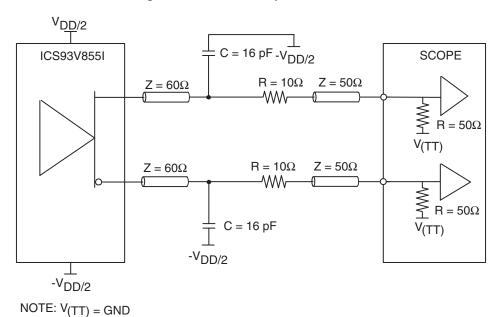

#### **Parameter Measurement Information**

Figure 1. IBIS Model Output Load

Figure 2. Output Load Test Circuit

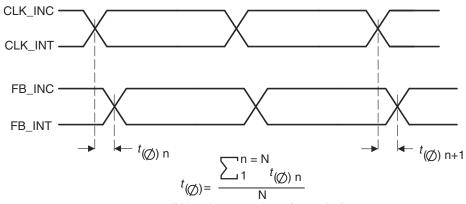

Figure 3. Cycle-to-Cycle Jitter

0783C-06/01/04

#### Parameter Measurement Information

(N is a large number of samples)

Figure 4. Static Phase Offset

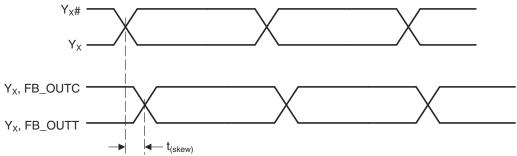

Figure 5. Output Skew

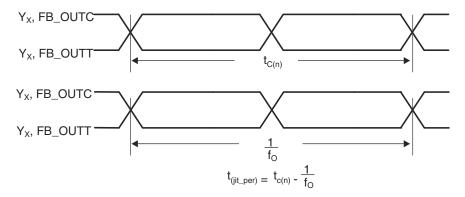

Figure 6. Period Jitter

#### Parameter Measurement Information

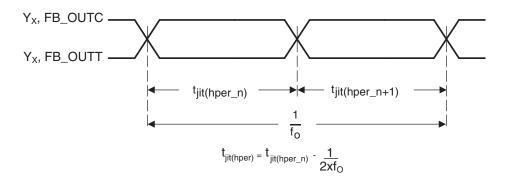

Figure 7. Half-Period Jitter

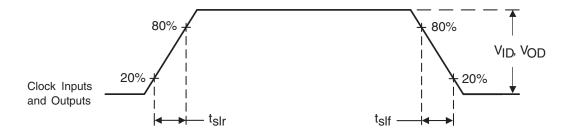

Figure 8. Input and Output Slew Rates

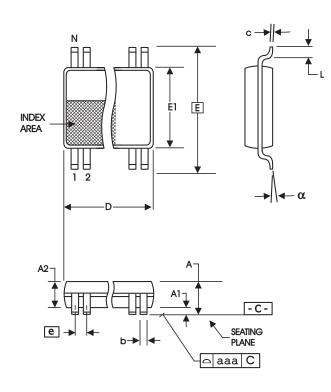

|        | In Milli       | meters    | In Inches         |          |  |

|--------|----------------|-----------|-------------------|----------|--|

| SYMBOL | COMMON D       | IMENSIONS | COMMON DIMENSIONS |          |  |

|        | MIN            | MAX       | MIN               | MAX      |  |

| Α      |                | 1.20      | -                 | .047     |  |

| A1     | 0.05           | 0.15      | .002              | .006     |  |

| A2     | 0.80           | 1.05      | .032              | .041     |  |

| b      | 0.19           | 0.30      | .007              | .012     |  |

| С      | 0.09           | 0.20      | .0035             | .008     |  |

| D      | SEE VARIATIONS |           | SEE VARIATIONS    |          |  |

| E      | 6.40 E         | BASIC     | 0.252 BASIC       |          |  |

| E1     | 4.30           | 4.50      | .169              | .177     |  |

| е      | 0.65 E         | BASIC     | 0.0256 BASIC      |          |  |

| L      | 0.45           | 0.75      | .018              | .030     |  |

| N      | SEE VARIATIONS |           | SEE VAF           | RIATIONS |  |

| а      | 0°             | 8°        | 0°                | 8°       |  |

| aaa    |                | 0.10      |                   | .004     |  |

#### **VARIATIONS**

| ı | N  | Dr   | nm.  | D (inch) |      |  |

|---|----|------|------|----------|------|--|

|   |    | MIN  | MAX  | MIN      | MAX  |  |

|   | 28 | 9.60 | 9.80 | .378     | .386 |  |

Reference Doc.: JEDEC Publication 95, MO-153

4.40 mm. Body, 0.65 mm. pitch TSSOP (173 mil) (0.0256 lnch)

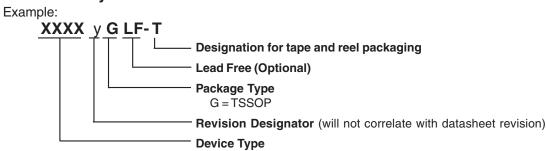

## **Ordering Information**

### 93V855yGILF-T

0783C-06/01/04