Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# PROGRAMMABLE TIMING CONTROL HUB FOR INTEL BASED SYSTEMS

ICS9LRS3187B

### **Recommended Application:**

CK505 version 1.1 clock, with fully integrated voltage regulators and series resistors

## **Output Features:**

- 2 CPU differential low power push-pull pairs

- 1 SRC differential low power push-pull pair

- 1 SATA differential low power push-pull pair

- 1 DOT differential low power push-pull pair

- 1 REF, able to drive 3 loads, 14.318MHz

- 1 27MHz\_SS/non\_SS single-ended output pair

#### Features/Benefits:

- Supports spread spectrum modulation, 0 to -0.5% down spread for CPU and SRC clocks

- Uses external 14.318MHz crystal, external crystal load caps are required for frequency tuning

- Available in commercial (0 to +70°C) and industrial (-40 to +85°C) temperature ranges

- Meets PCIe Gen2 specifications

## **Key Specifications:**

- CPU outputs cycle-cycle jitter <85ps</li>

- SRC outputs cycle-cycle jitter <125ps</li>

- +/- 100ppm frequency accuracy on all clocks

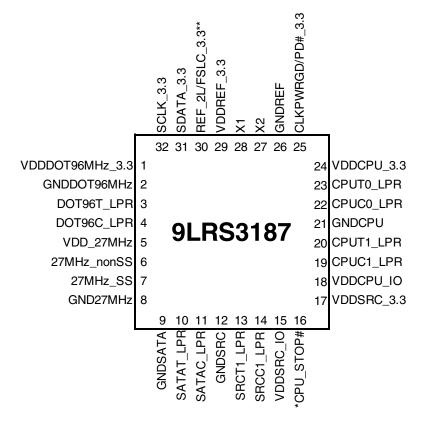

# **Pin Configuration**

<sup>\*\*</sup> Internal Pull-Down Resistor

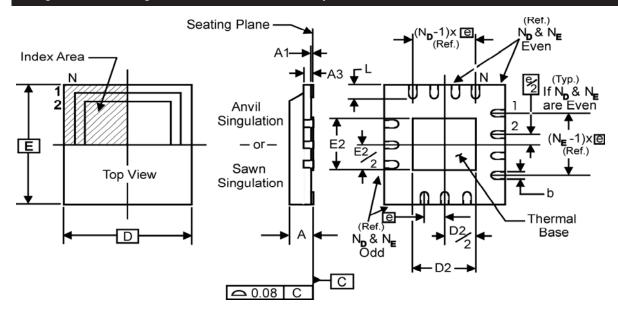

32-pin MLF

<sup>\*</sup> Internal Pull-Up Resistor

# **Pin Description**

|    | Description      | T     | Dia Description                                                                                                                                                                |

|----|------------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    | Pin Name         |       | Pin Description                                                                                                                                                                |

| 1  | VDDDOT96MHz_3.3  | PWR   | Power pin for the 96MHz output 3.3V.                                                                                                                                           |

| 2  | GNDDOT96MHz      | PWR   | Ground pin for the 96MHz output                                                                                                                                                |

| 3  | DOT96T_LPR       | OUT   | True DOT96 output with integrated 33ohm series resistor. No 50ohm resistor to GND needed.                                                                                      |

|    | DOT000   DD      | O. 17 | Complement DOT96 output with integrated 33ohm series                                                                                                                           |

| 4  | DOT96C_LPR       | OUT   | resistor. No 50ohm resistor to GND needed.                                                                                                                                     |

| 5  | VDD_27MHz        | PWR   | Power pin for the 27MHz output 3.3V.                                                                                                                                           |

| 6  | 27MHz_nonSS      | OUT   | 3.3V Single-ended 27MHz non-spread clock.                                                                                                                                      |

| 7  | 27MHz_SS         | OUT   | 3.3V Single-ended 27MHz spread clock.                                                                                                                                          |

| 8  | GND27MHz         | OUT   | Ground pin for the 27MHz outputs.                                                                                                                                              |

| 9  | GNDSATA          | PWR   | Ground pin for the SATA outputs.                                                                                                                                               |

| 10 | SATAT_LPR        | OUT   | True clock of differential 0.8V push-pull SATA/SRC output with integrated 33ohm series resistor. No 50ohm resistor to GND needed.                                              |

| 11 | SATAC_LPR        | OUT   | Complementary clock of differential 0.8V push-pull SATA/SRC output with integrated 33ohm series resistor. No 50ohm resistor to GND needed.                                     |

| 12 | GNDSRC           | PWR   | Ground pin for the SRC outputs                                                                                                                                                 |

|    |                  |       | True clock of differential 0.8V push-pull SRC output with                                                                                                                      |

| 13 | SRCT1_LPR        | OUT   | integrated 33ohm series resistor. No 50ohm resistor to GND needed.                                                                                                             |

| 14 | SRCC1_LPR        | OUT   | Complementary clock of differential 0.8V push-pull SRC output with integrated 33ohm series resistor. No 50ohm resistor to GND needed.                                          |

| 15 | VDDSRC_IO        | PWR   | 1.05V to 3.3V from external power supply                                                                                                                                       |

| 16 | *CPU_STOP#       | IN    | Stops all CPU clocks, except those set to be free running clocks                                                                                                               |

| 17 | VDDSRC_3.3       | PWR   | Supply for SRC clocks, 3.3V nominal                                                                                                                                            |

| 18 | VDDCPU_IO        | PWR   | 1.05V to 3.3V from external power supply                                                                                                                                       |

| 19 | CPUC1_LPR        | OUT   | Complementary clock of differential pair 0.8V push-pull CPU outputs with integrated 33ohm series resistor. No 50 ohm resistor to GND needed.                                   |

| 20 | CPUT1_LPR        | OUT   | True clock of differential pair 0.8V push-pull CPU outputs with integrated 33ohm series resistor. No 50 ohm resistor to GND needed.                                            |

| 21 | GNDCPU           | PWR   | Ground pin for the CPU outputs.                                                                                                                                                |

| 22 | CPUC0_LPR        | OUT   | Complementary clock of differential pair 0.8V push-pull CPU outputs with integrated 33ohm series resistor. No 50 ohm resistor to GND needed.                                   |

| 23 | CPUT0_LPR        | OUT   | True clock of differential pair 0.8V push-pull CPU outputs with integrated 33ohm series resistor. No 50 ohm resistor to GND needed.                                            |

| 24 | VDDCPU_3.3       | PWR   | Supply for CPU clocks, 3.3V nominal                                                                                                                                            |

| 25 | CLKPWRGD/PD#_3.3 | IN    | Notifies CK505 to sample latched inputs, or PWRDWN# mode                                                                                                                       |

| 26 | GNDREF           | PWR   | Ground pin for the REF outputs.                                                                                                                                                |

| 27 | X2               | OUT   | Crystal output, Nominally 14.318MHz                                                                                                                                            |

| 28 | X1               | IN    | Crystal input, Nominally 14.318MHz                                                                                                                                             |

| 29 | VDDREF_3.3       | PWR   | Power pin for the XTAL and REF clocks, nominal 3.3V                                                                                                                            |

| 30 | REF_2/FSLC_3.3** | I/O   | 14.318 MHz reference clock, which can drive 2 loads / 3.3V tolerant input for CPU frequency selection. Refer to input electrical characteristics for Vil_FS and Vih_FS values. |

| 31 | SDATA_3.3        | I/O   | Data pin for SMBus circuitry, 3.3V tolerant                                                                                                                                    |

| 32 | SCLK_3.3         | IN    | Clock pin of SMBus circuitry, 3.3V tolerant.                                                                                                                                   |

|    |                  |       |                                                                                                                                                                                |

IDT® Programmable Timing Control Hub for Intel Based Systems

# **General Description**

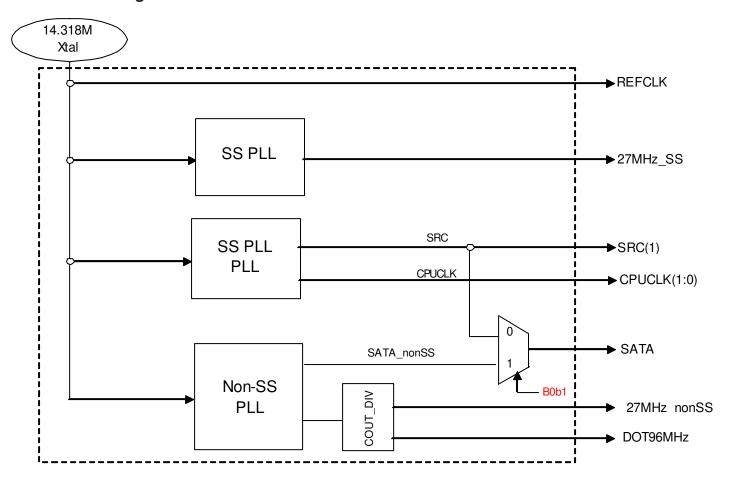

The ICS9LRS3187B is a CK505 clock synthesizer. The ICS9LRS3187B provides a single-chip solution for Intel based systems. The ICS9LRS3187B is driven with a 14.318MHz crystal.

# **Functional Block Diagram**

**Table: Power Distribution**

| Ground | VDD_IO | <b>VDD 3.3V</b> | Output |

|--------|--------|-----------------|--------|

| 2      |        | 1               | DOT96  |

| 8      |        | 5               | 27M    |

| 9      | 15     | 17              | SATA   |

| 12     | 15     | 17              | SRC    |

| 21     | 18     | 24              | CPU    |

| 26     |        | 29              | REF    |

**Table 1: CPU Frequency Select Table**

|             |        | <u> </u> |        |       |

|-------------|--------|----------|--------|-------|

| FS∟C        | CPU    | SRC      | REF    | DOT   |

| B0b7        | MHz    | MHz      | MHz    | MHz   |

| 0 (Default) | 133.33 | 100.00   | 14 210 | 96.00 |

| 1           | 100.00 | 100.00   | 14.318 | 96.00 |

1. FS<sub>L</sub>C is a low-threshold input.Please see V<sub>IL\_FS</sub> and V<sub>IH\_FS</sub> specifications in the Input/Supply/Common Output Parameters Table for correct values.

Also refer to the Test Clarification Table.

Table 2: pin 6, 7 Configuration

| B1b3 | B1b2   | B1b1 | Pin 6       | Pin 7    | Spread | Comment |

|------|--------|------|-------------|----------|--------|---------|

| B103 | D I DZ | D    | MHz         | MHz      | %      | Comment |

| 0    | 0      | 0    | 27MHz_nonSS | 27MHz_SS | -1.75% |         |

| 0    | 0      | 1    | 27MHz_nonSS | 27MHz_SS | +-0.5% |         |

| 0    | 1      | 0    | 27MHz_nonSS | 27MHz_SS | -0.5%  | Default |

| 0    | 1      | 1    | 27MHz_nonSS | 27MHz_SS | -1%    |         |

| 1    | 0      | 0    | 27MHz_nonSS | 27MHz_SS | -1.5%  |         |

| 1    | 0      | 1    | 27MHz_nonSS | 27MHz_SS | -2%    |         |

| 1    | 1      | 0    | 27MHz_nonSS | 27MHz_SS | -0.75% |         |

| 1    | 1      | 1    | 27MHz_nonSS | 27MHz_SS | -1.25% |         |

Table 3: IO\_Vout select table

| B9b2 | B9b1 | B9b0 | IO_Vout |

|------|------|------|---------|

| 0    | 0    | 0    | 0.3V    |

| 0    | 0    | 1    | 0.4V    |

| 0    | 1    | 0    | 0.5V    |

| 0    | 1    | 1    | 0.6V    |

| 1    | 0    | 0    | 0.7V    |

| 1    | 0 1  | 1    | 0.8V    |

| 1    | 1    | 0    | 0.9V    |

| 1    | 1    | 1    | 1.0V    |

## **CPU Power Management Table**

| PD# | CPU_STOP# | SMBus<br>Reg. OE | CPU1    | CPU1#   | CPU1# CPU0 CP |         |

|-----|-----------|------------------|---------|---------|---------------|---------|

| 1   | 1         | Enable           | Running | Running | Running       | Running |

| 0   | X         | Enable           | Low/20K | Low     | Low/20K       | Low     |

| 1   | 0         | Enable           | High    | Low     | High          | Low     |

| 1   | X         | Disable          | Low/20K | Low     | Low/20K       | Low     |

|     | M1        |                  | Running | Running | Low/20K       | Low     |

**SRC and DOT96MHz Power Management Table**

| PD# | CPU_STOP# | SMBus<br>Reg. OE | SRC     | SRC#    | DOT     | DOT#    |

|-----|-----------|------------------|---------|---------|---------|---------|

| 0   | X         | Enable           | Low/20K | Low     | Low/20K | Low     |

| 1   | X         | Enable           | Running | Running | Running | Running |

| 1   | X         | Disable          | Low/20K | Low     | Low/20K | Low     |

| M1  |           |                  | Low/20K | Low     | Low/20K | Low     |

**Singled-ended Power Management Table**

| PD# | CPU_STOP# | SMBus<br>Reg. OE | 27M     | REF     |

|-----|-----------|------------------|---------|---------|

| 1   | X         | Enable           | Running | Running |

| 0   | X         | Enable           | Low     | Hi-Z    |

| 1   | X         | Disable          | Low     | Low     |

|     | M1        | •                | Low     | Hi-Z    |

# General SMBus serial interface information for the ICS9LRS3187B

#### **How to Write:**

- · Controller (host) sends a start bit.

- Controller (host) sends the write address D2 (H)

- IDT clock will acknowledge

- Controller (host) sends the beginning byte location = N

- IDT clock will acknowledge

- Controller (host) sends the data byte count = X

- IDT clock will acknowledge

- Controller (host) starts sending Byte N through Byte N + X -1

- IDT clock will acknowledge each byte one at a time

- · Controller (host) sends a Stop bit

## **How to Read:**

- · Controller (host) will send start bit.

- Controller (host) sends the write address D2 (H)

- IDT clock will acknowledge

- Controller (host) sends the begining byte location = N

- IDT clock will acknowledge

- Controller (host) will send a separate start bit.

- Controller (host) sends the read address D3 (H)

- IDT clock will acknowledge

- IDT clock will send the data byte count = X

- IDT clock sends Byte N + X -1

- IDT clock sends Byte 0 through byte X (if X<sub>(H)</sub> was written to byte 8).

- · Controller (host) will need to acknowledge each byte

- · Controller (host) will send a not acknowledge bit

- · Controller (host) will send a stop bit

| Ind   | ex Block W                  | /rit                 | e Operation |

|-------|-----------------------------|----------------------|-------------|

| Cor   | ntroller (Host)             | IDT (Slave/Receiver) |             |

| Т     | starT bit                   |                      |             |

| Slav  | e Address D2 <sub>(H)</sub> |                      |             |

| WR    | WRite                       |                      |             |

|       |                             |                      | ACK         |

| Begi  | nning Byte = N              |                      |             |

|       |                             |                      | ACK         |

| Data  | Byte Count = X              |                      |             |

|       |                             |                      | ACK         |

| Begir | nning Byte N                |                      |             |

|       |                             |                      | ACK         |

|       | $\Diamond$                  | ţe                   |             |

|       | <b>\rightarrow</b>          | X Byte               | <b>\Q</b>   |

|       | $\Diamond$                  | ×                    | <b>♦</b>    |

|       |                             |                      | <b>♦</b>    |

| Byt   | e N + X - 1                 |                      |             |

|       |                             |                      | ACK         |

| Р     | stoP bit                    |                      |             |

| Ind       | ex Block Rea              | ad   | Operation          |

|-----------|---------------------------|------|--------------------|

| Con       | troller (Host)            | ID   | T (Slave/Receiver) |

| Т         | starT bit                 |      |                    |

| Slave     | Address D2 <sub>(H)</sub> |      |                    |

| WR        | WRite                     |      |                    |

|           |                           |      | ACK                |

| Begir     | nning Byte = N            |      |                    |

|           |                           |      | ACK                |

| RT        | Repeat starT              |      |                    |

| Slave     | Address D3 <sub>(H)</sub> |      |                    |

| RD        | ReaD                      |      |                    |

|           |                           |      | ACK                |

|           |                           |      |                    |

|           |                           | D    | ata Byte Count = X |

|           | ACK                       |      |                    |

|           |                           |      | Beginning Byte N   |

|           | ACK                       |      |                    |

|           |                           | Byte | $\Diamond$         |

|           | <b>♦</b>                  | B    | $\Diamond$         |

|           | <b>♦</b>                  | ×    | <b>\Q</b>          |

| <b>\Q</b> |                           |      |                    |

|           |                           |      | Byte N + X - 1     |

| N         | Not acknowledge           |      |                    |

| Р         | stoP bit                  |      |                    |

Byte 0 FS Readback and PLL Selection Register

| Bit | Pin | Name       | Description                                                                                                                                                                                                  | Туре               | 0                                      | 1                                     | Default |

|-----|-----|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|----------------------------------------|---------------------------------------|---------|

| 7   | -   | FSLC       | CPU Freq. Sel. Bit                                                                                                                                                                                           | R                  |                                        |                                       | Latch   |

| 6   | -   | Reserved   | Reserved                                                                                                                                                                                                     | RW                 | =                                      | -                                     | 0       |

| 5   | -   | Reserved   | Reserved                                                                                                                                                                                                     | RW                 | =                                      | =                                     | 1       |

| 4   | -   | iAMT_EN    | Set via SMBus                                                                                                                                                                                                | RW<br>(Sticky "1") | Legacy Mode                            | iAMT Enabled                          | 0       |

| 3   |     | Reserved   | Reserved                                                                                                                                                                                                     | RW                 |                                        |                                       | 0       |

| 2   | -   | Reserved   | Reserved                                                                                                                                                                                                     | RW                 |                                        |                                       | 0       |

| 1   | -   | SATA_SEL   | Select source for SATA clock                                                                                                                                                                                 | RW                 | SATA (SRC2<br>100MHz_SS) =<br>SRC_Main | SATA (100MHz<br>non_SS) = SATA<br>PLL | 0       |

| 0   | -   | PD_Restore | 1 = on Power Down de-assert return to last known state 0 = clear all SMBus configurations as if cold power on and go to latches open state This bit is ignored and treated at '1' if device is in iAMT mode. | RW                 | Configuration Not<br>Saved             | Configuration<br>Saved                | 1       |

Byte 1 DOT96 Select and PLL3 Quick Config Register,

| Bit | Pin | Name            | Description                    | Туре | 0 1              |                                    | Default |

|-----|-----|-----------------|--------------------------------|------|------------------|------------------------------------|---------|

| 7   |     | Reserved        | Reserved                       | RW   | -                | -                                  | 1       |

| 6   |     | SRC_PLL_SSC_SEL | Select 0.5% down or center SSC | RW   | Down spread      | Center spread                      | 0       |

| 5   |     | Reserved        | Reserved                       | RW   | -                | -                                  | 1       |

| 4   |     | Reserved        | Reserved                       | RW   |                  |                                    | 0       |

| 3   |     | 27SS PLL CF2    | 27SS PLL Quick Config Bit 2    | RW   |                  |                                    | 0       |

| 2   |     | 27SS PLL _CF1   | 27SS PLL Quick Config Bit 1    | RW   | See Table 2: pin | See Table 2: pin 6/7 Configuration |         |

| 1   |     | 27SS PLL CF0    | 27SS PLL Quick Config Bit 0    | RW   |                  |                                    | 0       |

| 0   |     | Reserved        | Reserved                       | RW   | -                | -                                  | 1       |

**Byte 2 Output Enable Register**

| Bit | Pin | Name      | Description                                                  | Туре | 0               | 1              | Default |

|-----|-----|-----------|--------------------------------------------------------------|------|-----------------|----------------|---------|

| 7   |     | REF_3L_OE | Output enable for REF0, if disabled output is tri-<br>stated | RW   | Output Disabled | Output Enabled | 1       |

| 6   |     | Reserved  | Reserved                                                     | RW   | -               | -              | 1       |

| 5   |     | Reserved  | Reserved                                                     | RW   | -               | -              | 1       |

| 4   |     | Reserved  | Reserved                                                     | RW   | -               | -              | 1       |

| 3   |     | Reserved  | Reserved                                                     | RW   | =               | =              | 1       |

| 2   |     | Reserved  | Reserved                                                     | RW   | -               | -              | 1       |

| 1   |     | Reserved  | Reserved                                                     | RW   | -               | -              | 1       |

| 0   |     | Reserved  | Reserved                                                     | RW   | -               | =              | 1       |

Byte 3 Output Enable Register

| Bit | Pin | Name     | Description | Type | 0 | 1 | Default |

|-----|-----|----------|-------------|------|---|---|---------|

| 7   |     | Reserved | Reserved    | RW   | - | - | 1       |

| 6   |     | Reserved | Reserved    | RW   | = | - | 1       |

| 5   |     | Reserved | Reserved    | RW   | = | - | 1       |

| 4   |     | Reserved | Reserved    | RW   | = | - | 1       |

| 3   |     | Reserved | Reserved    | RW   | = | - | 1       |

| 2   |     | Reserved | Reserved    | RW   | = | - | 1       |

| 1   |     | Reserved | Reserved    | RW   |   |   | 1       |

| 0   |     | Reserved | Reserved    | RW   | - | - | 1       |

Byte 4 Output Enable and Spread Spectrum Disable Register

| Bit | Pin | Name       | Description                     | Type | 0               | 1              | Default |

|-----|-----|------------|---------------------------------|------|-----------------|----------------|---------|

| 7   |     | Reserved   | Reserved                        | RW   | -               | -              | 1       |

| 6   |     | SATA_OE    | Output enable for SATA          | RW   | Output Disabled | Output Enabled | 1       |

| 5   |     | SRC1_OE    | Output enable for SRC1          | RW   | Output Disabled | Output Enabled | 1       |

| 4   |     | DOT96_OE   | Output enable for DOT96         | RW   | Output Disabled | Output Enabled | 1       |

| 3   |     | CPU1_OE    | Output enable for CPU1          | RW   | Output Disabled | Output Enabled | 1       |

| 2   |     | CPU0_OE    | Output enable for CPU0          | RW   | Output Disabled | Output Enabled | 1       |

| 1   |     | 27SS_ON    | Enable 27SS's spread modulation | RW   | Spread Disabled | Spread Enabled | 1       |

| 0   |     | SRC_SSC_ON | Enable SRC's spread modulation  | RW   | Spread Disabled | Spread Enabled | 1       |

**Byte 5 Reserved Register**

| Bit | Pin | Name     | Description | Туре | 0 | 1 | Default |

|-----|-----|----------|-------------|------|---|---|---------|

| 7   |     | Reserved | Reserved    | RW   | - | - | 1       |

| 6   |     | Reserved | Reserved    | RW   | - | - | 1       |

| 5   |     | Reserved | Reserved    | RW   | - | - | 1       |

| 4   |     | Reserved | Reserved    | RW   | - | - | 1       |

| 3   |     | Reserved | Reserved    | RW   | - | = | 1       |

| 2   |     | Reserved | Reserved    | RW   | - | - | 1       |

| 1   |     | Reserved | Reserved    | RW   | - | - | 1       |

| 0   |     | Reserved | Reserved    | RW   | - | - | 1       |

**Byte 6 Slew Rate Control Register**

| <u> </u> |     | CICII HUIO COIIIIC | · · · · · · · · · · · · · · · · · · · |      |        |        |         |

|----------|-----|--------------------|---------------------------------------|------|--------|--------|---------|

| Bit      | Pin | Name               | Description                           | Туре | 0      | 1      | Default |

| 7        |     | Reserved           | Reserved                              | RW   | -      | -      | 0       |

| 6        |     | Reserved           | Reserved                              | RW   | -      | -      | 0       |

| 5        |     | REF Slew           | Slew Rate Control                     | RW   | 2 V/ns | 1 V/ns | 0       |

| 4        |     | Reserved           | Reserved                              | RW   | -      | -      | 0       |

| 3        |     | 27MHz Slew         | Slew Rate Control                     | RW   | 2 V/ns | 1 V/ns | 0       |

| 2        |     | Reserved           | Reserved                              | RW   | -      | -      | 0       |

| 1        |     | Reserved           | Reserved                              | RW   | -      | -      | 0       |

| 0        |     | Reserved           | Reserved                              | RW   | -      | -      | 0       |

Byte 7 Vendor ID/ Revision ID

| Bit | Pin | Name            | Description         | Туре | 0      | 1        | Default |  |

|-----|-----|-----------------|---------------------|------|--------|----------|---------|--|

| 7   |     | Rev Code Bit 3  |                     | R    |        |          |         |  |

| 6   |     | Rev Code Bit 2  | Revision ID         | R    |        |          |         |  |

| 5   |     | Rev Code Bit 1  | nevision id         | R    |        |          | Χ       |  |

| 4   |     | Rev Code Bit 0  |                     | R    | Vendor | X        |         |  |

| 3   |     | Vendor ID bit 3 |                     | R    | Vendoi | specific | 0       |  |

| 2   |     | Vendor ID bit 2 | Vendor ID R         |      |        | 0        |         |  |

| 1   |     | Vendor ID bit 1 | ICS is 0001, binary | R    |        |          | 0       |  |

| 0   |     | Vendor ID bit 0 |                     | R    |        |          | 1       |  |

Byte 8 Device ID and Output Enable Register

| Bit | Pin | Name           | Description                                    | Type | 0                   | 1       | Default |

|-----|-----|----------------|------------------------------------------------|------|---------------------|---------|---------|

| 7   |     | Device_ID3     | Table of Device identifier codes, used for     | R    |                     | 1       |         |

| 6   |     | Device_ID2     | differentiating between CK505 package options, | R    | Soo Dovio           | 0       |         |

| 5   |     | Device_ID1     | 1                                              | R    | See Device ID Table |         | 0       |

| 4   |     | Device_ID0     | etc.                                           | R    |                     | 0       |         |

| 3   |     | Reserved       | Reserved                                       | RW   | =                   | -       | 0       |

| 2   |     | Reserved       | Reserved                                       | RW   | =                   | -       | 0       |

| 1   |     | 27MHz_nonSS_OE | Output enable for 27MHz_nonSS                  | RW   | Disabled            | Enabled | 1       |

| 0   |     | 27MHz_SS_OE    | SS_OE Output enable for 27MHz_SS               |      | Disabled            | Enabled | 1       |

**Byte 9 Output Control Register**

| Bit | Pin | Name     | Description                                      | Туре | 0                                                | 1 | Default |

|-----|-----|----------|--------------------------------------------------|------|--------------------------------------------------|---|---------|

| 7   |     | Reserved | Reserved                                         | RW   | =                                                | - | 0       |

| 6   |     | Reserved | Reserved                                         | R    |                                                  |   | 0       |

| 5   |     | Reserved | Reserved                                         | RW   |                                                  |   | 1       |

| 4   |     | Reserved | Reserved                                         | RW   |                                                  |   | 0       |

| 3   |     | Reserved | Reserved                                         | RW   | -                                                | - | 0       |

| 2   |     | IO_VOUT2 | IO Output Voltage Select (Most Significant Bit)  | RW   | See Table 3: V_IO Selection<br>(Default is 0.8V) |   | 1       |

| 1   |     | IO_VOUT1 | IO Output Voltage Select                         | RW   |                                                  |   | 0       |

| 0   |     | IO_VOUT0 | IO Output Voltage Select (Least Significant Bit) | RW   |                                                  |   | 1       |

**Byte 10 Output Control Register**

| Bit | Pin | Name              | Description                             | Туре | 0            | 1         | Default |

|-----|-----|-------------------|-----------------------------------------|------|--------------|-----------|---------|

| 7   |     | Reserved          | Reserved                                | RW   | =            | -         | 0       |

| 6   |     | Reserved          | Reserved                                | RW   | =            | Ē         | 0       |

| 5   |     | Reserved          | Reserved                                | RW   | =            | -         | 0       |

| 4   |     | Reserved          | Reserved                                | RW   | =            | Ē         | 0       |

| 3   |     | Reserved          | Reserved                                | RW   | =            | Ē         | 0       |

| 2   |     | Reserved          | Reserved                                | RW   | =            | Ē         | 0       |

| 1   |     | CPU 1 Stop Enable | Enables control of CPU1 with CPU_STOP#  | RW   | Free Running | Stoppable | 1       |

| 0   |     | CPU 0 Stop Enable | Enables control of CPU 0 with CPU_STOP# | RW   | Free Running | Stoppable | 1       |

**Byte 11 Reserved Register**

| Bit | Pin | Name        | Description                        | Туре   | 0        | 1                       | Default |

|-----|-----|-------------|------------------------------------|--------|----------|-------------------------|---------|

| 7   |     | Reserved    | Reserved                           | RW     |          |                         | 0       |

| 6   |     | Reserved    | Reserved                           | RW     |          |                         | 0       |

| 5   |     | Reserved    | Reserved                           | ved RW |          |                         | 0       |

| 4   |     | Reserved    | Reserved                           | RW     |          |                         | 0       |

| 3   |     | Reserved    | Reserved                           | RW     | =        | =                       | 0       |

| 2   |     | CPU1_AMT_EN | M1 mode clk enable                 | RW     | Disable  | Enable                  | 1       |

| 1   |     | PCI-E_GEN2  | Determines if PCI-E Gen2 compliant | R      | non-Gen2 | PCI-E Gen2<br>Compliant | 1       |

| 0   |     | Reserved    | Reserved                           | RW     |          | 1                       |         |

**Byte 12 Byte Count Register**

| Bit | Pin | Name     | Description                    | Type | 0 | 1 | Default |

|-----|-----|----------|--------------------------------|------|---|---|---------|

| 7   |     | Reserved |                                | RW   |   |   | 0       |

| 6   |     | Reserved |                                | RW   |   |   | 0       |

| 5   |     | BC5      |                                | RW   |   |   | 0       |

| 4   |     | BC4      |                                | RW   |   |   | 0       |

| 3   |     | BC3      | Read Back byte count register, | RW   |   |   | 1       |

| 2   |     | BC2      | max bytes = 32                 | RW   |   |   | 1       |

| 1   |     | BC1      |                                | RW   |   |   | 0       |

| 0   |     | BC0      |                                | RW   |   |   | 1       |

Absolute Maximum Ratings - DC Parameters, Commercial Temperature Range

| PARAMETER              | SYMBOL    | CONDITIONS                          | MIN       | TYP | MAX | UNITS | Notes |

|------------------------|-----------|-------------------------------------|-----------|-----|-----|-------|-------|

| Maximum Supply Voltage | VDDxxx    | Supply Voltage                      |           |     | 4.6 | ٧     | 1     |

| Maximum Supply Voltage | VDDxxx_IO | Low-Voltage Differential I/O Supply |           |     | 3.8 | ٧     | 1     |

| Maximum Input Voltage  | $V_{IH}$  | 3.3V Inputs                         |           |     | 4.6 | ٧     | 1,2   |

| Minimum Input Voltage  | $V_{IL}$  | Any Input                           | GND - 0.5 |     |     | ٧     | 1     |

| Storage Temperature    | Ts        | -                                   | -65       |     | 150 | °C    | 1     |

| Input ESD protection   | ESD prot  | Human Body Model                    | 2000      |     |     | ٧     | 1,3   |

Notes: (unless otherwise noted, guaranteed by design and characterization, not 100% tested in production).

Electrical Characteristics - Input/Supply/Common Output DC Parameters, Commercial Temperature Range

|                                               | J                      | Catput 20 : aramotoro, Commordia: Fompo.                                      |                       |         |                |       |       |

|-----------------------------------------------|------------------------|-------------------------------------------------------------------------------|-----------------------|---------|----------------|-------|-------|

| PARAMETER                                     | SYMBOL                 | CONDITIONS                                                                    | MIN                   | TYP     | MAX            | UNITS | Notes |

| Ambient Operating Temp                        | Tambient               | -                                                                             | 0                     |         | 70             | °C    |       |

| Supply Voltage                                | VDDxxx                 | Supply Voltage                                                                | 3.135                 |         | 3.465          | ٧     |       |

| Supply Voltage                                | VDDxxx_IO              | Low-Voltage Differential I/O Supply                                           | 0.9975                |         | 3.465          | ٧     | 5     |

| Input High Voltage                            | V <sub>IHSE</sub>      | Single-ended 3.3V inputs                                                      | 2                     |         | $V_{DD} + 0.3$ | ٧     | 3     |

| Input Low Voltage                             | $V_{ILSE}$             | Single-ended 3.3V inputs                                                      | V <sub>SS</sub> - 0.3 |         | 0.8            | ٧     | 3     |

| Low Threshold Input- FSC = '1' Voltage        | V <sub>IH_FSC</sub>    | 3.3 V +/-5%                                                                   | 0.7                   |         | 3.3            | ٧     | 4     |

| Low Threshold Input-Low Voltage               | $V_{IL\_FSC}$          | 3.3 V +/-5%                                                                   | V <sub>SS</sub> - 0.3 |         | 0.35           | ٧     |       |

| Input Leakage Current                         | I <sub>IN</sub>        | $V_{IN} = V_{DD}$ , $V_{IN} = GND$                                            | -5                    |         | 5              | uA    | 2     |

| Input Leakage Current                         | I <sub>INRES</sub>     | Inputs with pull up or pull down resistors $V_{IN} = V_{DD}$ , $V_{IN} = GND$ | -200                  |         | 200            | uA    |       |

| Output High Voltage                           | V <sub>OHSE</sub>      | Single-ended outputs, I <sub>OH</sub> = -1mA                                  | 2.4                   |         |                | V     | 1     |

| Output Low Voltage                            | V <sub>OLSE</sub>      | Single-ended outputs, I <sub>OL</sub> = 1 mA                                  |                       |         | 0.4            | ٧     | 1     |

| Operating Supply Current                      | I <sub>DDOP3.3</sub>   | Full Active, C <sub>L</sub> = Full load; Idd 3.3V                             |                       | 85      | 110            | mA    |       |

| Operating Supply Current                      | I <sub>DDOPIO</sub>    | Full Active, C <sub>L</sub> = Full load; IDD IO                               |                       | 18      | 25             | mA    | 5     |

| iAMT Mode Current                             | I <sub>DDiAMT3.3</sub> | M1 mode, 3.3V Rail                                                            |                       | 48      | 60             | mA    |       |

| IAMT Mode Current                             | I <sub>DDIAMTIO</sub>  | M1 Mode, IO Rail                                                              |                       | 6       | 10             | mA    | 5     |

| Powerdown Current                             | I <sub>DDPD3.3</sub>   | Power down mode, 3.3V Rail                                                    |                       | 6       | 5              | mA    |       |

| Powerdown Current                             | I <sub>DDPDIO</sub>    | Power down mode, IO Rail                                                      |                       | 0       | 0.1            | mA    | 5     |

| Input Frequency                               | Fi                     | $V_{DD} = 3.3 \text{ V}$                                                      |                       | 14.3182 | 15             | MHz   |       |

| Pin Inductance                                | L <sub>pin</sub>       |                                                                               |                       |         | 7              | nΗ    |       |

|                                               | C <sub>IN</sub>        | Logic Inputs                                                                  | 1.5                   |         | 5              | pF    |       |

| Input Capacitance                             | C <sub>OUT</sub>       | Output pin capacitance                                                        |                       |         | 6              | pF    |       |

|                                               | C <sub>INX</sub>       | X1 & X2 pins                                                                  |                       |         | 6              | pF    |       |

| Clk Stabilization                             | T <sub>STAB</sub>      | From VDD Power-Up or de-assertion of PD to 1st clock                          |                       | 1.0     | 1.8            | ms    |       |

| Tfall_SE                                      | T <sub>FALL</sub>      | Fall/rise time of all 3.3V control inputs from 20-80%                         |                       |         | 10             | ns    | 1     |

| Trise_SE                                      | T <sub>RISE</sub>      | Fail/fise time of all 3.3V control inputs from 20-60%                         |                       |         | 10             | ns    | 1     |

| SMBus Voltage                                 | $V_{DD}$               |                                                                               | 2.7                   |         | 5.5            | V     |       |

| Low-level Output Voltage                      | V <sub>OLSMB</sub>     | @ I <sub>PULLUP</sub>                                                         |                       |         | 0.4            | V     |       |

| Current sinking at V <sub>OLSMB</sub> = 0.4 V | I <sub>PULLUP</sub>    | SMB Data Pin                                                                  | 4                     | 5       |                | mA    |       |

| SCLK/SDATA                                    | T <sub>BI2C</sub>      | (Max VIL - 0.15) to                                                           |                       |         | 1000           | ns    |       |

| Clock/Data Rise Time SCLK/SDATA               | · nizu                 | (Min VIH + 0.15)                                                              |                       |         |                |       |       |

| SCLK/SDATA Clock/Data Fall Time               | T <sub>FI2C</sub>      | (Min VIH + 0.15) to<br>(Max VIL - 0.15)                                       |                       |         | 300            | ns    |       |

| Maximum SMBus Operating Frequency             | F <sub>SMBUS</sub>     | (Max VIE 0.10)                                                                |                       |         | 100            | kHz   |       |

| Spread Spectrum Modulation Frequency          | f <sub>SSMOD</sub>     | Triangular Modulation                                                         | 30                    | 32.54   | 33             | kHz   |       |

|                                               |                        | haracterization, not 100% tested in production).                              |                       |         |                |       | 1     |

Notes: (unless otherwise noted, guaranteed by design and characterization, not 100% tested in production).

<sup>&</sup>lt;sup>1</sup> Operation under these conditions is neither implied, nor guaranteed.

<sup>&</sup>lt;sup>2</sup> Maximum VIH is not to exceed VDD

<sup>&</sup>lt;sup>3</sup> Human Body Model

<sup>&</sup>lt;sup>1</sup>Signal is required to be monotonic in this region.

<sup>&</sup>lt;sup>2</sup> Input leakage current does not include inputs with pull-up or pull-down resistors

$<sup>^{\</sup>rm 3}\,\rm 3.3V$  referenced inputs are: SCLK, SDATA, and CKPWRGD

<sup>&</sup>lt;sup>4</sup> Frequency Select pins which have tri-level input

<sup>&</sup>lt;sup>5</sup> If present, not all parts have this feature.

AC Electrical Characteristics - Low Power Differential Outputs, Commercial Temperature Range

| PARAMETER                  | SYMBOL               | CONDITIONS                                           | MIN  | TYP  | MAX  | UNITS | Notes |

|----------------------------|----------------------|------------------------------------------------------|------|------|------|-------|-------|

| Rising Edge Slew Rate      | tSLR                 | Averaging on                                         | 2.5  | 3.7  | 4    | V/ns  | 2, 3  |

| Falling Edge Slew Rate     | tFLR                 | Averaging on                                         | 2.5  | 3.7  | 4    | V/ns  | 2, 3  |

| Slew Rate Variation        | tSLVAR               | Averaging on                                         |      | 3.6  | 20   | %     | 1, 6  |

| Differential Voltage Swing | VSWING               | Averaging off                                        | 300  |      |      | mV    | 2     |

| Crossing Point Voltage     | VXABS                | Averaging off                                        | 300  | 446  | 550  | mV    | 1,4,5 |

| Crossing Point Variation   | VXABSVAR             | Averaging off                                        |      | 70   | 140  | mV    | 1,4,9 |

| Maximum Output Voltage     | VHIGH                | Averaging off                                        |      |      | 1150 | mV    | 1,7   |

| Minimum Output Voltage     | VLOW                 | Averaging off                                        | -300 |      |      | mV    | 1,8   |

| Duty Cycle                 | DCYC                 | Averaging on                                         | 45   | 49.8 | 55   | %     | 2     |

| CPU Skew                   | CPUSKEW              | Averaging on                                         |      | 35   | 100  | ps    |       |

| SRC Skew                   | t <sub>SKEWSRC</sub> | Averaging on, SRC to SATA skew when Byte0, bit 1 = 0 |      | 259  | 350  | ps    |       |

NOTES: (unless otherwise noted, guaranteed by design and characterization, not 100% tested in production). CL = 2pF, Rs = 0 ohms.

Clock Jitter Specs - Low Power Differential Outputs, Commercial Temperature Range

| PARAMETER                        | SYMBOL                  | CONDITIONS                                 | MIN | TYP | MAX | UNITS        | Notes |

|----------------------------------|-------------------------|--------------------------------------------|-----|-----|-----|--------------|-------|

| CPU Jitter - Cycle to Cycle      | CPUJC2C                 | Differential Measurement                   |     | 50  | 85  | ps           | 1     |

| SRC/SATA Jitter - Cycle to Cycle | SRCJC2C                 | Differential Measurement                   |     | 50  | 125 | ps           | 1,2   |

| DOT Jitter - Cycle to Cycle      | DOTJC2C                 | Differential Measurement                   |     | 50  | 250 | ps           | 1     |

|                                  | t <sub>jphasePLL</sub>  | PCIe Gen 1                                 |     | 35  | 86  | ps (p-<br>p) | 1,2,3 |

| SRC Phase Jitter                 | t <sub>jphaseLo</sub>   | PCIe Gen 2<br>10kHz < f < 1.5MHz           |     | 1.8 | 3   | ps<br>(RMS)  | 1,2,3 |

|                                  | t <sub>jphaseHigh</sub> | PCIe Gen 2<br>1.5MHz < f < Nyquist (50MHz) |     | 2.3 | 3.1 | ps<br>(RMS)  | 1,2,3 |

NOTES: (unless otherwise noted, guaranteed by design and characterization, not 100% tested in production). CL = 2pF, Rs = 0 ohms.

<sup>&</sup>lt;sup>1</sup>Measurement taken for single ended waveform on a component test board (not in system)

$<sup>^{\</sup>rm 2}\,{\rm Measurement}$  taken from differential waveform on a component test board. (not in system)

<sup>&</sup>lt;sup>3</sup> Slew rate emastured through V\_swing voltage range centered about differential zero

<sup>&</sup>lt;sup>4</sup> Vcross is defined at the voltage where Clock = Clock#, measured on a component test board (not in system)

<sup>&</sup>lt;sup>5</sup> Only applies to the differential rising edge (Clock rising, Clock# falling)

<sup>&</sup>lt;sup>6</sup> Matching applies to rising edge rate for Clock and falling edge rate for Clock#. It is measured using a +/-75mV window centered on the average cross point where Clock rising meets Clock# falling. The median cross point is used to calculate the voltage

<sup>&</sup>lt;sup>7</sup> The max voltage including overshoot.

<sup>&</sup>lt;sup>8</sup> The min voltage including undershoot.

<sup>&</sup>lt;sup>9</sup> The total variation of all Vcross measurements in any particular system. Note this is a subset of V\_cross min/mas (V\_Cross absolute) allowed. The intent is to limit Vcross induced modulation by setting C\_cross\_delta to be smaller than V\_Cross absolute

<sup>&</sup>lt;sup>1</sup>JItter specs are specified as measured on a clock characterization board. System designers need to take special care not to use these numbers, as the in-system performance will be somewhat degraded. The receiver EMTS (chispet or CPU) will have the receiver jitter specs as measured in a real system.

<sup>&</sup>lt;sup>2</sup> Phase jitter requirement: The designated Gen2 outputs will meet the reference clock jitter requirements from the PCI Express Gen2 Base Spec. The test is performed on a component test board under quiet conditions with all outputs on.

<sup>&</sup>lt;sup>3</sup>See http://www.pcisig.com for complete specs

Electrical Characteristics - REF-14.318MHz, Commercial Temperature Range

| PARAMETER                     | SYMBOL            | CONDITIONS                             | MIN      | TYP      | MAX      | UNITS | Notes |

|-------------------------------|-------------------|----------------------------------------|----------|----------|----------|-------|-------|

| Long Accuracy                 | ppm               | see Tperiod min-max values             | -100     | 0        | 100      | ppm   | 2, 4  |

| Clock period                  | Tperiod           | 14.318MHz output nominal               | 69.82033 | 69.84129 | 69.86224 | ns    | 2, 3  |

| Absolute min/max period       | Tabs              | 14.318MHz output nominal               | 69.83400 |          | 70.84800 | ns    | 2     |

| CLK High Time                 | THIGH             |                                        | 29.97543 |          | 38.46654 | ٧     |       |

| CLK Low time                  | TLOW              |                                        | 29.57543 |          | 38.26654 | ٧     |       |

| Output High Current           | IOH               | VOH @MIN = 1.0 V,<br>VOH@MAX = 3.135 V | -33      |          | -33      | mA    |       |

| Output Low Current            | IOL               | VOL @MIN = 1.95 V,<br>VOL @MAX = 0.4 V | 30       |          | 38       | mA    |       |

| Rising/Falling Edge Slew Rate | t <sub>SLEW</sub> | Measured between 0.8 to 2.0 V          | 1        | 1.7      | 4        | V/ns  | 1     |

| Duty Cycle                    | dt1               | VT = 1.5 V                             | 45       | 53       | 55       | %     | 2     |

| Jitter, Cycle to cycle        | tjcyc-cyc         | VT = 1.5 V                             |          | 115      | 1000     | ps    | 2     |

NOTES: (unless otherwise noted, guaranteed by design and characterization, not 100% tested in production).

Electrical Characteristics - 27MHz\_Spread / 27MHz\_NonSpread, Commercial Temperature Range

| PARAMETER                      | SYMBOL                | CONDITIONS                                                   | MIN     | TYP  | MAX     | UNITS  | Notes |

|--------------------------------|-----------------------|--------------------------------------------------------------|---------|------|---------|--------|-------|

| Long Appurpay                  | nnm                   | see Tperiod min-max values                                   | -50     |      | 50      | nnm    | 1,2   |

| Long Accuracy                  | ppm                   | see i peliou IIIII-iliax values                              | -15     |      | 15      | 15 ppm |       |

| Clock period                   | T <sub>period</sub>   | 27.000MHz output nominal                                     | 37.0365 |      | 37.0376 |        |       |

| Output High Current            | I <sub>OH</sub>       | VOH @MIN = 1.0 V,<br>VOH@MAX = 3.135 V                       | -29     |      | -23     | mA     | 1     |

| Output Low Current             | I <sub>OL</sub>       | VOL @MIN = 1.95 V,<br>VOL @MAX = 0.4 V                       | 29      |      | 27      | mA     | 1     |

| Rising/Falling Edge Slew Rate  | t <sub>slewr/f</sub>  | Rising/Falling edge rate                                     | 1       | 2    | 4       | V/ns   | 1     |

| Duty Cycle                     | d <sub>t1</sub>       | $V_{T} = 1.5 V$                                              | 45      | 50.4 | 55      | %      | 1     |

|                                | t <sub>lti</sub>      | Long Term (10us)                                             |         | 485  | 800     | ps     |       |

| Jitter, 27MHz_NonSpread Output | t <sub>jpk-pk</sub>   | $V_{T} = 1.5 V$                                              | -100    |      | 100     | ps     |       |

|                                | t <sub>jcyc-cyc</sub> | $V_T = 1.5 V$                                                |         | 57   | 120     | ps     |       |

| Jitter, 27MHz_Spread Output    | t.                    | $V_T = 1.5 \text{ V SS}\% <= 1.5\% \text{ pk to pk}$         |         | 82   | 200     | ps     | 4     |

| onter, 27 wii iz_Spread Odiput | t <sub>jcyc-cyc</sub> | $V_T = 1.5 \text{ V}, \text{ SS\%} > 1.5\% \text{ pk to pk}$ |         | 134  | 200     | ps     | 4     |

NOTES: (unless otherwise noted, guaranteed by design and characterization, not 100% tested in production).

<sup>&</sup>lt;sup>1</sup>Edge rate in system is measured from 0.8V to 2.0V.

<sup>&</sup>lt;sup>2</sup> Duty cycle, Peroid and Jitter are measured with respect to 1.5V

<sup>&</sup>lt;sup>3</sup> The average period over any 1us period of time

$<sup>^4</sup>$  Using frequency counter with the measurment interval equal or greater that 0.15s, target frequency is 14.318180 MHz

<sup>&</sup>lt;sup>1</sup>Edge rate in system is measured from 0.8V to 2.0V at default slew rate control setting.

<sup>&</sup>lt;sup>2</sup> All Long Term Accuracy and Clock Period specifications are guaranteed assuming that REF out is at 14.31818MHz

<sup>&</sup>lt;sup>3</sup> At nominal temperature and voltage.

<sup>&</sup>lt;sup>4</sup> Long term and peak to peak jitter do not apply to the 27MHz spreading output. The spread modulation directly impacts these values.

## Absolute Maximum Ratings - DC Parameters, Industrial Temperature Range

| PARAMETER              | SYMBOL                | CONDITIONS                          | MIN       | TYP | MAX | UNITS | Notes |

|------------------------|-----------------------|-------------------------------------|-----------|-----|-----|-------|-------|

| Maximum Supply Voltage | $VDD_{xxx}$           | Supply Voltage                      |           |     | 4.6 | V     | 1     |

| Maximum Supply Voltage | VDD <sub>xxx_IO</sub> | Low-Voltage Differential I/O Supply |           |     | 3.8 | V     | 1     |

| Maximum Input Voltage  | V <sub>IH</sub>       | 3.3V Tolerant Inputs                |           |     | 4.6 | V     | 1,2   |

| Minimum Input Voltage  | $V_{IL}$              | Any Input                           | GND - 0.5 |     |     | V     | 1     |

| Storage Temperature    | Ts                    | •                                   | -65       |     | 150 | °C    | 1     |

| Input ESD protection   | ESD prot              | Human Body Model                    | 2000      |     |     | V     | 1,3   |

Notes: (unless otherwise noted, guaranteed by design and characterization, not 100% tested in production).

Electrical Characteristics - Input/Supply/Common Output DC Parameters, Industrial Temperature Range

| PARAMETER                                     | SYMBOL                 | CONDITIONS                                                                    | MIN                   | TYP    | MAX            | UNITS | Notes |

|-----------------------------------------------|------------------------|-------------------------------------------------------------------------------|-----------------------|--------|----------------|-------|-------|

| Ambient Operating Temp                        | T <sub>ambind</sub>    | Industrial Range                                                              | -40                   |        | 85             | ô     |       |

| Supply Voltage, Core                          | VDD <sub>xxx</sub>     | Supply Voltage                                                                | 3.135                 | 3.3    | 3.465          | V     |       |

| Supply Voltage, I/O                           | VDD <sub>xxx IO</sub>  | Low-Voltage Differential I/O Supply                                           | 0.9975                | 1.05   | 3.465          | V     | 5     |

| Input High Voltage                            | V <sub>IHSE</sub>      | Single-ended 3.3V inputs                                                      | 2                     | 2.4    | $V_{DD} + 0.3$ | V     | 3     |

| Input Low Voltage                             | V <sub>ILSE</sub>      | Single-ended 3.3V inputs                                                      | V <sub>SS</sub> - 0.3 | 0.4    | 0.8            | V     | 3     |

| Low Threshold Input - High Voltage            | V <sub>IH_FSC</sub>    | 3.3 V +/-5%, Voltage for which FSC = '1'                                      | 0.7                   |        | 3.3            | V     | 4     |

| Low Threshold Input - Low Voltage             | V <sub>IL FSC</sub>    | 3.3 V +/-5%                                                                   | V <sub>SS</sub> - 0.3 |        | 0.35           | V     |       |

| Input Leakage Current                         | I <sub>IN</sub>        | $V_{IN} = V_{DD}$ , $V_{IN} = GND$                                            | -5                    |        | 5              | uA    | 2     |

| Input Leakage Current                         | I <sub>INRES</sub>     | Inputs with pull up or pull down resistors $V_{IN} = V_{DD}$ , $V_{IN} = GND$ | -200                  |        | 200            | uA    |       |

| Output High Voltage                           | V <sub>OHSE</sub>      | Single-ended outputs, I <sub>OH</sub> = -1mA                                  | 2.4                   |        |                | ٧     | 1     |

| Output Low Voltage                            | $V_{OLSE}$             | Single-ended outputs, I <sub>OL</sub> = 1 mA                                  |                       |        | 0.4            | V     | 1     |

| Operating Supply Current                      | I <sub>DDOP3.3</sub>   | Full Active, C <sub>L</sub> = Full load; Idd 3.3V                             |                       | 92     | 110            | mA    |       |

| Operating Supply Current                      | I <sub>DDOPIO</sub>    | Full Active, C <sub>L</sub> = Full load; IDD IO                               |                       | 18     | 25             | mA    | 5     |

| iAMT Mode Current                             | I <sub>DDiAMT3.3</sub> | M1 mode, 3.3V Rail                                                            |                       | 48     | 65             | mA    |       |

| IAMT Mode Current                             | I <sub>DDIAMTIO</sub>  | M1 Mode, IO Rail                                                              |                       | 6      | 15             | mA    | 5     |

| Powerdown Current                             | I <sub>DDPD3.3</sub>   | Power down mode, 3.3V Rail                                                    |                       | 3.2    | 8              | mA    |       |

| i owerdown odnent                             | I <sub>DDPDIO</sub>    | Power down mode, IO Rail                                                      |                       | 0      | 0.05           | mA    | 5     |

| Input Frequency                               | Fi                     | V <sub>DD</sub> = 3.3 V                                                       |                       | 14.318 | 15             | MHz   |       |

| Pin Inductance                                | $L_{pin}$              |                                                                               |                       | 5      | 7              | nΗ    |       |

|                                               | C <sub>IN</sub>        | Logic Inputs                                                                  | 1.5                   | 4      | 5              | pF    |       |

| Input Capacitance                             | C <sub>OUT</sub>       | Output pin capacitance                                                        |                       | 5      | 6              | pF    |       |

|                                               | C <sub>INX</sub>       | X1 & X2 pins                                                                  |                       | 4      | 6              | pF    |       |

| Clk Stabilization                             | T <sub>STAB</sub>      | From VDD Power-Up or de-assertion of PD to 1st clock                          |                       |        | 1.8            | ms    |       |

| Tfall_SE                                      | T <sub>FALL</sub>      | Fall/rise time of all 3.3V control inputs from 20-80%                         |                       |        | 10             | ns    | 1     |

| Trise_SE                                      | T <sub>RISE</sub>      | Fail/fise time of all 5.5% control inputs from 20-60%                         |                       |        | 10             | ns    | 1     |

| SMBus Voltage                                 | $V_{DD}$               |                                                                               | 2.7                   | 3.3    | 5.5            | ٧     |       |

| Low-level Output Voltage                      | $V_{OLSMB}$            | @ I <sub>PULLUP</sub>                                                         |                       |        | 0.4            | ٧     |       |

| Current sinking at V <sub>OLSMB</sub> = 0.4 V | I <sub>PULLUP</sub>    | SMB Data Pin                                                                  | 4                     | 5      |                | mA    |       |

| SCLK/SDATA<br>Clock/Data Rise Time            | T <sub>RI2C</sub>      | (Max VIL - 0.15) to<br>(Min VIH + 0.15)                                       |                       |        | 1000           | ns    |       |

| SCLK/SDATA<br>Clock/Data Fall Time            | T <sub>FI2C</sub>      | (Min VIH + 0.15) to<br>(Max VIL - 0.15)                                       |                       |        | 300            | ns    |       |

| Maximum SMBus Operating Frequency             | F <sub>SMBUS</sub>     |                                                                               |                       |        | 100            | kHz   |       |

| Spread Spectrum Modulation Frequency          | f <sub>SSMOD</sub>     | Triangular Modulation                                                         | 30                    | 32.54  | 33             | kHz   |       |

Notes: (unless otherwise noted, guaranteed by design and characterization, not 100% tested in production).

<sup>&</sup>lt;sup>1</sup> Operation under these conditions is neither implied, nor guaranteed.

<sup>&</sup>lt;sup>2</sup> Maximum VIH is not to exceed VDD

<sup>&</sup>lt;sup>3</sup> Human Body Model

<sup>&</sup>lt;sup>1</sup>Signal is required to be monotonic in this region.

$<sup>^{\</sup>rm 2}\,{\rm Input}$  leakage current does not include inputs with pull-up or pull-down resistors

$<sup>^{\</sup>rm 3}\,3.3\text{V}$  referenced inputs are: SCLK, SDATA, and CKPWRGD

<sup>&</sup>lt;sup>4</sup> Frequency Select pins which have tri-level input

<sup>&</sup>lt;sup>5</sup> If present, not all parts have this feature.

#### AC Electrical Characteristics - Low Power Differential Outputs, Industrial Temperature Range

| PARAMETER                  | SYMBOL               | CONDITIONS                                           | MIN  | TYP  | МАХ  | UNITS | NOTES |

|----------------------------|----------------------|------------------------------------------------------|------|------|------|-------|-------|

| Rising Edge Slew Rate      | t <sub>SLR</sub>     | Averaging on                                         | 2.5  | 3.7  | 4.2  | V/ns  | 2, 3  |

| Falling Edge Slew Rate     | t <sub>FLR</sub>     | Averaging on                                         | 2.5  | 3.7  | 4.2  | V/ns  | 2, 3  |

| Slew Rate Variation        | t <sub>SLVAR</sub>   | Averaging on                                         |      | 12.2 | 20   | %     | 1, 6  |

| Differential Voltage Swing | V <sub>SWING</sub>   | Averaging off                                        | 300  |      |      | mV    | 2     |

| Crossing Point Voltage     | VX <sub>ABS</sub>    | Averaging off                                        | 300  | 447  | 550  | mV    | 1,4,5 |

| Crossing Point Variation   | VX <sub>ABSVAR</sub> | Averaging off                                        |      | 19   | 140  | mV    | 1,4,9 |

| Maximum Output Voltage     | $V_{HIGH}$           | Averaging off                                        |      | 941  | 1150 | mV    | 1,7   |

| Minimum Output Voltage     | $V_{LOW}$            | Averaging off                                        | -300 | -43  |      | mV    | 1,8   |

| Duty Cycle                 | DCYC                 | Averaging on                                         | 45   | 49.8 | 55   | %     | 2     |

| CPU Skew                   | t <sub>SKEWCPU</sub> | Averaging on                                         |      | 35   | 100  | ps    |       |

| SRC Skew                   | t <sub>SKEWSRC</sub> | Averaging on, SRC to SATA skew when Byte0, bit 1 = 0 |      | 288  | 350  | ps    |       |

NOTES: (unless otherwise noted, guaranteed by design and characterization, not 100% tested in production). C<sub>L</sub> = 2pF, Rs = 0 ohms.

#### Clock Jitter Specifications - Low Power Differential Outputs, Industrial Temperature Range

| PARAMETER                    | SYMBOL                  | CONDITIONS                                 | MIN | TYP | MAX | UNITS       | NOTES |

|------------------------------|-------------------------|--------------------------------------------|-----|-----|-----|-------------|-------|

| CPU Jitter - Cycle to Cycle  | CPUJ <sub>C2C</sub>     | Differential Measurement                   |     | 55  | 85  | ps          | 1     |

| SRC Jitter - Cycle to Cycle  | SRCJ <sub>C2C</sub>     | Differential Measurement                   |     | 55  | 125 | ps          | 1     |

| SATA Jitter - Cycle to Cycle | SATAJ <sub>C2C</sub>    | Differential Measurement                   |     | 55  | 125 | ps          | 1     |

| DOT Jitter - Cycle to Cycle  | DOTJ <sub>C2C</sub>     | Differential Measurement                   |     | 55  | 250 | ps          | 1     |

|                              | t <sub>jphasePLL</sub>  | PCIe Gen 1                                 |     | 45  | 86  | ps (p-p)    | 1,2,3 |

| SRC Phase Jitter             | t <sub>jphaseLo</sub>   | PCIe Gen 2<br>10kHz < f < 1.5MHz           |     | 2   | 3   | ps<br>(RMS) | 1,2,3 |

|                              | t <sub>jphaseHigh</sub> | PCIe Gen 2<br>1.5MHz < f < Nyquist (50MHz) |     | 2.6 | 3.1 | ps<br>(RMS) | 1,2,3 |

NOTES: (unless otherwise noted, guaranteed by design and characterization, not 100% tested in production).  $C_L = 2pF$ , Rs = 0 ohms.

<sup>&</sup>lt;sup>1</sup>Measurement taken for single ended waveform on a component test board (not in system)

$<sup>^{2}</sup>$  Measurement taken from differential waveform on a component test board. (not in system)

$<sup>^3</sup>$  Slew rate measured through mimimum V\_swing voltage range centered about differential zero

<sup>&</sup>lt;sup>4</sup> Vcross is defined at the voltage where Clock = Clock#, measured on a component test board (not in system)

<sup>&</sup>lt;sup>5</sup> Only applies to the differential rising edge (Clock rising, Clock# falling)

<sup>&</sup>lt;sup>6</sup> Matching applies to rising edge rate for Clock and falling edge rate for Clock#. It is measured using a +/-75mV window centered on the average cross point where Clock rising meets Clock# falling. The median cross point is used to calculate the voltage

<sup>&</sup>lt;sup>7</sup> The max voltage including overshoot.

<sup>&</sup>lt;sup>8</sup> The min voltage including undershoot.

<sup>&</sup>lt;sup>9</sup> The total variation of all Vcross measurements in any particular system. Note this is a subset of V\_cross min/max (V\_Cross absolute) allowed. The intent is to limit Vcross induced modulation by setting C\_cross\_delta to be smaller than V\_Cross absolute

<sup>&</sup>lt;sup>1</sup>JItter specs are specified as measured on a clock characterization board. System designers need to take special care not to use these numbers, as the in-system performance will be somewhat degraded. The receiver EMTS (chispet or CPU) will have the receiver jitter specs as measured in a real system.

<sup>&</sup>lt;sup>2</sup> Phase jitter requirement: The designated Gen2 outputs will meet the reference clock jitter requirements from the PCI Express Gen2 Base Spec. The test is performed on a component test board under quiet conditions with all outputs on.

<sup>&</sup>lt;sup>3</sup>See http://www.pcisig.com for complete specs

#### Electrical Characteristics - REF-14.318MHz, Industrial Temperature Range

| PARAMETER                     | SYMBOL            | CONDITIONS                             | MIN      | TYP      | MAX      | UNITS | Notes |

|-------------------------------|-------------------|----------------------------------------|----------|----------|----------|-------|-------|

| Long Accuracy                 | ppm               | see Tperiod min-max values             | -100     | 0        | 100      | ppm   | 2, 4  |

| Clock period                  | Tperiod           | 14.318MHz output nominal               | 69.82033 | 69.84129 | 69.86224 | ns    | 2, 3  |

| Absolute min/max period       | Tabs              | 14.318MHz output nominal               | 69.83400 |          | 70.84800 | ns    | 2     |

| CLK High Time                 | THIGH             |                                        | 29.97543 |          | 38.46654 | V     |       |

| CLK Low time                  | TLOW              |                                        | 29.57543 |          | 38.26654 | V     |       |

| Output High Current           | ЮН                | VOH @MIN = 1.0 V,<br>VOH@MAX = 3.135 V | -33      |          | -33      | mA    |       |

| Output Low Current            | IOL               | VOL @MIN = 1.95 V,<br>VOL @MAX = 0.4 V | 30       |          | 38       | mA    |       |

| Rising/Falling Edge Slew Rate | t <sub>SLEW</sub> | Measured between 0.8 to 2.0 V          | 1        | 1.8      | 4        | V/ns  | 1     |

| Duty Cycle                    | dt1               | VT = 1.5 V                             | 45       | 52.8     | 55       | %     | 2     |

| Jitter, Cycle to cycle        | tjcyc-cyc         | VT = 1.5 V                             |          | 122      | 500      | ps    | 2     |

NOTES: (unless otherwise noted, guaranteed by design and characterization, not 100% tested in production).

### Electrical Characteristics - 27MHz\_Spread / 27MHz\_NonSpread, Industrial Temperature Range

| PARAMETER                      | SYMBOL                | CONDITIONS                                                   | MIN     | TYP  | MAX     | UNITS | Notes |

|--------------------------------|-----------------------|--------------------------------------------------------------|---------|------|---------|-------|-------|

| Long Acquirocu                 | 2000                  | and Theriad min may value                                    | -50     |      | 50      |       | 1,2   |

| Long Accuracy                  | ppm                   | see Tperiod min-max values                                   | -15     |      | 15      | ppm   | 1,2,3 |

| Clock period                   | T <sub>period</sub>   | 27.000M outputs, 27M SS with SS OFF                          | 37.0365 |      | 37.0376 |       |       |

| Output High Current            | I <sub>OH</sub>       | VOH @MIN = 1.0 V,<br>VOH@MAX = 3.135 V                       | -29     |      | -23     | mA    |       |

| Output Low Current             | I <sub>OL</sub>       | VOL @MIN = 1.95 V,<br>VOL @MAX = 0.4 V                       | 29      |      | 27      | mA    |       |

| Rising/Falling Edge Slew Rate  | t <sub>SLEW</sub>     | Measured between 0.8 to 2.0 V                                | 1       | 2    | 4       | V/ns  | 1     |

| Duty Cycle                     | d <sub>t1</sub>       | $V_T = 1.5 \text{ V}$                                        | 45      | 50.4 | 55      | %     |       |

|                                | t <sub>lti</sub>      | Long Term (10us)                                             |         | 485  | 800     | ps    |       |

| Jitter, 27MHz_NonSpread Output | t <sub>ipk-pk</sub>   | V <sub>T</sub> = 1.5 V                                       | -100    |      | 100     | ps    |       |

|                                | t <sub>icyc-cyc</sub> | V <sub>T</sub> = 1.5 V                                       |         | 57   | 120     | ps    |       |

| Litter OZMULT Coreed Output    |                       | V <sub>T</sub> = 1.5 V SS% <= 1.5% pk to pk                  |         | 108  | 200     | ps    | 4     |