Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# ProASIC3 nano FPGA Fabric User's Guide

# **Table of Contents**

|   | Introduction                                                                  | 7              |

|---|-------------------------------------------------------------------------------|----------------|

|   | Contents                                                                      | 7              |

|   | Revision History                                                              | 7              |

|   | Related Information                                                           | 7              |

|   |                                                                               |                |

| 1 | FPGA Array Architecture in Low Power Flash Devices                            | 9              |

|   | Device Architecture                                                           | 9              |

|   | FPGA Array Architecture Support                                               | 10             |

|   | Device Overview                                                               | 11             |

|   | Related Documents                                                             | 20             |

|   | List of Changes                                                               | 20             |

|   |                                                                               |                |

| 2 | Low Power Modes in ProASIC3/E and ProASIC3 nano FPGAs                         | 21             |

|   | Introduction                                                                  | 21             |

|   | Power Consumption Overview                                                    | 21             |

|   | Static (Idle) Mode                                                            | 22             |

|   | User Low Static (Idle) Mode                                                   | 23             |

|   | Sleep Mode                                                                    | 25             |

|   | Shutdown Mode                                                                 | 27             |

|   | Conclusion                                                                    | 28             |

|   | Related Documents                                                             | 28             |

|   | List of Changes                                                               | 29             |

|   |                                                                               |                |

| 3 | Global Resources in Low Power Flash Devices.                                  | 31             |

|   | Introduction                                                                  |                |

|   | Global Architecture                                                           |                |

|   | Global Resource Support in Flash-Based Devices                                | 32             |

|   | VersaNet Global Network Distribution                                          | 33             |

|   | Chip and Quadrant Global I/Os                                                 | 35             |

|   | Spine Architecture                                                            | 41             |

|   | Using Clock Aggregation                                                       | 44             |

|   | Design Recommendations                                                        | 46             |

|   | Conclusion                                                                    | 58             |

|   | Related Documents                                                             | 58             |

|   | List of Changes                                                               | 59             |

|   |                                                                               |                |

| 4 | Clock Conditioning Circuits in Low Power Flash Devices and Mixed Signal FPGAs |                |

|   | Introduction                                                                  |                |

|   | Overview of Clock Conditioning Circuitry                                      |                |

|   |                                                                               |                |

|   | CCC Support in Microsemi's Flash Devices                                      |                |

|   | Global Buffers with No Programmable Delays                                    | 64             |

|   | Global Buffers with No Programmable Delays                                    | 64<br>64       |

|   | Global Buffers with No Programmable Delays                                    | 64<br>64       |

|   | Global Buffers with No Programmable Delays                                    | 64<br>64<br>67 |

### ProASIC3 nano FPGA Fabric User's Guide

|   | PLL Core Specifications                                                  | 84    |

|---|--------------------------------------------------------------------------|-------|

|   | Functional Description                                                   | 85    |

|   | Software Configuration                                                   | 96    |

|   | Detailed Usage Information                                               | . 104 |

|   | Recommended Board-Level Considerations                                   | . 112 |

|   | Conclusion                                                               | . 113 |

|   | Related Documents                                                        | . 113 |

|   | List of Changes                                                          | . 113 |

|   |                                                                          |       |

| 5 | FlashROM in Microsemi's Low Power Flash Devices                          | . 117 |

|   | Introduction                                                             |       |

|   | Architecture of User Nonvolatile FlashROM                                |       |

|   | FlashROM Support in Flash-Based Devices                                  |       |

|   | FlashROM Applications                                                    | . 120 |

|   | FlashROM Security                                                        | . 121 |

|   | Programming and Accessing FlashROM                                       | . 122 |

|   | FlashROM Design Flow                                                     | . 124 |

|   | Custom Serialization Using FlashROM                                      | . 129 |

|   | Conclusion                                                               | . 130 |

|   | Related Documents                                                        | . 130 |

|   | List of Changes                                                          | . 130 |

| _ |                                                                          |       |

| 6 | SRAM and FIFO Memories in Microsemi's Low Power Flash Devices            |       |

|   | Introduction                                                             |       |

|   | Device Architecture                                                      |       |

|   | SRAM/FIFO Support in Flash-Based Devices                                 |       |

|   | SRAM and FIFO Architecture                                               |       |

|   | Memory Blocks and Macros                                                 |       |

|   | Initializing the RAM/FIFO                                                |       |

|   | Software Support                                                         |       |

|   | Conclusion                                                               |       |

|   | List of Changes                                                          | . 157 |

| 7 | I/O Christiana in none Devices                                           | 450   |

| 1 | I/O Structures in nano Devices.                                          |       |

|   | Introduction                                                             |       |

|   | Low Power Flash Device I/O Support                                       |       |

|   | nano Standard I/Os                                                       |       |

|   | I/O Architecture                                                         |       |

|   | I/O Standards                                                            |       |

|   | Wide Range I/O Support                                                   |       |

|   | I/O Features                                                             |       |

|   | Simultaneously Switching Outputs (SSOs) and Printed Circuit Board Layout |       |

|   | I/O Software Support                                                     |       |

|   | User I/O Naming Convention                                               |       |

|   | I/O Bank Architecture and CCC Naming Conventions                         |       |

|   | Board-Level Considerations                                               |       |

|   | Conclusion                                                               |       |

|   | Related Documents                                                        |       |

|   | List of Changes                                                          | 183   |

### Table of Contents

| 8  | I/O Software Control in Low Power Flash Devices                                          | 185 |

|----|------------------------------------------------------------------------------------------|-----|

|    | Flash FPGAs I/O Support                                                                  | 186 |

|    | Software-Controlled I/O Attributes                                                       | 187 |

|    | Implementing I/Os in Microsemi Software                                                  | 188 |

|    | Assigning Technologies and VREF to I/O Banks                                             | 198 |

|    | Conclusion                                                                               | 203 |

|    | Related Documents                                                                        | 203 |

|    | List of Changes                                                                          | 204 |

| 9  | DDR for Microsemi's Low Power Flash Devices                                              | 205 |

|    | Introduction                                                                             | 205 |

|    | Double Data Rate (DDR) Architecture                                                      | 205 |

|    | DDR Support in Flash-Based Devices                                                       | 206 |

|    | I/O Cell Architecture                                                                    | 207 |

|    | Input Support for DDR                                                                    | 209 |

|    | Output Support for DDR                                                                   | 209 |

|    | Instantiating DDR Registers                                                              | 210 |

|    | Design Example                                                                           | 216 |

|    | Conclusion                                                                               | 218 |

|    | List of Changes                                                                          | 219 |

| 10 | Programming Flash Devices                                                                | 221 |

|    | Introduction                                                                             | 22  |

|    | Summary of Programming Support                                                           | 22  |

|    | Programming Support in Flash Devices                                                     | 222 |

|    | General Flash Programming Information                                                    | 223 |

|    | Important Programming Guidelines                                                         | 229 |

|    | Related Documents                                                                        | 231 |

|    | List of Changes                                                                          | 232 |

| 11 | Security in Low Power Flash Devices                                                      | 235 |

|    | Security in Programmable Logic                                                           | 235 |

|    | Security Support in Flash-Based Devices                                                  | 236 |

|    | Security Architecture                                                                    | 237 |

|    | Security Features                                                                        | 238 |

|    | Security in Action                                                                       | 242 |

|    | FlashROM Security Use Models                                                             | 245 |

|    | Generating Programming Files                                                             | 247 |

|    | Conclusion                                                                               | 258 |

|    | Glossary                                                                                 | 258 |

|    | References                                                                               | 258 |

|    | Related Documents                                                                        | 259 |

|    | List of Changes                                                                          | 259 |

| 12 | In-System Programming (ISP) of Microsemi's Low Power Flash Devices Using FlashPro4/3/3X. | 261 |

|    | Introduction                                                                             |     |

|    | ISP Architecture                                                                         |     |

|    | ISP Support in Flash-Based Devices                                                       |     |

|    | Programming Voltage (VPUMP) and VJTAG                                                    | 263 |

|    | Nonvolatile Memory (NVM) Programming Voltage                                             | 263 |

### ProASIC3 nano FPGA Fabric User's Guide

|    | IEEE 1532 (JTAG) Interface                                                   |     |

|----|------------------------------------------------------------------------------|-----|

|    | Security                                                                     | 264 |

|    | Security in ARM-Enabled Low Power Flash Devices                              | 265 |

|    | FlashROM and Programming Files                                               | 267 |

|    | Programming Solution                                                         | 268 |

|    | ISP Programming Header Information                                           | 269 |

|    | Board-Level Considerations                                                   | 271 |

|    | Conclusion                                                                   | 272 |

|    | Related Documents                                                            | 272 |

|    | List of Changes                                                              | 273 |

|    |                                                                              |     |

| 13 | Core Voltage Switching Circuit for IGLOO and ProASIC3L In-System Programming | 275 |

|    | Introduction                                                                 |     |

|    | Microsemi's Flash Families Support Voltage Switching Circuit                 | 276 |

|    | Circuit Description                                                          | 277 |

|    | Circuit Verification                                                         | 278 |

|    | DirectC                                                                      | 280 |

|    | Conclusion                                                                   | 280 |

|    | List of Changes                                                              | 281 |

| 11 | Microprocessor Programming of Microsemi's Low Power Flash Devices            | 283 |

| 14 | Introduction                                                                 |     |

|    |                                                                              |     |

|    | Microprocessor Programming Support in Flash Devices                          |     |

|    | Programming Algorithm                                                        |     |

|    | Implementation Overview                                                      |     |

|    | Hardware Requirement                                                         |     |

|    | Security                                                                     |     |

|    | Conclusion                                                                   |     |

|    | List of Changes                                                              | 290 |

| 15 | Boundary Scan in Low Power Flash Devices                                     | 291 |

|    | Boundary Scan                                                                | 291 |

|    | TAP Controller State Machine                                                 | 291 |

|    | Microsemi's Flash Devices Support the JTAG Feature                           | 292 |

|    | Boundary Scan Support in Low Power Devices                                   |     |

|    | Boundary Scan Opcodes                                                        |     |

|    | Boundary Scan Chain                                                          |     |

|    | Board-Level Recommendations                                                  |     |

|    | Advanced Boundary Scan Register Settings                                     |     |

|    | List of Changes                                                              |     |

| 40 |                                                                              | 007 |

| 16 | UJTAG Applications in Microsemi's Low Power Flash Devices                    |     |

|    | Introduction                                                                 |     |

|    | UJTAG Support in Flash-Based Devices                                         |     |

|    | UJTAG Macro                                                                  |     |

|    | UJTAG Operation                                                              |     |

|    | Typical UJTAG Applications                                                   | 302 |

|    | Conclusion                                                                   | 306 |

|    | Related Documents                                                            |     |

|    | List of Changes                                                              | 306 |

### Table of Contents

| 17 | Power-Up/-Down Behavior of Low Power Flash Devices | . 307 |

|----|----------------------------------------------------|-------|

|    | Introduction                                       | 307   |

|    | Flash Devices Support Power-Up Behavior            | 308   |

|    | Power-Up/-Down Sequence and Transient Current      | 309   |

|    | I/O Behavior at Power-Up/-Down                     | 311   |

|    | Cold-Sparing                                       | 316   |

|    | Hot-Swapping                                       | 317   |

|    | Conclusion                                         | 317   |

|    | Related Documents                                  | 318   |

|    | List of Changes                                    | 318   |

| Α  | Summary of Changes                                 | . 319 |

|    | History of Revision to Chapters                    |       |

| В  | Product Support                                    | . 321 |

|    | Customer Service                                   | 321   |

|    | Customer Technical Support Center                  |       |

|    | Technical Support                                  |       |

|    | Website                                            | 321   |

|    | Contacting the Customer Technical Support Center   | 321   |

|    | ITAR Technical Support                             |       |

|    | Index                                              | 323   |

## Introduction

#### **Contents**

This user's guide contains information to help designers understand and use Microsemi's ProASIC®3 nano devices. Each chapter addresses a specific topic. Most of these chapters apply to other Microsemi device families as well. When a feature or description applies only to a specific device family, this is made clear in the text.

## **Revision History**

The revision history for each chapter is listed at the end of the chapter. Most of these chapters were formerly included in device handbooks. Some were originally application notes or information included in device datasheets.

A "Summary of Changes" table at the end of this user's guide lists the chapters that were changed in each revision of the document, with links to the "List of Changes" sections for those chapters.

#### **Related Information**

Refer to the *ProASIC3 nano Low Power Flash FPGAs* datasheet for detailed specifications, timing, and package and pin information.

The website for ProASIC3 nano devices is /www.microsemi.com/soc/products/pa3nano/default.aspx.

# 1 – FPGA Array Architecture in Low Power Flash Devices

## **Device Architecture**

#### **Advanced Flash Switch**

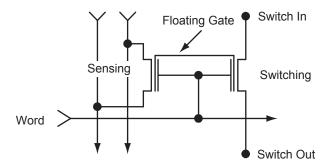

Unlike SRAM FPGAs, the low power flash devices use a live-at-power-up ISP flash switch as their programming element. Flash cells are distributed throughout the device to provide nonvolatile, reconfigurable programming to connect signal lines to the appropriate VersaTile inputs and outputs. In the flash switch, two transistors share the floating gate, which stores the programming information (Figure 1-1). One is the sensing transistor, which is only used for writing and verification of the floating gate voltage. The other is the switching transistor. The latter is used to connect or separate routing nets, or to configure VersaTile logic. It is also used to erase the floating gate. Dedicated high-performance lines are connected as required using the flash switch for fast, low-skew, global signal distribution throughout the device core. Maximum core utilization is possible for virtually any design. The use of the flash switch technology also removes the possibility of firm errors, which are increasingly common in SRAM-based FPGAs.

Figure 1-1 • Flash-Based Switch

## **FPGA Array Architecture Support**

The flash FPGAs listed in Table 1-1 support the architecture features described in this document.

Table 1-1 • Flash-Based FPGAs

| Series    | Family*              | Description                                                                                                                                                                                    |

|-----------|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IGLOO®    | IGL00                | Ultra-low power 1.2 V to 1.5 V FPGAs with Flash*Freeze technology                                                                                                                              |

|           | IGLOOe               | Higher density IGLOO FPGAs with six PLLs and additional I/O standards                                                                                                                          |

|           | IGLOO nano           | The industry's lowest-power, smallest-size solution                                                                                                                                            |

|           | IGLOO PLUS           | IGLOO FPGAs with enhanced I/O capabilities                                                                                                                                                     |

| ProASIC®3 | ProASIC3             | Low power, high-performance 1.5 V FPGAs                                                                                                                                                        |

|           | ProASIC3E            | Higher density ProASIC3 FPGAs with six PLLs and additional I/O standards                                                                                                                       |

|           | ProASIC3 nano        | Lowest-cost solution with enhanced I/O capabilities                                                                                                                                            |

|           | ProASIC3L            | ProASIC3 FPGAs supporting 1.2 V to 1.5 V with Flash*Freeze technology                                                                                                                          |

|           | RT ProASIC3          | Radiation-tolerant RT3PE600L and RT3PE3000L                                                                                                                                                    |

|           | Military ProASIC3/EL | Military temperature A3PE600L, A3P1000, and A3PE3000L                                                                                                                                          |

|           | Automotive ProASIC3  | ProASIC3 FPGAs qualified for automotive applications                                                                                                                                           |

| Fusion    | Fusion               | Mixed signal FPGA integrating ProASIC3 FPGA fabric, programmable analog block, support for ARM <sup>®</sup> Cortex <sup>™</sup> -M1 soft processors, and flash memory into a monolithic device |

Note: \*The device names link to the appropriate datasheet, including product brief, DC and switching characteristics, and packaging information.

## IGLOO Terminology

In documentation, the terms IGLOO series and IGLOO devices refer to all of the IGLOO devices as listed in Table 1-1. Where the information applies to only one product line or limited devices, these exclusions will be explicitly stated.

## ProASIC3 Terminology

In documentation, the terms ProASIC3 series and ProASIC3 devices refer to all of the ProASIC3 devices as listed in Table 1-1. Where the information applies to only one product line or limited devices, these exclusions will be explicitly stated.

To further understand the differences between the IGLOO and ProASIC3 devices, refer to the *Industry's Lowest Power FPGAs Portfolio*.

## **Device Overview**

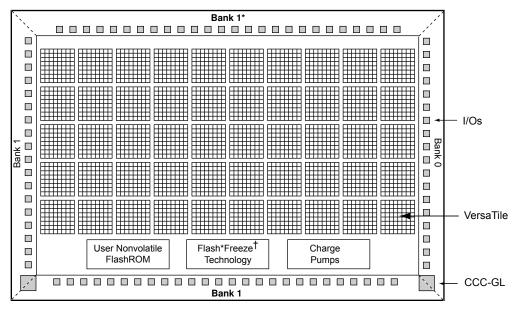

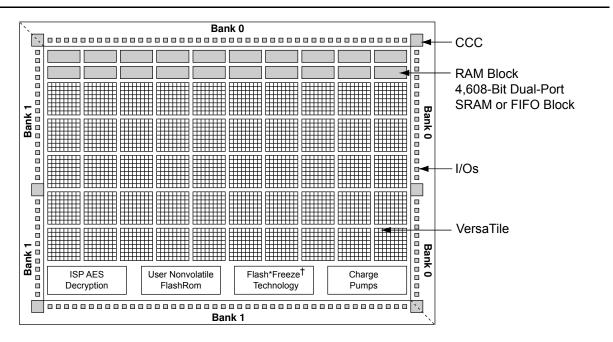

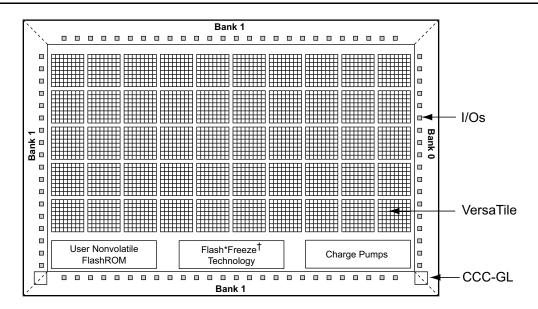

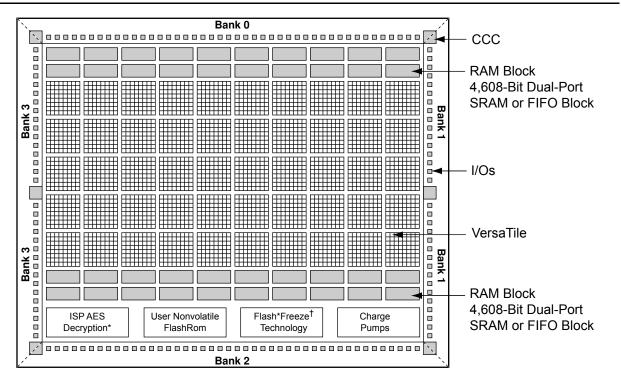

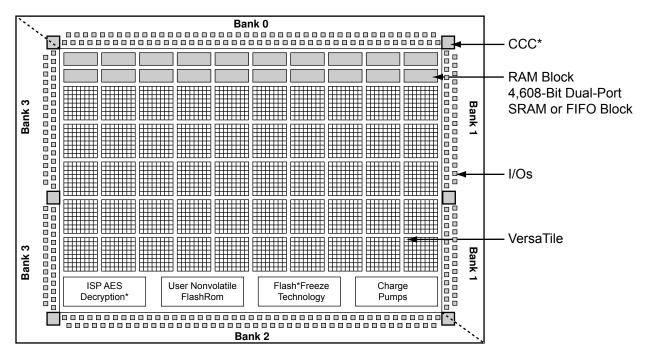

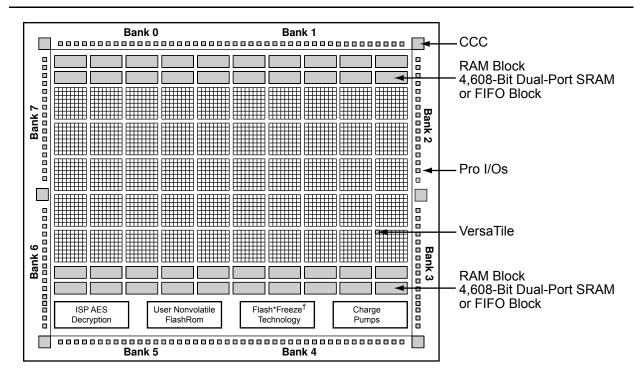

Low power flash devices consist of multiple distinct programmable architectural features (Figure 1-5 on page 13 through Figure 1-7 on page 14):

- · FPGA fabric/core (VersaTiles)

- · Routing and clock resources (VersaNets)

- FlashROM

- · Dedicated SRAM and/or FIFO

- 30 k gate and smaller device densities do not support SRAM or FIFO.

- Automotive devices do not support FIFO operation.

- I/O structures

- Flash\*Freeze technology and low power modes

Notes: \* Bank 0 for the 30 k devices

† Flash\*Freeze mode is supported on IGLOO devices.

Figure 1-2 • IGLOO and ProASIC3 nano Device Architecture Overview with Two I/O Banks (applies to 10 k and 30 k device densities, excluding IGLOO PLUS devices)

Note: † Flash\*Freeze mode is supported on IGLOO devices.

Figure 1-3 • IGLOO Device Architecture Overview with Two I/O Banks with RAM and PLL (60 k and 125 k gate densities)

Note: † Flash\*Freeze mode is supported on IGLOO devices.

Figure 1-4 • IGLOO Device Architecture Overview with Three I/O Banks (AGLN015, AGLN020, A3PN015, and A3PN020)

Note: Flash\*Freeze technology only applies to IGLOO and ProASIC3L families.

Figure 1-5 • IGLOO, IGLOO nano, ProASIC3 nano, and ProASIC3/L Device Architecture Overview with Four I/O Banks (AGL600 device is shown)

Note: \* AGLP030 does not contain a PLL or support AES security.

Figure 1-6 · IGLOO PLUS Device Architecture Overview with Four I/O Banks

Note: Flash\*Freeze technology only applies to IGLOOe devices.

Figure 1-7 · IGLOOe and ProASIC3E Device Architecture Overview (AGLE600 device is shown)

## I/O State of Newly Shipped Devices

Devices are shipped from the factory with a test design in the device. The power-on switch for VCC is OFF by default in this test design, so I/Os are tristated by default. Tristated means the I/O is not actively driven and floats. The exact value cannot be guaranteed when it is floating. Even in simulation software, a tristate value is marked as unknown. Due to process variations and shifts, tristated I/Os may float toward High or Low, depending on the particular device and leakage level.

If there is concern regarding the exact state of unused I/Os, weak pull-up/pull-down should be added to the floating I/Os so their state is controlled and stabilized.

#### **Core Architecture**

#### VersaTile

The proprietary IGLOO and ProASIC3 device architectures provide granularity comparable to gate arrays. The device core consists of a sea-of-VersaTiles architecture.

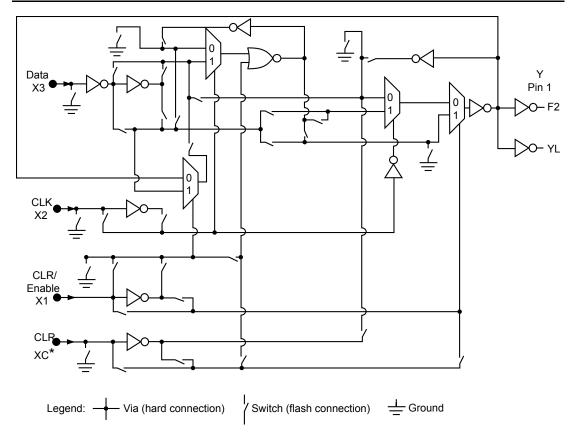

As illustrated in Figure 1-8, there are four inputs in a logic VersaTile cell, and each VersaTile can be configured using the appropriate flash switch connections:

- Any 3-input logic function

- · Latch with clear or set

- · D-flip-flop with clear or set

- Enable D-flip-flop with clear or set (on a 4<sup>th</sup> input)

VersaTiles can flexibly map the logic and sequential gates of a design. The inputs of the VersaTile can be inverted (allowing bubble pushing), and the output of the tile can connect to high-speed, very-long-line routing resources. VersaTiles and larger functions can be connected with any of the four levels of routing hierarchy.

When the VersaTile is used as an enable D-flip-flop, SET/CLR is supported by a fourth input. The SET/CLR signal can only be routed to this fourth input over the VersaNet (global) network. However, if, in the user's design, the SET/CLR signal is not routed over the VersaNet network, a compile warning message will be given, and the intended logic function will be implemented by two VersaTiles instead of one.

The output of the VersaTile is F2 when the connection is to the ultra-fast local lines, or YL when the connection is to the efficient long-line or very-long-line resources.

\* This input can only be connected to the global clock distribution network.

Figure 1-8 · Low Power Flash Device Core VersaTile

## **Array Coordinates**

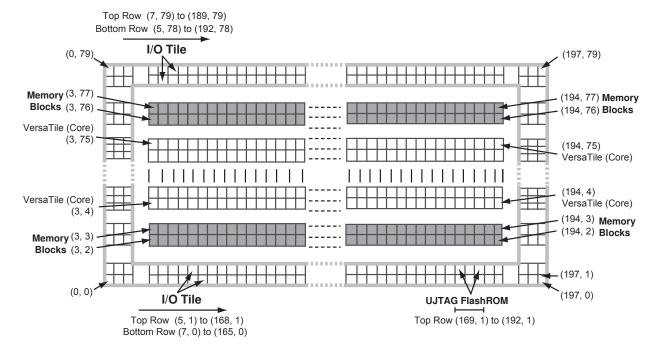

During many place-and-route operations in the Microsemi Designer software tool, it is possible to set constraints that require array coordinates. Table 1-2 provides array coordinates of core cells and memory blocks for IGLOO and ProASIC3 devices. Table 1-3 provides the information for IGLOO PLUS devices. Table 1-4 on page 17 provides the information for IGLOO nano and ProASIC3 nano devices. The array coordinates are measured from the lower left (0, 0). They can be used in region constraints for specific logic groups/blocks, designated by a wildcard, and can contain core cells, memories, and I/Os.

I/O and cell coordinates are used for placement constraints. Two coordinate systems are needed because there is not a one-to-one correspondence between I/O cells and core cells. In addition, the I/O coordinate system changes depending on the die/package combination. It is not listed in Table 1-2. The Designer ChipPlanner tool provides the array coordinates of all I/O locations. I/O and cell coordinates are used for placement constraints. However, I/O placement is easier by package pin assignment.

Figure 1-9 on page 17 illustrates the array coordinates of a 600 k gate device. For more information on how to use array coordinates for region/placement constraints, see the *Designer User's Guide* or online help (available in the software) for software tools.

Table 1-2 · IGLOO and ProASIC3 Array Coordinates

|          |                           | VersaTiles |   |      | Memory Rows |                        | Entire Die                 |        |            |

|----------|---------------------------|------------|---|------|-------------|------------------------|----------------------------|--------|------------|

| Device   |                           | Min.       |   | Max. |             | Bottom                 | Тор                        | Min.   | Max.       |

| IGL00    | ProASIC3/<br>ProASIC3L    | х          | у | х    | у           | (x, y)                 | (x, y)                     | (x, y) | (x, y)     |

| AGL015   | A3P015                    | 3          | 2 | 34   | 13          | None                   | None                       | (0, 0) | (37, 15)   |

| AGL030   | A3P030                    | 3          | 3 | 66   | 13          | None                   | None                       | (0, 0) | (69, 15)   |

| AGL060   | A3P060                    | 3          | 2 | 66   | 25          | None                   | (3, 26)                    | (0, 0) | (69, 29)   |

| AGL125   | A3P125                    | 3          | 2 | 130  | 25          | None                   | (3, 26)                    | (0, 0) | (133, 29)  |

| AGL250   | A3P250/L                  | 3          | 2 | 130  | 49          | None                   | (3, 50)                    | (0, 0) | (133, 53)  |

| AGL400   | A3P400                    | 3          | 2 | 194  | 49          | None                   | (3, 50)                    | (0, 0) | (197, 53)  |

| AGL600   | A3P600/L                  | 3          | 4 | 194  | 75          | (3, 2)                 | (3, 76)                    | (0, 0) | (197, 79)  |

| AGL1000  | A3P1000/L                 | 3          | 4 | 258  | 99          | (3, 2)                 | (3, 100)                   | (0, 0) | (261, 103) |

| AGLE600  | A3PE600/L,<br>RT3PE600L   | 3          | 4 | 194  | 75          | (3, 2)                 | (3, 76)                    | (0, 0) | (197, 79)  |

|          | A3PE1500                  | 3          | 4 | 322  | 123         | (3, 2)                 | (3, 124)                   | (0, 0) | (325, 127) |

| AGLE3000 | A3PE3000/L,<br>RT3PE3000L | 3          | 6 | 450  | 173         | (3, 2)<br>or<br>(3, 4) | (3, 174)<br>or<br>(3, 176) | (0, 0) | (453, 179) |

Table 1-3 · IGLOO PLUS Array Coordinates

|            | VersaTiles |   |        |     | Memor  | y Rows  | Entire Die |           |

|------------|------------|---|--------|-----|--------|---------|------------|-----------|

| Device     | Min. Max.  |   | Bottom | Тор | Min.   | Max.    |            |           |

| IGLOO PLUS | х          | у | х      | у   | (x, y) | (x, y)  | (x, y)     | (x, y)    |

| AGLP030    | 2          | 3 | 67     | 13  | None   | None    | (0, 0)     | (69, 15)  |

| AGLP060    | 2          | 2 | 67     | 25  | None   | (3, 26) | (0, 0)     | (69, 29)  |

| AGLP125    | 2          | 2 | 131    | 25  | None   | (3, 26) | (0, 0)     | (133, 29) |

| Table 1-4 · | IGLOO nano | and ProASIC3 nano | <b>Array Coordinates</b> |

|-------------|------------|-------------------|--------------------------|

|-------------|------------|-------------------|--------------------------|

|            |               | VersaTiles |           | Memory | y Rows  | Entire Die |           |

|------------|---------------|------------|-----------|--------|---------|------------|-----------|

| Device     |               | Min.       | Max.      | Bottom | Тор     | Min.       | Max.      |

| IGLOO nano | ProASIC3 nano | (x, y)     | (x, y)    | (x, y) | (x, y)  | (x, y)     | (x, y)    |

| AGLN010    | A3P010        | (0, 2)     | (32, 5)   | None   | None    | (0, 0)     | (34, 5)   |

| AGLN015    | A3PN015       | (0, 2)     | (32, 9)   | None   | None    | (0, 0)     | (34, 9)   |

| AGLN020    | A3PN020       | (0, 2)     | 32, 13)   | None   | None    | (0, 0)     | (34, 13)  |

| AGLN060    | A3PN060       | (3, 2)     | (66, 25)  | None   | (3, 26) | (0, 0)     | (69, 29)  |

| AGLN125    | A3PN125       | (3, 2)     | (130, 25) | None   | (3, 26) | (0, 0)     | (133, 29) |

| AGLN250    | A3PN250       | (3, 2)     | (130, 49) | None   | (3, 50) | (0, 0)     | (133, 49) |

Note: The vertical I/O tile coordinates are not shown. West-side coordinates are {(0, 2) to (2, 2)} to {(0, 77) to (2, 77)}; east-side coordinates are {(195, 2) to (197, 2)} to {(195, 77) to (197, 77)}.

Figure 1-9 · Array Coordinates for AGL600, AGLE600, A3P600, and A3PE600

## **Routing Architecture**

The routing structure of low power flash devices is designed to provide high performance through a flexible four-level hierarchy of routing resources: ultra-fast local resources; efficient long-line resources; high-speed, very-long-line resources; and the high-performance VersaNet networks.

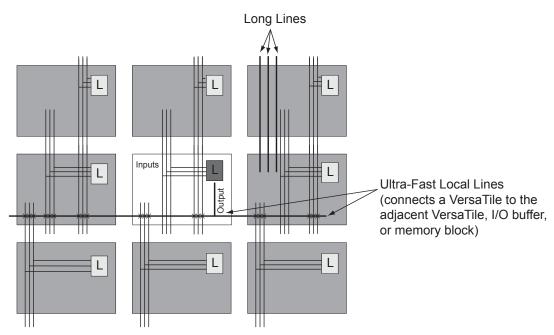

The ultra-fast local resources are dedicated lines that allow the output of each VersaTile to connect directly to every input of the eight surrounding VersaTiles (Figure 1-10). The exception to this is that the SET/CLR input of a VersaTile configured as a D-flip-flop is driven only by the VersaTile global network.

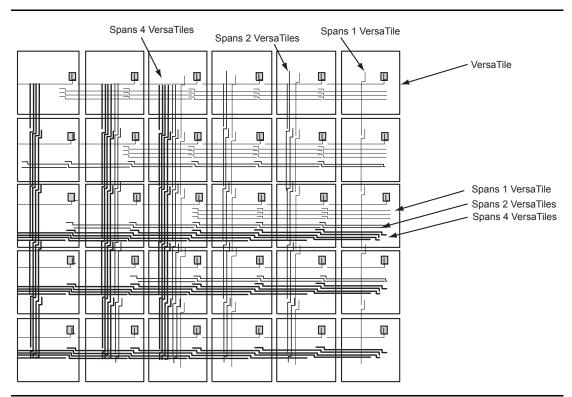

The efficient long-line resources provide routing for longer distances and higher-fanout connections. These resources vary in length (spanning one, two, or four VersaTiles), run both vertically and horizontally, and cover the entire device (Figure 1-11 on page 19). Each VersaTile can drive signals onto the efficient long-line resources, which can access every input of every VersaTile. Routing software automatically inserts active buffers to limit loading effects.

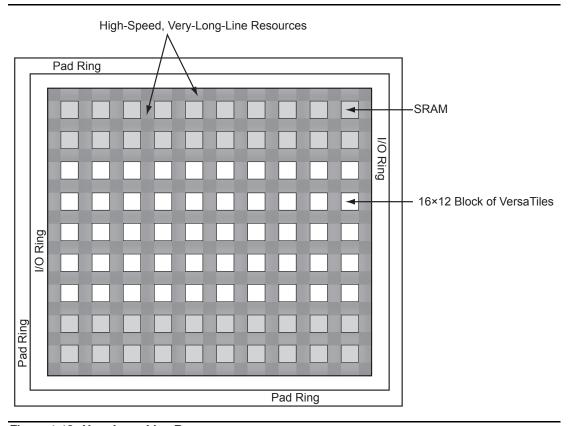

The high-speed, very-long-line resources, which span the entire device with minimal delay, are used to route very long or high-fanout nets: length ±12 VersaTiles in the vertical direction and length ±16 in the horizontal direction from a given core VersaTile (Figure 1-12 on page 19). Very long lines in low power flash devices have been enhanced over those in previous ProASIC families. This provides a significant performance boost for long-reach signals.

The high-performance VersaNet global networks are low-skew, high-fanout nets that are accessible from external pins or internal logic. These nets are typically used to distribute clocks, resets, and other high-fanout nets requiring minimum skew. The VersaNet networks are implemented as clock trees, and signals can be introduced at any junction. These can be employed hierarchically, with signals accessing every input of every VersaTile. For more details on VersaNets, refer to the "Global Resources in Low Power Flash Devices" section on page 31.

Note: Input to the core cell for the D-flip-flop set and reset is only available via the VersaNet global network connection.

Figure 1-10 • Ultra-Fast Local Lines Connected to the Eight Nearest Neighbors

Figure 1-11 • Efficient Long-Line Resources

Figure 1-12 • Very-Long-Line Resources

## **Related Documents**

## **User's Guides**

Designer User's Guide

http://www.microsemi.com/soc/documents/designer\_ug.pdf

# **List of Changes**

The following table lists critical changes that were made in each revision of the chapter.

| Date                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Changes                                                                                                                                                                                                   | Page   |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| August 2012                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | The "I/O State of Newly Shipped Devices" section is new (SAR 39542).                                                                                                                                      | 14     |

| July 2010                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | This chapter is no longer published separately with its own part number and version but is now part of several FPGA fabric user's guides.                                                                 | N/A    |

| IGLOO nano and ProASIC3 nano devices were added to Table 1-1 • Flash-Based FPGAs.  Figure 1-2 • IGLOO and ProASIC3 nano Device Architecture Overview with Two I/O Banks (applies to 10 k and 30 k device densities, excluding IGLOO PLUS devices) through Figure 1-5 • IGLOO, IGLOO nano, ProASIC3 nano, and ProASIC3/L Device Architecture Overview with Four I/O Banks (AGL600 device is shown) are new.  Table 1-4 • IGLOO nano and ProASIC3 nano Array Coordinates is new.  The title of this document was changed from "Core Architecture of IGLOO and ProASIC3 Devices" to "FPGA Array Architecture in Low Power Flash Devices."  The "FPGA Array Architecture Support" section was revised to include new families and make the information more concise. | 10                                                                                                                                                                                                        |        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Banks (applies to 10 k and 30 k device densities, excluding IGLOO PLUS devices) through Figure 1-5 • IGLOO, IGLOO nano, ProASIC3 nano, and ProASIC3/L Device                                              | 11, 12 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Table 1-4 • IGLOO nano and ProASIC3 nano Array Coordinates is new.                                                                                                                                        | 17     |

| v1.3<br>(October 2008)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                           | 9      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                           | 10     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Table 1-2 • IGLOO and ProASIC3 Array Coordinates was updated to include Military ProASIC3/EL and RT ProASIC3 devices.                                                                                     | 16     |

| v1.2<br>(June 2008)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | The following changes were made to the family descriptions in Table 1-1 • Flash-Based FPGAs:  • ProASIC3L was updated to include 1.5 V.  • The number of PLLs for ProASIC3E was changed from five to six. | 10     |

| v1.1<br>(March 2008)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Table 1-1 • Flash-Based FPGAs and the accompanying text was updated to include the IGLOO PLUS family. The "IGLOO Terminology" section and "Device Overview" section are new.                              | 10     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | The "Device Overview" section was updated to note that 15 k devices do not support SRAM or FIFO.                                                                                                          | 11     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Figure 1-6 • IGLOO PLUS Device Architecture Overview with Four I/O Banks is new.                                                                                                                          | 13     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Table 1-2 • IGLOO and ProASIC3 Array Coordinates was updated to add A3P015 and AGL015.                                                                                                                    | 16     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Table 1-3 • IGLOO PLUS Array Coordinates is new.                                                                                                                                                          | 16     |

# 2 – Low Power Modes in ProASIC3/E and ProASIC3 nano FPGAs

## Introduction

The demand for low power systems and semiconductors, combined with the strong growth observed for value-based FPGAs, is driving growing demand for low power FPGAs. For portable and battery-operated applications, power consumption has always been the greatest challenge. The battery life of a system and on-board devices has a direct impact on the success of the product. As a result, FPGAs used in these applications should meet low power consumption requirements.

ProASIC® 3/E and ProASIC3 nano FPGAs offer low power consumption capability inherited from their nonvolatile and live-at-power-up (LAPU) flash technology. This application note describes the power consumption and how to use different power saving modes to further reduce power consumption for power-conscious electronics design.

## **Power Consumption Overview**

In evaluating the power consumption of FPGA technologies, it is important to consider it from a system point of view. Generally, the overall power consumption should be based on static, dynamic, inrush, and configuration power. Few FPGAs implement ways to reduce static power consumption utilizing sleep modes.

SRAM-based FPGAs use volatile memory for their configuration, so the device must be reconfigured after each power-up cycle. Moreover, during this initialization state, the logic could be in an indeterminate state, which might cause inrush current and power spikes. More complex power supplies are required to eliminate potential system power-up failures, resulting in higher costs. For portable electronics requiring frequent power-up and -down cycles, this directly affects battery life, requiring more frequent recharging or replacement.

SRAM-Based FPGA Total Power Consumption =  $P_{\text{static}} + P_{\text{dynamic}} + P_{\text{inrush}} + P_{\text{config}}$

EQ 1

ProASIC3/E Total Power Consumption = P<sub>static</sub> + P<sub>dynamic</sub>

EQ 2

Unlike SRAM-based FPGAs, Microsemi flash-based FPGAs are nonvolatile and do not require power-up configuration. Additionally, Microsemi nonvolatile flash FPGAs are live at power-up and do not require additional support components. Total power consumption is reduced as the inrush current and configuration power components are eliminated.

Note that the static power component can be reduced in flash FPGAs (such as the ProASIC3/E devices) by entering User Low Static mode or Sleep mode. This leads to an extremely low static power component contribution to the total system power consumption.

The following sections describe the usage of Static (Idle) mode to reduce the power component, User Low Static mode to reduce the static power component, and Sleep mode and Shutdown mode to achieve a range of power consumption when the FPGA or system is idle. Table 2-1 on page 22 summarizes the different low power modes offered by ProASIC3/E devices.

Table 2-1 • ProASIC3/E/nano Low Power Modes Summary

| Mode          | Power Supplies / Clock Status                                                                                                                                                                      | Needed to Start Up                                         |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|

| Active        | On – All, clock                                                                                                                                                                                    | N/A (already active)                                       |

|               | Off – None                                                                                                                                                                                         |                                                            |

| Static (Idle) | On – All                                                                                                                                                                                           | Initiate clock source.                                     |

|               | Off – No active clock in FPGA                                                                                                                                                                      | No need to initialize volatile contents.                   |

|               | Optional: Enter User Low Static (Idle) Mode by enabling ULSICC macro to further reduce power consumption by powering down FlashROM.                                                                |                                                            |

| Sleep         | On – VCCI                                                                                                                                                                                          | Need to turn on core.                                      |

|               | Off – VCC (core voltage), VJTAG (JTAG DC voltage), and VPUMP (programming voltage)                                                                                                                 | Load states from external memory.                          |

|               | LAPU enables immediate operation when power returns.                                                                                                                                               | As needed, restore volatile contents from external memory. |

|               | Optional: Save state of volatile contents in external memory.                                                                                                                                      |                                                            |

| Shutdown      | On – None                                                                                                                                                                                          | Need to turn on VCC, VCCI.                                 |

|               | Off – All power supplies                                                                                                                                                                           |                                                            |

|               | Applicable to all ProASIC3 nano devices, cold-sparing and hot-insertion allow the device to be powered down without bringing down the system. LAPU enables immediate operation when power returns. |                                                            |

## Static (Idle) Mode

In Static (Idle) mode, the clock inputs are not switching and the static power consumption is the minimum power required to keep the device powered up. In this mode, I/Os are only drawing the minimum leakage current specified in the datasheet. Also, in Static (Idle) mode, embedded SRAM, I/Os, and registers retain their values, so the device can enter and exit this mode without any penalty.

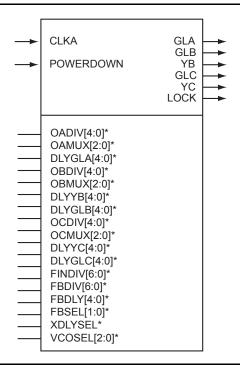

If the embedded PLLs are used as the clock source, Static (Idle) mode can be entered easily by pulling LOW the PLL POWERDOWN pin (active-low). By pulling the PLL POWERDOWN pin to LOW, the PLL is turned off. Refer to Figure 2-1 on page 23 for more information.

Figure 2-1 • CCC/PLL Macro

## **User Low Static (Idle) Mode**

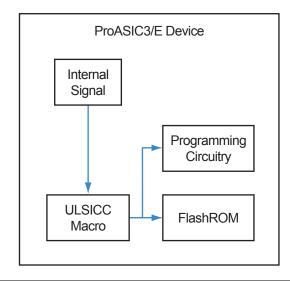

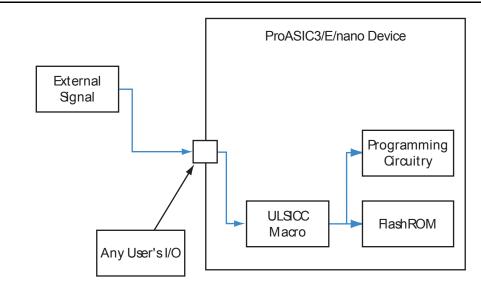

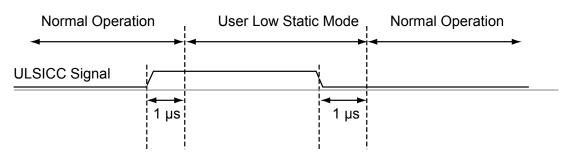

User Low Static (Idle) mode is an advanced feature supported by ProASIC3/E devices to reduce static (idle) power consumption. Entering and exiting this mode is made possible using the ULSICC macro by setting its value to disable/enable the User Low Static (Idle) mode. Under typical operating conditions, characterization results show up to 25% reduction of the static (idle) power consumption. The greatest power savings in terms of percentage are seen in the smaller members of the ProASIC3 family. The active-high control signal for User Low Static (Idle) mode can be generated by internal or external logic. When the device is operating in User Low Static (Idle) mode, FlashROM functionality is temporarily disabled to save power. If FlashROM functionality is needed, the device can exit User Low Static mode temporarily and re-enter the mode once the functionality is no longer needed.

To utilize User Low Static (Idle) mode, simply instantiate the ULSICC macro (Table 2-2 on page 24) in your design, and connect the input port to either an internal logic signal or a device package pin, as illustrated in Figure 2-2 on page 24 or Figure 2-3 on page 25, respectively. The attribute is used so the Synplify® synthesis tool will not optimize the instance with no output port.

This mode can be used to lower standard static (idle) power consumption when the FlashROM feature is not needed. Configuring the device to enter User Low Static (Idle) mode is beneficial when the FPGA enters and exits static mode frequently and lowering power consumption as much as possible is desired. The device is still functional, and data is retained in this state so the device can enter and exit this mode quickly, resulting in reduced total power consumption. The device can also stay in User Low Static mode when the FlashROM feature is not used in the device.

Table 2-2 • Using ULSICC Macro\*

| VHDL                    |             |              | Verilog                          |

|-------------------------|-------------|--------------|----------------------------------|

| COMPONENT ULSICC        |             |              | module ULSICC(LSICC);            |

| port (                  |             |              | input LSICC;                     |

|                         | : in        | STD_ULOGIC); | endmodule                        |

| END COMPONENT;          |             |              |                                  |

|                         |             |              | Example:                         |

| Example:                |             |              | ULSICC U1(.LSICC(myInputSignal)) |

| COMPONENT ULSICC        |             |              | /* synthesis syn_noprune=1 */;   |

| port (                  |             |              |                                  |

| LSICC                   | : in        | STD_ULOGIC); |                                  |

| END COMPONENT;          |             |              |                                  |

| attribute syn_noprune : | hooloan.    |              |                                  |

| attribute syn_noprune o | · ·         |              |                                  |

|                         |             |              |                                  |

| u1: ULSICC port map(myI | nputsignal) |              |                                  |

Note: \*Supported in Libero® software v7.2 and newer versions.

Figure 2-2 • User Low Static (Idle) Mode Application—Internal Control Signal

Figure 2-3 · User Low Static (Idle) Mode Application—External Control Signal

Figure 2-4 · User Low Static (Idle) Mode Timing Diagram

## **Sleep Mode**

ProASIC3/E and ProASIC3 nano FPGAs support Sleep mode when device functionality is not required. In Sleep mode, the VCC (core voltage), VJTAG (JTAG DC voltage), and VPUMP (programming voltage) are grounded, resulting in the FPGA core being turned off to reduce power consumption. While the ProASIC3/E device is in Sleep mode, the rest of the system is still operating and driving the input buffers of the ProASIC3/E device. The driven inputs do not pull up power planes, and the current draw is limited to a minimal leakage current.

Table 2-3 shows the status of the power supplies in Sleep mode. When a power supply is powered off, the corresponding power pin can be left floating or grounded.

Table 2-3 · Sleep Mode—Power Supply Requirements for ProASIC3/E/nano Devices

| Power Supplies | ProASIC3/E/nano Device |

|----------------|------------------------|

| VCC            | Powered off            |

| VCCI = VMV     | Powered on             |

| VJTAG          | Powered off            |

| VPUMP          | Powered off            |