Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# 36 V, 400 mA automotive synchronous step-down switching regulator

Datasheet - production data

### **Features**

- AEC-Q100 qualified

- · 400 mA DC output current

- 4.5 V to 36 V operating input voltage

- · Synchronous rectification

- Low consumption mode or low noise mode

- 75  $\mu$ A I<sub>O</sub> at light load (LCM V<sub>OUT</sub> = 3.3 V)

- 13 μA I<sub>Q-SHTDWN</sub>

- Adjustable f<sub>SW</sub> (250 kHz 600 kHz)

- Output voltage adjustable from 0.9 V

- No resistor divider required for 3.3 V V<sub>OUT</sub>

- V<sub>BIAS</sub> maximizes efficiency at light load

- · 350 mA valley current limit

- · Constant on-time control scheme

- PGOOD open collector

- Thermal shutdown

### **Applications**

- · Car body and ADAS applications (LCM)

- Car audio and low noise applications (LNM)

### **Description**

The A6984 is a step-down monolithic switching regulator able to deliver up to 400 mA DC. The output voltage adjustability ranges from 0.9 V. The fixed 3.3 V VOUT requires no external resistor divider. The "low consumption mode" (LCM) is designed for applications active during car parking, so it maximizes the efficiency at light load with controlled output voltage ripple. The "low noise mode" (LNM) makes the switching frequency almost constant over the load current range, serving low noise application specifications such as car audio/sensors. The PGOOD open collector output can implement output voltage sequencing during the power-up phase. The synchronous rectification, designed for high efficiency at medium-heavy load, and the high switching frequency capability make the size of the application compact. Pulse-by-pulse current sensing on the low-side power element implements effective constant current protection. The package lead finishing guarantees side solderability, thus allowing visual inspection during manufacturing.

# **Contents**

| 1 | Pin s | ettings                                                  |

|---|-------|----------------------------------------------------------|

|   | 1.1   | Pin connection                                           |

|   | 1.2   | Pin description                                          |

|   | 1.3   | Maximum ratings                                          |

|   | 1.4   | Thermal data                                             |

|   | 1.5   | ESD protection                                           |

| 2 | Elect | rical characteristics                                    |

| 3 | Datas | sheet parameters over the temperature range 10           |

| 4 | Devi  | ce description11                                         |

|   | 4.1   | Output voltage adjustment                                |

|   |       | 4.1.1 Maximum output voltage                             |

|   |       | 4.1.2 Leading network                                    |

|   | 4.2   | Control loop                                             |

|   | 4.3   | Optional virtual ESR network                             |

|   |       | Output voltage accuracy and optimized resistor divider23 |

|   | 4.4   | Soft-start 27                                            |

|   | 4.5   | Light load operation                                     |

|   |       | 4.5.1 Low noise mode (LNM)                               |

|   |       | 4.5.2 Low consumption mode (LCM)                         |

|   | 4.6   | Switchover feature 3                                     |

|   |       | 4.6.1 LCM                                                |

|   |       | 4.6.2 LNM                                                |

|   | 4.7   | Overcurrent protection 3                                 |

|   | 4.8   | PGOOD 33                                                 |

|   | 4.9   | Overvoltage protection                                   |

|   | 4.10  | Thermal shutdown 34                                      |

| 5 | Desig | gn of the power components                               |

|   | 5.1   | Input capacitor selection                                |

|   | 5.2   | Inductor selection                                       |

|   |       |                                                          |

| Δ | 6984 | 1 |

|---|------|---|

|   |      |   |

|    | 5.3    | Output capacitor selection                  |

|----|--------|---------------------------------------------|

|    |        | 5.3.1 Output voltage ripple                 |

|    |        | 5.3.2 COUT specification and loop stability |

| 6  | Appli  | ation board                                 |

| 7  | Effici | ncy curves                                  |

| 8  | Packa  | ge information                              |

|    | 8.1    | VFDFPN10 4 x 4 x 1.0 mm package information |

| 9  | Orde   | ng information 46                           |

| 10 | Revis  | on history                                  |

Pin settings A6984

# 1 Pin settings

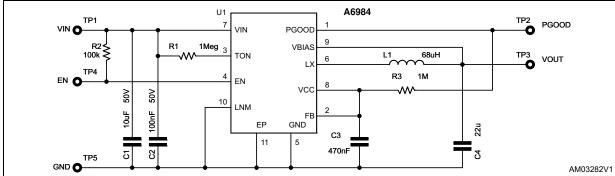

### 1.1 Pin connection

Figure 2. Pin connection (top view)

### 1.2 Pin description

Table 1. Pin description

| N° | Pin   | Description                                                                                                                                                                                                                                                                                                                                          |

|----|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1  | PGOOD | The open collector output is driven low when the FB voltage is below the $V_{PGD\ L}$ threshold (see <i>Table 5</i> ).                                                                                                                                                                                                                               |

| 2  | FB    | Inverting input of the error amplifier                                                                                                                                                                                                                                                                                                               |

| 3  | TON   | A resistor connected between this pin and V <sub>IN</sub> sets the switching frequency.                                                                                                                                                                                                                                                              |

| 4  | EN    | Enable pin. A logical active high signal enables the device. Connect this pin to $V_{\text{IN}}$ if not used.                                                                                                                                                                                                                                        |

| 5  | GND   | Power GND                                                                                                                                                                                                                                                                                                                                            |

| 6  | LX    | Switching node                                                                                                                                                                                                                                                                                                                                       |

| 7  | VIN   | DC input voltage                                                                                                                                                                                                                                                                                                                                     |

| 8  | VCC   | Embedded regulator output that supplies the main switching controller. Connect an external 1 $\mu$ F capacitor for proper operation. An integrated LDO regulates VCC = 3.3 V if VBIAS voltage is < 2.4 V. VCC is connected to VBIAS through a MOSFET switch if VBIAS > 3.2 V and the embedded LDO is disabled to increase the light load efficiency. |

| 9  | VBIAS | Typically connected to the regulated output voltage. An external voltage reference can be used to supply the analog circuitry to increase the efficiency at light load. Connect to GND if not used.                                                                                                                                                  |

| 10 | LNM   | Connect to V <sub>CC</sub> for low noise mode (LNM) / to GND for low consumption mode (LCM) operation.                                                                                                                                                                                                                                               |

A6984 Pin settings

### 1.3 Maximum ratings

Stressing the device above the rating listed in *Table 2: Absolute maximum ratings* may cause permanent damage to the device.

These are stress ratings only and operation of the device at these or any other conditions above those indicated in *Table 5* of this specification is not implied.

Exposure to absolute maximum rating conditions may affect device reliability.

Table 2. Absolute maximum ratings

| Symbol                              | Description                             | Min. | Max.                  | Unit |

|-------------------------------------|-----------------------------------------|------|-----------------------|------|

| dV <sub>IN</sub> /dt <sup>(1)</sup> | Input slew rate                         |      | 0.1                   | V/µs |

| V <sub>IN</sub>                     | -                                       |      | 38                    |      |

| LX                                  | device ON                               |      | V <sub>IN</sub> + 0.3 |      |

| LX                                  | device OFF                              |      | 25                    |      |

| EN                                  |                                         |      | V <sub>IN</sub> + 0.3 |      |

| TON                                 |                                         | -0.3 | -                     | V    |

| V <sub>CC</sub>                     |                                         | 0.0  | 6                     |      |

| $V_{BIAS}$                          | see <i>Table 1</i>                      |      | ŭ .                   |      |

| PGOOD                               |                                         |      |                       |      |

| FB                                  |                                         |      | V <sub>CC</sub> + 0.3 |      |

| LNM                                 |                                         |      |                       |      |

| T <sub>J</sub>                      | Operating temperature range             | -40  | 150                   |      |

| T <sub>STG</sub>                    | Storage temperature range               | -    | -55 to 150            | °C   |

| T <sub>LEAD</sub>                   | Lead temperature (soldering 10 sec.)    | -    | 260                   |      |

| I <sub>HS</sub> , I <sub>LS</sub>   | High-side / low-side RMS switch current | -    | 400                   | mA   |

<sup>1.</sup> Maximum slew rate should be limited as detailed in Section 5.1.

### 1.4 Thermal data

Table 3. Thermal data

| Symbol             | Parameter                                                                                    | Value | Unit |

|--------------------|----------------------------------------------------------------------------------------------|-------|------|

| R <sub>th JA</sub> | Thermal resistance junction ambient (device soldered on STMicroelectronics evaluation board) | 50    | °C/W |

Pin settings A6984

# 1.5 ESD protection

Table 4. ESD protection

| Symbol | Test condition | Value | Unit |

|--------|----------------|-------|------|

| ESD    | НВМ            | 2     | KV   |

|        | MM             | 200   | V    |

|        | CDM            | 500   | V    |

### 2 Electrical characteristics

$T_J$  = -40 to 125 °C,  $V_{IN}$  =  $V_{EN}$  = 12 V,  $V_{BIAS}$  = 3.3 V unless otherwise specified.

**Table 5. Electrical characteristics**

| Symbol               | Parameter                                   | Test condition                                   |     | Min. | Тур. | Max. | Unit |

|----------------------|---------------------------------------------|--------------------------------------------------|-----|------|------|------|------|

| V <sub>IN</sub>      | Operating input voltage range               |                                                  | -   | 4.5  |      | 36   |      |

|                      |                                             | Rising edge $V_{CC}$ regulator $V_{BIAS} = GND$  | -   | 3.1  | 3.8  | 4.5  |      |

| V <sub>IN_UVLO</sub> | UVLO thresholds                             | Falling edge $V_{CC}$ regulator $V_{BIAS} = GND$ | -   | 2.9  | 3.6  | 4.3  | V    |

| V <sub>OUT</sub>     | Fixed output voltage valley regulation      | FB = V <sub>CC</sub> , no load                   | -   | 3.23 | 3.3  | 3.37 |      |

| V <sub>FB</sub>      | Adjustable output voltage valley regulation | No load                                          | -   | 0.88 | 0.9  | 0.92 |      |

| R <sub>DSON HS</sub> | High-side RDSON                             | I <sub>SW</sub> = 0.1 A                          | -   | 0.6  | 1.3  | 2.2  | Ω    |

| R <sub>DSON LS</sub> | Low-side RDSON                              | I <sub>SW</sub> = 0.1 A                          | -   | 0.4  | 1.0  | 1.9  | 2.2  |

| T <sub>OFF</sub>     | Minimum Low-side conduction time            | V <sub>IN</sub> = V <sub>EN</sub> = 4.5 V        | -   | 100  | 200  | 400  | ns   |

| Current lin          | nit and zero crossing comparat              | or                                               |     | •    | •    |      |      |

| I <sub>VY</sub>      | Valley current limit                        | -                                                | -   | 350  | 400  | 470  | ^    |

| I <sub>ZCD</sub>     | Zero crossing current threshold             | -                                                | (1) | 12   | 27   | 46   | mA   |

| VCC regula           | ator                                        |                                                  | •   |      | •    |      | •    |

| V <sub>CC</sub>      | VCC voltage                                 | V <sub>FB</sub> = 1 V, V <sub>BIAS</sub> = GND   | -   | 3    | 3.8  | 4.6  |      |

| V                    | V <sub>BIAS</sub> falling threshold         | -                                                | -   | 2.4  | 2.6  | 2.8  | ٧    |

| $V_{BIAS}$           | V <sub>BIAS</sub> rising threshold          | -                                                | -   | 2.6  | 2.9  | 3.2  |      |

| Power con            | sumption                                    |                                                  | •   |      |      | •    | •    |

| I <sub>SHTDWN</sub>  | Shutdown current from V <sub>IN</sub>       | EN = GND                                         | -   | 3    | 13   | 22   | μΑ   |

Electrical characteristics A6984

Table 5. Electrical characteristics (continued)

| Symbol             | Parameter                                              | Test condition                                                                                                                                                                                                       |     | Min. | Тур. | Max. | Unit  |

|--------------------|--------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|------|------|-------|

|                    |                                                        | $\label{eq:controller} \begin{split} & \textbf{LCM - SWO} \\ & V_{REF} < V_{FB} < V_{OVP} \text{ (SLEEP)} \\ & V_{BIAS} = 3.3 \text{ V} \end{split}$                                                                 | (2) | 11   | 26   | 41   | -     |

|                    |                                                        | $\begin{aligned} & \textbf{LCM - NO SWO} \\ & \textbf{V}_{REF} < \textbf{V}_{FB} < \textbf{V}_{OVP} \text{ (SLEEP)} \\ & \textbf{V}_{BIAS} = \textbf{GND} \end{aligned}$                                             | (2) | 90   | 160  | 230  |       |

| IQ OPVIN           | Quiescent current from V <sub>IN</sub>                 | $\label{eq:local_local_local_local} \begin{split} & \textbf{LNM - SWO} \\ & \textbf{V}_{\text{REF}} < \textbf{V}_{\text{FB}} < \textbf{V}_{\text{OVP}} \\ & \textbf{V}_{\text{BIAS}} = 3.3 \ \textbf{V} \end{split}$ | -   | 11   | 26   | 42   |       |

|                    |                                                        | LNM - NO SWO $V_{REF} < V_{FB} < V_{OVP}$ $V_{BIAS} = GND$                                                                                                                                                           | -   | 200  | 320  | 440  | μΑ    |

|                    | Outliness at a surround from V                         | $\begin{aligned} & \textbf{LCM - SWO} \\ & \textbf{V}_{\text{REF}} < \textbf{V}_{\text{FB}} < \textbf{V}_{\text{OVP}} \text{ (SLEEP)} \\ & \textbf{V}_{\text{BIAS}} = 3.3 \text{ V} \end{aligned}$                   | (2) | 80   | 150  | 200  |       |

| IQ OPVBIAS         | Quiescent current from V <sub>BIAS</sub>               | $\begin{aligned} & \textbf{LNM - SWO} \\ & \textbf{V}_{\text{REF}} < \textbf{V}_{\text{FB}} < \textbf{V}_{\text{OVP}} \\ & \textbf{V}_{\text{BIAS}} = 3.3 \text{ V} \end{aligned}$                                   | -   | 180  | 300  | 390  |       |

| Enable             |                                                        |                                                                                                                                                                                                                      |     |      |      | •    | •     |

|                    | EN thresholds                                          | Device inhibited                                                                                                                                                                                                     | -   | 1.1  | -    | -    | V     |

| EN                 |                                                        | Device enabled                                                                                                                                                                                                       | -   | -    | -    | 2.6  | \ \ \ |

|                    | EN hysteresis                                          | -                                                                                                                                                                                                                    | (3) | -    | 650  | -    | mV    |

| Overvoltag         | ge protection                                          |                                                                                                                                                                                                                      |     |      | •    |      | •     |

| V <sub>OVP</sub>   | Overvoltage trip (V <sub>OVP</sub> /V <sub>REF</sub> ) | Rising edge                                                                                                                                                                                                          |     | 18   | 23   | 28   | %     |

| PGOOD              |                                                        |                                                                                                                                                                                                                      | ı   | I.   | 1    |      |       |

| V                  | Dower good I OWI throubold                             | V <sub>FB</sub> rising edge<br>(PGOOD high impedance)                                                                                                                                                                | (3) | -    | 90   | -    |       |

| V <sub>PGD L</sub> | Power good LOW threshold                               | V <sub>FB</sub> falling edge<br>(PGOOD low impedance)                                                                                                                                                                | -   | 84   | 88   | 92   |       |

| Vacau              | Power good HIGH threshold                              | Internal FB rising edge<br>(PGOOD low impedance)<br>V <sub>FB</sub> = V <sub>CC</sub>                                                                                                                                | -   | 118  | 123  | 128  | %     |

| V <sub>PGD H</sub> |                                                        | Internal FB falling edge (PGOOD high impedance) $V_{FB} = V_{CC}$                                                                                                                                                    | (3) | -    | 100  | -    |       |

| V <sub>PGOOD</sub> | PGOOD open collector output                            | V <sub>IN</sub> > V <sub>IN_UVLO_H</sub> ,<br>V <sub>FB</sub> =GND<br>4 mA sinking load                                                                                                                              | -   | -    | -    | 0.6  | V     |

|                    |                                                        | 2.9 < V <sub>IN</sub> < V <sub>IN_UVLO_H</sub><br>100 μA sinking load                                                                                                                                                | -   | -    | -    | 0.6  | ٧     |

Table 5. Electrical characteristics (continued)

| Symbol             | Parameter                    | Test condition |     | Min. | Тур. | Max. | Unit |

|--------------------|------------------------------|----------------|-----|------|------|------|------|

| Thermal sl         | Thermal shutdown             |                |     |      |      |      |      |

| T <sub>SHDWN</sub> | Thermal shutdown temperature | -              | (3) | -    | 150  | -    | °C   |

| T <sub>HYS</sub>   | Thermal shutdown hysteresis  | -              | (3) | -    | 20   | -    | °C   |

- 1. Parameter tested in static condition during testing phase. Parameter value may change over dynamic application condition.

- 2. LCM enables SLEEP mode (part of the internal circuitry is disabled) at light load.

- 3. Not tested in production.

### 3 Datasheet parameters over the temperature range

100% of the population in the production flow is tested at three different ambient temperatures (-40 °C; 25 °C, 125 °C) to guarantee datasheet parameters within the junction temperature range (-40 °C to 125 °C).

Device operation is guaranteed when the junction temperature is within the -40 °C to 150 °C temperature range. The designer can estimate the silicon temperature increase with respect to the ambient temperature evaluating the internal power losses generated during the device operation.

However, the embedded thermal protection disables the switching activity to protect the device in case the junction temperature reaches the  $T_{SHTDWN}$  (+150 °C min) temperature.

All the datasheet parameters can be guaranteed to a maximum junction temperature of +125 °C to avoid triggering the thermal shutdown protection during the testing phase due to self-heating.

10/49 DocID030396 Rev 3

### 4 Device description

The A6984 device is based on a "Constant On-Time" (COT) control scheme with frequency feed-forward correction over the  $V_{\rm IN}$  range. As a consequence the device features fast load transient response, almost constant switching frequency operation over the input voltage range and simple stability control.

The switching frequency can be adjusted in the 250 kHz - 600 kHz range.

The LNM (low noise mode) implements constant PWM control to minimize the voltage ripple over the load range, the LCM (low consumption mode) pulse skipping technique to increase the efficiency at the light load.

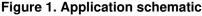

No external resistor divider is required to regulate fixed 3.3 V output voltage, connecting FB to the  $V_{CC}$  pin and  $V_{BIAS}$  to the regulated output voltage (see *Figure 1 on page 1*). An external voltage divider implements the output voltage adjustability.

The switchover capability of the internal regulator derives a portion of the quiescent current from an external voltage source (V<sub>BIAS</sub> pin is typically connected to the regulated output voltage) to maximize the efficiency at the light load.

The device main internal blocks are shown in the block diagram in Figure 6 on page 15:

- The bandgap reference voltage

- The on-time controller

- A "pulse width modulation" (PWM) comparator and the driving circuitry of the embedded power elements

- The SMPS controller block

- The soft-start block to ramp the current limitation

- The switchover capability of the internal regulator to supply a portion of the quiescent current when the VBIAS pin is connected to an external output voltage

- The current limitation circuit to implement the constant current protection, sensing pulse-by-pulse low-side switch current.

- A circuit to implement the thermal protection function

- LNM pin strapping sets the LNM/LCM mode

- The PG ("Power Good") open collector output

- The thermal protection circuitry

Device description A6984

VIN STARTUP VOLTAGE VCC\_ENABLE VCC internal regulator output COMPARATOR vcc AND VCC GENERATOR VBIAS rising threshold SWITCH **♦∨віаѕ** PGOOD LOW/SIDE PWM\_COMP\_OUT GND VCC VIN **VBIAS** HIGH-SIDE MOS **HGATE** LEVEL SHIFTER FΒ FB ( SELECTOR SMPS TON TON ( LX **GENERATOR** CONTROLLER VCC

LGATE

LOW-SIDE MOS

Figure 3. A6984 block diagram

CO25949

LNM 🔵

GND 🔷

#### 4.1 Output voltage adjustment

No external resistor divider is required to regulate fixed 3.3 V output voltage, connecting FB to the  $V_{CC}$  pin and  $V_{BIAS}$  to the regulated output voltage (see *Figure 1 on page 1*). An external voltage divider otherwise implements the output voltage adjustability.

A6984 U1 TP1 **PGOOD** VIN O VIN PGOOD 1Meg <sub>3</sub> R1 **VBIAS** 100k L1 68uH TON LX R3 1M ΕN VCC 50 50 LNM 100hF FΒ GND ΕP 22 470nF TP5 GND AM03728

Figure 4. Internal voltage divider for 3.3 V output voltage

The error amplifier reference voltage is 0.9 V typical.

The output voltage is adjusted accordingly with the following formula (see *Figure 6*):

#### **Equation 1**

$$V_{OUT} = 0.9 \cdot \left(1 + \frac{R_3}{R_2}\right)$$

#### 4.1.1 Maximum output voltage

The constant on-time control scheme naturally requires a minimum cycle-by-cycle off time to sense the feedback voltage and properly driving the switching activity.

The A6984 minimum off time, as reported in Table 2 on page 5, is 300 nsec typical and 400 nsec max.

The control loop generates the proper PWM signal to regulate the programmed output voltage over the application conditions. Since the power losses are proportional to the delivered output power, the duty cycle increases with the load current request.

The fixed minimum off time limits the maximum duty cycle, so the maximum output voltage, depending on the selected switching frequency (see Section 4.2).

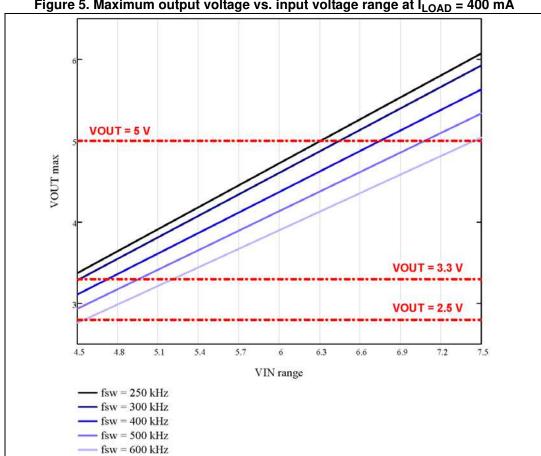

Figure 5 shows the worst case scenario for maximum output voltage limitation over the input voltage range, that happens at the maximum current request and considering the upper datasheet limit time for the minimum off time parameter.

#### Figure 5. Maximum output voltage vs. input voltage range at I<sub>LOAD</sub> = 400 mA

#### 4.1.2 Leading network

The small signal contribution of a simple voltage divider is:

### **Equation 2**

$$G_{DIV}(s) = \frac{R_2}{R_2 + R_3}$$

A small signal capacitor in parallel to the upper resistor (see C3 in Figure 6) of the voltage divider implements a leading network ( $f_{zero} < f_{pole}$ ) that can improve the dynamic regulation for boundary application conditions (high f<sub>SW</sub> / high duty cycle conversion) and improves the SNR for the feedback comparator operation, entirely coupling the high frequency output voltage ripple without the resistive divider attenuation.

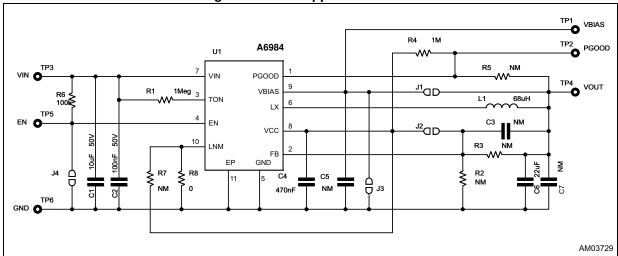

Figure 6. A6984 application circuit

Laplace transformer of the leading network:

#### **Equation 3**

$$\mathsf{G}_{\mathsf{DIV}}(\mathsf{s}) = \frac{\mathsf{R}_2}{\mathsf{R}_2 + \mathsf{R}_3} \cdot \frac{(1 + \mathsf{s} \cdot \mathsf{R}_3 \cdot \mathsf{C}_{\mathsf{R}3})}{\left(1 + \mathsf{s} \cdot \frac{\mathsf{R}_2 \cdot \mathsf{R}_3}{\mathsf{R}_2 + \mathsf{R}_3} \cdot \mathsf{C}_{\mathsf{R}3}\right)}$$

where:

#### **Equation 4**

$$\begin{split} f_Z &= \frac{1}{2 \cdot \pi \cdot R_3 \cdot C_{R3}} \\ f_P &= \frac{1}{2 \cdot \pi \cdot \frac{R_2 \cdot R_3}{R_2 + R_3} \cdot C_{R3}} \\ f_Z &< f_P \end{split}$$

The R2, R3 compose the voltage divider.  $C_{R3}$  is calculated as (see *Section 5.3.2: COUT specification and loop stability on page 39* for  $C_{OUT}$  selection):

#### **Equation 5**

$$C_{R3} = 28 \cdot 10^{-3} \cdot \frac{V_{OUT} \cdot C_{OUT}}{R_3}$$

#### 4.2 Control loop

The A6984 device is based on a constant on-time control loop with frequency feed-forward correction over the input voltage range. As a consequence the on-time generator compensates the input voltage variations in order to adapt the duty cycle and so keeping the switching frequency almost constant over the input voltage range.

The general constraint for converters based on the COT architecture is the selection of the output capacitor with an ESR high enough to guarantee a proper output voltage ripple for the noiseless operation of the internal PWM comparator. The A6984 innovative control loop otherwise supports the output ceramic capacitors with the negligible ESR.

The device generates a T<sub>ON</sub> duration switching pulse as soon as the voltage ripple drops below the valley voltage threshold.

The A6984 on-time is internally generated as shown in *Figure 7*.

RTON **LOGIC** TON □ IN 0.9 V CEXT **CPAR** CINT OUT GND

Figure 7. T<sub>ON</sub> generator

where R<sub>TON</sub> represents the external resistor connected between the V<sub>IN</sub> and T<sub>ON</sub> pins, C<sub>INT</sub> is the integrated capacitor, CPAR the pin parasitic capacitor of the board trace at the pin 3.

The overall contribution of the C<sub>PAR</sub> and C<sub>INT</sub> for the A6984 device soldered on the STMicroelectronics evaluation board is 7.5 pF typical but the precise value depends on the parasitic capacitance connected at the pin 3 (TON) that may depend on the implemented board layouts.

As a consequence, a further fine tune of the R<sub>TON</sub> value with the direct scope measurement is required for precise f<sub>SW</sub> adjustment accordingly with the designed board layout.

The ON time can be calculated as:

#### **Equation 6**

16/49

$$T_{ON} = \frac{0.9 \cdot R_{TON} \cdot C_{TON}}{V_{IN}} = \frac{0.9 \cdot R_{TON} \cdot (C_{INT} + C_{PAR})}{V_{IN}} \cong \frac{0.9 \cdot R_{TON} \cdot 7.5pF}{V_{IN}}$$

The natural feedforward of the generator in Figure 7 corrects the fixed T<sub>ON</sub> time with the input voltage to achieve almost constant switching frequency over the input voltage range.

On the other hand, the PWM comparator (see Figure 3 on page 12) in the closed loop operation modulates the T<sub>OFF</sub> time, given the programmed T<sub>ON</sub>, to compensate conversion losses (i.e. conduction, switching, inductor losses, etc.) that are proportional to the output current.

> 77/ DocID030396 Rev 3

As a consequence the switching frequency slightly depends on the conversion losses:

#### **Equation 7**

$$f_{SW}(I_{OUT}) = \frac{D_{REAL}(I_{OUT})}{T_{ON}}$$

where  $D_{REAL}$  is the real duty cycle accounting conduction losses:

#### **Equation 8**

$$D_{REAL}(I_{OUT}) = \frac{V_{OUT} + (R_{ON\_LS} + DCR) \cdot I_{OUT}}{V_{IN} + (R_{ON} L_S - R_{ON} H_S) \cdot I_{OUT}}$$

$R_{ON\_HS}$  and  $R_{ON\_LS}$  represent the RDSON value of the embedded power elements (see *Table 5 on page*  $\overline{7}$ ) and DCR the equivalent series resistor of the selected inductor.

Finally from Equation 7 and Equation 8:

#### **Equation 9**

$$R_{TON} = \frac{1}{0.9} \cdot \frac{V_{IN} \cdot D_{REAL}(I_{OUT})}{f_{SW} \cdot C_{TON}}$$

where  $f_{SW}$  is the desired switching frequency at a certain  $I_{OUT}$  load current level.

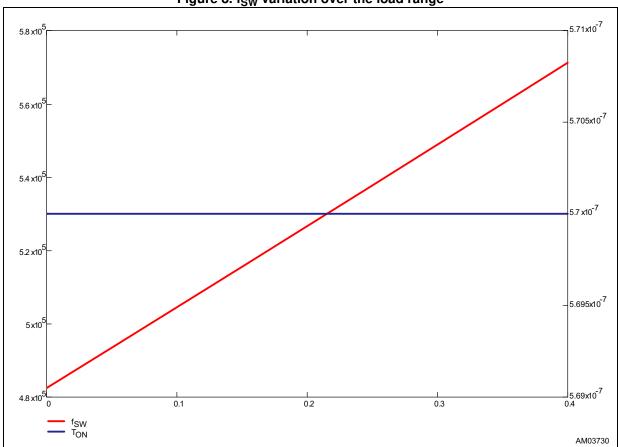

Figure 8 shows the estimated  $f_{SW}$  variation over the load range assuming the typical RDSON of the power elements, DCR = 420 m $\Omega$  (see Section 6 on page 40 for details on the selected inductor for the reference application board.) and  $R_{TON}$  = 1 M.

Figure 8. f<sub>SW</sub> variation over the load range

A general requirement for applications compatible with humid environments, is to limit the maximum resistor value to minimize the resistor variation determined by the leakage path.

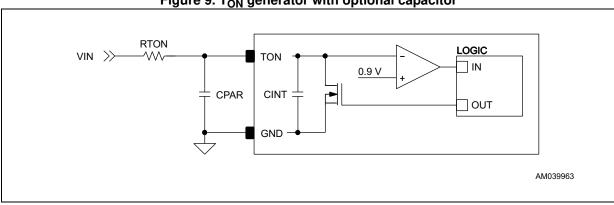

An optional external capacitor C<sub>TON</sub> >> (C<sub>INT</sub> + C<sub>PAR</sub>) connected as shown in *Figure 9* helps to limit the R<sub>TON</sub> value and also minimizes the f<sub>SW</sub> variation with the p.c.b. parasitic components C<sub>PAR</sub>.

Figure 9. T<sub>ON</sub> generator with optional capacitor

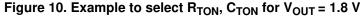

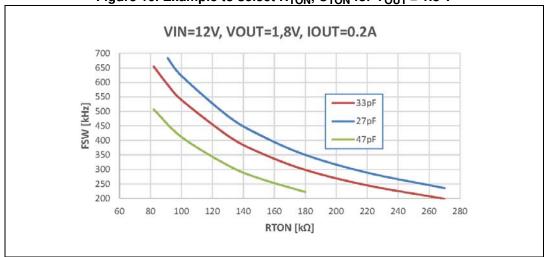

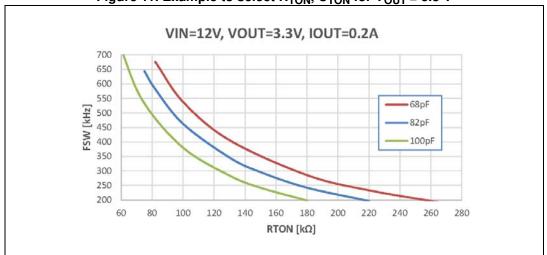

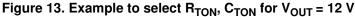

Figure 10, Figure 11, Figure 12, and Figure 13 show the numeric example to program the switching frequency accordingly with the R<sub>TON</sub>, C<sub>TON</sub> pair selection.

The eDesignSuite online tool supports the A6984 and  $R_{TON}$ ,  $C_{TON}$  dimensioning for proper switching frequency selection, see

http://www.st.com/content/st\_com/en/support/resources/edesign.html).

Figure 11. Example to select  $R_{TON}$ ,  $C_{TON}$  for  $V_{OUT} = 3.3 \text{ V}$

Device description A6984

Figure 12. Example to select  $R_{TON}$ ,  $C_{TON}$  for  $V_{OUT} = 5 V$

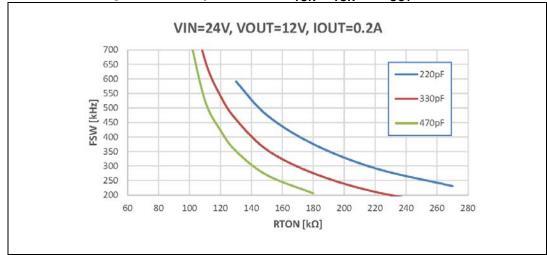

### 4.3 Optional virtual ESR network

A standard COT loop requires a high ESR output capacitor to generate a proper PWM signal.

The A6984 architecture naturally supports output ceramic capacitors with the negligible ESR generating an internal voltage ramp proportional to the inductor current to emulate a high ESR output capacitor for the proper PWM comparator operation.

The control scheme is designed to guarantee the minimum signal for the PWM comparator cycle-by-cycle operation with controlled duty cycle jitter, that is a natural duty cycle dithering that helps to reduce the switching noise emission for EMC.

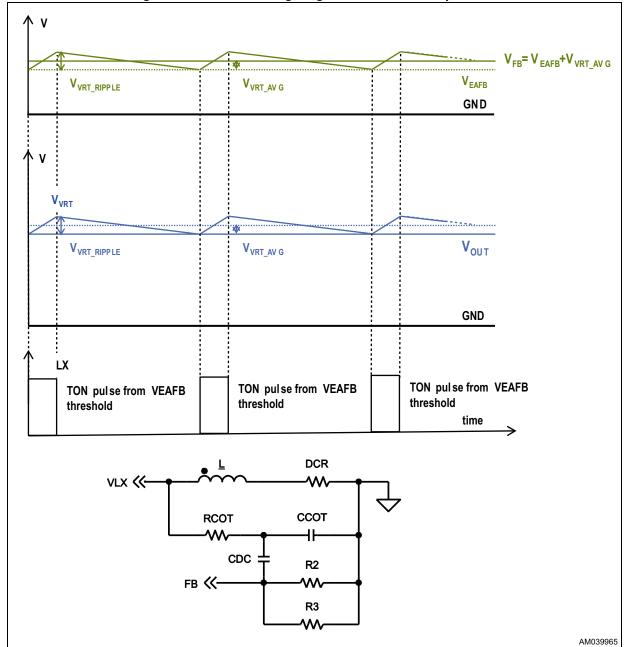

If required, an optional external virtual ESR network (see *Figure 14* can be designed to generate a higher signal for the PWM comparator operation and remove the duty cycle dithering. This network requires the external voltage divider to set the output voltage and supports the LNM and LCM device operation.

A6984 7 VIN PGOOD RTON **VBIAS** 3 **Φ** TON L LX RCOT CCOT ΕN VCC ₩ 20 \ 10 CDC LNM FB 10 µF GND •VOUT CTON CVCC 0 Ω R2 COUT GND O AM039968

Figure 14. Virtual ESR network

The  $C_{DC}$  capacitor decouples the feedback DC path through the  $R_{COT}$  so the output voltage is adjusted accordingly with Section 4.1 on page 13.

Basically the network  $R_{COT}$ ,  $C_{COT}$  generates a voltage signal proportional to the inductor current ripple and superimposed with the real partitioned output voltage that increases the SNR at the input of the PWM comparator. As a consequence the PWM converter commutation is clean, removing the duty cycle dithering.

For the purpose of the signal generated by the  $R_{COT}$  and  $C_{COT}$  the output capacitor represents a virtual ground so the equivalent small signal circuit of the output of the virtual ESR network is shown in *Figure 15*.

Figure 15. Virtual ESR equivalent circuit

Device description A6984

The switching activity drives the inductor voltage so the small signal transfer function can be calculated as:

#### **Equation 10**

$$H(s) = \frac{vFB(s)}{iL(s)} = \frac{(s \cdot L + DCR)}{R_{COT} + \frac{1}{s \cdot C_{COT}} + \frac{1}{\frac{1}{s \cdot C_{DC}} + \frac{1}{\frac{1}{R_2} + \frac{1}{R_3}}} \cdot \frac{1}{s \cdot C_{COT} + \frac{1}{\frac{1}{s \cdot C_{DC}}} + \frac{1}{\frac{1}{R_2} + \frac{1}{R_3}}} \cdot \frac{\frac{1}{\frac{1}{R_2} + \frac{1}{R_3}}}{\frac{1}{s \cdot C_{DC}} + \frac{1}{\frac{1}{R_2} + \frac{1}{R_3}}} \cdot \frac{\frac{1}{\frac{1}{R_2} + \frac{1}{R_3}}}{\frac{1}{s \cdot C_{DC}} + \frac{1}{\frac{1}{R_2} + \frac{1}{R_3}}}$$

Equation 10 can be simplified as follows:

#### **Equation 11**

$$H(s) = \frac{vFB(s)}{iL(s)} = \frac{(s \cdot L + DCR) \cdot s}{\left[1 + s \cdot \left(\frac{1}{R_2} + \frac{1}{R_3}\right) \cdot C_{DC}\right] \cdot \left[1 + s \cdot \left(\frac{1}{\frac{1}{R_2} + \frac{1}{R_3} + \frac{1}{R_{COT}}}\right) \cdot C_{COT}\right]} \cdot \frac{\frac{C_{DC}}{\frac{1}{R_2} + \frac{1}{R_3}}}{\frac{1}{R_2} + \frac{1}{R_3}}$$

The pole splitting is guaranteed by the condition:

#### **Equation 12**

$$C_{DC} > 10 \cdot C_{COT}$$

$$R_{COT} > 10 \cdot \left(\frac{R_2 x R_3}{R_2 + R_3}\right)$$

In case:

#### **Equation 13**

$$\begin{split} f_z &= \frac{1}{2 \cdot \pi} \cdot \frac{L}{DCR} \cdot \text{fsw} \\ f_{PL} &= \frac{1}{2 \cdot \pi \cdot R_{COT} + \frac{1}{\frac{1}{R_2} + \frac{1}{R_3}} \cdot C_{DC}} \cdot \text{fsw} \\ f_{PH} &= \frac{1}{2 \cdot \pi \cdot \left(\frac{1}{\frac{1}{R_2} + \frac{1}{R_3} + \frac{1}{R_{COT}}}\right) \cdot C_{COT}} \cdot \text{fsw} \end{split}$$

Equation 10 can be simplified as:

### **Equation 14**

$$\mathsf{ESR}_{\mathsf{VRT}} = \left. \mathsf{H(s)}_{\mathsf{S} \,\rightarrow\, (2 \,\cdot\, \pi \,\cdot\, \mathsf{fsw})} \, = \left( \frac{\mathsf{vFB(s)}}{\mathsf{iL(s)}} \right)_{\mathsf{S} \,\rightarrow\, (2 \,\cdot\, \pi \,\cdot\, \mathsf{fsw})} = \frac{\mathsf{L}}{\mathsf{R}_{\mathsf{COT}} \cdot \mathsf{C}_{\mathsf{COT}}}$$

which represents the virtual ESR of the network in Figure 14.

Device description A6984

As a consequence, the injected triangular voltage ripple in the FB is:

#### **Equation 15**

$$\mathsf{VFB}_{\mathsf{RIPPLE}}\left(\mathsf{V}_{\mathsf{IN}}\right) \ = \ \mathsf{IL}_{\mathsf{RIPPLE}} \cdot \mathsf{ESR}_{\mathsf{VRT}} \ = \ \frac{\mathsf{V}_{\mathsf{IN}} - \mathsf{V}_{\mathsf{OUT}}}{\mathsf{R}_{\mathsf{COT}} \cdot \mathsf{C}_{\mathsf{COT}}} \cdot \frac{\mathsf{V}_{\mathsf{OUT}}}{\mathsf{V}_{\mathsf{IN}}} \cdot \frac{\mathsf{1}}{\mathsf{fsw}}$$

that does not depend on the R<sub>2</sub>, R<sub>3</sub>, C<sub>DC</sub>, L and DCR.

A virtual ESR network able to guarantee a peak-to-peak signal higher than 20 mV at the FB pin removes any duty cycle dithering at the switching node.

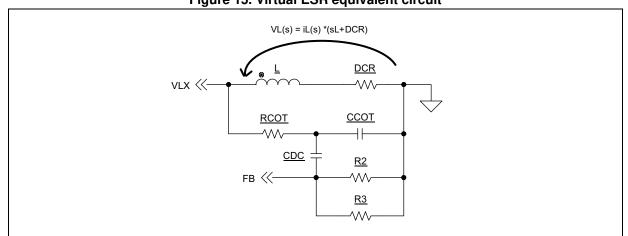

### Output voltage accuracy and optimized resistor divider

The constant on-time control scheme implements valley output voltage regulation: the internal comparator monitors the FB voltage cycle-by-cycle and generates a fixed  $T_{ON}$  pulse if the sensed voltage drops below the internal voltage reference ( $V_{EAFB} = 0.9 \text{ V}$  typical).

The virtual ESR network generates a signal proportional to the inductor current that is AC coupled to the FB pin through the  $C_{DC}$  capacitor (refer to Section 4.3 for dimensioning rules) and superimposed on the voltage divider contribution as shown in Figure 16.

24/49 DocID030396 Rev 3

Figure 16. Virtual ESR signal generation in CCM operation