Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

### Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

#### AB-RTCMC-32.768kHz-B5ZE-S3

#### Moisture Sensitivity Level: MSL=1

#### FEATURES:

- With state-of-the-art RTC Technology by Micro Crystal AG

- RTC module with built-in crystal oscillating at 32.768 kHz

- 1 MHz Fast-mode Plus (Fm+) two-wire I2C interface

- Wide Interface operating voltage: 1.6 5.5 V

- Wide clock operating voltage: 1.2 5.5 V

- Ultra low power consumption: 130 nA typ @ 3.0V / 25°C

- Provides year, month, day, weekday, hours, minutes, seconds

- Freely programmable Alarm and Timer functions with interrupt capability

- Low voltage detector, internal power on reset

- Battery backup input pin and switch-over circuit

- INT 1 can be programmed either as interrupt or clock output (open-drain)

- Programmable clock output for peripheral devices (32.768 kHz, 16.384 kHz, 8192 Hz, 4096 Hz, 1024 Hz, 32 Hz and 1 Hz)

- Programmable offset register for frequency adjustment

- I2C slave address: read D1h, write D0h

- Small and compact package size: 3.7 x 2.5 x 0.9 mm. RoHS-compliant and 100% leadfree

# **RoHS/RoHS II compliant**

3.7 x 2.5 x 0.9 mm

#### **APPLICATIONS:**

- Wide range in communication & measuring equipment

- Commercial & Industrial applications

- Automotive electronics applications

- Wireless communications

- PDA and Palm Pilots

- · Credit Cards with Security Technology

#### > STANDARD SPECIFICATIONS:

#### **Absolute Maximum Ratings**

| Parameters                                      | Min. | Тур. | Max. | Units | Notes                  |

|-------------------------------------------------|------|------|------|-------|------------------------|

| Supply Voltage (V <sub>DD</sub> )               | -0.5 |      | +6.5 | V     |                        |

| Battery Supply voltage (V <sub>BACKUP</sub> )   | -0.5 |      | +6.5 | V     |                        |

| Input Voltage (V <sub>I</sub> )                 | -0.5 |      | +6.5 | V     |                        |

| Output Voltage (V <sub>O</sub> )                | -0.5 |      | +6.5 | V     |                        |

| Supply Current (I <sub>DD</sub> )               | -50  |      | +50  | mA    |                        |

| DC Input Current (I <sub>I</sub> )              | -10  |      | +10  | mA    |                        |

| DC Output Current (I <sub>O</sub> )             | -10  |      | +10  | mA    |                        |

| Operating Temperature Range (T <sub>OPR</sub> ) | -40  |      | +85  | °C    |                        |

| Storage Temperature (T <sub>STO</sub> )         | -55  |      | +125 | °C    | Stored as bare product |

#### **Frequency Characteristics**

| Parameters                                      | Min.                                                    | Typ. | Max. | Units                            | Notes                                                 |

|-------------------------------------------------|---------------------------------------------------------|------|------|----------------------------------|-------------------------------------------------------|

| Frequency Accuracy (ΔF/F)                       |                                                         | ±10  | ±20  | ppm                              | $T_{AMB}$ =+25°C; $V_{DD}$ =3.0V                      |

| Frequency vs Voltage (ΔF/V)                     |                                                         | ±0.8 | ±1.5 | ppm/V                            | T <sub>AMB</sub> =+25°C;<br>V <sub>DD</sub> =1.8~5.5V |

| Frequency vs Temperature ( $\Delta F/T_{OPR}$ ) | $-0.035$ ppm/°C <sup>2</sup> $(T_{OPR}-T_O)^2 \pm 10\%$ |      | ppm  | $T_{REF}$ =+25°C; $V_{DD}$ =3.0V |                                                       |

| Turnover Temperature (T <sub>O</sub> )          | +20                                                     | +25  | +30  | $^{\circ}\!\mathrm{C}$           |                                                       |

| Aging (first year)                              | -3                                                      |      | +3   | ppm                              | $T_{AMB}$ =+25°C                                      |

| Oscillator Start-up Time (T <sub>START</sub> )  |                                                         | 350  | 500  | ms                               | $T_{AMB}$ =+25°C                                      |

| CLKOUT duty cycle                               | 40                                                      | 50   | 60   | %                                | $T_{AMB}$ =+25°C                                      |

3.7 x 2.5 x 0.9 mm

#### **Static Characteristics**

$V_{DD}$  = 1.2 V to 5.5 V;  $V_{SS}$  = 0 V;  $T_{AMB}$  = -40°C to +85°C;  $f_{OSC}$  = 32.768 kHz; unless otherwise specified

| Parameters                                                 |                                                        | Min. | Тур. | Max. | Units | Notes                                                                                                                                                                     |

|------------------------------------------------------------|--------------------------------------------------------|------|------|------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                            | For clock data integrity I <sup>2</sup> C bus inactive | 1.2  |      | 5.5  |       |                                                                                                                                                                           |

| Supply Voltage $(V_{DD})$                                  | I <sup>2</sup> C bus active                            | 1.6  |      | 5.5  | V     |                                                                                                                                                                           |

| (* DD)                                                     | Power management function active                       | 1.8  |      | 5.5  |       |                                                                                                                                                                           |

| Slew Rate (SR)                                             | Of V <sub>DD</sub>                                     |      |      | ±0.5 | V/ms  |                                                                                                                                                                           |

| Battery Supply Voltage (V <sub>BACKUP</sub> )              | Power management function active                       | 1.8  |      | 5.5  | V     |                                                                                                                                                                           |

| Current                                                    | $f_{SCL}=1000kHz$ $V_{DD}=3.0V$                        |      | 100  | 200  | μА    |                                                                                                                                                                           |

| Consumption (I <sub>DD</sub> ) I <sup>2</sup> C bus active | $f_{SCL}=100kHz$ $V_{DD}=3.0V$                         |      | 50   | 100  | μΑ    |                                                                                                                                                                           |

| Current Consumption (I <sub>DDO</sub> )                    | $V_{DD} = 3.0V$                                        |      | 130  | 180  | nA    | I <sup>2</sup> C bus inactive (f <sub>SCL</sub> =0Hz)<br>Interrupts disabled<br>CLKOUT disabled<br>Power management fct. disabled                                         |

| 1)                                                         | $V_{DD} = 2.0V$                                        |      | 110  | 160  | nA    | (PM[2:0] = 111)<br>$T_{amb} = +25$ °C                                                                                                                                     |

| Current<br>Consumption (I <sub>DDO</sub> )                 | $V_{DD} = 2.0 \text{ to } 5.0 \text{V}$                |      |      | 500  | nA    | I <sup>2</sup> C bus inactive ( $f_{SCL}$ =0Hz)<br>Interrupts disabled<br>CLKOUT disabled<br>Power management fct. disabled<br>(PM[2:0] = 111)<br>$T_{amb}$ = -40 ~ +85°C |

| Current Consumption $(I_{DD32k})^{2}$                      | $V_{BACKUP}$ or $V_{DD} = 3.0V$                        |      | 1200 |      | nA    | $I^2C$ bus inactive ( $f_{SCL}$ =0Hz)<br>Interrupts disabled<br>CLKOUT enabled (32.768kHz)<br>Power management fct. enabled<br>(PM[2:0] = 000)<br>$T_{amb}$ = +25°C       |

| Current Consumption $(I_{DD32k})^{2}$                      | $V_{BACKUP}$ or $V_{DD} = 2.0$ to $5.0V$               |      |      | 3600 | nA    | $I^2C$ bus inactive ( $f_{SCL}$ =0Hz)<br>Interrupts disabled<br>CLKOUT enabled (32.768kHz)<br>Power management fct. enabled<br>(PM[2:0] = 000)<br>$T_{amb}$ = -40 ~ +85°C |

| Battery Leakage<br>Current (I <sub>L(bat)</sub> )          | V <sub>DD</sub> active;<br>V <sub>BACKUP</sub> =3.0V   |      | 50   | 100  | nA    |                                                                                                                                                                           |

3.7 x 2.5 x 0.9 mm

#### (Continued)

$V_{DD} = 1.2 \text{ V}$  to 5.5 V;  $V_{SS} = 0 \text{ V}$ ;  $T_{AMB} = -40^{\circ}\text{C}$  to  $+85^{\circ}\text{C}$ ;  $f_{OSC} = 32.768 \text{ kHz}$ ; unless otherwise specified

| Paramet                                                    | Min.                                                                                                                    | Тур.         | Max. | Units                | Notes |  |

|------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|--------------|------|----------------------|-------|--|

| Power Management                                           |                                                                                                                         |              |      |                      |       |  |

| Battery Switch Threshold Vo                                | ltage (V <sub>th(sw)bat</sub> )                                                                                         | 2.28         | 2.5  | 2.7                  | V     |  |

| Inputs 3)                                                  |                                                                                                                         |              |      |                      |       |  |

| LOW Level Input Voltage (V                                 | T <sub>IL</sub> )                                                                                                       |              |      | $30\%V_{DD}$         | V     |  |

| HIGH Level Input Voltage (V                                | $V_{ m IH})$                                                                                                            | $70\%V_{DD}$ |      |                      | V     |  |

| Input Voltage (V <sub>I</sub> )                            |                                                                                                                         | -0.5         |      | V <sub>DD</sub> +0.5 | V     |  |

| Innut I calso as Cumant (I )                               | $V_I = V_{DD}$ or $V_{SS}$                                                                                              |              | 0    |                      | nA    |  |

| Input Leakage Current (I <sub>L</sub> )                    | Post ESD Event                                                                                                          | -1           |      | +1                   | μΑ    |  |

| Input Capacitance (C <sub>I</sub> ) 4)                     |                                                                                                                         |              |      | 7                    | рF    |  |

| Outputs                                                    |                                                                                                                         |              |      |                      |       |  |

| Output Voltage (V <sub>O</sub> )                           | On pin INT_1, INT_2,<br>CLKOUT, SDA (refers to<br>ext. pull-up voltage)                                                 | -0.5         |      | +5.5                 | V     |  |

| LOW Level Output Voltage (                                 | $(V_{OL})$                                                                                                              | $V_{SS}$     |      | 0.4                  | V     |  |

| LOW Level Output Current $(I_{OL})^{5}$                    | Output sink current;<br>On pin $\overline{INT}_{-1}$ , $\overline{INT}_{-2}$ , CLKOUT<br>$V_{OL}$ =0.4V; $V_{DD}$ =5.0V | 1.5          |      |                      | mA    |  |

| On pin SDA<br>V <sub>OL</sub> =0.4V; V <sub>DD</sub> =3.0V |                                                                                                                         | 20           |      |                      | mA    |  |

| Output Leakage Current                                     | $V_O = V_{DD}$ or $V_{SS}$                                                                                              |              | 0    |                      | nA    |  |

| $(I_{LO})$                                                 | Post ESD Event                                                                                                          | -1           |      | +1                   | μΑ    |  |

<sup>1)</sup> Timer source clock = 1/3600 Hz, level of pins SCL and SDA is  $V_{SS}$  or  $V_{DD}$ .

<sup>2)</sup> When the device is supplied via the  $V_{BACKUP}$  pin instead of the  $V_{DD}$  pin, the current values for  $I_{BACKUP}$  will be as specified for  $I_{DD}$  under the same conditions.

<sup>3)</sup> The I<sup>2</sup>C bus is 5V tolerant.

<sup>4)</sup> Implicit by design.

<sup>5)</sup> Tested on sample basis.

3.7 x 2.5 x 0.9 mm

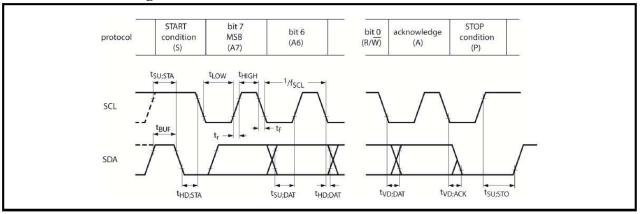

#### I<sup>2</sup>C Interface Dynamic Characteristics

| Parameters                                                                                                              | Symbol                | Standard<br>Mode |      | Fast Mode<br>(FM)    |      | Fast Mode<br>Plus (FM+) 1) |      | Units |  |  |

|-------------------------------------------------------------------------------------------------------------------------|-----------------------|------------------|------|----------------------|------|----------------------------|------|-------|--|--|

| 2 *** *********************************                                                                                 |                       | Min.             | Max. | Min.                 | Max. | Min.                       | Max. | 01110 |  |  |

| Pin SCL                                                                                                                 |                       |                  |      |                      |      |                            |      |       |  |  |

| SCL clock frequency <sup>2)</sup>                                                                                       | $f_{SCL}$             |                  | 100  |                      | 400  |                            | 1000 | kHz   |  |  |

| LOW period of SCL clock                                                                                                 | $t_{LOW}$             | 4.7              |      | 1.3                  |      | 0.5                        |      | μs    |  |  |

| HIGH period of SCL clock                                                                                                | $t_{\rm HIGH}$        | 4.0              |      | 1.6                  |      | 0.26                       |      | μs    |  |  |

| Pin SDA                                                                                                                 |                       |                  |      |                      |      |                            |      |       |  |  |

| Data setup time                                                                                                         | $t_{\mathrm{SU;DAT}}$ | 250              |      | 100                  |      | 50                         |      | ns    |  |  |

| Data hold time                                                                                                          | $t_{HD;DAT}$          | 0                |      | 0                    |      | 0                          |      | ns    |  |  |

| Pin SCL and SDA                                                                                                         |                       |                  |      |                      |      |                            |      |       |  |  |

| Bus free time between STOP and START condition                                                                          | $t_{ m BUF}$          | 4.7              |      | 1.3                  |      | 0.5                        |      | μs    |  |  |

| Setup time for STOP condition                                                                                           | $t_{\mathrm{SU;STO}}$ | 4.0              |      | 0.6                  |      | 0.26                       |      | μs    |  |  |

| Hold time (repeated) START condition                                                                                    | $t_{\text{HD;STA}}$   | 4.0              |      | 0.6                  |      | 0.26                       |      | μs    |  |  |

| Setup time for repeated START condition                                                                                 | $t_{\mathrm{SU;STA}}$ | 4.7              |      | 0.6                  |      | 0.26                       |      | μs    |  |  |

| Rise time of both SDA and SCL signals 3) 4)                                                                             | $t_{\rm r}$           |                  | 1000 | 20+0.1C <sub>b</sub> | 300  |                            | 120  | ns    |  |  |

| Fall time of both SDA and SCL signals 3)4)                                                                              | $t_{\mathrm{f}}$      |                  | 300  | 20+0.1C <sub>b</sub> | 300  |                            | 120  | ns    |  |  |

| Capacitive load for each bus line                                                                                       | $C_b$                 |                  | 400  |                      | 400  |                            | 550  | pF    |  |  |

| Data valid acknowledge time 5)                                                                                          | t <sub>VD;ACK</sub>   |                  | 3.45 |                      | 0.9  |                            | 0.45 | μs    |  |  |

| Data valid time <sup>6)</sup>                                                                                           | $t_{\mathrm{VD;DAT}}$ |                  | 3.45 |                      | 0.9  |                            | 0.45 | μs    |  |  |

| Pulse width of spikes that must be suppressed by the input filter 7)  1) Fact mode plus guaranteed at 3.0 V < V < 5.5 V | $t_{\mathrm{SP}}$     |                  | 50   |                      | 50   |                            | 50   | ns    |  |  |

- 1) Fast mode plus guaranteed at 3.0 V  $\leq$  V<sub>DD</sub>  $\leq$  5.5 V.

- 2) The minimum SCL clock frequency is limited by the bus time-out feature, which resets the serial bus interface if either the SDA or SCL is held LOW for a minimum of 25 ms. The bus time-out feature must be disabled for DC operation.

- 3) A master device must internally provide a hold time of at least 300 ns for the SDA signal (refer to the  $V_{\rm IL}$  of the SCL signal) in order to bridge the undefined region of the falling edge of SCL.

- 4) The maximum  $t_f$  for the SDA and SCL bus lines is 300 ns. The maximum fall time for the SDA output stage,  $t_f$  is 250 ns. This allows series protection resistors to be connected between the SDA pin, the SCL pin and the SDA/SCL bus lines without exceeding the maximum  $t_f$ .

- 5) t<sub>VD;ACK</sub> = time for acknowledgement signal from SCL LOW to SDA output LOW.

- 6) t<sub>VD;DAT</sub> = minimum time for valid SDA output following SCL LOW.

- 7) Input filters on the SDA and SCL inputs suppress noise spikes of less than 50 ns.

#### I<sup>2</sup>C Interface Timing Characteristics

AB-RTCMC-32.768kHz-B5ZE-S3

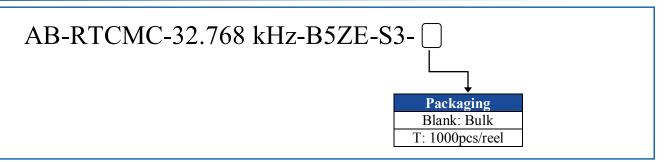

#### **▶** PART IDENTIFICATIONS:

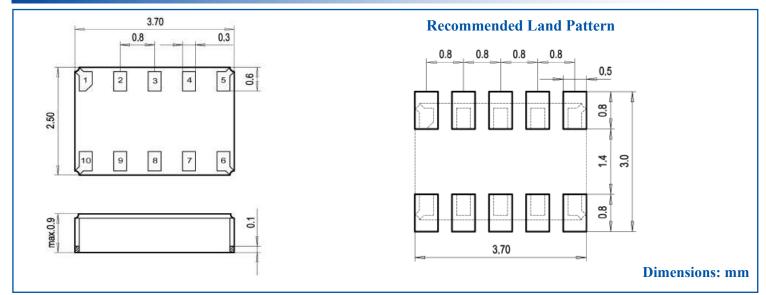

### **OUTLINE DIMENSIONS:**

### **▶ PIN DESCRIPTIONS:**

| Pin No. | Pin Name     | Function                     |

|---------|--------------|------------------------------|

| 1       | $V_{DD}$     | Power Supply Voltage         |

| 2       | INT_1        | Interrupt _1 Output pin      |

| 3       | SCL          | Serial Clock Input pin       |

| 4       | SDA          | Serial Data Input-Output pin |

| 5       | CLKOUT       | Clock Output pin; push-pull  |

| 6       | INT_2        | Interrupt _2 Output pin      |

| 7       | $V_{SS}$     | Ground                       |

| 8       | $V_{BACKUP}$ | Backup Supply Voltage        |

| 9       | N.C.         | Not Connected                |

| 10      | N.C.         | Not Connected                |

AB-RTCMC-32.768kHz-B5ZE-S3

3.7 x 2.5 x 0.9 mm

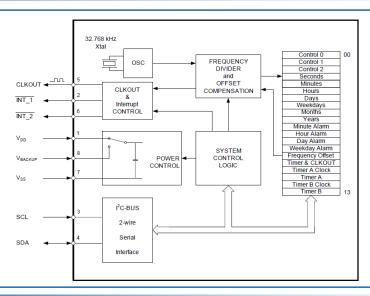

#### **BLOCK DIAGRAM:**

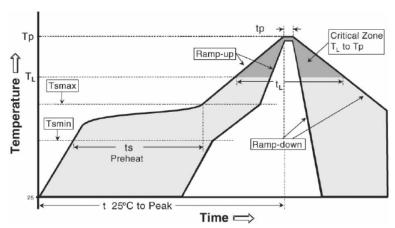

#### **RECOMMENDED REFLOW PROFILE:**

#### Maximum Reflow Conditions in accordance with IPC/JEDEC J-STD-020C "Pb-free"

| Temperature                                                 | Conditions     | Units<br>°C/s           |  |

|-------------------------------------------------------------|----------------|-------------------------|--|

| Average Ramp-up Rate (T <sub>Smax</sub> to T <sub>P</sub> ) | 3°C/second max |                         |  |

| Ramp Down Rate (T <sub>cool</sub> )                         | 6°C/second max | °C/s                    |  |

| Time 25°C to Peak Temperature (T to-peak)                   | 8 minutes max  | m                       |  |

| Preheat                                                     |                |                         |  |

| Temperature Min (T <sub>Smin</sub> )                        | 150            | $^{\circ}$ C            |  |

| Temperature Max (T <sub>Smax</sub> )                        | 200            | $^{\circ}$ C            |  |

| Time Ts <sub>min</sub> to Ts <sub>max</sub> (ts)            | 60 ~ 180       | sec                     |  |

| Time Above Liquidus                                         |                |                         |  |

| Temperature Liquidus (T <sub>L</sub> )                      | 217            | $^{\circ}$ C            |  |

| Time above Liquidus (t <sub>L</sub> )                       | 60~150         | sec                     |  |

| Peak Temperature                                            |                |                         |  |

| Peak Temperature (T <sub>P</sub> )                          | 260            | $^{\circ}\! \mathbb{C}$ |  |

| Time within 5°C of Peak Temperature (t <sub>P</sub> )       | $20\sim40$     | sec                     |  |

AB-RTCMC-32.768kHz-B5ZE-S3

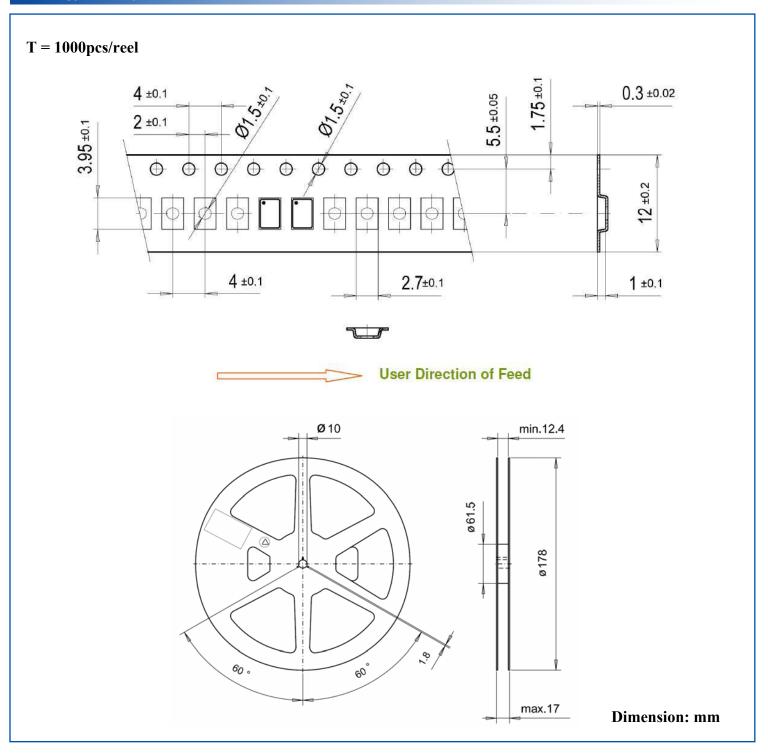

#### **TAPE & REEL:**

**ATTENTION:** Abracon Corporation's products are COTS – Commercial-Off-The-Shelf products; suitable for Commercial, Industrial and, where designated, Automotive Applications. Abracon's products are not specifically designed for Military, Aviation, Aerospace, Life-dependant Medical applications or any application requiring high reliability where component failure could result in loss of life and/or property. For applications requiring high reliability and/or presenting an extreme operating environment, written consent and authorization from Abracon Corporation is required. Please contact Abracon Corporation for more information.