Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# 28/44-Pin dsPIC30F1010/202X Enhanced Flash SMPS 16-Bit Digital Signal Controller

**Note:** This data sheet summarizes features of this group of dsPIC30F devices and is not intended to be a complete reference source. For more information on the CPU, peripherals, register descriptions and general device functionality, refer to the "dsPIC30F Family Reference Manual" (DS70046). For more information on the device instruction set and programming, refer to the "dsPIC30F/33F Programmer's Reference Manual" (DS70157).

# **High-Performance Modified RISC CPU:**

- · Modified Harvard architecture

- · C compiler optimized instruction set architecture

- 83 base instructions with flexible addressing modes

- · 24-bit wide instructions, 16-bit wide data path

- · 12 Kbytes on-chip Flash program space

- 512 bytes on-chip data RAM

- · 16 x 16-bit working register array

- Up to 30 MIPS operation:

- Dual Internal RC

- 9.7 and 14.55 MHz (±1%) Industrial Temp

- 6.4 and 9.7 MHz (±1%) Extended Temp

- 32X PLL with 480 MHz VCO

- PLL inputs ±3%

- External EC clock 6.0 to 14.55 MHz

- HS Crystal mode 6.0 to 14.55 MHz

- · 32 interrupt sources

- · Three external interrupt sources

- · 8 user-selectable priority levels for each interrupt

- · 4 processor exceptions and software traps

### **DSP Engine Features:**

- · Modulo and Bit-Reversed modes

- Two 40-bit wide accumulators with optional saturation logic

- 17-bit x 17-bit single-cycle hardware fractional/ integer multiplier

- Single-cycle Multiply-Accumulate (MAC) operation

- · 40-stage Barrel Shifter

- Dual data fetch

### **Peripheral Features:**

- · High-current sink/source I/O pins: 25 mA/25 mA

- Three 16-bit timers/counters; optionally pair up 16-bit timers into 32-bit timer modules

- · One 16-bit Capture input functions

- Two 16-bit Compare/PWM output functions

- Dual Compare mode available

- 3-wire SPI modules (supports 4 Frame modes)

- I<sup>2</sup>C<sup>TM</sup> module supports Multi-Master/Slave mode and 7-bit/10-bit addressing

- · UART Module:

- Supports RS-232, RS-485 and LIN 1.2

- Supports IrDA® with on-chip hardware endec

- Auto wake-up on Start bit

- Auto-Baud Detect

- 4-level FIFO buffer

### **Power Supply PWM Module Features:**

- · Four PWM generators with 8 outputs

- Each PWM generator has independent time base and duty cycle

- Duty cycle resolution of 1.1 ns at 30 MIPS

- · Individual dead time for each PWM generator:

- Dead-time resolution 4.2 ns at 30 MIPS

- Dead time for rising and falling edges

- · Phase-shift resolution of 4.2 ns @ 30 MIPS

- Frequency resolution of 8.4 ns @ 30 MIPS

- · PWM modes supported:

- Complementary

- Push-Pull

- Multi-Phase

- Variable Phase

- Current Reset

- Current-Limit

- · Independent Current-Limit and Fault Inputs

- · Output Override Control

- · Special Event Trigger

- · PWM generated ADC Trigger

# **Analog Features:**

#### ADC

- · 10-bit resolution

- 2000 Ksps conversion rate

- · Up to 12 input channels

- "Conversion pairing" allows simultaneous conversion of two inputs (i.e., current and voltage) with a single trigger

- PWM control loop:

- Up to six conversion pairs available

- Each conversion pair has up to four PWM and seven other selectable trigger sources

- Interrupt hardware supports up to 1M interrupts per second

#### **COMPARATOR**

- · Four Analog Comparators:

- 20 ns response time

- 10-bit DAC reference generator

- Programmable output polarity

- Selectable input source

- ADC sample and convert capable

- · PWM module interface

- PWM Duty Cycle Control

- PWM Period Control

- PWM Fault Detect

- Special Event Trigger

- PWM-generated ADC Trigger

# **Special Microcontroller Features:**

- · Enhanced Flash program memory:

- 10,000 erase/write cycle (min.) for industrial temperature range, 100k (typical)

- · Self-reprogrammable under software control

- Power-on Reset (POR), Power-up Timer (PWRT) and Oscillator Start-up Timer (OST)

- Flexible Watchdog Timer (WDT) with on-chip low power RC oscillator for reliable operation

- · Fail-Safe clock monitor operation

- Detects clock failure and switches to on-chip low power RC oscillator

- · Programmable code protection

- In-Circuit Serial Programming™ (ICSP™)

- · Selectable Power Management modes

- Sleep, Idle and Alternate Clock modes

# **CMOS Technology:**

- · Low-power, high-speed Flash technology

- 3.3V and 5.0V operation (±10%)

- · Industrial and Extended temperature ranges

- · Low power consumption

#### dsPIC30F SWITCH MODE POWER SUPPLY FAMILY

| Product      | Pins | Packaging | Program<br>Memory<br>(Bytes) | Data SRAM<br>(Bytes) | Timers | Capture | Compare | UART | SPI | I²C™ | PWM | ADCs | S & Н | A/D<br>Inputs | Analog<br>Comparators | GPIO |

|--------------|------|-----------|------------------------------|----------------------|--------|---------|---------|------|-----|------|-----|------|-------|---------------|-----------------------|------|

| dsPIC30F1010 | 28   | SDIP      | 6K                           | 256                  | 2      | 0       | 1       | 1    | 1   | 1    | 2x2 | 1    | 3     | 6 ch          | 2                     | 21   |

| dsPIC30F1010 | 28   | SOIC      | 6K                           | 256                  | 2      | 0       | 1       | 1    | 1   | 1    | 2x2 | 1    | 3     | 6 ch          | 2                     | 21   |

| dsPIC30F1010 | 28   | QFN-S     | 6K                           | 256                  | 2      | 0       | 1       | 1    | 1   | 1    | 2x2 | 1    | 3     | 6 ch          | 2                     | 21   |

| dsPIC30F2020 | 28   | SDIP      | 12K                          | 512                  | 3      | 1       | 2       | 1    | 1   | 1    | 4x2 | 1    | 5     | 8 ch          | 4                     | 21   |

| dsPIC30F2020 | 28   | SOIC      | 12K                          | 512                  | 3      | 1       | 2       | 1    | 1   | 1    | 4x2 | 1    | 5     | 8 ch          | 4                     | 21   |

| dsPIC30F2020 | 28   | QFN-S     | 12K                          | 512                  | 3      | 1       | 2       | 1    | 1   | 1    | 4x2 | 1    | 5     | 8 ch          | 4                     | 21   |

| dsPIC30F2023 | 44   | QFN       | 12K                          | 512                  | 3      | 1       | 2       | 1    | 1   | 1    | 4x2 | 1    | 5     | 12 ch         | 4                     | 35   |

| dsPIC30F2023 | 44   | TQFP      | 12K                          | 512                  | 3      | 1       | 2       | 1    | 1   | 1    | 4x2 | 1    | 5     | 12 ch         | 4                     | 35   |

# **Table of Contents**

| 1.0   | Device Overview                                           | 9     |

|-------|-----------------------------------------------------------|-------|

| 2.0   | CPU Architecture Overview                                 | 19    |

| 3.0   | Memory Organization                                       |       |

| 4.0   | Address Generator Units                                   | 41    |

| 5.0   | Interrupts                                                | 47    |

| 6.0   | I/O Ports                                                 | 77    |

| 7.0   | Flash Program Memory                                      | 81    |

| 8.0   | Timer1 Module                                             | 87    |

| 9.0   | Timer2/3 Module                                           | 91    |

| 10.0  | Input Capture Module                                      | 97    |

| 11.0  | Output Compare Module                                     | . 101 |

| 12.0  | Power Supply PWM                                          | . 107 |

| 13.0  | Serial Peripheral Interface (SPI)                         | . 145 |

| 14.0  | I2C <sup>TM</sup> Module                                  | . 153 |

| 15.0  | Universal Asynchronous Receiver Transmitter (UART) Module | . 161 |

| 16.0  | 10-bit 2 Msps Analog-to-Digital Converter (ADC) Module    | . 169 |

| 17.0  | SMPS Comparator Module                                    | . 191 |

| 18.0  | System Integration                                        | . 197 |

| 19.0  | Instruction Set Summary                                   | . 219 |

| 20.0  | Development Support                                       |       |

| 21.0  | Electrical Characteristics                                | . 231 |

| 22.0  | Package Marking Information                               | . 267 |

| Appe  | ndix A: Revision History                                  | . 275 |

| Index |                                                           | . 277 |

### TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at docerrors@microchip.com. We welcome your feedback.

#### **Most Current Data Sheet**

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000).

#### **Errata**

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- · Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using

#### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

### 1.0 DEVICE OVERVIEW

**Note:** This data sheet summarizes features of this group of dsPIC30F devices and is not intended to be a complete reference source. For more information on the CPU, peripherals, register descriptions and general device functionality, refer to the "dsPIC30F Family Reference Manual" (DS70046). For more information on the device instruction set and programming, refer to the "dsPIC30F/33F Programmer's Reference Manual" (DS70157).

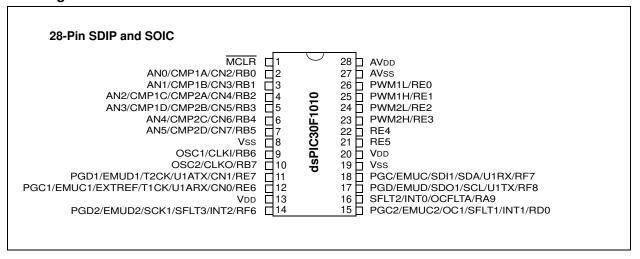

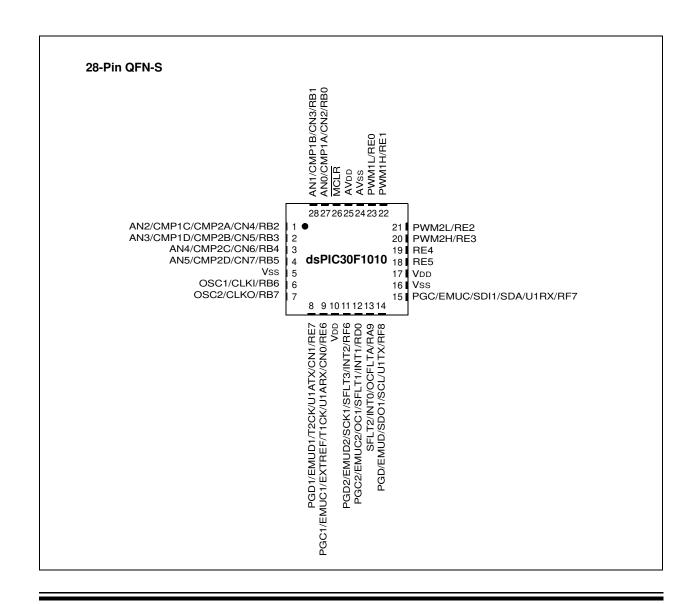

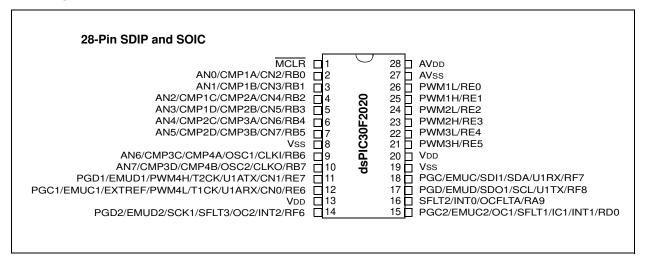

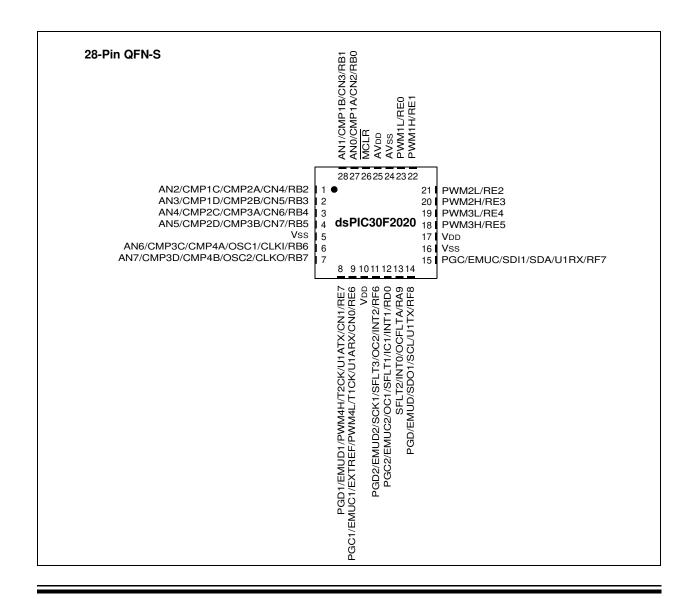

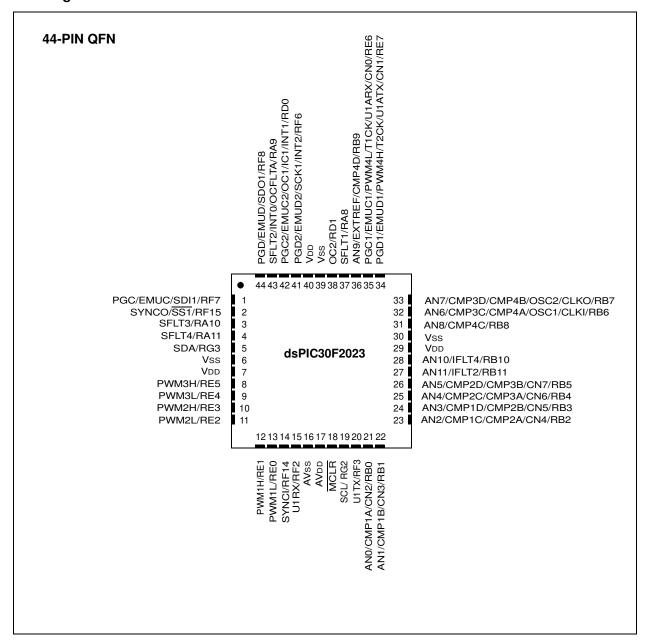

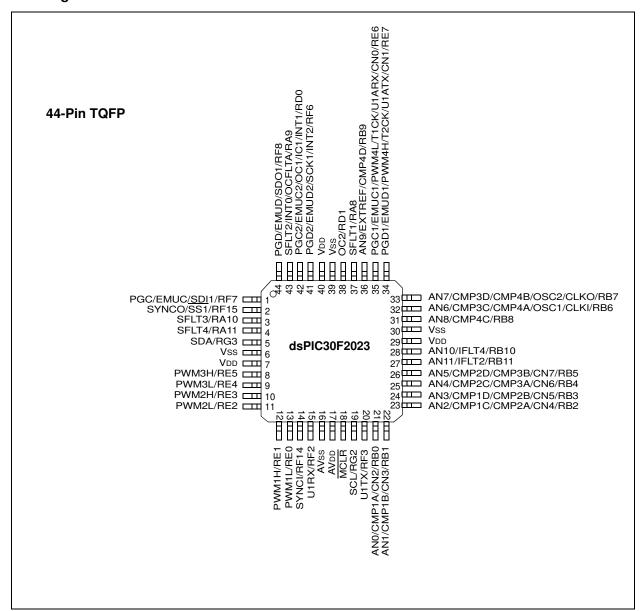

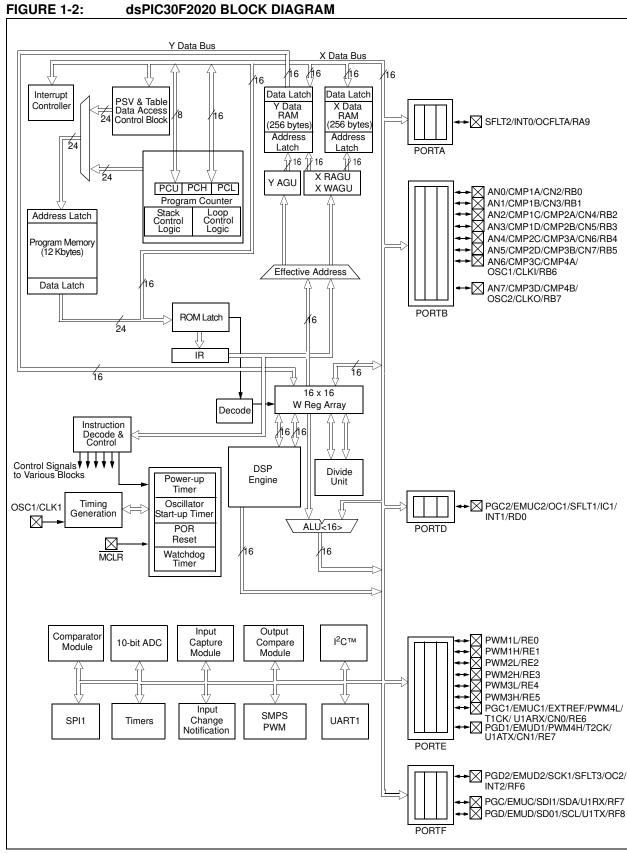

This document contains device specific information for the dsPIC30F1010/202X SMPS devices. These devices contain extensive Digital Signal Processor (DSP) functionality within a high-performance 16-bit microcontroller (MCU) architecture, as reflected in the following block diagrams. Figure 1-1 and Table 1-1 describe the dsPIC30F1010 SMPS device, Figure 1-2 and Table 1-2 describe the dsPIC30F2020 device and Figure 1-3 and Table 1-3 describe the dsPIC30F2023 SMPS device.

FIGURE 1-1: dsPIC30F1010 BLOCK DIAGRAM Y Data Bus X Data Bus 16 116 16 Interrupt Data Latch Data Latch PSV & Table Data Access Controlle Y Data X Data RAM RAM (256 bytes 16 Control Block SFLT2/INT0/OCFLTA/RA9 (256 bytes Address Address 24 Latch Latch PORTA 16 24 X RAGU Y AGU PCŮ PCH PCL X WAGU AN0/CMP1A/CN2/RB0 Program Counter AN1/CMP1B/CN3/RB1 Stack Loop Control Logic Address Latch AN2/CMP1C/CMP2A/CN4/RB2 Control AN3/CMP1D/CMP2B/CN5/RB3 AN4/CMP2C/CN6/RB4 Program Memory (12 Kbytes) AN5/CMP2D/CN7/RB5 OSC1/CLKI/RB6 Effective Address OSC2/CLKO/RB7 16 Data Latch **ROM Latch** 6 IR 16 16 16 x 16 W Reg Array Decode Instruction 16/16 Decode & Control Control Signals V V V V to Various Blocks DSP Divide Power-up Engine Unit Oscillator PGC2/EMUC2/OC1/SFLT1/ OSC1/CLK1 Generation tart-up Timei INT1/RD0  $\boxtimes$ ALU<16> POR PORTD Reset MCLR Watchdog Timer 116 16 Output Comparator PWM1L/RE0  $I^2C^{TM}$ 10-bit ADC Compare Module PWM1H/RE1 Module PWM2L/RE2 PWM2H/RE3 RE4 RE5 PGC1/EMUC1/EXTREF/T1CK/ U1ARX/CN0/RE6 Input SMPS Change Notification SPI1 UART1 Timers PGD1/EMUD1/T2CK/U1ATX/ CN1/RE7 **PWM PORTE** PGD2/EMUD2/SCK1/SFLT3/ INT2/RF6 PGC/EMUC/SDI1/SDA/U1RX/RF7 PGD/EMUD/SD01/SCL/U1TX/RF8 PORTF

Table 1-1 provides a brief description of device I/O pinouts for the dsPIC30F1010 and the functions that may be multiplexed to a port pin. Multiple functions may exist on one port pin. When multiplexing occurs, the peripheral module's functional requirements may force an override of the data direction of the port pin.

TABLE 1-1: PINOUT I/O DESCRIPTIONS FOR dsPIC30F1010

| Pin Name | Pin<br>Type | Buffer<br>Type | Description                                                                                                                                                                                                                                               |  |

|----------|-------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| AN0-AN5  | I           | Analog         | Analog input channels.                                                                                                                                                                                                                                    |  |

| AVDD     | Р           | Р              | Positive supply for analog module.                                                                                                                                                                                                                        |  |

| AVss     | Р           | Р              | Ground reference for analog module.                                                                                                                                                                                                                       |  |

| CLKO     | - 0         | ST/CMOS        | External clock source input. Always associated with OSC1 pin function. Oscillator crystal output. Connects to crystal or resonator in Crystal Oscillator mode. Optionally functions as CLKO in RC and EC modes. Always associated with OSC2 pin function. |  |

| EMUD     | I/O         | ST             | ICD Primary Communication Channel data input/output pin.                                                                                                                                                                                                  |  |

| EMUC     | I/O         | ST             | ICD Primary Communication Channel clock input/output pin.                                                                                                                                                                                                 |  |

| EMUD1    | I/O         | ST             | ICD Secondary Communication Channel data input/output pin.                                                                                                                                                                                                |  |

| EMUC1    | I/O         | ST             | ICD Secondary Communication Channel clock input/output pin.                                                                                                                                                                                               |  |

| EMUD2    | I/O         | ST             | ICD Tertiary Communication Channel data input/output pin.                                                                                                                                                                                                 |  |

| EMUC2    | I/O         | ST             | ICD Tertiary Communication Channel clock input/output pin.                                                                                                                                                                                                |  |

| INT0     | I           | ST             | External interrupt 0                                                                                                                                                                                                                                      |  |

| INT1     | I           | ST             | External interrupt 1                                                                                                                                                                                                                                      |  |

| INT2     | I           | ST             | External interrupt 2                                                                                                                                                                                                                                      |  |

| SFLT1    | I           | ST             | Shared Fault Pin 1                                                                                                                                                                                                                                        |  |

| SFLT2    | I           | ST             | Shared Fault Pin 2                                                                                                                                                                                                                                        |  |

| SFLT3    | I           | ST             | Shared Fault Pin 3                                                                                                                                                                                                                                        |  |

| PWM1L    | 0           | _              | PWM 1 Low output                                                                                                                                                                                                                                          |  |

| PWM1H    | 0           | _              | PWM 1 High output                                                                                                                                                                                                                                         |  |

| PWM2L    | 0           | _              | PWM 2 Low output                                                                                                                                                                                                                                          |  |

| PWM2H    | 0           | _              | PWM 2 High output                                                                                                                                                                                                                                         |  |

| MCLR     | I/P         | ST             | Master Clear (Reset) input or programming voltage input. This pin is an active low Reset to the device.                                                                                                                                                   |  |

| OC1      | 0           | _              | Compare outputs.                                                                                                                                                                                                                                          |  |

| OCFLTA   | I           | ST             | Output Compare Fault Pin                                                                                                                                                                                                                                  |  |

| OSC1     | I           | CMOS           | Oscillator crystal input.                                                                                                                                                                                                                                 |  |

| OSC2     | I/O         | _              | Oscillator crystal output. Connects to crystal or resonator in Crystal Oscillator mode. Optionally functions as CLKO in FRC and EC modes.                                                                                                                 |  |

| PGD      | I/O         | ST             | In-Circuit Serial Programming™ data input/output pin.                                                                                                                                                                                                     |  |

| PGC      | I           | ST             | In-Circuit Serial Programming clock input pin.                                                                                                                                                                                                            |  |

| PGD1     | I/O         | ST             | In-Circuit Serial Programming data input/output pin 1.                                                                                                                                                                                                    |  |

| PGC1     | I           | ST             | In-Circuit Serial Programming clock input pin 1.                                                                                                                                                                                                          |  |

| PGD2     | I/O         | ST             | In-Circuit Serial Programming data input/output pin 2.                                                                                                                                                                                                    |  |

| PGC2     | I           | ST             | In-Circuit Serial Programming clock input pin 2.                                                                                                                                                                                                          |  |

| RB0-RB7  | I/O         | ST             | PORTB is a bidirectional I/O port.                                                                                                                                                                                                                        |  |

| RA9      | I/O         | ST             | PORTA is a bidirectional I/O port.                                                                                                                                                                                                                        |  |

| RD0      | I/O         | ST             | PORTD is a bidirectional I/O port.                                                                                                                                                                                                                        |  |

Legend:CMOS=CMOS compatible input or outputAnalog=Analog inputST=Schmitt Trigger input with CMOS levelsO=OutputI=InputP=Power

TABLE 1-1: PINOUT I/O DESCRIPTIONS FOR dsPIC30F1010 (CONTINUED)

| Pin Name      | Pin<br>Type | Buffer<br>Type | Description                                                          |  |

|---------------|-------------|----------------|----------------------------------------------------------------------|--|

| RE0-RE7       | I/O         | ST             | PORTE is a bidirectional I/O port.                                   |  |

| RF6, RF7, RF8 | I/O         | ST             | PORTF is a bidirectional I/O port.                                   |  |

| SCK1          | I/O         | ST             | Synchronous serial clock input/output for SPI #1.                    |  |

| SDI1          | I           | ST             | SPI #1 Data In.                                                      |  |

| SDO1          | 0           | _              | SPI #1 Data Out.                                                     |  |

| SCL           | I/O         | ST             | Synchronous serial clock input/output for I <sup>2</sup> C™.         |  |

| SDA           | I/O         | ST             | Synchronous serial data input/output for I <sup>2</sup> C.           |  |

| T1CK          | I           | ST             | Timer1 external clock input.                                         |  |

| T2CK          | I           | ST             | Timer2 external clock input.                                         |  |

| U1RX          | I           | ST             | UART1 Receive.                                                       |  |

| U1TX          | 0           | _              | UART1 Transmit.                                                      |  |

| U1ARX         | 1           | ST             | Alternate UART1 Receive.                                             |  |

| U1ATX         | 0           | -              | Alternate UART1 Transmit.                                            |  |

| CMP1A         | I           | Analog         | Comparator 1 Channel A                                               |  |

| CMP1B         | 1           | Analog         | Comparator 1 Channel B                                               |  |

| CMP1C         | I           | Analog         | Comparator 1 Channel C                                               |  |

| CMP1D         | 1           | Analog         | Comparator 1 Channel D                                               |  |

| CMP2A         | I           | Analog         | Comparator 2 Channel A                                               |  |

| CMP2B         | I           | Analog         | Comparator 2 Channel B                                               |  |

| CMP2C         | 1           | Analog         | Comparator 2 Channel C                                               |  |

| CMP2D         | I           | Analog         | Comparator 2 Channel D                                               |  |

| CN0-CN7       | I           | ST             | Input Change notification inputs                                     |  |

|               |             |                | Can be software programmed for internal weak pull-ups on all inputs. |  |

| VDD           | Р           |                | Positive supply for logic and I/O pins.                              |  |

| Vss           | Р           |                | Ground reference for logic and I/O pins.                             |  |

| EXTREF        | Ī           | Analog         | External reference to Comparator DAC                                 |  |

Legend:CMOS=CMOS compatible input or outputAnalog=Analog inputST=Schmitt Trigger input with CMOS levelsO=OutputI=InputP=Power

Table 1-2 provides a brief description of device I/O pinouts for the dsPIC30F2020 and the functions that may be multiplexed to a port pin. Multiple functions may exist on one port pin. When multiplexing occurs, the peripheral module's functional requirements may force an override of the data direction of the port pin.

TABLE 1-2: PINOUT I/O DESCRIPTIONS FOR dsPIC30F2020

| Pin Name                                                                                                 | Pin<br>Type                     | Buffer<br>Type                   | Description                                                                                                                                                                                                                                                                                                                                                    |  |  |

|----------------------------------------------------------------------------------------------------------|---------------------------------|----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| AN0-AN7                                                                                                  | I                               | Analog                           | Analog input channels.                                                                                                                                                                                                                                                                                                                                         |  |  |

| AVDD                                                                                                     | Р                               | Р                                | Positive supply for analog module.                                                                                                                                                                                                                                                                                                                             |  |  |

| AVss                                                                                                     | Р                               | Р                                | Ground reference for analog module.                                                                                                                                                                                                                                                                                                                            |  |  |

| CLKO                                                                                                     | 0                               | ST/CMOS<br>—                     | External clock source input. Always associated with OSC1 pin function. Oscillator crystal output. Connects to crystal or resonator in Crystal Oscillator mode. Optionally functions as CLKO in RC and EC modes. Always associated with OSC2 pin function.                                                                                                      |  |  |

| EMUD<br>EMUC<br>EMUD1<br>EMUC1<br>EMUD2<br>EMUC2                                                         | I/O<br>I/O<br>I/O<br>I/O<br>I/O | ST<br>ST<br>ST<br>ST<br>ST<br>ST | ICD Primary Communication Channel data input/output pin. ICD Primary Communication Channel clock input/output pin. ICD Secondary Communication Channel data input/output pin. ICD Secondary Communication Channel clock input/output pin. ICD Tertiary Communication Channel data input/output pin. ICD Tertiary Communication Channel clock input/output pin. |  |  |

| IC1                                                                                                      | I                               | ST                               | Capture input.                                                                                                                                                                                                                                                                                                                                                 |  |  |

| INT0<br>INT1<br>INT2                                                                                     | <br>                            | ST<br>ST<br>ST                   | External interrupt 0 External interrupt 1 External interrupt 2                                                                                                                                                                                                                                                                                                 |  |  |

| SFLT1<br>SFLT2<br>SFLT3<br>PWM1L<br>PWM1H<br>PWM2L<br>PWM2H<br>PWM3L<br>PWM3L<br>PWM3H<br>PWM4L<br>PWM4H | 1 1 0 0 0 0 0 0 0               | ST<br>ST<br><br><br><br>         | Shared Fault Pin 1 Shared Fault Pin 2 Shared Fault Pin 3 PWM 1 Low output PWM 1 High output PWM 2 Low output PWM 2 High output PWM 3 Low output PWM 3 Low output PWM 4 High output                                                                                                                                                                             |  |  |

| MCLR                                                                                                     | I/P                             | ST                               | Master Clear (Reset) input or programming voltage input. This pin is an active low Reset to the device.                                                                                                                                                                                                                                                        |  |  |

| OC1-OC2<br>OCFLTA                                                                                        | O<br>                           | _                                | Compare outputs. Output Compare Fault pin                                                                                                                                                                                                                                                                                                                      |  |  |

| OSC1<br>OSC2                                                                                             | I<br>I/O                        | CMOS<br>—                        | Oscillator crystal input. Oscillator crystal output. Connects to crystal or resonator in Crystal Oscillator mode. Optionally functions as CLKO in FRC and EC modes.                                                                                                                                                                                            |  |  |

| PGD<br>PGC<br>PGD1<br>PGC1<br>PGD2<br>PGC2                                                               | I/O<br>I<br>I/O<br>I<br>I/O     | ST<br>ST<br>ST<br>ST<br>ST<br>ST | In-Circuit Serial Programming™ data input/output pin. In-Circuit Serial Programming clock input pin. In-Circuit Serial Programming data input/output pin 1. In-Circuit Serial Programming clock input pin 1. In-Circuit Serial Programming data input/output pin 2. In-Circuit Serial Programming clock input pin 2.                                           |  |  |

Legend:CMOS=CMOS compatible input or outputAnalog=Analog inputST=Schmitt Trigger input with CMOS levelsO=OutputI=InputP=Power

TABLE 1-2: PINOUT I/O DESCRIPTIONS FOR dsPIC30F2020 (CONTINUED)

| Pin Name                                                                                                                   | Pin<br>Type   | Buffer<br>Type                                                                                           | Description                                                                                                                                                                                                                                                                                                                                              |  |

|----------------------------------------------------------------------------------------------------------------------------|---------------|----------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| RB0-RB7                                                                                                                    | I/O           | ST                                                                                                       | PORTB is a bidirectional I/O port.                                                                                                                                                                                                                                                                                                                       |  |

| RA9                                                                                                                        | I/O           | ST                                                                                                       | PORTA is a bidirectional I/O port.                                                                                                                                                                                                                                                                                                                       |  |

| RD0                                                                                                                        | I/O           | ST                                                                                                       | PORTD is a bidirectional I/O port.                                                                                                                                                                                                                                                                                                                       |  |

| RE0-RE7                                                                                                                    | I/O           | ST                                                                                                       | PORTE is a bidirectional I/O port.                                                                                                                                                                                                                                                                                                                       |  |

| RF6, RF7, RF8                                                                                                              | I/O           | ST                                                                                                       | PORTF is a bidirectional I/O port.                                                                                                                                                                                                                                                                                                                       |  |

| SCK1<br>SDI1<br>SDO1                                                                                                       | I/O<br>I<br>O | ST<br>ST<br>—                                                                                            | Synchronous serial clock input/output for SPI #1. SPI #1 Data In. SPI #1 Data Out.                                                                                                                                                                                                                                                                       |  |

| SCL<br>SDA                                                                                                                 | I/O<br>I/O    | ST<br>ST                                                                                                 | Synchronous serial clock input/output for I <sup>2</sup> C <sup>™</sup> . Synchronous serial data input/output for I <sup>2</sup> C.                                                                                                                                                                                                                     |  |

| T1CK<br>T2CK                                                                                                               | <br>          | ST<br>ST                                                                                                 | Timer1 external clock input. Timer2 external clock input.                                                                                                                                                                                                                                                                                                |  |

| U1RX<br>U1TX<br>U1ARX<br>U1ATX                                                                                             | - 0 - 0       | ST<br>—<br>ST<br>O                                                                                       | UART1 Receive. UART1 Transmit. Alternate UART1 Receive. Alternate UART1 Transmit.                                                                                                                                                                                                                                                                        |  |

| CMP1A<br>CMP1B<br>CMP1C<br>CMP1D<br>CMP2A<br>CMP2B<br>CMP2C<br>CMP2D<br>CMP3A<br>CMP3B<br>CMP3C<br>CMP3D<br>CMP4A<br>CMP4B |               | Analog | Comparator 1 Channel A Comparator 1 Channel B Comparator 1 Channel C Comparator 1 Channel D Comparator 2 Channel A Comparator 2 Channel B Comparator 2 Channel C Comparator 2 Channel D Comparator 3 Channel D Comparator 3 Channel B Comparator 3 Channel B Comparator 3 Channel C Comparator 3 Channel C Comparator 4 Channel D Comparator 4 Channel B |  |

| CN0-CN7                                                                                                                    | I             | ST                                                                                                       | Input Change notification inputs Can be software programmed for internal weak pull-ups on all inputs.                                                                                                                                                                                                                                                    |  |

| VDD                                                                                                                        | Р             | -                                                                                                        | Positive supply for logic and I/O pins.                                                                                                                                                                                                                                                                                                                  |  |

| Vss                                                                                                                        | Р             | _                                                                                                        | Ground reference for logic and I/O pins.                                                                                                                                                                                                                                                                                                                 |  |

| EXTREF                                                                                                                     | I             | Analog                                                                                                   | External reference to Comparator DAC                                                                                                                                                                                                                                                                                                                     |  |

Legend:

CMOS

=

CMOS compatible input or output

Analog

=

Analog input

ST

=

Schmitt Trigger input with CMOS levels

O

=

Output

I

=

Input

P

=

Power

Y Data Bus X Data Bus 16 16 16 Data Latch Interrupt Data Latch PSV & Table Data Access Control Block Controlle Y Data X Data SFLT1/RA8 RAM RAM 256 bytes 256 bytes SFLT2/INT0/OCFLTA/RA9 Address Address SFLT3/RA10 24 Latch Latch SFLT4/RA11 16 17 16 16 **PORTA** 24 X RAGU Y AGU PCU PCH PCL X WAGU AN0/CMP1A/CN2/RB0 Program Counter AN1/CMP1B/CN3/RB1 Stack Loop Control Logic AN2/CMP1C/CMP2A/CN4/RB2 Address Latch Control AN3/CMP1D/CMP2B/CN5/RB3 AN4/CMP2C/CMP3A/CN6/RB4 Program Memory (12 Kbytes) AN5/CMP2D/CMP3B/CN7/RB5 AN6/CMP3C/CMP4A/ Effective Address OSC1/CLKI/RB6 16 Data Latch AN7/CMP3D/CMP4B/ OSC2/CLKO/RB7 AN8/CMP4C/RB8 **ROM Latch** 16 AN9/EXTREF/CMP4D/RB9 24 AN10/IFLT4/RB10 Д AN11/IFLT2/RB11 IR **PORTB** 16 16 16 x 16 W Reg Array PGC2/EMUC2/OC1/IC1/INT1/ RD0 Decode Instruction OC2/RD1 16/16 Decode & PORTD Control Control Signals V V V V V to Various Blocks DSP Divide Power-up Engine Unit PWM1L/RE0 Timing Oscillator PWM1H/RE1 OSC1/CLK1 Generation tart-up Timer PWM2L/RE2 ALU<16> POR PWM2H/RE3 PWM3L/RE4 Reset PWM3H/RE5 16 Watchdog 46 MCLR PGC1/EMUC1/PWM4L/T1CK/ U1ARX/CN0/RE6 Timer PGD1/EMUD1/PWM4H/T2CK/ U1ATX/CN1/RE7 Input Output Comparator Capture  $I^2C^{TM}$ 10-bit ADC Compare Module U1RX/RF2 Module Module U1TX/RF3 PGD2/EMUD2/SCK1/INT2/RF6 PGC/EMUC/SDI1/RF7 PGD/EMUD/SD01/RF8 SYNCI/RF14 Input Power Supply SYNCO/SSI/RF15 Change SPI1 UART1 Timers PWM Notification SCL/RG2 SDA/RG3 **PORTG**

FIGURE 1-3: dsPIC30F2023 BLOCK DIAGRAM

Table 1-3 provides a brief description of device I/O pinouts for the dsPIC30F2023 and the functions that may be multiplexed to a port pin. Multiple functions may exist on one port pin. When multiplexing occurs, the peripheral module's functional requirements may force an override of the data direction of the port pin.

TABLE 1-3: PINOUT I/O DESCRIPTIONS FOR dsPIC30F2023

| Pin Name                                                                                  | Pin<br>Type                     | Buffer<br>Type                                 | Description                                                                                                                                                                                                                                                                                                                                                    |  |

|-------------------------------------------------------------------------------------------|---------------------------------|------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| AN0-AN11                                                                                  | ı                               | Analog                                         | Analog input channels.                                                                                                                                                                                                                                                                                                                                         |  |

| AVDD                                                                                      | Р                               | Р                                              | Positive supply for analog module.                                                                                                                                                                                                                                                                                                                             |  |

| AVss                                                                                      | Р                               | Р                                              | Ground reference for analog module.                                                                                                                                                                                                                                                                                                                            |  |

| CLKI                                                                                      | - 0                             | ST/CMOS<br>—                                   | External clock source input. Always associated with OSC1 pin function. Oscillator crystal output. Connects to crystal or resonator in Crystal Oscillator mode. Optionally functions as CLKO in RC and EC modes. Always associated with OSC2 pin function.                                                                                                      |  |

| EMUD<br>EMUC<br>EMUD1<br>EMUC1<br>EMUD2<br>EMUC2                                          | I/O<br>I/O<br>I/O<br>I/O<br>I/O | ST<br>ST<br>ST<br>ST<br>ST<br>ST               | ICD Primary Communication Channel data input/output pin. ICD Primary Communication Channel clock input/output pin. ICD Secondary Communication Channel data input/output pin. ICD Secondary Communication Channel clock input/output pin. ICD Tertiary Communication Channel data input/output pin. ICD Tertiary Communication Channel clock input/output pin. |  |

| IC1                                                                                       | I                               | ST                                             | Capture input.                                                                                                                                                                                                                                                                                                                                                 |  |

| INT0<br>INT1<br>INT2                                                                      | <br>                            | ST<br>ST<br>ST                                 | External interrupt 0 External interrupt 1 External interrupt 2                                                                                                                                                                                                                                                                                                 |  |

| SFLT1 SFLT2 SFLT3 SFLT4 IFLT2 IFLT4 PWM1L PWM1H PWM2L PWM2H PWM3L PWM3H PWM4H SYNCO SYNCI |                                 | ST<br>ST<br>ST<br>ST<br>ST<br>—<br>—<br>—<br>— | Shared Fault 2 Shared Fault 3 Shared Fault 4 Independent Fault 2 Independent Fault 4 PWM 1 Low output PWM 2 Low output PWM 2 High output PWM 3 Low output PWM 3 High output PWM 4 High output PWM 4 Low output PWM 5 High output PWM 6 High output PWM 6 High output PWM 7 High output PWM 8 High output PWM 8 High output PWM 8 SYNC output PWM SYNC input    |  |

| MCLR                                                                                      | I/P                             | ST                                             | Master Clear (Reset) input or programming voltage input. This pin is an active low Reset to the device.                                                                                                                                                                                                                                                        |  |

| OC1-OC2<br>OCFLTA                                                                         | 0<br>                           | —<br>ST                                        | Compare outputs. Output Compare Fault condition.                                                                                                                                                                                                                                                                                                               |  |

| OSC1<br>OSC2                                                                              | I<br>I/O                        | CMOS<br>—                                      | Oscillator crystal input. Oscillator crystal output. Connects to crystal or resonator in Crystal Oscillator mode. Optionally functions as CLKO in FRC and EC modes.                                                                                                                                                                                            |  |

Legend:CMOS=CMOS compatible input or outputAnalog=Analog inputST=Schmitt Trigger input with CMOS levelsO=Output

= Input P = Power

TABLE 1-3: PINOUT I/O DESCRIPTIONS FOR dsPIC30F2023 (CONTINUED)

|                        | ABLE 1-3. FINOUT I/O DESCRIPTIONS FOR USFICSOI 2023 (CONTINUED) |                |                                                                                                        |  |

|------------------------|-----------------------------------------------------------------|----------------|--------------------------------------------------------------------------------------------------------|--|

| Pin Name               | Pin<br>Type                                                     | Buffer<br>Type | Description                                                                                            |  |

| PGD                    | I/O                                                             | ST             | In-Circuit Serial Programming™ data input/output pin.                                                  |  |

| PGC                    | I                                                               | ST             | In-Circuit Serial Programming clock input pin.                                                         |  |

| PGD1                   | I/O                                                             | ST             | In-Circuit Serial Programming data input/output pin 1.                                                 |  |

| PGC1                   | I                                                               | ST             | In-Circuit Serial Programming clock input pin 1.                                                       |  |

| PGD2                   | I/O                                                             | ST             | In-Circuit Serial Programming data input/output pin 2.                                                 |  |

| PGC2                   | - 1                                                             | ST             | In-Circuit Serial Programming clock input pin 2.                                                       |  |

| RA8-RA11               | I/O                                                             | ST             | PORTA is a bidirectional I/O port.                                                                     |  |

| RB0-RB11               | I/O                                                             | ST             | PORTB is a bidirectional I/O port.                                                                     |  |

| RD0,RD1                | I/O                                                             | ST             | PORTD is a bidirectional I/O port.                                                                     |  |

| RE0-RE7                | I/O                                                             | ST             | PORTE is a bidirectional I/O port.                                                                     |  |

| RF2, RF3,              | I/O                                                             | ST             | PORTF is a bidirectional I/O port.                                                                     |  |

| RF6-RF8, RF14,<br>RF15 |                                                                 |                |                                                                                                        |  |

| RG2, RG3               | I/O                                                             | ST             | PORTG is a bidirectional I/O port.                                                                     |  |

| SCK1                   | I/O                                                             | ST             | Synchronous serial clock input/output for SPI #1.                                                      |  |

| SDI1                   | I                                                               | ST             | SPI #1 Data In.                                                                                        |  |

| SDO1                   | 0                                                               | _              | SPI #1 Data Out.                                                                                       |  |

| SS1                    | I                                                               | ST             | SPI #1 Slave Synchronization.                                                                          |  |

| SCL                    | I/O                                                             | ST             | Synchronous serial clock input/output for I <sup>2</sup> C.                                            |  |

| SDA                    | I/O                                                             | ST             | Synchronous serial data input/output for I <sup>2</sup> C.                                             |  |

| T1CK                   | I                                                               | ST             | Timer1 external clock input.                                                                           |  |

| T2CK                   | I                                                               | ST             | Timer2 external clock input.                                                                           |  |

| U1RX                   | I                                                               | ST             | UART1 Receive.                                                                                         |  |

| U1TX                   | 0                                                               | _              | UART1 Transmit.                                                                                        |  |

| U1ARX                  | I                                                               | ST             | Alternate UART1 Receive.                                                                               |  |

| U1ATX                  | 0                                                               | _              | Alternate UART1 Transmit                                                                               |  |

| CMP1A                  | I                                                               | Analog         | Comparator 1 Channel A                                                                                 |  |

| CMP1B                  | I                                                               | Analog         | Comparator 1 Channel B                                                                                 |  |

| CMP1C                  | - 1                                                             | Analog         | Comparator 1 Channel C                                                                                 |  |

| CMP1D                  | I                                                               | Analog         | Comparator 1 Channel D                                                                                 |  |

| CMP2A                  | I                                                               | Analog         | Comparator 2 Channel A                                                                                 |  |

| CMP2B                  | I                                                               | Analog         | Comparator 2 Channel B                                                                                 |  |

| CMP2C                  |                                                                 | Analog         | Comparator 2 Channel C                                                                                 |  |

| CMP2D                  |                                                                 | Analog         | Comparator 2 Channel D                                                                                 |  |

| CMP3A                  |                                                                 | Analog         | Comparator 3 Channel A                                                                                 |  |

| CMP3B                  |                                                                 | Analog         | Comparator 3 Channel B                                                                                 |  |

| CMP3C                  |                                                                 | Analog         | Comparator 3 Channel C                                                                                 |  |

| CMP3D                  |                                                                 | Analog         | Comparator 3 Channel D                                                                                 |  |

| CMP4A                  |                                                                 | Analog         | Comparator 4 Channel A                                                                                 |  |

| CMP4B                  |                                                                 | Analog         | Comparator 4 Channel B                                                                                 |  |

| CMP4C                  |                                                                 | Analog         | Comparator 4 Channel C                                                                                 |  |

| CMP4D                  |                                                                 | Analog         | Comparator 4 Channel D                                                                                 |  |

| CN0-CN7                | I                                                               | ST             | Input Change notification inputs  Can be software programmed for internal weak pull-ups on all inputs. |  |

| VDD                    | Р                                                               | _              | Positive supply for logic and I/O pins.                                                                |  |

| Vss                    | Р                                                               | _              | Ground reference for logic and I/O pins.                                                               |  |

| EXTREF                 | ı                                                               | Analog         | External reference to Comparator DAC                                                                   |  |

|                        | <u>'</u>                                                        | , widiog       | External following to comparation by to                                                                |  |

Legend:CMOS=CMOS compatible input or outputAnalog=Analog inputST=Schmitt Trigger input with CMOS levelsO=OutputI=InputP=Power

DS70000178D-page 18

# 2.0 CPU ARCHITECTURE OVERVIEW

**Note:** This data sheet summarizes features of this group of dsPIC30F devices and is not intended to be a complete reference source. For more information on the CPU, peripherals, register descriptions and general device functionality, refer to the "dsPIC30F Family Reference Manual" (DS70046). For more information on the device instruction set and programming, refer to the "dsPIC30F/33F Programmer's Reference Manual" (DS70157).

#### 2.1 Core Overview

The core has a 24-bit instruction word. The Program Counter (PC) is 23 bits wide with the Least Significant bit (LSb) always clear (see **Section 3.1 "Program Address Space"**), and the Most Significant bit (MSb) is ignored during normal program execution, except for certain specialized instructions. Thus, the PC can address up to 4M instruction words of user program space. An instruction prefetch mechanism is used to help maintain throughput. Program loop constructs, free from loop count management overhead, are supported using the DO and REPEAT instructions, both of which are interruptible at any point.

The working register array consists of 16x16-bit registers, each of which can act as data, address or offset registers. One working register (W15) operates as a software Stack Pointer for interrupts and calls.

The data space is 64 Kbytes (32K words) and is split into two blocks, referred to as X and Y data memory. Each block has its own independent Address Generation Unit (AGU). Most instructions operate solely through the X memory AGU, which provides the appearance of a single unified data space. The Multiply-Accumulate (MAC) class of dual source DSP instructions operate through both the X and Y AGUs, splitting the data address space into two parts (see Section 3.2 "Data Address Space"). The X and Y data space boundary is device-specific and cannot be altered by the user. Each data word consists of 2 bytes, and most instructions can address data either as words or bytes.

There are two methods of accessing data stored in program memory:

• The upper 32 Kbytes of data space memory can be mapped into the lower half (user space) of program space at any 16K program word boundary, defined by the 8-bit Program Space Visibility Page (PSVPAG) register. This lets any instruction access program space as if it were data space, with a limitation that the access requires an additional cycle. Moreover, only the lower 16 bits of each instruction word can be accessed using this method.

Linear indirect access of 32K word pages within program space is also possible using any working register, via table read and write instructions.

Table read and write instructions can be used to access all 24 bits of an instruction word.

Overhead-free circular buffers (modulo addressing) are supported in both X and Y address spaces. This is primarily intended to remove the loop overhead for DSP algorithms.

The X AGU also supports Bit-Reversed Addressing mode on destination effective addresses, to greatly simplify input or output data reordering for radix-2 FFT algorithms. Refer to **Section 4.0 "Address Generator Units"** for details on modulo and Bit-Reversed Addressing.

The core supports Inherent (no operand), Relative, Literal, Memory Direct, Register Direct, Register Indirect, Register Offset and Literal Offset Addressing modes. Instructions are associated with predefined Addressing modes, depending upon their functional requirements.

For most instructions, the core is capable of executing a data (or program data) memory read, a working register (data) read, a data memory write and a program (instruction) memory read per instruction cycle. As a result, 3-operand instructions are supported, allowing C = A + B operations to be executed in a single cycle.

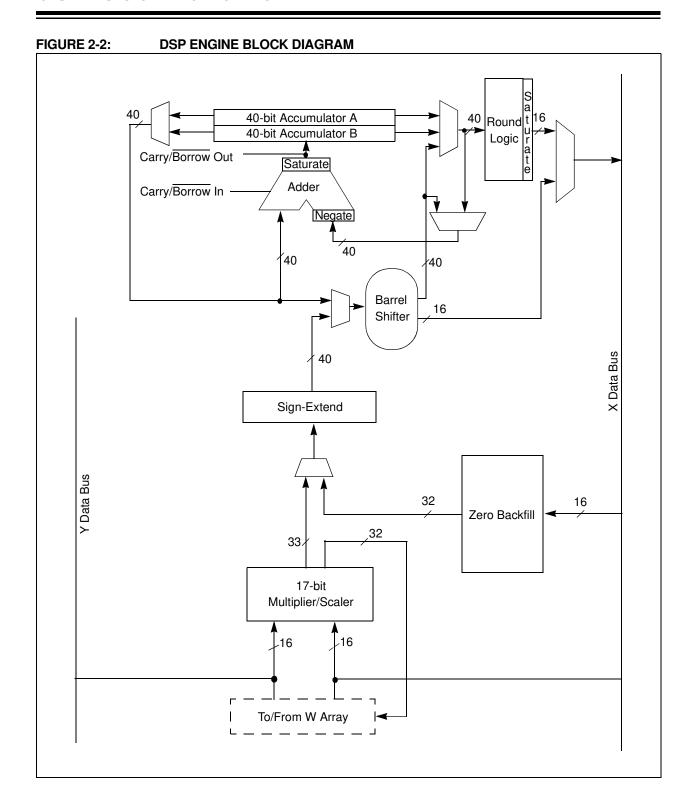

A DSP engine has been included to significantly enhance the core arithmetic capability and throughput. It features a high-speed 17-bit by 17-bit multiplier, a 40-bit ALU, two 40-bit saturating accumulators and a 40-bit bidirectional barrel shifter. Data in the accumulator or any working register can be shifted up to 15 bits right or 16 bits left in a single cycle. The DSP instructions operate seamlessly with all other instructions and have been designed for optimal real-time performance. The MAC class of instructions can concurrently fetch two data operands from memory, while multiplying two W registers. To enable this concurrent fetching of data operands, the data space has been split for these instructions and linear for all others. This has been achieved in a transparent and flexible manner, by dedicating certain working registers to each address space for the MAC class of instructions.

The core does not support a multi-stage instruction pipeline. However, a single stage instruction prefetch mechanism is used, which accesses and partially decodes instructions a cycle ahead of execution, in order to maximize available execution time. Most instructions execute in a single cycle, with certain exceptions.

The core features a vectored exception processing structure for traps and interrupts, with 62 independent vectors. The exceptions consist of up to 8 traps (of which 4 are reserved) and 54 interrupts. Each interrupt is prioritized based on a user-assigned priority between 1 and 7 (1 being the lowest priority and 7 being the highest) in conjunction with a predetermined 'natural order'. Traps have fixed priorities, ranging from 8 to 15.

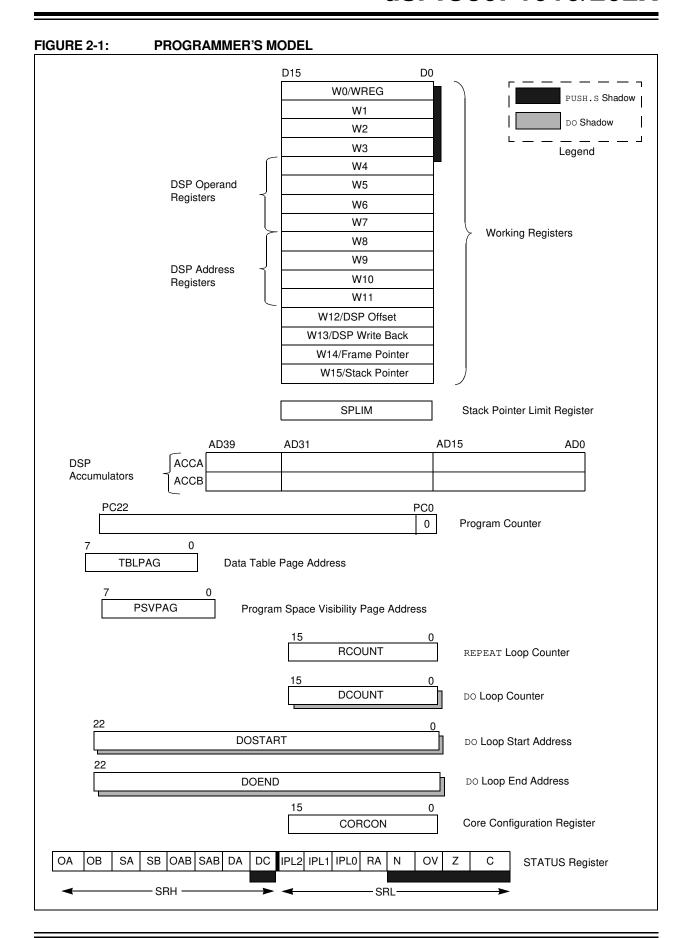

### 2.2 Programmer's Model

The programmer's model is shown in Figure 2-1 and consists of 16x16-bit working registers (W0 through W15), 2x40-bit accumulators (ACCA and ACCB), STATUS register (SR), Data Table Page register (TBLPAG), Program Space Visibility Page register (PSVPAG), DO and REPEAT registers (DOSTART, DOEND, DCOUNT and RCOUNT), and Program Counter (PC). The working registers can act as data, address or offset registers. All registers are memory mapped. W0 acts as the W register for file register addressing.

Some of these registers have a shadow register associated with each of them, as shown in Figure 2-1. The shadow register is used as a temporary holding register and can transfer its contents to or from its host register upon the occurrence of an event. None of the shadow registers are accessible directly. The following rules apply for transfer of registers into and out of shadows.

- PUSH.S and POP.S W0, W1, W2, W3, SR (DC, N, OV, Z and C bits only) are transferred.

- DO instruction

DOSTART, DOEND, DCOUNT shadows are

pushed on loop start, and popped on loop end.

When a byte operation is performed on a working register, only the Least Significant Byte (LSB) of the target register is affected. However, a benefit of memory mapped working registers is that both the Least and Most Significant Bytes (MSBs) can be manipulated through byte wide data memory space accesses.

### 2.2.1 SOFTWARE STACK POINTER/ FRAME POINTER

The dsPIC® DSC devices contain a software stack. W15 is the dedicated software Stack Pointer (SP), and will be automatically modified by exception processing and subroutine calls and returns. However, W15 can be referenced by any instruction in the same manner as all other W registers. This simplifies the reading, writing and manipulation of the Stack Pointer (e.g., creating stack frames).

**Note:** In order to protect against misaligned stack accesses, W15<0> is always clear.

W15 is initialized to 0x0800 during a Reset. The user may reprogram the SP during initialization to any location within data space.

W14 has been dedicated as a Stack Frame Pointer as defined by the LNK and ULNK instructions. However, W14 can be referenced by any instruction in the same manner as all other W registers.

### 2.2.2 STATUS REGISTER

The dsPIC DSC core has a 16-bit STATUS Register (SR), the LSB of which is referred to as the SR Low Byte (SRL) and the MSB as the SR High Byte (SRH). See Figure 2-1 for SR layout.

SRL contains all the MCU ALU operation status flags (including the Z bit), as well as the CPU Interrupt Priority Level Status bits, IPL<2:0>, and the REPEAT active Status bit, RA. During exception processing, SRL is concatenated with the MSB of the PC to form a complete word value, which is then stacked.

The upper byte of the STATUS register contains the DSP Adder/Subtracter status bits, the DO Loop Active bit (DA) and the Digit Carry (DC) Status bit.

#### 2.2.3 PROGRAM COUNTER

The Program Counter is 23 bits wide. Bit 0 is always clear. Therefore, the PC can address up to 4M instruction words.

# 2.3 Divide Support

The dsPIC DSC devices feature a 16/16-bit signed fractional divide operation, as well as 32/16-bit and 16/16-bit signed and unsigned integer divide operations, in the form of single instruction iterative divides. The following instructions and data sizes are supported:

- 1. DIVF 16/16 signed fractional divide

- 2. DIV.sd 32/16 signed divide

- 3. DIV.ud 32/16 unsigned divide

- 4. DIV.sw 16/16 signed divide

- 5. DIV.uw 16/16 unsigned divide

The 16/16 divides are similar to the 32/16 (same number of iterations), but the dividend is either zero-extended or sign-extended during the first iteration.

The divide instructions must be executed within a REPEAT loop. Any other form of execution (e.g. a series of discrete divide instructions) will not function correctly because the instruction flow depends on RCOUNT. The divide instruction does not automatically set up the RCOUNT value, and it must, therefore, be explicitly and correctly specified in the REPEAT instruction, as shown in Table 2-1 (REPEAT will execute the target instruction {operand value + 1} times). The REPEAT loop count must be set up for 18 iterations of the DIV/DIVF instruction. Thus, a complete divide operation requires 19 cycles.

**Note:** The Divide flow is interruptible. However, the user needs to save the context as appropriate.

TABLE 2-1: DIVIDE INSTRUCTIONS

| Instruction | Function                                                               |

|-------------|------------------------------------------------------------------------|

| DIVF        | Signed fractional divide: Wm/Wn $\rightarrow$ W0; Rem $\rightarrow$ W1 |

| DIV.sd      | Signed divide: (Wm + 1:Wm)/Wn $\rightarrow$ W0; Rem $\rightarrow$ W1   |

| DIV.ud      | Unsigned divide: (Wm + 1:Wm)/Wn → W0; Rem → W1                         |

| DIV.sw      | Signed divide: Wm/Wn $\rightarrow$ W0; Rem $\rightarrow$ W1            |

| DIV.uw      | Unsigned divide: Wm/Wn $\rightarrow$ W0; Rem $\rightarrow$ W1          |

# 2.4 DSP Engine

The DSP engine consists of a high speed 17-bit x 17-bit multiplier, a barrel shifter, and a 40-bit adder/subtracter (with two target accumulators, round and saturation logic).

The DSP engine also has the capability to perform inherent accumulator-to-accumulator operations, which require no additional data. These instructions are ADD, SUB and NEG.

The DSP engine has various options selected through various bits in the CPU Core Configuration Register (CORCON), as listed below:

- 1. Fractional or integer DSP multiply (IF).

- 2. Signed or unsigned DSP multiply (US).

- 3. Conventional or convergent rounding (RND).

- 4. Automatic saturation on/off for ACCA (SATA).

- 5. Automatic saturation on/off for ACCB (SATB).

- Automatic saturation on/off for writes to data memory (SATDW).

- Accumulator Saturation mode selection (ACCSAT).

**Note:** For CORCON layout, see Table 3-3.

A block diagram of the DSP engine is shown in Figure 2-2.

TABLE 2-2: DSP INSTRUCTION SUMMARY

| Instruction | Algebraic Operation | ACC WB? |

|-------------|---------------------|---------|