# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

FINAL DATASHEET

PLL Frequency Synthesizer with Integrated VCO

#### ADVANCED COMMUNICATIONS PRODUCT GROUP

#### Introduction

The ACS1790T is a high-performance, low phase noise, programmable frequency synthesizer with ultra-fine dynamic output frequency control. It can be used as a companion to a compatible ToPSync<sup>™</sup> device to generate outputs locked to an external reference source or standalone for standard frequency generation for common applications. The circuit includes an integrated VCO, loop filter, phase-and-frequency detector and output dividers. The default power-up mode is definable by pin settings and once operational the ACS1790T is fully-programmable via an I<sup>2</sup>C interface. The ACS1790T requires only a low-speed external clock input for operation.

When used in conjunction with a compatible ToPSync<sup>®</sup> device in a Synchronous Ethernet system the ACS1790T allows the Ethernet transmit clocks to be derived initially from the local reference oscillator and subsequently frequency-locked to an external reference source once the system is fully configured, simplifying system design and reducing component count and BOM cost.

#### Features

- Optimised for Synchronous Ethernet, SONET and SDH operation

- Meets RMS jitter requirements of Gigabit Ethernet, 10 Gigabit Ethernet and OC-48 / STM-16

- Default options for 25 MHz & 125 MHz or 25 MHz & 156.25 MHz outputs at reset

- High frequency LVPECL output: 10 MHz – 200 MHz, 1 ppb step

- Low frequency LVCMOS output: 2 kHz – 125 MHz 1.8V, 2.5V and 3.3V operation

- Very-low frequency feedback clock output for connection to ToPSync® or external PFD

- Tunable over +/- 500 ppm range without loss of lock

- Integrated VCO, PFD and loop filter

- 2.3 2.7 GHz VCO frequency

- Typical RMS jitter performance for target application masks: OC-48, STM-16 (ANSI T1.105.03 & ITU-T G.813) 0.56 ps (12 kHz - 20 MHz)

1G Ethernet (IEEE 802.3-2008 38 & 39) 0.15 ps (637 kHz - 20 MHz)

XAUI (IEEE 802.3-2008 Clause 47) 0.11 ps (1.875 MHz - 20 MHz)

10G Ethernet (IEEE 802.3-2008 53 & 54) 0.29 ps (4 MHz - 80 MHz)

- Reference spurs: < -67 dBc</li>

- 10, 12.8, 20 or 25 MHz input clock

- Operating voltage: 3.0 3.6V

- I<sup>2</sup>C -bus interface

- Four selectable slave addresses to allow multiple devices to be used with a single controlling master

- Lock detect output

- Pin and register output enable control

- Temperature range: -40 to 85C

- 4 x 4 mm QFN 24 package

- Pb-Free, Halogen free, RoHS/WEEE compliant product

### ADVANCED COMMUNICATIONS PRODUCT GROUP

### FINAL DATASHEET

# **Table of Contents**

| PIN DIAGRAM       1         FEATURES       1         BLOCK DAGRAM       5         PIN DESCRIPTION       6         DEVICE OPERATION       7         ThE COUPTOR DIVER BLOCK       7         The COUPTOR DIVER BLOCK       7         The COUPTOR DIVER BLOCK       8         THE COUPTOR STAGE       8         THE COUPTOR BLOCK       8         THE COUPTOR BLOCK       8         Reset       9         USING THE ACS1790T       9         HARDWARE DEVICE CONFIGURATION       9         Input Clock frequency selection       9         Input Clock frequency selection       10         PC Stave address selection       10         PC Stave address selection       10         PC Stave address selection       11         PC Register map       12         Register map       12         Register map       13         VOC OLIBRATION AND LOCK DETECTION       18         The OUT SLEW MATE CONTROL       19         OUT1 and OUT2       19         OUT1 and OUT2       19         OUT1 and OUT2       19         OUT1 and OUT2       21         MAXMUM RATINGS                                                                                                                                            | INTRODUCTION                       | 1  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|----|

| BLOCK DIAGRAM       5         PIN DESCRIPTION       6         DEVICE OPERATION       7         The VCO PLL BLOCK       7         The VCO PLL BLOCK       7         The OUTPOT STAGE       8         THE OUTPOT STACE       8         THE OUTPOT STACE       8         THE OUTPOT STACE       9         USING THE ACS1790T       9         HAROWARE DEVICE CONFIGURATION       9         Input clock frequency selection       9         Input clock frequency selection       10         Reset       11         I/C Flave address selection       10         I/C Stave address selection       10         I/C Read       11         I/C Read       12         Register Descriptions       12         OUTT UT ENABLE CONTROL AND SQUELCHING       19         OUTT 2 SUE-ATE AND VOLTAGE CONTROL       20         PEGLK       19         OUTT 2 SUE-ATE AND VOLTAGE CONTROL       20         ELECTRICAL SPECIFICATIONS       21         OUTT 2 SUE-ATE AND VOLTAGE CO                                                                                                                                   | PIN DIAGRAM                        | 1  |

| PIN DESCRIPTION       6         DEVICE OPERATION       7         The VCO PLL BLOCK       7         The OUTPUT DWIDER BLOCK       8         THE OUTPUT STARE       8         THE CONTROL BLOCK       8         Reset       9         USING THE ACS1790T       9         HARDWARE DEVICE CONFIGURATION       9         Input clock frequency selection       9         Default output frequency selection       10         I <sup>2</sup> C slave address selection       10         I <sup>2</sup> C slave address selection       10         I <sup>2</sup> C Read       11         Register map       12         Register Descriptions       13         VCO CALIBRATION AND LOCK DETECTION       18         OUTT and OUT2       19         FRACTIONAL DWIDER DIFERING       18         OUTT and OUT2       19         OUT2 SLEW-RATE AND VOLTAGE CONTROL       20         ELECTRICAL SPECIFICATIONS       21         MAXIMUM RATINGS       21         OPERATING CONDITIONS       22         REQUENTIONS INFORMATION       28         USING THE ACS1790T TIM A STANDALOR APPLICATION       28         USING THE ACS179OT TIM A STANDALOR APPLICATION       28 </td <td>FEATURES</td> <td>1</td>               | FEATURES                           | 1  |

| PIN DESCRIPTION       6         DEVICE OPERATION       7         The VCO PLL BLOCK       7         The OUTPUT DWIDER BLOCK       8         THE OUTPUT STARE       8         THE CONTROL BLOCK       8         Reset       9         USING THE ACS1790T       9         HARDWARE DEVICE CONFIGURATION       9         Input clock frequency selection       9         Default output frequency selection       10         I <sup>2</sup> C slave address selection       10         I <sup>2</sup> C slave address selection       10         I <sup>2</sup> C Read       11         Register map       12         Register Descriptions       13         VCO CALIBRATION AND LOCK DETECTION       18         OUTT and OUT2       19         FRACTIONAL DWIDER DIFERING       18         OUTT and OUT2       19         OUT2 SLEW-RATE AND VOLTAGE CONTROL       20         ELECTRICAL SPECIFICATIONS       21         MAXIMUM RATINGS       21         OPERATING CONDITIONS       22         REQUENTIONS INFORMATION       28         USING THE ACS1790T TIM A STANDALOR APPLICATION       28         USING THE ACS179OT TIM A STANDALOR APPLICATION       28 </td <td>BLOCK DIAGRAM</td> <td>5</td>          | BLOCK DIAGRAM                      | 5  |

| DEVICE OPERATION       7         THE VCO PLL BLOCK       7         THE OUTPUT DWIDER BLOCK       8         THE OUTPUT STARE       8         THE CONTROL BLOCK       8         Reset       9         USING THE ACS1790T       9         HARDWARE DEVICE CONFIGURATION       9         Input clock frequency selection       9         Default output frequency selection       10         I/2 stave address selection       10         I/2 stave address selection       10         I/2 read       11         Register Map       12         Register Desciptions       13         VCO CLIBRATION AND LOCK DETECTION       18         OUTUT ENABLE CONTROL AND SQUELCHING       19         OUTUT ENABLE CONTROL AND SQUELCHING       19         OUTUT AND OUTZ       19         OUTU 1 and OUTZ       19         OUTU 2 SLEW-RATE AND VOLTAGE CONTROL       20         ELECTRICAL SPECIFICATIONS       21         MAXIMUM RATINGS       21         OPERATING CONDITION       22         USING THE ACS1790T WITH TOPSYNC       28         USING THE ACS179OT WITH TOPSYNC       28         USING THE ACS179OT WITH TOPSYNC       28                                                                              | PIN DESCRIPTION                    | 6  |

| THE VCO PLL BLOCK       7         THE OUTPUT DWDER BLOCK.       8         THE OUTPUT STAGE.       8         THE CONTROL BLOCK       8         Reset       9         USING THE ACS1790T       9         HARDWARE DEVICE CONFIGURATION.       9         Default output frequency selection       9         Default output frequency selection       10         RCSISTER-BASED DEVICE CONFIGURATION       10         I'C Silver address selection       10         I'C Write       11         I'C Read       11         Register map       12         Register map       13         VCO CALIBRATION AND LOCK DETECTION       18         OutPut Fraue Controls and Squelching       19         OUT1 and OUT2       19         FECLK       19         OUT2 SLEW-RATE AND VOLTAGE CONTROL       20         ELECTRICAL SPECIFICATIONS       21         DeFATING CONDITIONS       21         DEFATING CONDITIONS       21         DC CHARACTERISTICS       21         MAXIMUM RATINGS       21         OPERATING CONDITIONS       22         USING THE ACS1790T IN A STATIO APPLICATION       30         USING THE ACS                                                                                                |                                    |    |

| THE OUTPUT DIVIDER BLOCK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                    |    |

| THE OUTPUT STAGE       8         THE CONTROL BLOCK       8         Reset       9         USING THE ACS1790T       9         HARDWARE DEVICE CONFIGURATION       9         Input clock frequency selection       10         PC slave address selection       10         I <sup>2</sup> C Write       11         I <sup>2</sup> C Read       13         VCO CALIBRATION AND LOCK DETECTION       18         FRACTIONAL DIVIER DITHERING       19         OUTPUT ENABLE CONTROL AND SQUELCHING       19         OUT1 and OUT2       19         FBCLK       19         OUT2 LEW-PATE AND VOLTAGE CONTROL       20         ELECTRICAL SPECIFICATIONS       21         OPERATING CONDITI |                                    |    |

| Reset       9         USING THE ACS1790T       99         HARDWARE DEVICE CONFIGURATION       9         Input clock frequency selection       9         Default output frequency selection       10         Resister PassED DEVICE CONFIGURATION       10         IPC slave address selection       10         IPC Read       11         IPC Read       11         Register map       12         Register map       12         Register Descriptions       13         VCO CALIBRATION AND LOCK DETECTION       18         FRACTIONAL DIVICEND DITHERING       18         OUTPUT ENABLE CONTROL AND SQUELCHING       19         OUT1 and OUT2       19         FBCLK       19         OUT2 SLEW-RATE AND VOLTAGE CONTROL       20         ELECTRICAL SPECIFICATIONS       21         DOFERATING CONDITIONS       21         DC CHARACTERISTICS       22         RF CHARACTERISTICS       22         RF CHARACTERISTICS       24         APPLICATIONS INFORMATION       28         USING THE ACS1790T WITH TOPSYNC       28         USING THE ACS1790T WITH TOPSYNC       28         USING THE ACS1790T IN A STANDALONE APPLICATION                                                                             |                                    |    |

| USING THE AC\$1790T       9         HARDWARE DEVICE CONFIGURATION       9         Input clock frequency selection       9         Default output frequency selection       10         REGISTER-BASED DEVICE CONFIGURATION       10         IPC Stave address selection       10         IPC Krite       11         IPC Read       11         IPC Read       11         Register map       12         Register map       12         Register Descriptions       13         VCO CAUBRATION AND LOCK DETECTION       18         FRACTIONAL DIVIDER DITHERING       19         OUT1 and OUT2       19         FBCLK       19         OUT2 SLEW-RATE AND VOLTAGE CONTROL       20         ELECTRICAL SPECIFICATIONS       21         MAXIMUM RATINGS       21         OPERATING CONDITIONS       21         OPERATING CONDITIONS       22         RF CHARACTERISTICS       24         APLICATIONS INFORMATION       28         USING THE ACS1790T WITH TOPSYNC       28         USING THE ACS1790T WITH TOPSYNC       28         USING THE ACS1790T WITH TOPSYNC       28         USING THE ACS1790T NITH A STANDALONE APPLICATION       30 <td>THE CONTROL BLOCK</td> <td>8</td>                                  | THE CONTROL BLOCK                  | 8  |

| HARDWARE DEVICE CONFIGURATION       9         Input clock frequency selection       9         Default output frequency selection       10         Resister Assed Device CONFIGURATION       10         IPC virte       10         IPC Read       11         IPC Read       11         IPC Read       11         Register Descriptions       13         VCO CALIBRATION AND LOCK DETECTION       18         OUTPUT ENABLE CONTROL AND SQUELCHING       19         OUT1 and OUT2       19         FBCLK       19         OUT2 SLEW-RATE AND VOLTAGE CONTROL       20         ELECTRICAL SPECIFICATIONS       21         MAXIMUM RATINGS       21         DOFERATIONS       21         DC CHARACTERISTICS       21         DC CHARACTERISTICS       21         DC CHARACTERISTICS       22         R FULCATIONS INFORMATION       28         USING THE ACS1790T WITH TOPSYNC       28         USING THE ACS1790T IN A STANDALONE APPLICATION       30                                                            | Reset                              | 9  |

| Input clock frequency selection9Default output frequency selection10RecistER-BASED DEVICE CONFIGURATION10IPC Write10IPC Write11IPC Read11Register map12Register Descriptions13VCO CALIBRATION AND LOCK DETECTION18FRACTIONAL DIVDER DIFFERING19OUT1 and OUT219OUT2 SLEW-RATE AND VOLTAGE CONTROL20ELECTRICAL SPECIFICATIONS21MAXIMUM RATINGS21OPERATING CONDITIONS21DC CHARACTERISTICS21DC CHARACTERISTICS22RF CHARACTERISTICS21DC CHARACTERISTICS22RF CHARACTERISTICS22RF CHARACTERISTICS22RF CHARACTERISTICS24APPLICATIONS INFORMATION30USING THE ACS1790T WITH TOPSYNC28USING THE ACS1790T IN A STANDALONE APPLICATION30COKINGURATION FOR A PARTICULAR OUTPLIFREQUENCY31Programming for the OUT1 output31Programming for the OUT1 output35Programming to use both outputs37                                                                                                                                                                                                                                                                                                                                                                                                                                | USING THE ACS1790T                 | 9  |

| Default output frequency selection10Register-BASED DEVICE CONFIGURATION10I²C slave address selection10I²C Write11I²C Read11I²C Read11Register map12Register map13VCO calibration AND LOCK DETECTION18FRACTIONAL DIVIDER DITHERING18OUTU TENABLE CONTROL AND SQUELCHING19OUT1 and OUT219FBCLK19OUT2 SLEW-RATE AND VOLTAGE CONTROL20ELECTRICAL SPECIFICATIONS21MAXIMUM RATINGS21OPERATING CONDITIONS21DC CHARACTERISTICS22RF CHARACTERISTICS24APPLICATIONS INFORMATION28USING THE ACS179OT WITH TOPSYNC28USING THE ACS179OT WITH TOPSYNC28USING THE ACS179OT IN A STANDALONE APPLICATION30USING THE ACS179OT IN A STANDALONE APPLICATION30Second USING THE                                                      |                                    |    |

| Register-BASED DeVICE CONFIGURATION       10         I²C slave address selection       10         I²C Write       11         I²C Read       11         I²C Read       11         Register map       12         Register Descriptions       13         VCO CALIBRATION AND LOCK DETECTION       18         FRACTIONAL DIVIDER DITHERING       18         OUTPUT ENABLE CONTROL AND SQUELCHING       19         OUT1 and OUT2       19         OUT2 SLEW-RATE AND VOLTAGE CONTROL       20         ELECTRICAL SPECIFICATIONS       21         MAXIMUM RATINGS       21         OPERATING CONDITIONS       21         DC CHARACTERISTICS       22         RF CHARACTERISTICS       22         RF CHARACTERISTICS       24         APPLICATIONS INFORMATION       28         USING THE ACS179OT WITH TOPSYNC       28         USING THE ACS179OT IN A STANDALONE APPLICATION       30         USING THE ACS179OT IN A ST                          |                                    |    |

| I <sup>2</sup> C slave address selection       10         I <sup>2</sup> C Write       11         I <sup>2</sup> C Read       11         Register map       12         Register Descriptions       13         VCO CALIBRATION AND LOCK DETECTION       18         FRACTIONAL DIVORE DITHERING       18         OUTPUT ENABLE CONTROL AND SQUELCHING       19         OUT1 and OUT2       19         FBCLK       19         OUT2 SLEW-RATE AND VOLTAGE CONTROL       20         ELECTRICAL SPECIFICATIONS       21         MAXIMUM RATINGS       21         OPERATING CONDITIONS       21         OPERATING CONDITIONS       21         OPERATING CONDITIONS       21         OPERATING SINFORMATION       22         RF CHARACTERISTICS       22         RF CHARACTERISTICS       24         APPLICATIONS INFORMATION       28         USING THE ACS179OT WITH TOPSYNC       28         USING THE ACS179OT IN A STANDALONE APPLICATION       30         USING THE ACS179OT NA STANDALONE APPLICATION       30         USING THE ACS179OT IN A STANDALONE APPLICATION       30         USING THE ACS179OT IN A STANDALONE APPLICATION       30         USING THE ACS179OT IN A STANDALONE APPLICATION       3  |                                    |    |

| IPC Write       11         IPC Read       11         Register map       12         Register Descriptions       13         VCO CALIBRATION AND LOCK DETECTION       18         FRACTIONAL DIVIDER DITHERING       18         OUTPUT ENABLE CONTROL AND SQUELCHING       19         OUT1 and OUT2       19         FBCLK       19         OUT2 SLEW-RATE AND VOLTAGE CONTROL       20         ELECTRICAL SPECIFICATIONS       21         MAXIMUM RATINGS       21         OPERATING CONDITIONS       21         DC CHARACTERISTICS       21         DC CHARACTERISTICS       21         DC CHARACTERISTICS       22         RF CHARACTERISTICS       22         RF CHARACTERISTICS       22         USING THE ACS1790T WITH TOPSYNC       28         USING THE ACS1790T WITH TOPSYNC       28         USING THE ACS1790T NA STANDALONE APPLICATION       30         USING THE ACS1790T WITH TOPSYNC       28                                            |                                    |    |

| IPC Read11Register map12Register Descriptions13VCO CALIBRATION AND LOCK DETECTION18FRACTIONAL DIVIDER DITHERING18OUTPUT ENABLE CONTROL AND SQUELCHING19OUT1 and OUT219PBCLK19OUT2 SLEW-RATE AND VOLTAGE CONTROL20ELECTRICAL SPECIFICATIONS21MAXIMUM RATINGS21OPERATING CONDITIONS21DC CHARACTERISTICS21DC CHARACTERISTICS22RF CHARACTERISTICS22RF CHARACTERISTICS24APPLICATIONS INFORMATION28USING THE ACS1790T WITH TOPSYNC28USING THE ACS1790T N A STANDALONE APPLICATION30USING THE ACS1790T N A STANDALONE APPLICATION31Programming for the OUT1 output31Programming for the OUT2 output35Programming for the OUT2 output35Programming to use both outputs37                                                                                                                                                                                                                                                                                                                                                                                                 |                                    |    |

| Register map12Register Descriptions.13VCO CALIBRATION AND LOCK DETECTION18FRACTIONAL DIVIDER DITHERING.18OUTPUT ENABLE CONTROL AND SQUELCHING.19OUT1 and OUT2.19FBCLK19OUT2 SLEW-RATE AND VOLTAGE CONTROL20ELECTRICAL SPECIFICATIONS.21MAXIMUM RATINGS.21OPERATING CONDITIONS.21DC CHARACTERISTICS22RF CHARACTERISTICS22RF CHARACTERISTICS24APPLICATIONS INFORMATION28USING THE ACS179OT WITH TOPSYNC28USING THE ACS179OT WITH TOPSYNC30CONFIGURATION NA STANDALONE APPLICATION30CONFIGURATION FOR APARTICULAR OUTPUT FREQUENCY31Programming for the OUT1 output31Programming for the OUT2 output35Programming to use both outputs37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                    |    |

| Register Descriptions       13         VCO caliBration and Lock DETECTION       18         Fractional Divider Dithering       18         OUTPUT ENABLE CONTROL AND SQUELCHING       19         OUT1 and OUT2       19         FBCLK       19         OUT2 SLEW-RATE AND VOLTAGE CONTROL       20         ELECTRICAL SPECIFICATIONS       21         MAXIMUM RATINGS       21         OPERATING CONDITIONS       21         DC CHARACTERISTICS       22         RF CHARACTERISTICS       22         RF CHARACTERISTICS       22         RF CHARACTERISTICS       24         APPLICATIONS INFORMATION       28         USING THE ACS1790T WITH TOPSYNC       28         USING THE ACS1790T IN A STANDALONE APPLICATION       30         CONFIGURATION FOR A PARTICULAR OUTPUT FREQUENCY       31         Programming for the OUT1 output       31         Programming for the OUT2 output       35         Programming to use both outputs       37                                                                                                                                                                                                                                                             |                                    |    |

| VCO CALIBRATION AND LOCK DETECTION18FRACTIONAL DIVIDER DITHERING18OUTPUT ENABLE CONTROL AND SQUELCHING19OUT1 and OUT219FBCLK19OUT2 SLEW-RATE AND VOLTAGE CONTROL20ELECTRICAL SPECIFICATIONS21MAXIMUM RATINGS21OPERATING CONDITIONS21DC CHARACTERISTICS22RF CHARACTERISTICS22RF CHARACTERISTICS24APPLICATIONS INFORMATION28USING THE ACS1790T WITH TOPSYNC28USING THE ACS1790T IN A STANDALONE APPLICATION30CONFIGURATION FOR A PART OF A PHASE-LOCKED LOOP30CONFIGURATION FOR A PARTICULAR OUTPUT FREQUENCY.31Programming for the OUT1 output.35Programming for the OUT2 output.35Programming to use both outputs37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                    |    |

| FRACTIONAL DIVIDER DITHERING.18OUTPUT ENABLE CONTROL AND SQUELCHING19OUT1 and OUT2.19FBCLK19OUT2 SLEW-RATE AND VOLTAGE CONTROL.20ELECTRICAL SPECIFICATIONS.21MAXIMUM RATINGS.21OPERATING CONDITIONS21DC CHARACTERISTICS.21DC CHARACTERISTICS22RF CHARACTERISTICS24APPLICATIONS INFORMATION.28USING THE ACS1790T WITH TOPSYNC28USING THE ACS1790T IN A STANDALONE APPLICATION30USING THE ACS1790T AS PART OF A PHASE-LOCKED LOOP.30CONFIGURATION FOR A PARTICULAR OUTPUT FREQUENCY.31Programming for the OUT1 output.31Programming for the OUT2 output.35Programming to use both outputs37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                    |    |

| OUTPUT ENABLE CONTROL AND SQUELCHING19OUT1 and OUT219FBCLK19OUT2 SLEW-RATE AND VOLTAGE CONTROL20ELECTRICAL SPECIFICATIONS21MAXIMUM RATINGS21OPERATING CONDITIONS21DC CHARACTERISTICS21DC CHARACTERISTICS22RF CHARACTERISTICS22RF CHARACTERISTICS24APPLICATIONS INFORMATION28USING THE ACS1790T WITH TOPSYNC28USING THE ACS1790T IN A STANDALONE APPLICATION30USING THE ACS1790T AS PART OF A PHASE-LOCKED LOOP30CONFIGURATION FOR A PARTICULAR OUTPUT FREQUENCY31Programming for the OUT1 output31Programming for the OUT2 output35Programming to use both outputs37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                    |    |

| OUT1 and OUT219FBCLK19OUT2 SLEW-RATE AND VOLTAGE CONTROL20ELECTRICAL SPECIFICATIONS21MAXIMUM RATINGS21OPERATING CONDITIONS21DC CHARACTERISTICS21DC CHARACTERISTICS22RF CHARACTERISTICS22RF CHARACTERISTICS24APPLICATIONS INFORMATION28USING THE ACS1790T WITH TOPSYNC28USING THE ACS1790T WITH TOPSYNC28USING THE ACS1790T IN A STANDALONE APPLICATION30USING THE ACS1790T AS PART OF A PHASE-LOCKED LOOP30CONFIGURATION FOR A PARTICULAR OUTPUT FREQUENCY31Programming for the OUT1 output31Programming for the OUT2 output35Programming to use both outputs37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                    |    |

| FBCLK19OUT2 SLEW-RATE AND VOLTAGE CONTROL20ELECTRICAL SPECIFICATIONS21MAXIMUM RATINGS21OPERATING CONDITIONS21DC CHARACTERISTICS21DC CHARACTERISTICS22RF CHARACTERISTICS24APPLICATIONS INFORMATION28USING THE ACS1790T WITH TOPSYNC28USING THE ACS1790T WITH TOPSYNC28USING THE ACS1790T IN A STANDALONE APPLICATION30USING THE ACS1790T IN A STANDALONE APPLICATION30Programming for the OUT1 output31Programming for the OUT1 output35Programming to use both outputs37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | •                                  |    |

| ELECTRICAL SPECIFICATIONS21MAXIMUM RATINGS21OPERATING CONDITIONS21DC CHARACTERISTICS22RF CHARACTERISTICS22RF CHARACTERISTICS24APPLICATIONS INFORMATION28USING THE ACS1790T WITH TOPSYNC28USING THE ACS1790T IN A STANDALONE APPLICATION30USING THE ACS1790T AS PART OF A PHASE-LOCKED LOOP30CONFIGURATION FOR A PARTICULAR OUTPUT FREQUENCY31Programming for the OUT1 output31Programming for the OUT2 output35Programming to use both outputs37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                    |    |

| Maximum Ratings21OPERATING CONDITIONS21DC CHARACTERISTICS22RF CHARACTERISTICS24APPLICATIONS INFORMATION28USING THE ACS1790T WITH TOPSYNC28USING THE ACS1790T IN A STANDALONE APPLICATION30USING THE ACS1790T A SPART OF A PHASE-LOCKED LOOP30CONFIGURATION FOR A PARTICULAR OUTPUT FREQUENCY31Programming for the OUT1 output31Programming for the OUT2 output35Programming to use both outputs37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | OUT2 SLEW-RATE AND VOLTAGE CONTROL |    |

| OPERATING CONDITIONS21DC CHARACTERISTICS22RF CHARACTERISTICS24APPLICATIONS INFORMATION28USING THE ACS1790T WITH TOPSYNC28USING THE ACS1790T IN A STANDALONE APPLICATION30USING THE ACS1790T AS PART OF A PHASE-LOCKED LOOP30CONFIGURATION FOR A PARTICULAR OUTPUT FREQUENCY31Programming for the OUT1 output31Programming for the OUT2 output35Programming to use both outputs37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ELECTRICAL SPECIFICATIONS          |    |

| OPERATING CONDITIONS21DC CHARACTERISTICS22RF CHARACTERISTICS24APPLICATIONS INFORMATION28USING THE ACS1790T WITH TOPSYNC28USING THE ACS1790T IN A STANDALONE APPLICATION30USING THE ACS1790T AS PART OF A PHASE-LOCKED LOOP30CONFIGURATION FOR A PARTICULAR OUTPUT FREQUENCY31Programming for the OUT1 output31Programming for the OUT2 output35Programming to use both outputs37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                    | 21 |

| RF CHARACTERISTICS24APPLICATIONS INFORMATION28USING THE ACS1790T WITH TOPSYNC28USING THE ACS1790T IN A STANDALONE APPLICATION30USING THE ACS1790T AS PART OF A PHASE-LOCKED LOOP.30CONFIGURATION FOR A PARTICULAR OUTPUT FREQUENCY.31Programming for the OUT1 output31Programming for the OUT2 output35Programming to use both outputs37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                    |    |

| APPLICATIONS INFORMATION.       28         USING THE ACS1790T WITH TOPSYNC       28         USING THE ACS1790T IN A STANDALONE APPLICATION       30         USING THE ACS1790T AS PART OF A PHASE-LOCKED LOOP.       30         CONFIGURATION FOR A PARTICULAR OUTPUT FREQUENCY.       31         Programming for the OUT1 output.       31         Programming for the OUT2 output.       35         Programming to use both outputs       37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | DC CHARACTERISTICS                 |    |

| USING THE ACS1790T WITH TOPSYNC       28         USING THE ACS1790T IN A STANDALONE APPLICATION       30         USING THE ACS1790T AS PART OF A PHASE-LOCKED LOOP.       30         CONFIGURATION FOR A PARTICULAR OUTPUT FREQUENCY.       31         Programming for the OUT1 output       31         Programming for the OUT2 output       35         Programming to use both outputs       37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | RF CHARACTERISTICS                 | 24 |

| USING THE ACS1790T IN A STANDALONE APPLICATION       30         USING THE ACS1790T AS PART OF A PHASE-LOCKED LOOP.       30         CONFIGURATION FOR A PARTICULAR OUTPUT FREQUENCY.       31         Programming for the OUT1 output       31         Programming for the OUT2 output       35         Programming to use both outputs       37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | APPLICATIONS INFORMATION           |    |

| USING THE ACS1790T AS PART OF A PHASE-LOCKED LOOP.       30         CONFIGURATION FOR A PARTICULAR OUTPUT FREQUENCY.       31         Programming for the OUT1 output.       31         Programming for the OUT2 output.       35         Programming to use both outputs       37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | USING THE ACS1790T WITH TOPSYNC    |    |

| CONFIGURATION FOR A PARTICULAR OUTPUT FREQUENCY.       31         Programming for the OUT1 output       31         Programming for the OUT2 output       35         Programming to use both outputs       37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                    |    |

| Programming for the OUT1 output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                    |    |

| Programming for the OUT2 output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | •                                  |    |

| Programming to use both outputs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                    |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                    |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                    |    |

| Configuration for common output frequencies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                    |    |

FINAL DATASHEET

# SEMTECH

### ADVANCED COMMUNICATIONS PRODUCT GROUP

| DESIGN CONSIDERATIONS<br>PCB placement | 43<br>43 |

|----------------------------------------|----------|

| Output clock termination               | 43       |

| Power supplies and filtering           |          |

| APPLICATION EXAMPLE                    | 45       |

| PACKAGING INFORMATION                  | 46       |

| REVISION STATUS/ HISTORY               | 47       |

| DRDERING INFORMATION                   | 48       |

| DISCLAIMERS<br>CONTACTS                | 48<br>48 |

# **List of Tables**

| Table 1 : ACS1790T Pin Description                                             | 6 |

|--------------------------------------------------------------------------------|---|

| Table 2 : Input Clock Frequency Selection                                      | 9 |

| Table 3 : Default Output Frequency Selection                                   |   |

| Table 4 : I <sup>2</sup> C Interface Slave Address Selection                   |   |

| Table 5 : ACS1790T Register Map                                                |   |

| Table 6 : OUT1 and OUT2 Output Control                                         |   |

| Table 7 : FBCLK Output Control                                                 |   |

| Table 8 : OUT2 Drive-Type Setting                                              |   |

| Table 9 : Absolute Maximum Ratings                                             |   |

| Table 10 : Operating Conditions                                                |   |

| Table 11 : DC Characteristics                                                  |   |

| Table 12 : RF Characteristics                                                  |   |

| Table 13 : I <sup>2</sup> C Timing Specification                               |   |

| Table 14 : OUT1 Output Division Ratios                                         |   |

| Table 15 : VCO PLL Prescaler Division Ratios                                   |   |

| Table 16 : VCO PLL Reference Frequencies                                       |   |

| Table 17 : Register Settings for 155.52 MHz Output                             |   |

| Table 18 : OUT2 Output Division Ratios                                         |   |

| Table 19 : Register Settings for 10.24 MHz Output                              |   |

| Table 20 : Register Settings for Ethernet (25MHz input)                        |   |

| Table 21 : Feedback Clock Output Division Ratios                               |   |

| Table 22 : Register Settings for Common Frequencies (Input clock 10 or 20 MHz) |   |

| Table 23 : Register Settings for Common Frequencies (Input clock 12.8 MHz)     |   |

| Table 24 : Register Settings for Common Frequencies (Input clock 25 MHz)       |   |

| Table 25 : Ordering Information                                                |   |

FINAL DATASHEET

### ADVANCED COMMUNICATIONS PRODUCT GROUP

# **List of Figures**

| Figure 1 : ACS1790T Block Diagram                                                        | 5  |

|------------------------------------------------------------------------------------------|----|

| Figure 2 : ACS1790T VC0 PLL                                                              | 7  |

| Figure 3 : ACS1790T Output Divider Structure                                             | 8  |

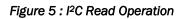

| Figure 4 : I <sup>2</sup> C Write Operation                                              |    |

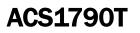

| Figure 5 : I <sup>2</sup> C Read Operation                                               |    |

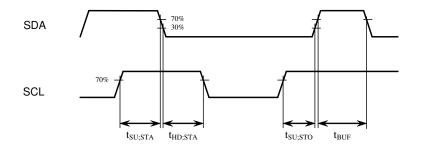

| Figure 6 : I <sup>2</sup> C Start and Stop Timing                                        |    |

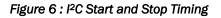

| Figure 7 : I <sup>2</sup> C Data Timing                                                  | 25 |

| Figure 8 : OUT1 Phase Noise (fin = 12.8 MHz, fout = 155.52 MHz)                          |    |

| Figure 9 : OUT1 Phase Noise (fin = 12.8 MHz, fout = 125 MHz)                             |    |

| Figure 10 : OUT1 Phase Noise (f <sub>in</sub> = 12.8 MHz, f <sub>out</sub> = 156.25 MHz) |    |

| Figure 11 : OUT2 Phase Noise (f <sub>in</sub> = 12.8 MHz, f <sub>out</sub> = 25 MHz)     |    |

| Figure 12 : ToPSync and ACS1790T Operation with Separate Oscillators                     |    |

| Figure 13 : ToPSync and ACS1790T Operation with a Shared Oscillator                      |    |

| Figure 14 : ToPSync and ACS1790T Operation with a Shared VCXO                            |    |

| Figure 15 : Standalone ACS1790T Operation                                                |    |

| Figure 16 : Using the ACS1790T as Part of a PLL                                          |    |

| Figure 17 : Simplified View of OUT1 Output Path                                          | 31 |

| Figure 18 : Simplified View of OUT2 Output Path                                          | 35 |

| Figure 19 : Simplified View of Both Output Paths                                         |    |

| Figure 20 : FBCLK Output Path                                                            |    |

| Figure 21 : Recommended LVPECL DC Termination                                            |    |

| Figure 22 : Recommended LVPECL AC Termination                                            |    |

| Figure 23 : Recommended Power Supply Filtering                                           |    |

| Figure 24 : Example Synchronous Ethernet Application                                     |    |

| Figure 25 : QFN-24 Physical Package Detail                                               |    |

| Figure 26 : Recommended PCB Land Pattern                                                 |    |

|                                                                                          |    |

#### ADVANCED COMMUNICATIONS PRODUCT GROUP

FINAL DATASHEET

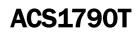

Figure 1 : ACS1790T Block Diagram

**FINAL DATASHEET**

#### ADVANCED COMMUNICATIONS PRODUCT GROUP

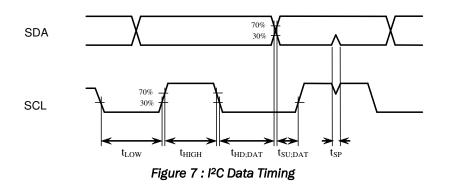

#### **Pin Description**

The ACS1790T uses a QFN 24 package with 24 device pins and a center thermal pad that is connected to the device ground. Table 1 shows the pin definitions.

| Number | Name            | Туре   | Description                                                 |

|--------|-----------------|--------|-------------------------------------------------------------|

| 1      | RESETB          | I      | Active Low Reset                                            |

| 2      | <b>OSCFSELO</b> | PD     | Input Clock Frequency Selection                             |

| 3      | CLK             | 1      | Input Clock                                                 |

| 4      | OSCFSEL1        | [PD    | Input Clock Frequency Selection                             |

| 5      | VDDD            | Power  | Digital Power Supply for Internal Logic and FBCLK Output    |

| 6      | VSSD            | Ground | Digital Ground for Internal Logic and FBCLK Output          |

| 7      | SCL             | 1      | I <sup>2</sup> C Clock (requires external pull up resistor) |

| 8      | SDA             | I/O    | I <sup>2</sup> C Data (requires external pull up resistor)  |

| 9      | AO              | IPD    | I <sup>2</sup> C Address Selection                          |

| 10     | FBCLK           | 0      | Feedback Clock to ToPSync (LVCMOS)                          |

| 11     | A1              | [PD    | I <sup>2</sup> C Address Selection                          |

| 12     | VDDD2           | Power  | Digital Power Supply for OUT2 Clock Output                  |

| 13     | OUT2            | 0      | Single-ended Output Clock (LVCMOS)                          |

| 14     | VSSD2           | Power  | Digital Ground for OUT2 Clock Output                        |

| 15     | VSSA            | Ground | Analogue Ground                                             |

| 16     | OUT1N           | 0      | Differential Output Clock (LVPECL)                          |

| 17     | OUT1P           | 0      | Differential Output Clock (LVPECL)                          |

| 18     | VDDA            | Power  | Analogue Supply                                             |

| 19     | VDDF            | Power  | RF Supply                                                   |

| 20     | VSSF            | Ground | RF Ground                                                   |

| 21     | IC              | -      | Internally connected pin – do not connect                   |

| 22     | MODE            | IPD    | Initial Mode Select                                         |

| 23     | OEB             | 1      | Output Enable                                               |

| 24     | LD              | 0      | Lock Detect (Open Drain)                                    |

| 25     | GND             | Ground | Center Body Contact. Connect to ground                      |

#### Table 1 : ACS1790T Pin Description

I/O – Bidirectional pin

IPD – Input with internal pull-down

### Device Operation

Figure 1 shows the internal architecture of the ACS1790T. The ACS1790T can be divided into a number of main blocks – the voltage-controlled oscillator phase-locked-loop (VCO PLL) block, the output divider block, the output stage and the control block.

# The VCO PLL block

The VCO PLL block is a fully self-contained phase-locked loop that generates an output frequency of between 2.3 and 2.7 GHz that is phase-locked to the clock input. This block is shown in Figure 2.

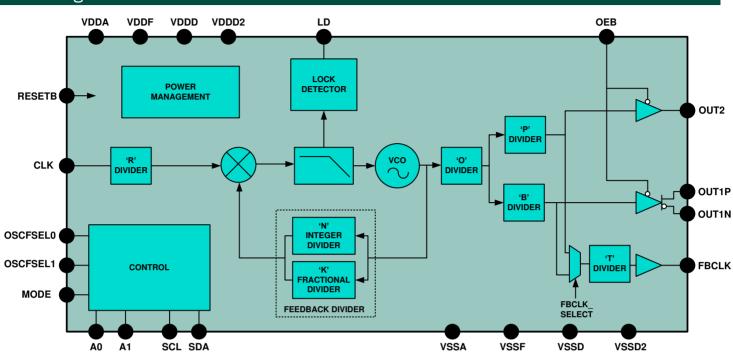

Figure 2 : ACS1790T VCO PLL

The VCO frequency,  $f_{VCO}$  is determined by a divider in the feedback path that supports fractional division ratios and that locks the VCO output to a multiple of the reference frequency,  $f_{PFD}$ , which is the input frequency after passing through the R-divider shown in Figure 1. For input frequencies of 10 and 12.8 MHz the R-divider is in bypass mode, making  $f_{PFD}$  equal to 10 or 12.8 MHz respectively. For input frequencies of 20 and 25 MHz the R-divider is set to divide by two, making  $f_{PFD}$  equal to 10 or 12.5 MHz respectively. The high resolution of the fractional feedback divider provides ultra-fine control of the VCO output. Any frequency within the VCO operating range can be achieved with an accuracy of better than 1 ppb. The design of the VCO and the corresponding phase-and-frequency detector ensure that the output has very low jitter and is not adversely affected by noise and jitter on the input clock that falls above the ACS179OT's PLL bandwidth.

Locking of the VCO to an arbitrary frequency, including immediately after reset, is a two stage process. Firstly, the ACS1790T performs a calibration operation to select the optimal VCO operating point for the selected frequency. When this operation is complete the ACS1790T transitions to a "fine-lock" state in which the VCO output frequency is tuned until it is phase-locked to the reference clock. Once in the fine-lock state, the output frequency of the ACS1790T can be adjusted by up to +/- 500 ppm from the frequency at which the calibration operation was performed without requiring further calibration. However, if the frequency is moved outside of this range then a new calibration cycle must be initiated. At reset the VCO frequency is set to 2.5 GHz. Therefore, once calibrated, the actual output frequency can be set to any value between 2.49875 GHz and 2.50125 GHz without needing to reinitiate the calibration process. This +/- 500 ppm adjustment range should be adequate for any application in which the output frequency is set and subsequently fine-tuned. Refer to the *Applications Information* section for further details of setting the VCO output frequency and initiating recalibration.

The VCO PLL block provides a lock detect signal, LD, to indicate when lock has been achieved after a recalibration cycle. This is an open-drain pin that is pulled low until lock is established, at which time it is released and pulled high by an external pull-up resistor. This allows the LD pins of multiple ACS1790T devices to be connected together to provide a single overall lock indication.

FINAL DATASHEET

# The output divider block

The output of the VCO PLL block drives the divider block that consists of a number of cascaded dividers, and a multiplexer, as shown in Figure 3.

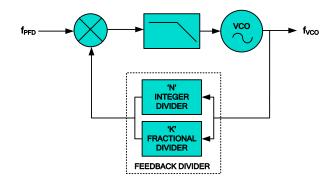

#### Figure 3 : ACS1790T Output Divider Structure

The O-divider is a shared prescaler whereas the B- and P-dividers are specific to the OUT1 and OUT2 outputs respectively. The Tdivider further divides down either the OUT1 or OUT2 output to generate the feedback clock that is used when the ACS1790T forms the controllable oscillator portion of an external phase-locked loop, such as when the ACS1790T is used in conjunction with a suitable ToPSync device.

The O, P, B and T-dividers are individually programmable, and together with the frequency of the VCO, determine the ACS1790T output frequencies. Additionally, the P and B-dividers can be individually disabled in the case that only a single output is being used to reduce power consumption and device noise. The T-divider, which is responsible for generating the low-speed feedback output, FBCLK, can be driven from the output of either the P or B-divider through the multiplexer shown in Figure 3.

Refer to the Using the ACS1790T section for further information on the output dividers.

# The output stage

The ACS1790T provides a total of three clock outputs – a high-speed LVPECL output, OUT1; a low-speed LVCMOS output, OUT2 and; a low-speed LVCMOS feedback clock, FBCLK.

The OUT2 output features a separate power supply pin for the output buffer, allowing operation at 1.8V, 2.5V or 3.3V. There is also a slew-rate limiting option on the OUT2 output to slow the edge-rate of the output clock. The FBCLK output operates at a fixed 3.3V level.

An active-low output enable signal, OEB, is provided to disable the OUT1 and OUT2 outputs, and these outputs can also be disabled under software control.

# The control block

The control block is responsible for control of the other parts of the ACS1790T and includes a set of registers accessible to an external device through a standard I<sup>2</sup>C interface. These registers allow configuration of the VCO PLL, output dividers and output stage, as well as monitoring of the ACS1790T's status. The registers are fully documented in the section entitled *Register-based Device Configuration*.

FINAL DATASHEET

### Reset

The control block is also responsible for handling device reset. The ACS1790T includes a power monitor to reset the device automatically at power-up, and an external, active-low, reset pin, RESETB.

During reset, all the registers are reset to their default values, the I<sup>2</sup>C interface is reset and the clock outputs are held inactive. Immediately after reset, the registers are loaded with default values dependent on the state of the MODE and OSCFSEL[1:0] pins (see the section entitled *Hardware Device Configuration*) to enable generation of frequencies for 1G or 10G Ethernet designs. The VCO will automatically enter a calibration cycle during which the lock-detect pin, LD, is driven low. Once the calibration cycle is complete the LD pin is released and the outputs are activated (unless disabled). The ACS1790T is now fully functional and can be programmed under software control.

#### Using the ACS1790T

There are two methods of programming the ACS1790T. The initial operating mode is determined by the state of various device pins that are sampled at power-up and reset. Subsequent control, and status monitoring, is provided through a set of registers accessible to an external microprocessor through an I<sup>2</sup>C-compatible interface.

# Hardware device configuration

There are three device pins that determine the initial operating state at power-up and reset – OSCFSEL0, OSCFSEL1 and MODE.

The state of these pins is sampled during reset and the pins have internal pull-down mechanisms to ensure that valid inputs are sensed even if the pin is left floating. In a typical application these configuration pins would be connected to a static level, either by tying them directly to ground or 3.3V as appropriate, or connecting them to ground or 3.3V through a pull-up/pull-down resistor. The presence of the internal pull-down means that care needs to be taken when using an external pull-up resistor to ensure that the voltage at the pin exceeds the minimum  $V_{\rm H}$  threshold. A single 4.7Kohm resistor per pin, or a 1Kohm resistor shared between up to three pins, is recommended to ensure this requirement is met.

Should dynamic control of the hardware configuration pins be required then they can be actively driven from logic. However, since the state of these pins is only sampled at reset, it is necessary to reset the ACS1790T, by asserting RESETB, whenever the state of the configuration pins is changed.

#### Input clock frequency selection

The two OSCFSEL pins determine the frequency of the ACS1790T's input clock. Table 2 shows the acceptable frequencies.

|          | Table 2 . Input Gock Trequency Selection |                        |  |  |  |  |  |  |  |

|----------|------------------------------------------|------------------------|--|--|--|--|--|--|--|

| OSCFSEL1 | OSCFSELO                                 | Input Frequency of CLK |  |  |  |  |  |  |  |

| 0        | 0                                        | 20 MHz                 |  |  |  |  |  |  |  |

| 0        | 1                                        | 10 MHz                 |  |  |  |  |  |  |  |

| 1        | 0                                        | 12.8 MHz               |  |  |  |  |  |  |  |

| 1        | 1                                        | 25 MHz                 |  |  |  |  |  |  |  |

#### Table 2 : Input Clock Frequency Selection

The 10, 12.8 and 20 MHz options correspond to the supported reference clock frequencies of the ToPSync family allowing a single oscillator and OSCFSEL setting to be shared between the two parts when the ACS1790T is used as a companion to a ToPSync device. The 25 MHz input frequency is not supported by the ToPSync but is a frequency commonly found in Ethernet applications and easily generated using very-low cost oscillators.

# Default output frequency selection

The MODE pin determines the initial output frequencies from the ACS1790T as shown in Table 3.

| MODE | OUT1       | OUT2   | Typical Application |

|------|------------|--------|---------------------|

| 0    | 125 MHz    | 25 MHz | Gigabit Ethernet    |

| 1    | 156.25 MHz | 25 MHz | 10 Gigabit Ethernet |

#### Table 3 : Default Output Frequency Selection

When the ACS1790T is used in a Synchronous Ethernet application the MODE pin will typically be set to generate the appropriate output frequencies for the desired Ethernet speed. This allows the ACS1790T's outputs to provide clocks to the Ethernet circuitry immediately after reset prior to any additional configuration being performed.

When the ACS1790T is used for an application other than Synchronous Ethernet, for example as a Sonet clock generator, it is unlikely that either setting of the MODE pin will provide the desired output frequency. In this case, the MODE pin setting is arbitrary and the ACS1790T output frequency must be set via the I<sup>2</sup>C interface, either from a microprocessor or a companion ToPSync, prior to the output clocks being used.

# Register-based device configuration

The ACS1790T incorporates eleven user-accessible registers accessed by a microprocessor or companion ToPSync through an industry-standard I<sup>2</sup>C interface. This section documents these registers and the method of accessing them. Since the I<sup>2</sup>C bus is a widely-adopted standard, non-ACS1790T specific details, such as the general I<sup>2</sup>C protocol, are not included here. For this information refer to the I<sup>2</sup>C specification, which can be obtained from NXP Semiconductors.

The ACS1790T I<sup>2</sup>C interface meets the requirements of an F/S-mode I<sup>2</sup>C device as defined in the I<sup>2</sup>C specification. The ACS1790T is able to complete register accesses faster than the I<sup>2</sup>C bus and therefore cycle-stretching is unnecessary and SCL is an input only to the ACS1790T. For full electrical and timing characteristics of the I<sup>2</sup>C interface refer to the *Electrical Specifications* section.

### I<sup>2</sup>C slave address selection

The ACS1790T provides two address selection pins, A0 and A1, to allow one of four different I<sup>2</sup>C slave addresses to be selected as shown in Table 4. This allows a single device, such as a ToPSync, to control up to four associated ACS1790T devices.

| 14 |    |                                      |  |  |  |  |  |  |  |

|----|----|--------------------------------------|--|--|--|--|--|--|--|

| A1 | AO | I <sup>2</sup> C Slave Address (0x0) |  |  |  |  |  |  |  |

| 0  | 0  | C0 (b'1100 000x)                     |  |  |  |  |  |  |  |

| 0  | 1  | C2 (b'1100 001x)                     |  |  |  |  |  |  |  |

| 1  | 0  | C4 (b'1100 010x)                     |  |  |  |  |  |  |  |

| 1  | 1  | C6 (b'1100 011x)                     |  |  |  |  |  |  |  |

The AO and A1 address pins should be connected to static levels on the PCB – either directly to power or ground or through 4.7K-ohm, or lower, resistors. The state of these pins should not be changed during operation.

#### P: Stop condition

Page 11

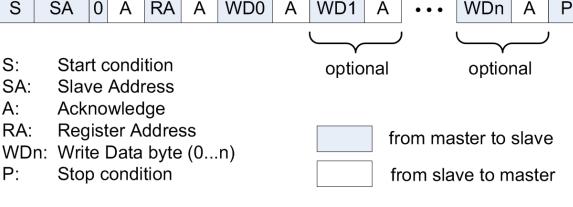

# Figure 4 : I<sup>2</sup>C Write Operation

# I<sup>2</sup>C Read

Figure 5 shows the process used to read one or more registers. It starts off in the same way as a register write operation, with the host writing the slave address (with bit 0 clear) followed by the address of the register to access. However, the host must then issue a repeated start condition, or optionally a stop followed by a start, followed by a write of the slave address with bit 0 set to initiate a read operation. The host can then read consecutive registers as required until generating a final stop condition. As for write operations, the auto-increment of the address stops at the last register, allowing this register to be polled with repeated reads without needing to re-write the register address. In accordance with the I<sup>2</sup>C specification, the host must acknowledge receipt of each byte read, by driving SDA low during the ninth bit time of the byte, except for the last byte that must not be acknowledged (by allowing SDA to float). This signals the ACS1790T to not drive SDA during the next bit time so that the host can generate the stop condition.

# ADVANCED COMMUNICATIONS PRODUCT GROUP

# I<sup>2</sup>C Write

Figure 4 shows the process used to write one or more registers. The operation is initiated by the host generating a start, or repeated start, condition and then writing the appropriate slave address (with bit 0 clear) followed immediately by the eight bit address of the first register to be written and then one or more data bytes containing the desired register contents. After each register write the register address pointer is automatically incremented unless it has reached the address of the highest register, 0x0A. This allows multiple consecutive registers to be written simply by sending additional data bytes. The host must generate either a stop or a repeated start condition to terminate the write operation. The ACS1790T acknowledges the slave address, and all subsequent bytes written, in accordance with the I<sup>2</sup>C specification.

**FINAL DATASHEET**

ACS1790T

### **Register map**

Table 5 shows the ACS1790T register map.

|               | ഗ       | ц.      |            | Bit significance                        |               |               |             |              |              |                   |

|---------------|---------|---------|------------|-----------------------------------------|---------------|---------------|-------------|--------------|--------------|-------------------|

| Register name | Address | Default | 7<br>(MSB) | 6                                       | 5             | 4             | 3           | 2            | 1            | 0<br>(LSB)        |

| reg_status    | 00      | *       |            | mode                                    | oscfsel1      | oscfselO      | a0          | al           | oeb          | lock              |

| reg_output    | 01      | 6C      |            | fbclk_                                  | out1/2_       | fbclk_        | out1_       | out2_        | out2_        | out2_             |

|               |         |         |            | auto_                                   | auto_         | enable        | enable      | enable       | slew-        | drive             |

|               |         |         |            | squelch                                 | squelch       |               |             |              | rate         |                   |

| reg_n_div     | 02      | *       |            | integer portion of VCO feedback divider |               |               |             |              |              |                   |

| reg_k_div_hi  | 03      | *       |            | bits [2                                 | 3:16] of fra  | ctional por   | tion of VCC | ) feedback   | ( divider    |                   |

| reg_k_div_med | 04      | 00      |            | k                                       | oits [15:8] o | of fractional | portion of  | VCO feed     | back divide  | er                |

| reg_k_div_lo  | 05      | 00      |            | k                                       | oits [7:0] of | fractional p  | ortion of N | /CO feedba   | ack divider  | r                 |

| reg_o_div     | 06      | *       |            |                                         |               |               | l           | prescaler o  | division rat | tio               |

| reg_b_div     | 07      | *       |            |                                         |               |               | <u> </u>    | out          | 1 division   | ratio             |

| reg_t_div     | 08      | 00      | fbclk_     |                                         |               |               |             | facedbook    | -lividor rot |                   |

|               |         |         | select     |                                         |               |               |             | feedback     | ulviuer rau  | 10                |

| reg_p_div     | 09      | *       |            | 1                                       |               |               | out         | 2 division i | ratio        |                   |

| reg_vco       | OA      | 01      |            |                                         |               |               |             |              |              | vco_<br>calibrate |

| reg_dither    | 1B      | *       | (pres      | serve)                                  | dither        |               |             | (preserve)   | )            |                   |

#### Table 5 : ACS1790T Register Map

Address and default values are in hexadecimal

\* indicates that the default value of this register is determined by the state of the hardware configuration pins at reset