## imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

Synchronous Equipment Timing Source for SONET or SDH Network Elements

#### ADVANCED COMMUNICATIONS

#### Description

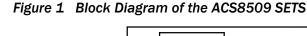

The ACS8509 is a highly integrated, single-chip solution for the Synchronous Equipment Timing Source (SETS) function in a SONET or SDH Network Element. The device generates SONET or SDH Equipment Clocks (SEC) and Frame Synchronization clocks. The ACS8509 is fully compliant with the required international specifications and standards.

EMTECH

The device supports Free-run, Locked and Holdover modes. It also supports all three types of reference clock source: recovered line clock, PDH network, and node synchronization. The ACS8509 generates independent SEC and BITS/SSU clocks, an 8 kHz Frame Synchronization clock and a 2 kHz Multi-Frame Synchronization clock.

Two ACS8509 devices can be used together in a Master/ Slave configuration mode allowing system protection against a single ACS8509 failure.

A microprocessor port is incorporated, providing access to the configuration and status registers for device setup and monitoring.

The ACS8509 includes a choice of edge alignment for 8 kHz input, as well as a low jitter n x E1/DS1 output mode. The User can choose between OCXO or TCXO to define the Stratum and/or Holdover performance required.

#### Block Diagram

#### Features

**FINAL**

- Suitable for Stratum 3E\*, 3, 4E, 4 and SONET Minimum Clock (SMC) or SONET/SDH Equipment Clock (SEC) applications

- Meets AT&T, ITU-T, ETSI and Telcordia specifications

- Accepts four individual input reference clocks

- Generates six output clocks

- Supports Free-run, Locked and Holdover modes of operation

- Robust input clock source quality monitoring on all inputs

- Automatic "hit-less" source switchover on loss of input

- Phase build-out for output clock phase continuity during input switchover and mode transitions

- Microprocessor interface Intel, Motorola, Serial, Multiplexed, EPROM

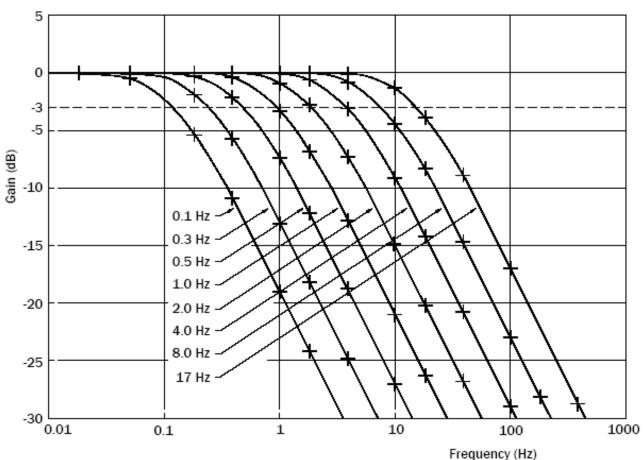

- Programmable wander and jitter tracking attenuation 0.1 Hz to 20 Hz

- Support for Master/Slave device configuration alignment and hot/standby redundancy

- IEEE 1149.1 JTAG Boundary Scan

- Single +3.3 V operation, +5 V I/O compatible

- Operating temperature (ambient) -40°C to +85°C

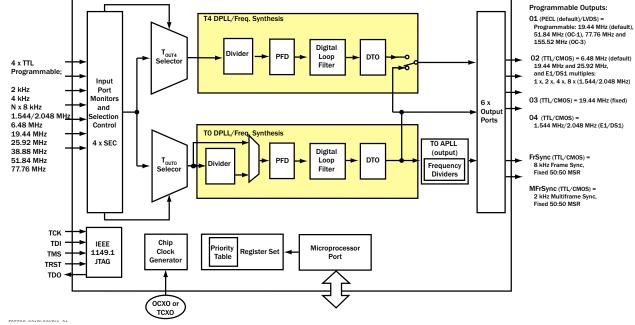

- Available in 100 pin LQFP package.

- Lead (Pb)-free version available (ACS8509T), RoHS and WEEE compliant.

Note...\* Meets holdover requirements, lowest bandwidth 0.1 Hz.

Revision 2.00/January 2006 © Semtech Corp.

#### DATASHEET

### ADVANCED COMMUNICATIONS Table of Contents

**FINAL**

## DATASHEET

Page

#### Section

| Description                                                         | 1    |

|---------------------------------------------------------------------|------|

| Block Diagram                                                       | 1    |

| Features                                                            | 1    |

| Table of Contents                                                   | 2    |

| Pin Diagram                                                         | 4    |

| Pin Description                                                     | 5    |

| Functional Description                                              | 8    |

| Local Oscillator Clock                                              |      |

| Crystal Frequency Calibration                                       | 8    |

| Input Interfaces                                                    |      |

| Over-Voltage Protection                                             |      |

| Input Reference Clock Ports                                         | 9    |

| DivN Examples                                                       |      |

| Input Wander and Jitter Tolerance                                   |      |

| Frame Sync and Multi-Frame Sync Clocks (Part of T <sub>OUTO</sub> ) |      |

| Output Clock Ports                                                  |      |

| Low-speed Output Clock (T <sub>OUT4</sub> )                         |      |

| High-speed Output Clock (Part of T <sub>OUTO</sub> )                | . 12 |

| Low Jitter Multiple E1/DS1 Outputs                                  |      |

| Output Wander and Jitter                                            | 13   |

| Phase Variation                                                     |      |

| Phase Build-Out                                                     |      |

| Microprocessor Interface                                            |      |

| Motorola Mode                                                       |      |

| Intel Mode                                                          |      |

| Multiplexed Mode                                                    |      |

| Serial Mode                                                         |      |

| EPROM Mode                                                          |      |

| Register Set                                                        |      |

| Configuration Registers                                             |      |

| Status Registers                                                    |      |

| Register Access                                                     |      |

| Interrupt Enable and Clear                                          |      |

| Register Map                                                        |      |

| Register Map Description                                            |      |

| Selection of Input Reference Clock Source                           |      |

| Forced Control Selection                                            |      |

| Automatic Control Selection                                         |      |

| Ultra Fast Switching                                                |      |

| Clock Quality Monitoring                                            |      |

| Activity Monitoring                                                 |      |

| Frequency Monitoring                                                |      |

| Modes of Operation                                                  |      |

| Free-run mode                                                       |      |

| Pre-Locked mode                                                     |      |

| Locked mode                                                         |      |

| Lost_Phase mode                                                     |      |

| Holdover mode                                                       |      |

| Pre-Locked(2) mode                                                  | . 41 |

#### ADVANCED COMMUNICATIONS

#### ΕΙΝΛΙ

#### DATASHEET

| Advanced communications Final                                                                               | DATASHEET |

|-------------------------------------------------------------------------------------------------------------|-----------|

| Section                                                                                                     | Page      |

| Protection Facility                                                                                         |           |

| Protection Facility<br>Alignment of Priority Tables in Master and Slave ACS8509                             |           |

| Alignment of the Selection of Reference Sources for T <sub>OUT4</sub> Generation in the Master and Slave AC | S8509 42  |

| Alignment of the Phases of the 8 kHz and 2 kHz Clocks in both Master and Slave ACS8509                      | 42        |

| JTAG                                                                                                        |           |

| PORB                                                                                                        |           |

| Electrical Specification                                                                                    |           |

| Operating Conditions                                                                                        |           |

| DC Characteristics                                                                                          |           |

| Notes for Tables 24 to 30                                                                                   |           |

| Input/Output Timing                                                                                         |           |

| Motorola Mode                                                                                               |           |

| Intel Mode                                                                                                  |           |

| Multiplexed Mode                                                                                            |           |

| Serial Mode                                                                                                 |           |

| EPROM Mode                                                                                                  |           |

| Package Information                                                                                         |           |

| Thermal Conditions                                                                                          |           |

| Application Information                                                                                     |           |

| References                                                                                                  |           |

| Abbreviations                                                                                               |           |

|                                                                                                             |           |

| References                 | 65 |

|----------------------------|----|

| Abbreviations              | 65 |

| Trademark Acknowledgements | 66 |

| Revision Status/History    | 67 |

| Ordering Information       | 68 |

| Disclaimers                | 68 |

| Contacts                   | 68 |

**FINAL**

DATASHEET

Pin Diagram

Figure 2 ACS8509 Pin Diagram Synchronous Equipment Timing Source for SONET or SDH Network Elements

### ADVANCED COMMUNICATIONS

**FINAL**

## ACS8509 SETS

DATASHEET

#### Pin Description

| Table 1 | Power Pins |

|---------|------------|

|---------|------------|

| Pin Number                                         | Symbol   | I/0 | Туре | Description                                                                                                                                                                                                                      |

|----------------------------------------------------|----------|-----|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 12, 13, 16                                         | VD+      | Р   | -    | Supply Voltage: Digital supply to gates in analog section, +3.3 Volts $\pm 10\%$ .                                                                                                                                               |

| 33, 39                                             | VDD_DIFF | Р   | -    | Supply Voltage: Digital supply for differential ports, +3.3 Volts ±10%.                                                                                                                                                          |

| 44                                                 | VDD5     | Р   | -    | Digital Supply for +5 Volts Tolerance to Input Pins. Connect to +5 Volts $(\pm 10\%)$ for clamping to +5 Volts. Connect to VDD for clamping to +3.3 Volts. Leave floating for no clamping, input pins tolerant up to +5.5 Volts. |

| 50, 61, 85,<br>86 91                               | VDD      | Р   | -    | Supply Voltage: Digital supply to logic, +3.3 Volts ±10%.                                                                                                                                                                        |

| 6                                                  | VA1+     | Р   | -    | Supply Voltage: Analog supply to clock multiplying PLL, +3.3 Volts $\pm 10\%$ .                                                                                                                                                  |

| 19                                                 | VA2+     | Р   | -    | Supply Voltage: Analog supply to output PLLs, +3.3 Volts ±10%.                                                                                                                                                                   |

| 11, 14, 15,<br>24, 25, 29,<br>49, 62, 84,<br>87,92 | DGND     | Р   | -    | Supply Ground: Digital ground for logic                                                                                                                                                                                          |

| 32,<br>38                                          | GND_DIFF | Р   | -    | Supply Ground: Digital ground for differential ports.                                                                                                                                                                            |

| 1, 5,<br>20                                        | AGND     | Р   | -    | Supply Ground: Analog grounds.                                                                                                                                                                                                   |

Note...I = Input, O = Output, P = Power,  $TTL^{U} = TTL$  input with pull-up resistor,  $TTL_{D} = TTL$  input with pull-down resistor.

| Pin Number                                                                                                  | Symbol | I/0 | Туре | Description                           |

|-------------------------------------------------------------------------------------------------------------|--------|-----|------|---------------------------------------|

| 4, 17, 26                                                                                                   | NC     | NC  | -    | Not connected: Leave to Float         |

| 3, 18, 22, 27,<br>28, 34, 35,<br>40, 41, 42,<br>43, 46, 47,<br>52, 53, 55,<br>57, 89, 93,<br>94, 96, 97, 98 | IC     | IC  | -    | Internally Connected: Leave to Float. |

#### Table 3 Other Pins

| Pin Number | Symbol | I/0 | Туре             | Description                                                                                                                                                                                                  |

|------------|--------|-----|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2          | TRST   | I   | TTL <sub>D</sub> | JTAG Control Reset Input: TRST = 1 to enable JTAG Boundary Scan mode.<br>TRST = 0 for Boundary Scan stand-by mode, still allowing correct device<br>operation. If not used connect to GND or leave floating. |

| 7          | TMS    | I   | ττι <sup>υ</sup> | JTAG Test Mode Select: Boundary Scan enable. Sampled on rising edge of TCK. If not used connect to VDD or leave floating.                                                                                    |

#### ADVANCED COMMUNICATIONS

**ACS8509 SETS**

#### DATASHEET

#### Table 3 Other Pins (cont...)

| Pin Number | Symbol       | I/0 | Туре             | Description                                                                                                                                                                                                                                                              |

|------------|--------------|-----|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8          | INTREQ       | 0   | TTL/CMOS         | Interrupt Request: Active High software Interrupt output.                                                                                                                                                                                                                |

| 9          | тск          | I   | TTL <sub>D</sub> | JTAG Clock: Boundary Scan clock input. If not used connect to GND or leave floating. This pin may require a capacitor placed between the pin and the nearest GND, to reduce noise pickup. A value of 10 pF should be adequate, but the value is dependent on PCB layout. |

| 10         | REFCLK       | I   | TTL              | Reference Clock: 12.800 MHz (refer to "Local Oscillator Clock" on page 8).                                                                                                                                                                                               |

| 21         | TDO          | 0   | TTL/CMOS         | JTAG Output: Serial test data output. Updated on falling edge of TCK. If not used leave floating.                                                                                                                                                                        |

| 23         | TDI          | Ι   | TTL <sup>U</sup> | JTAG Input: Serial test data Input. Sampled on rising edge of TCK. If not used connect to VDD or leave floating.                                                                                                                                                         |

| 30         | FrSync       | 0   | TTL/CMOS         | Output Reference: 8 kHz Frame Sync output (square wave).                                                                                                                                                                                                                 |

| 31         | MFrSync      | 0   | TTL/CMOS         | Output Reference: 2 kHz Multi-Frame Sync output (square wave).                                                                                                                                                                                                           |

| 36,<br>37  | 01POS, 01NEG | 0   | PECL/LVDS        | Output Reference 01: Programmable, default 19.44 MHz. Also 51.84 MHz, 77.76 MHz, 155.52 MHz. MHz, default type PECL.                                                                                                                                                     |

| 45         | SYNC2K       | Ι   | TTLD             | Synchronize 2 kHz: Connect to 2 kHz Multi-Frame Sync output of partner ACS8509 in redundancy system.                                                                                                                                                                     |

| 48         | SEC1         | I   | TTL <sub>D</sub> | Input Reference SEC1: Programmable, default 19.44 MHz (Default Priority 7).                                                                                                                                                                                              |

| 51         | SEC2         | I   | TTL <sub>D</sub> | Input Reference SEC2 : Programmable, default 19.44 MHz (Default Priority 8).                                                                                                                                                                                             |

| 54         | SEC3         | I   | TTLD             | Input Reference SEC3: Programmable, default (Master mode)<br>1.544/2.048 MHz, default (Slave mode) 6.48 MHz.<br>(Default Priority 11).                                                                                                                                   |

| 56         | SEC4         | I   | TTL <sub>D</sub> | Input Reference SEC4 (Priority 13): Programmable, default 1.544/2.048 MHz (Default Priority 13).                                                                                                                                                                         |

| 58 - 60    | UPSEL(2:0)   | I   | TTL <sub>D</sub> | Microprocessor Select: Configures the interface for a particular microprocessor type at reset.                                                                                                                                                                           |

| 63 - 69    | A(6:0)       | I   | TTL <sub>D</sub> | Microprocessor Interface Address: Address bus for the microprocessor interface registers. A(0) is SDI in Serial mode - output in EPROM mode only.                                                                                                                        |

| 70         | CSB          | I   | TTL <sup>U</sup> | Chip Select (Active <i>Low</i> ): This pin is asserted <i>Low</i> by the microprocessor to enable the microprocessor interface - output in EPROM mode only.                                                                                                              |

| 71         | WRB          | I   | TTL <sup>U</sup> | Write (Active <i>Low</i> ): This pin is asserted <i>Low</i> by the microprocessor to initiate a write cycle. In Motorola mode, WRB = 1 for Read.                                                                                                                         |

| 72         | RDB          | I   | TTL <sup>U</sup> | Read (Active <i>Low</i> ): This pin is asserted <i>Low</i> by the microprocessor to initiate a read cycle.                                                                                                                                                               |

| 73         | ALE          | Ι   | TTL <sub>D</sub> | Address Latch Enable: This pin becomes the address latch enable from the microprocessor. When this pin transitions from <i>High</i> to <i>Low</i> , the address bus inputs are latched into the internal registers. ALE = SCLK in Serial mode.                           |

| 74         | PORB         | I   | TTL <sup>U</sup> | Power-On Reset: Master reset. If PORB is forced <i>Low</i> , all internal states are reset back to default values.                                                                                                                                                       |

### ADVANCED COMMUNICATIONS

Revision 2.00/January 2006 © Semtech Corp.

| Pin Number | Symbol  | I/O | Туре             | Description                                                                                                                                                                                                                                                                                                                                                                           |

|------------|---------|-----|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 75         | RDY     | 0   | TTL/CMOS         | Ready/Data Acknowledge: This pin is asserted <i>High</i> to indicate the device has completed a read or write operation.                                                                                                                                                                                                                                                              |

| 76 - 83    | AD(7:0) | Ю   | TTLD             | Address/Data: Multiplexed data/address bus depending on the microprocessor mode selection. AD(0) is SD0 in Serial mode.                                                                                                                                                                                                                                                               |

| 88         | 02      | 0   | TTL/CMOS         | Output Reference 2: Default 6.48 MHz. Also Dig1 (1.544 MHz/2.048 MHz and 2, 4, 8 x), 19.44 MHz, 25.92 MHz                                                                                                                                                                                                                                                                             |

| 90         | 03      | 0   | TTL/CMOS         | Output Reference 3: 19.44 MHz - fixed.                                                                                                                                                                                                                                                                                                                                                |

| 95         | 04      | 0   | TTL/CMOS         | Output Reference 4: 1.544/2.048 MHz, (T4 BITS).                                                                                                                                                                                                                                                                                                                                       |

| 99         | MSTSLVB | Ι   | TTL <sup>U</sup> | Master/Slave Select: Sets the initial power-up state (or state after a PORB) of the Master/Slave selection register, Reg. 34, Bit 1. The register state can be changed after power up by software.                                                                                                                                                                                    |

| 100        | SONSDHB | I   | ττι <sub>d</sub> | SONET or SDH Frequency Select: Sets the initial power-up state (or state after a PORB) of the SONET/SDH frequency selection registers, Reg. 34, Bit 2 and Reg. 38, Bit 5 and Bit 6. When set <i>Low</i> , SDH rates are selected (2.048 MHz etc.) and when set <i>High</i> , SONET rates are selected (1.544 MHz etc.) The register states can be changed after power-up by software. |

**FINAL**

## ACS8509 SETS

DATASHEET

EMTECH

#### **Functional Description**

The ACS8509 is a highly integrated, single-chip solution for the SETS function in a SONET/SDH Network Element, for the generation of SEC and frame synchronization pulses.

In Free-run mode, the ACS8509 generates a stable, low noise clock signal from an internal oscillator.

In Locked mode, the ACS8509 selects the most appropriate input reference source and generates a stable, low-noise clock signal locked to the selected reference.

In Holdover mode, the ACS8509 generates a stable, lownoise clock signal from the internal oscillator, adjusted to match the last known good frequency of the last selected reference source.

In all modes, the frequency accuracy, jitter and drift performance of the clock meet the requirements of ITU  $G.812^{[10]}$ ,  $G.813^{[11]}$ ,  $G.823^{[13]}$ , and Telcordia GR-1244-CORE<sup>[19]</sup>.

The ACS8509 supports all three types of reference clock source: recovered line clock ( $T_{IN1}$ ), PDH network synchronization timing ( $T_{IN2}$ ) and node synchronization ( $T_{IN3}$ ). The ACS8509 generates independent  $T_{OUT0}$  and  $T_{OUT4}$  clocks, an 8 kHz Frame Synchronization clock and a 2 kHz Multi-Frame Synchronization clock.

The ACS8509 has a high tolerance to input jitter and wander. The jitter/wander transfer is programmable (0.1 Hz up to 20 Hz cut-off points).

The ACS8509 supports protection. Two ACS8509 devices can be configured to provide protection against a single ACS8509 failure.

The protection maintains alignment of the two ACS8509 devices (Master and Slave) and ensures that both ACS8509 devices maintain the same priority table, choose the same reference input and generate the  $T_{OUTO}$  clock, the 8 kHz Frame Synchronization clock and the 2 kHz Multi-Frame Synchronization clock with the same phase.

The ACS8509 includes a microprocessor port, providing access to the configuration and status registers for device setup and monitoring.

#### Local Oscillator Clock

The Master system clock on the ACS8509 should be provided by an external clock oscillator of frequency

12.80 MHz. The clock specification is important for meeting the ITU/ETSI and Telcordia performance requirements for Holdover mode. ITU and ETSI specifications permit a combined drift characteristic, at constant temperature, of all non-temperature related parameters, of up to 10 ppb per day. The same specifications allow a drift of 1 ppm over a temperature range of 0 to +70°C.

#### Table 4 ITU and ETSI Specification

FINAL

| Parameter                                                                         | Value                                 |

|-----------------------------------------------------------------------------------|---------------------------------------|

| Tolerance                                                                         | ±4.6 ppm over 20 year lifetime        |

| Drift<br>(Frequency Drift<br>over supply<br>voltage range of<br>+2.7 V to +3.3 V) | ±0.05 ppm/15 seconds @ constant temp. |

|                                                                                   | ±0.01 ppm/day @ constant temp.        |

|                                                                                   | ±1 ppm over temp. range 0 to +70°C    |

Telcordia specifications are somewhat tighter, requiring a non-temperature-related drift of less than 40 ppb per day and a drift of 280 ppb over the temperature range 0 to +50 °C.

#### Table 5 Telcordia GR-1244 CORE Specification

| Parameter                                                                         | Value                                      |

|-----------------------------------------------------------------------------------|--------------------------------------------|

| Tolerance                                                                         | ±4.6 ppm over 20 year lifetime             |

| Drift<br>(Frequency Drift<br>over supply<br>voltage range of<br>+2.7 V to +3.3 V) | $\pm 0.05$ ppm/15 seconds @ constant temp. |

|                                                                                   | $\pm 0.04$ ppm/15 seconds @ constant temp. |

|                                                                                   | ±0.28 ppm/over temp. range 0 to +50 °C     |

Please contact Semtech for information on crystal oscillator suppliers.

#### **Crystal Frequency Calibration**

The absolute crystal frequency accuracy is less important than the stability since any frequency offset can be compensated by adjustment of register values in the IC. This allows for calibration and compensation of any crystal frequency variation away from its nominal value.  $\pm$  50 ppm adjustment would be sufficient to cope with most crystals, in fact the range is an order of magnitude larger due to the use of two 8-bit register locations. The setting of the *conf\_nominal\_frequency* register allows for this adjustment. An increase in the register value increases the output frequencies by 0.02 ppm for each LSB step. The default value (in decimal) is 39321.

#### DATASHEET

DATASHEET

FINAL

The minimum being 0 and the maximum 65535, gives a -700 ppm to +500 ppm adjustment range of the output frequencies.

EMTECH

ADVANCED COMMUNICATIONS

For example, if the crystal was oscillating at 12.8 MHz + 5 ppm, then the calibration value in the register to give a -5 ppm adjustment in output frequencies to compensate for the crystal inaccuracy, would be:

39321 - (5 / 0.02) = 39071 (decimal)

#### **Input Interfaces**

The ACS8509 supports up to four input reference clock sources from input types  $T_{IN1},\,T_{IN2}$  and  $T_{IN3}$  using TTL/CMOS I/O technologies. These interface technologies support +3.3 V and +5 V operation.

#### **Over-Voltage Protection**

The ACS8509 may require Over-Voltage Protection on input reference clock ports according to ITU Recommendation K.41. Semtech protection devices are recommended for this purpose (see separate Semtech data book).

#### **Input Reference Clock Ports**

Table 6 gives details of the input reference ports, showing the input technologies and the range of frequencies supported on each port; the default spot frequencies and default priorities assigned to each port on power-up or by reset are also shown. Note that SDH and SONET networks use different default frequencies; the network type is pinselectable using the SONSDHB pin). Specific frequencies and priorities are set by configuration.

Although each input port is shown as belonging to one of the types,  $T_{IN1}$ ,  $T_{IN2}$  or  $T_{IN3}$ , they are fully interchangeable as long as the selected speed is within the maximum operating speed of the input port technology.

SDH and SONET networks use different default frequencies; the network type is selectable using the *config\_mode* register 34 Hex, bit 2.

For SONET, config\_mode register 34 Hex, bit 2 = 1, for SDH config\_mode register 34 Hex, bit 2 = 0. On power-up or by reset, the default will be set by the state of the SONSDHB pin (pin 100). Specific frequencies and priorities are set by configuration.

TTL ports (compatible also with CMOS signals) support clock speeds up to 100 MHz, with the highest spot

frequency being 77.76 MHz. The actual spot frequencies supported are:

- 2 kHz,

- 4 kHz,

- 8 kHz (and N x 8 kHz),

- 1.544 MHz (SONET)/2.048 MHz (SDH),

- 6.48 MHz,

- 19.44 MHz,

- 25.92 MHz,

- 38.88 MHz,

- 51.84 MHz,

- 77.76 MHz.

The frequency selection is programmed via the *cnfg\_ref\_source\_frequency* register. The internal DPLL will normally lock to the selected input at the frequency of the input, e.g. 19.44 MHz will lock the DPLL phase comparisons at 19.44 MHz. It is, however, possible to utilize an internal pre-divider to the DPLL to divide the input frequency before it is used for phase comparisons in the DPLL. This pre-divider can be used in one of 2 ways:

- Any of the supported spot frequencies can be divided to 8 kHz by setting the *lock8K* bit (bit 6) in the appropriate *cnfg\_ref\_source\_frequency* register location. For good jitter tolerance for all frequencies and for operation at 19.44 MHz and above, use lock8K. It is possible to choose which edge of the 8 kHz input to lock to, by setting the appropriate bit of the *cnfg\_control1* register.

- 2. Any multiple of 8 kHz between 1544 kHz to 100 MHz can be supported by using the *DivN* feature (bit 7 of the *cnfg\_ref\_source\_frequency* register). Any reference input can be set to use DivN independently of the frequencies and configurations of the other inputs.

Any reference input with the DivN bit set in the *cnfg\_ref\_source\_frequency* register will employ the internal pre-divider prior to the DPLL locking.

The cnfg\_freq\_divn register contains the divider ratio N where the reference input will get divided by (N+1) where  $0 < N < 2^{14}$ -1. The cnfg\_ref\_source\_frequency register must be set to the closest supported spot frequency to the input frequency, but must be lower than the input frequency. When using the DivN feature the post-divider

#### ADVANCED COMMUNICATIONS

FINAL

DATASHEET

Table 6 Input Reference Source Selection and Priority Table

| Port Number | Channel<br>Number (Bin) | Port Type        | Input Port<br>Technology | Frequencies Supported                                                                                                                | Default<br>Priority |

|-------------|-------------------------|------------------|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------|---------------------|

| SEC1        | 0111                    | T <sub>IN1</sub> | TTL/CMOS                 | Up to 100 MHz (see Note (i))<br>Default (SONET): 19.44 MHz<br>Default (SDH): 19.44 MHz                                               | 8                   |

| SEC2        | 1000                    | T <sub>IN1</sub> | TTL/CMOS                 | Up to 100 MHz (see Note (i))<br>Default (SONET): 19.44 MHz<br>Default (SDH): 19.44 MHz                                               | 9                   |

| SEC3        | 1011                    | T <sub>IN2</sub> | TTL/CMOS                 | Up to 100 MHz (see Note (i))<br>Default (Master) (SONET): 1.544 MHz<br>Default (Master) (SDH): 2.048 MHz<br>Default (Slave) 6.48 MHz | 12/1 (Note<br>(ii)) |

| SEC4        | 1101                    | T <sub>IN2</sub> | TTL/CMOS                 | Up to 100 MHz (see Note (i))<br>Default (SONET): 1.544 MHz<br>Default (SDH): 2.048 MHz                                               | 14                  |

Notes: (i) TTL ports (compatible also with CMOS signals) support clock speeds up to 100 MHz, with the highest spot frequency being 77.76 MHz. The actual spot frequencies are: 2 kHz, 4 kHz, 8 kHz (and N x 8 kHz), 1.544 MHz (SONET)/2.048 MHz (SDH), 6.48 MHz, 19.44 MHz, 25.92 MHz, 38.88 MHz, 51.84 MHz, 77.76 MHz. SONET or SDH is selected using the SONSDHB pin. When the SONSDHB pin is High SONET is selected, when the SONSDHB pin is Low SDH is selected.

(ii) Input port SEC4 is set at 12 on the Master SETS IC and 1 on the Slave SETS IC, as default on power up (or PORB). The default setup of Master or Slave SEC4 priority is determined by the MSTSLVB pin.

frequency must be 8 kHz, which is indicated by setting the *lock8k* bit high (bit 6 in *cnfg\_ref\_source\_frequency* register). Any input set to DivN must have the frequency monitors disabled (If the frequency monitors are disabled, they are disabled for all inputs regardless of the input configurations, in this case only activity monitoring will take place). Whilst any number of inputs can be set to use the DivN feature, only one N can be programmed, hence all inputs using the DivN feature must require the same division to get to 8 kHz.

#### **DivN Examples**

To lock to 2.000 MHz:

- The cnfg\_ref\_source\_frequency register is set to 11XX0001 (binary) to set the DivN, lock8k bits, and the frequency to E1/DS1. (XX = "leaky bucket" ID for this input).

- 2. The *cnfg\_mode* register (34Hex) bit 2 needs to be set to 1 to select SONET frequencies (DS1).

- 3. The frequency monitors are disabled in *cnfg\_monitors* register (48Hex) by writing 00 to bits 0 and 1.

- 4. The DivN register is set to F9 Hex (249 decimal).

To lock to 10.000 MHz:

- 1. The cnfg\_ref\_source\_frequency register is set to 11XX0010 (binary) to set the DivN, lock8k bits, and the frequency to 6.48 MHz. (XX = "leaky bucket" ID for this input).

- 2. The frequency monitors are disabled in *cnfg\_monitors* register (48Hex) by writing 00 to bits 0 and 1.

- 3. The DivN register is set to 4E1 Hex (1249 decimal).

#### **Input Wander and Jitter Tolerance**

The ACS8509 is compliant to the requirements of all relevant standards, principally ITU Recommendation  $G.825^{[15]}$ , ANSI T1.101-1999<sup>[1]</sup> and ETSI ETS 300 462-5 (1996)<sup>[4]</sup>.

All reference clock inputs have a tight frequency tolerance but a generous jitter tolerance. Pullin, hold-in and pull-out ranges are specified for each input port in Table 7. Minimum jitter tolerance masks are specified in Figures 3 and 4, and Tables 8 and 9, respectively. The ACS8509 will tolerate wander and jitter components greater than those shown in Figure 3 and Figure 4, up to a limit determined by a combination of the apparent long-term frequency offset caused by wander and the eye-closure caused by jitter (the input source will be rejected if the offset pushes

DATASHEET

#### ADVANCED COMMUNICATIONS

FINAL

the frequency outside the hold-in range for long enough to be detected, whilst the signal will also be rejected if the eye closes sufficiently to affect the signal purity). The "8klock" mode should be engaged for high jitter tolerance according to these masks. All reference clock ports are monitored for quality, including frequency offset and general activity. Single short-term interruptions in selected reference clocks may not cause rearrangements, whilst longer interruptions, or multiple, short-term interruptions, will cause rearrangements, as will frequency offsets which are sufficiently large or sufficiently long to cause loss-of-lock in the phase-locked loop. The failed reference source will be removed from the priority table and declared as unserviceable, until its perceived quality has been restored to an acceptable level.

The registers sts\_curr\_inc\_offset (address OC, OD, O7) report the frequency of the DPLL with respect to the external TCXO frequency. This is a 19-bit signed number with one LSB representing 0.0003 ppm (range of  $\pm$ 80 ppm). Reading this regularly can show how the currently locked source is varying in value e.g. due to wander on its input.

The ACS8509 performs automatic frequency monitoring with an acceptable input frequency offset range of  $\pm 16.6$  ppm. The ACS8509 DPLL has a programmable frequency limit of  $\pm 80$  ppm. If the range is programmed to be > 16.6 ppm, the frequency monitors should be disabled so the input reference source is not automatically rejected as out of frequency range.

#### Table 7 Input Reference Source Jitter Tolerance

| Jitter Tolerance | Frequency Monitor<br>Acceptance Range | Frequency Acceptance<br>Range (Pull-in) | Frequency Acceptance<br>Range (Hold-in) | Frequency Acceptance<br>Range (Pull-out) |

|------------------|---------------------------------------|-----------------------------------------|-----------------------------------------|------------------------------------------|

| G.703            |                                       | ±4.6 ppm                                | ±4.6 ppm                                | ±4.6 ppm                                 |

| G.783            | ±16.6 ppm                             | (see Note (i))                          | (see Note (i))                          | (see Note (i))                           |

| G.823            | - <u>110.0 ppm</u>                    | ±9.2 ppm                                | ±9.2 ppm                                | ±9.2 ppm                                 |

| GR-1244-CORE     |                                       | (see Note (ii))                         | (see Note (ii))                         | (see Note (ii))                          |

Notes: (i) The frequency acceptance and generation range will be  $\pm 4.6$  ppm around the required frequency when the external crystal frequency accuracy is within a tolerance of  $\pm 4.6$  ppm.

(ii) The fundamental acceptance range and generation range is ± 9.2 ppm with an exact external crystal frequency of 12.8 MHz. This is the default DPLL range, the range is also programmable from 0 to 80 ppm in 0.08 ppm steps.

DATASHEET

#### ADVANCED COMMUNICATIONS

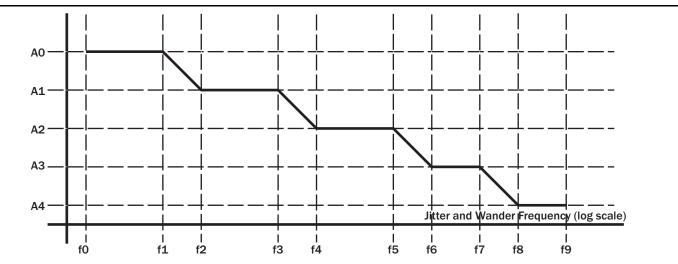

Figure 3 Minimum Input Jitter Tolerance (OC-3/STM-1)

MTECH

FINAL

Note...For inputs supporting G.783<sup>[9]</sup> compliant sources.)

| -       |                       |                       |                           |

|---------|-----------------------|-----------------------|---------------------------|

| Tahla Q | Amplitude and Frequen | nov Values for litter | Tolerance (OC-3/STM-1)    |

|         | Amplitude and riequen | icy values for filler | 10101010100 (00-3/3110-1) |

| STM<br>level | Peak to peak amplitude (unit<br>Interval) |     |    |     |      |      | Frequency (Hz) |       |        |       |      |     |       |      |      |

|--------------|-------------------------------------------|-----|----|-----|------|------|----------------|-------|--------|-------|------|-----|-------|------|------|

|              | AO                                        | A1  | A2 | A3  | A4   | FO   | F1             | F2    | F3     | F4    | F5   | F6  | F7    | F8   | F9   |

| STM-1        | 2800                                      | 311 | 39 | 1.5 | 0.15 | 12 u | 178 u          | 1.6 m | 15.6 m | 0.125 | 19.3 | 500 | 6.5 k | 65 k | 1.3m |

#### Frame Sync and Multi-Frame Sync Clocks (Part of T<sub>OUTO</sub>)

Frame Sync (8 kHz) and Multi-Frame Sync (2 kHz) clocks are provided on outputs "FrSync" and "MFrSync". The FrSync and MFrSync clocks have a 50:50 mark space ratio. These are driven from the TOUTO clock. They are synchronized with their counterparts in a second ACS8509 device (if used), using the technique described later.

#### **Output Clock Ports**

The device supports a set of main output clocks, T<sub>OUTO</sub> and T<sub>OUT4</sub>, and a pair of secondary output clocks, "Frame Sync" and "Multi-Frame Sync". The two main output clocks,  $T_{OUTO}$  and  $T_{OUT4}$ , are independent of each other and are individually selectable. The two secondary output clocks, Frame Sync and Multi-Frame Sync, are derived from T<sub>OUTO</sub>. The frequencies of the output clocks are selectable from a range of pre-defined spot frequencies and a variety of output technologies are supported, as defined in Table 10.

#### Low-speed Output Clock (T<sub>OUT4</sub>)

The  $T_{OUT4}$  clock is supplied on output port O4. This port will provide a TTL/CMOS signal at either 1.544 MHz or 2.048 MHz, depending on the setting of the SONSDHB pin.

#### High-speed Output Clock (Part of Touro)

The T<sub>OUTO</sub> port has multiple outputs. Output O1 is differential and can support clocks up to 155.52 MHz. Output 02 is a TTL/CMOS output with a choice of 11 different frequencies up to 51.84 MHz. Output 03 is a TTL/CMOS output with fixed frequency of 19.44 MHz. Each output is individually configured to operate at the frequencies shown in Table 10 (configuration must be consistent between ACS8509 devices for protectionswitching to be effective - output clocks will be phasealigned between devices). Using the cnfg\_differential\_outputs register, output 01 can be made to be LVDS or PECL compatible.

#### ADVANCED COMMUNICATIONS FINAL

Figure 4 Minimum Input Jitter Tolerance (DS1/E1)

Table 9 Amplitude and Frequency Values for Jitter Tolerance (DS1/E1)

| Туре | Spec.                        | Amplitu | de (UI <sub>p-p</sub> ) | Frequency (Hz) |       |      |      |  |

|------|------------------------------|---------|-------------------------|----------------|-------|------|------|--|

|      |                              | A1      | A2                      | F1             | F2    | F3   | F4   |  |

| DS1  | GR-1244-CORE <sup>[19]</sup> | 5       | 0.1                     | 10             | 500   | 8 k  | 40 k |  |

| E1   | ITU G.823 <sup>[13]</sup>    | 1.5     | 0.2                     | 20             | 2.4 k | 18 k | 100k |  |

#### Low Jitter Multiple E1/DS1 Outputs

This feature is activated using the *cnfg\_control1* register. This sends a frequency of twice the Dig2 rate (see reg addr 39h, bits 7:6) to the APLL instead of the normal 77.76 MHz. For this feature to be used, the Dig2 rate must only be set to 12352 kHz/16384 kHz using the *cnfg\_T0\_output\_frequencies* register. The normal OC-3 rate outputs are then replaced with E1/DS1 multiple rates. The E1(SONET)/DS1(SDH) selection is made in the same way as for Dig2 using the *cnfg\_T0\_output\_enable* register.

Table 11 shows the relationship between primary output frequencies and the corresponding output in E1/DS1 mode, and from which output they are available.

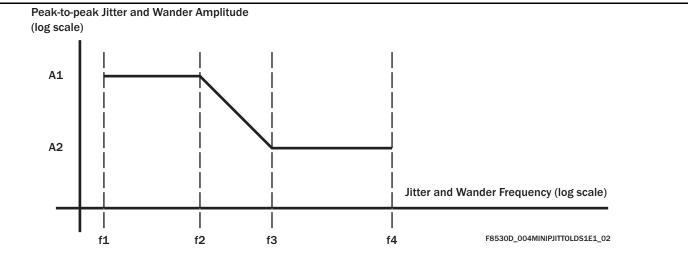

#### **Output Wander and Jitter**

Wander and jitter present on the output clocks are dependent on:

1. The magnitude of wander and jitter on the selected input reference clock (in Locked mode).

- 2. The internal wander and jitter transfer characteristic (in Locked mode).

- 3. The jitter on the local oscillator clock.

- 4. The wander on the local oscillator clock (in Holdover mode).

Wander and jitter are treated in different ways to reflect their differing impacts on network design. Jitter is always strongly attenuated, whilst wander attenuation can be varied to suit the application and operating state. Wander and jitter attenuation is performed using a digital phase locked loop (DPLL) with a programmable bandwidth. This gives a transfer characteristic of a low pass filter, with a programmable pole. It is sometimes necessary to change the filter dynamics to suit particular circumstances - one example being when locking to a new source, the filter can be opened up to reduce locking time and can then be gradually tightened again to remove wander. Since wander represents a relatively long-term deviation from the nominal operating frequency, it affects the rate of supply of data to the network element. Strong wander attenuation limits the rate of consumption of data to within a smaller range, so a larger buffer store is required to prevent data loss. But, since any buffer store potentially

SEMTECH

**FINAL**

DATASHEET

Table 10 Output Reference Source Selection Table

| Port<br>Name | Output Port<br>Technology   | Frequencies Supported                                                                                                          |

|--------------|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------|

| 01           | PECL/LVDS<br>(PECL default) | 19.44 MHz (default), 51.84 MHz, 77.76 MHz, 155.52 MHz                                                                          |

| 02           | TTL/CMOS                    | 1.544 MHz/2.048 MHz, 3.088 MHz/4.096 MHz, 6.176 MHz/8.192 MHz, 6.48 MHz (default), 12.352 MHz/16.384 MHz, 19.44 MHz, 25.92 MHz |

| 03           | TTL/CMOS                    | 19.44 MHz - fixed                                                                                                              |

| 04           | TTL/CMOS                    | 1.544 MHz/2.048 MHz                                                                                                            |

| FrSync       | TTL/CMOS                    | FrSync, 8 kHz - with a 50:50 MSR                                                                                               |

| MFrSync      | TTL/CMOS                    | MFrSync, 2 kHz - with a 50:50 MSR                                                                                              |

Note...1.544 MHz/2.048 MHz are shown for SONET/SDH respectively. Pin SONSDHB controls default, when High SONET is default.

| Mode                            | Freq to<br>APLL | APLL<br>Multiplier | APLL<br>Freq | cik_ filt | cik_<br>filt/2 | clk_<br>filt/4 | cik_ filt/6 | clk_<br>filt/8 | clk_<br>filt/12 | cik_<br>filt/16 | clk_<br>filt/48 | DPLL<br>Freq |

|---------------------------------|-----------------|--------------------|--------------|-----------|----------------|----------------|-------------|----------------|-----------------|-----------------|-----------------|--------------|

| Default                         | 77.76           | 4                  | 311.04       | 311.04    | 155.52         | 77.76          | 51.84       | 38.88          | 25.92           | 19.44           | 6.48            | 77.76        |

| n value                         |                 |                    |              |           |                | 16             |             | 8              | 4               |                 |                 |              |

| n x E1                          | 32.768          | 4                  | 131.072      | 131.072   | 65.536         | 32.768         | 21.84533    | 16.384         | 10.92267        | 8.192           | 2.730667        | 77.76        |

| n x T1                          | 24.704          | 4                  | 98.816       | 98.816    | 49.408         | 24.704         | 16.46933    | 12.352         | 8.234667        | 6.176           | 2.058667        | 77.76        |

|                                 |                 |                    |              | ľ         |                |                |             |                |                 | 02              |                 |              |

| Frequencies Available by Output |                 |                    |              |           |                |                |             |                |                 | 03              |                 |              |

|                                 |                 |                    |              |           | 01             |                |             |                |                 | 01              |                 |              |

Table 11 Multiple E1/DS1 Outputs in Relation to Standard Outputs

increases latency, wander may often only need to be removed at specific points within a network where buffer stores are acceptable, such as at digital cross connects. Otherwise, wander is sometimes not required to be attenuated and can be passed through transparently. The ACS8509 has programmable wander transfer characteristics in a range from 0.1 Hz to 20 Hz. The wander and jitter transfer characteristic is shown in Figure 5.

Wander on the local oscillator clock will not have significant effect on the output clock whilst in Locked mode, so long as the DPLL bandwidth is set high enough so that the DPLL can compensate quickly enough for any frequency changes in the crystal. In Free-run or Holdover mode wander on the crystal is more significant. Variation in crystal temperature or supply voltage both cause drifts in operating frequency, as does ageing. These effects must be limited by careful selection of a suitable component for the local oscillator, as specified in the Section "Local Oscillator Clock" on page 8.

#### **Phase Variation**

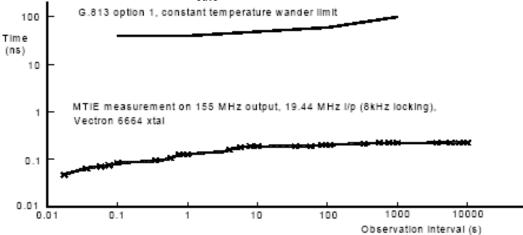

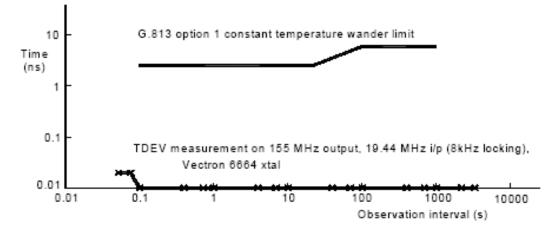

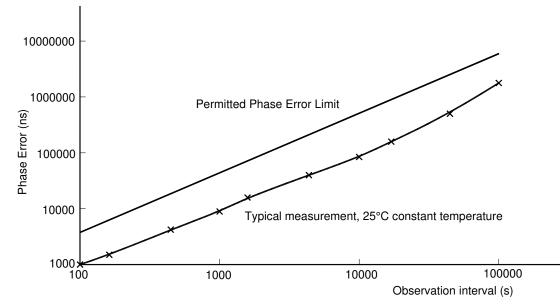

There will be a phase shift across the ACS8509 between the selected input reference source and the output clock. This phase shift may vary over time but will be constrained to lie within specified limits. The phase shift is characterized using two parameters, MTIE (Maximum Time Interval Error), and TDEV (Time Deviation), which, although being specified in all relevant specifications, differ in acceptable limits in each one. Typical measurements for the ACS8509 are shown in Figures 6 and 7, for Locked mode operation. Figure 8 shows a typical measurement of Phase Error accumulation in Holdover mode operation.

MTECH

FINAL

DATASHEET

The required performance for phase variation during Holdover is specified in several ways depending upon the particular circumstances pertaining:

- 1. ETSI 300 462-5, Section 9.1, requires that the short term phase error during switchover (i.e., Locked to Holdover to Locked) be limited to an accumulation rate no greater than 0.05 ppm during a 15 second interval.

- 2. ETSI 300 462-5, Section 9.2, requires that the long term phase error in the Holdover mode should not exceed:

$\{(a1+a2)S+0.5bS^2+c\}$  where:

- a1 = 50 ns/s (allowance for initial frequency offset)

- a2 = 2000 ns/s (allowance for temperature variation)

- $b = 1.16 \times 10^{-4} \text{ ns/s}^2$  (allowance for ageing)

- c = 120 ns (allowance for entry into Holdover mode).

- 3. ANSI Tin1.101-1994, Section 8.2.2, requires that the phase variation be limited so that no more than 255

slips (of 125 µs each) occur during the first day of Holdover. This requires a frequency accuracy better than:

$((24x60x60)+(255x125\mu s))/(24x60x60) = 0.37 \text{ ppm}$

Temperature variation is not restricted, except to within the normal bounds of 0 to 50 °C.

- 4. Telcordia GR.1244.CORE, Section 5.2., Table 4, shows that an initial frequency offset of 50 ppb is permitted on entering Holdover, whilst a drift over temperature of 280 ppb is allowed; an allowance of 40 ppb is permitted for all other effects.

- ITU G.822, Section 2.6, requires that the slip rate during category (b) operation (interpreted as being applicable to Holdover mode operation) be limited to less than 30 slips (of 125 μs each) per hour:

((((60 x 60)/30)+125µs)/(60x60)) = 1.042 ppm

**ADVANCED COMMUNICATIONS**

#### FINAL

DATASHEET

#### Figure 6 Maximum Time Interval Error of T<sub>out0</sub> Output Port

Figure 7 Time Deviation of T<sub>out0</sub> Output Port

Figure 8 Phase Error Accumulation of TO PLL Output Port in Holdover Mode

DATASHEET

#### ADVANCED COMMUNICATIONS

SEMTECH

#### **Phase Build-Out**

Phase Build-Out (PBO) is the function to minimize phase transients on the output SEC clock during input reference switching. If the currently selected input reference clock source is lost (due to a short interruption, out of frequency detection, or complete loss of reference), the second, next highest priority reference source will be selected. During this transition, the *Lost\_Phase* mode is entered.

The typical phase disturbance on clock reference source switching will be less than 12 ns on the ACS8509. For clock reference switching caused by the main input failing or being disconnected, then the phase disturbance on the output will still be less than the 120 ns allowed for in the G.813 spec. The actual value is dependent on the frequency being locked to.

ITU-T G.813 states that the max allowable short term phase transient response, resulting from a switch from one clock source to another, with Holdover mode entered in between, should be a maximum of 1  $\mu$ s over a 15 second interval. The maximum phase transient or jump should be less than 120 ns at a rate of change of less than 7.5 ppm and the Holdover performance should be better than 0.05 ppm.

On the ACS8509, PBO can be enabled, disabled or frozen using the  $\mu$ P interface. By default, it is enabled. When PBO is enabled, it can also be frozen, which will disable the PBO operation on the next input reference switch, but will

remain with the current offset. If PBO is disabled while the device is in the Locked mode, there will be a phase jump on the output SEC clocks as the DPLL locks back to 0 degree phase error.

#### **Microprocessor Interface**

**FINAL**

The ACS8509 incorporates a microprocessor interface, which can be configured for the following modes via the bus interface mode control pins UPSEL(2:0) as defined in Table 12.

| UPSEL(2:0) | Mode        | Description                    |

|------------|-------------|--------------------------------|

| 111 (7)    | OFF         | Interface disabled             |

| 110 (6)    | OFF         | Interface disabled             |

| 101 (5)    | SERIAL      | Serial uP bus interface        |

| 100 (4)    | MOTOROLA    | Motorola interface             |

| 011 (3)    | INTEL       | Intel compatible bus interface |

| 010 (2)    | MULTIPLEXED | Multiplexed bus interface      |

| 001 (1)    | EPROM       | EPROM read mode                |

| 000 (0)    | OFF         | Interface disabled             |

#### **Motorola Mode**

Parallel data + address: this mode is suitable for use with Motorola's 68x0 type bus.

#### **Intel Mode**

Parallel data + address: this mode is suitable for use with Intel's 80x86 type bus.

#### **Multiplexed Mode**

Data/address: this mode is suitable for use with microprocessors which share bus signals between address and data (e.g., Intel's 80x86 family).

#### **Serial Mode**

This mode is suitable for use with microprocessor which use a serial interface.

#### **EPROM Mode**

This mode is suitable for simple standalone applications where it is required to change the default loading of the register values to suit different applications.

This can be done by loading values from an external ROM. The data is read from the ROM automatically after powerup when the UPSEL(2:0) pins are set to "001". Each register value is stored sequentially, with ROM address 0 corresponding to register address 0 and so on.

DATASHEET

#### ADVANCED COMMUNICATIONS

The value in the *chip\_id* location (address 00 & 01) is checked to see if it matches the ID number of the ACS8509 (value 213E). Upon a successful number match, the remaining data from the ROM is used to set the internal register values. Only 64 locations in the ROM are required.

#### **Register Set**

All registers are 8-bits wide, organized with the mostsignificant bit positioned in the left-most bit, with bit significance decreasing towards the right most bit. Some registers carry several individual data fields of various sizes, from single-bit values (e.g. flags) upwards. Several data fields are spread across multiple registers; their organization is shown in the register map, Table 13.

#### **Configuration Registers**

Each configuration register reverts to a default value on power-up or following a reset. Most default values are fixed, but some will be pinsettable. All configuration registers can be read out over the microprocessor port.

#### **Status Registers**

The Status Registers contain readable registers. They may all be read from outside the chip but are not writeable from outside the chip (except for a clearing operation). All status registers are read via shadow registers to avoid data hits due to dynamic operation. Each individual status register has a unique location.

#### **Register Access**

Most registers are of one of two types, configuration registers or status registers, the exceptions being the *chip\_ID* and *chip\_revision* registers. Configuration registers may be written to or read from at any time (the complete 8-bit register must be written, even if only one bit is being modified). All status registers may be read at any time and, in some status registers (such as the *sts\_interrupts* register), any individual data field may be cleared by writing a "1" into each bit of the field (writing a "0" value into a bit will not affect the value of the bit). A description of each register is given in the Register Map, and Register Map Description.

#### **Interrupt Enable and Clear**

Interrupt requests are flagged on pin INTREQ (active High). Bits in the interrupt status register

are set (high) by the following conditions:

FINAL

1. Any reference source becoming valid or going invalid.

2. A change in the operating state (e.g. Locked, Holdover etc.)

3. A brief loss of the currently selected reference source.

All interrupt sources are maskable via the mask register, each one being enabled by writing a "1" to the appropriate bit. Any unmasked bit set in the interrupt status register will cause the interrupt request pin to be asserted (high). All interrupts are cleared by writing a "1" to the bit(s) to be cleared in the status register. When all pending unmasked interrupts are cleared the interrupt pin will go inactive (low).

The loss of the currently selected reference source will eventually cause the input to be considered invalid, triggering an interrupt. The time taken to raise this interrupt is dependant on the leaky bucket configuration of the activity monitors. The fastest leaky bucket setting will still take up to 128 ms to trigger the interrupt. The interrupt caused by the brief loss of the currently selected reference source is provided to facilitate very fast source failure detection if desired. It is triggered after missing just a couple of cycles of the reference source. Some applications require the facility to switch downstream devices based on the status of the reference sources. In order to provide extra flexibility, it is possible to flag the "main reference failed" interrupt (addr 06, bit 6) on the pin TDO. This is simply a copy of the status bit in the interrupt register and is independent of the mask register settings. The bit is reset by writing to the interrupt status register in the normal way. This feature can be enabled and disabled by writing to bit 6 of register 48Hex.

#### **Register Map**

Shaded areas in the map are "don't care" and writing either 0 or 1 will not affect any function of the device. Bits labelled Set to 0 or Set to 1 must be set as stated during initialization of the device, either following power-up, or after a power-on reset (POR). Failure to correctly set these bits may result in the device operating in an unexpected way.

Some registers do not appear in this list. These are either not used, or have test functionality. Do not write to any undefined registers as this may cause the device to operate in a test mode. If an undefined register has been inadvertently addressed, the device should be reset to ensure the undefined registers are at default values.

#### ADVANCED COMMUNICATIONS

FINAL

## ACS8509 SETS

#### DATASHEET

#### Table 13 Register Map

| Addr  | Register Name                     |                                    |                                    |                                                                                                                              | Dat                                | ta Bit               |                                    |                                                |              |  |  |  |  |

|-------|-----------------------------------|------------------------------------|------------------------------------|------------------------------------------------------------------------------------------------------------------------------|------------------------------------|----------------------|------------------------------------|------------------------------------------------|--------------|--|--|--|--|

| (Hex) |                                   | 7 (msb)                            | 6                                  | 5                                                                                                                            | 4                                  | 3                    | 2                                  | 1                                              | 0 (Isb)      |  |  |  |  |

| 00    | chip_id                           |                                    |                                    |                                                                                                                              | Device part                        | number (7:0          | )                                  |                                                |              |  |  |  |  |

| 01    | (read only)                       |                                    |                                    |                                                                                                                              | Device part i                      | number (15:8         | 8)                                 |                                                |              |  |  |  |  |

| 02    | chip_revision<br>(read only)      |                                    |                                    |                                                                                                                              | Chip revisior                      | n number (7:0        | D)                                 |                                                |              |  |  |  |  |

| 03    | cnfg_control1<br>(read/write)     |                                    |                                    | Multiple<br>E1/T1 O/P                                                                                                        | Analog<br>div sync                 | Set to 0             | 8k Edge<br>Polarity                | Set to 0                                       | Set to 0     |  |  |  |  |

| 04    | cnfg_control2<br>(read/write)     |                                    |                                    | Ph                                                                                                                           | ase loss flag                      | limit                | Set to 0                           | Set to 1                                       | Set to 0     |  |  |  |  |

| 05    | sts_interrupts<br>(read/write)    | <sec2><br/>valid<br/>change</sec2> | <sec1><br/>valid<br/>change</sec1> |                                                                                                                              |                                    |                      |                                    |                                                |              |  |  |  |  |

| 06    |                                   | Operating mode                     | Main ref.<br>failed                |                                                                                                                              | <sec4><br/>valid<br/>change</sec4> |                      | <sec3><br/>valid<br/>change</sec3> |                                                |              |  |  |  |  |

| 08    | sts_T4_inputs<br>(read/write)     |                                    |                                    |                                                                                                                              | T4 ref failed                      |                      |                                    |                                                |              |  |  |  |  |

| 09    | sts_operating_mode<br>(read only) |                                    |                                    |                                                                                                                              |                                    |                      | 0                                  | perating mod                                   | e (2:0)      |  |  |  |  |

| OA    | sts_priority_table                |                                    | Highest prior                      | ity valid sourc                                                                                                              | e                                  | Cu                   | irrently select                    | ed reference                                   | source       |  |  |  |  |

| 0B    | (read only)                       | 3                                  | ord highest prio                   | ority valid sou                                                                                                              | rce                                | 2                    | 2nd highest p                      | riority valid so                               | ource        |  |  |  |  |

| 00    | sts_curr_inc_offset               | Current increment offset (7:0)     |                                    |                                                                                                                              |                                    |                      |                                    |                                                |              |  |  |  |  |

| 0D    | (read only)                       | Current increment offset (15:8)    |                                    |                                                                                                                              |                                    |                      |                                    |                                                |              |  |  |  |  |

| 07    |                                   |                                    |                                    |                                                                                                                              |                                    |                      | Current                            | increment of                                   | fset (18:16) |  |  |  |  |

| 0E    | sts_sources_valid                 | <sec2></sec2>                      | <sec1></sec1>                      |                                                                                                                              |                                    |                      |                                    |                                                |              |  |  |  |  |

| OF    | (read only)                       |                                    |                                    |                                                                                                                              | <sec4></sec4>                      |                      | <sec3></sec3>                      |                                                |              |  |  |  |  |

| 13    | sts_reference_sources             |                                    | status                             | <sec2></sec2>                                                                                                                |                                    |                      | statu                              | s <sec1></sec1>                                |              |  |  |  |  |

| 15    | (read/write)                      |                                    |                                    |                                                                                                                              |                                    | status <sec3></sec3> |                                    |                                                |              |  |  |  |  |

| 16    |                                   |                                    |                                    |                                                                                                                              |                                    |                      | statu                              | s <sec4></sec4>                                |              |  |  |  |  |

| 1B    | cnfg_ref_selection_               |                                    | programmed_                        | priority <sec2< td=""><td>2&gt;</td><td></td><td>programmed</td><td>I_priority <se< td=""><td>C1&gt;</td></se<></td></sec2<> | 2>                                 |                      | programmed                         | I_priority <se< td=""><td>C1&gt;</td></se<>    | C1>          |  |  |  |  |

| 1D    | priority<br>(read/write)          |                                    |                                    |                                                                                                                              |                                    |                      | programmed                         | I_priority <se< td=""><td>03&gt;</td></se<>    | 03>          |  |  |  |  |

| 1E    |                                   |                                    |                                    |                                                                                                                              |                                    |                      | programmed                         | I_priority <se< td=""><td>C4&gt;</td></se<>    | C4>          |  |  |  |  |

| 26    | cnfg_ref_source_                  | divn                               | lock8k                             | bucket_id                                                                                                                    | <sec1>(1:0)</sec1>                 | refere               | ence_source_                       | frequency <s< td=""><td>EC1&gt;(3:0)</td></s<> | EC1>(3:0)    |  |  |  |  |