# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# 23V Buck-Boost Converter with Integrated MOSFETs

# **FEATURES**

- · Buck-Boost Converter with 4 Integrated Switches

- Wide VIN Range: 4V to 23V (No Dead Zone)

- 3.0V to 23V Wide output Voltage Range

- Seamless Transition between Buck and Boost Operation

- Supports Programmable Power Supply (PPS)

- Programmable Frequency: 125KHz, 250KHz, 500kHz, and 1MHz

- 2V ~ 5V/100mA Programmable Output LDO

- +/-4% Output Constant Current Regulation (@10mΩ, 3A)

- Programmable Output Voltage and Current via both Pin and I2C

- Enable Pin for Power On/OFF Control

- Output Cord Compensation

- Programmable Output Soft-Start

- Cycle by Cycle Current Limit

- Built in ADC for Temperature, Input and Output Voltage and Current Monitoring

- +  $25m\Omega$  FET from VIN to SW1

- 25mΩ FET from SW2 to VOUT

- $35m\Omega$  FET from SW1 to PGND

- 35mΩ FET from SW2 to PGND

- Thermal Protection

- Thermally Enhanced 32-Lead 4mx4mm QFN

# **APPLICATIONS**

- · Car Charger

- Docking Stations

- Multiple Power Source Supplies

- DC UPS

- Solar Powered Devices

- Solid-State Lighting

# GENERAL DESCRIPTION

The ACT510x is a buck-boost converter with 4 integrated MOSFETs. It offers a high efficiency, low component counts, compact solution for a wide input voltage range from 4V to 23V application.

The 4 internal low resistance NMOS switches minimize the size of the application circuit and reduce power losses to maximize efficiency. Internal high side gate drivers, which require only the addition of two small external capacitors, further simplify the design process. An advanced switch control algorithm allows the buckboost converter to maintain output voltage regulation with input voltages that are above, below or equal to the output voltage. Transitions between these operating modes are seamless and free of transients and subharmonic switching.

The ACT510x output voltage can be set between  $3V \sim 23V$  which can be configured by either external resistor divider or I2C. The output constant current limit and cord compensation makes it flexible for any kinds of protocols like USB PD, QC 3.0/4.0 etc. The system can be monitored and configured by I2C as well. The build-in ADC can be read for the information of input/output voltages and currents, die temperature, and generic input signals.

ACT510x integrated a 100mA LDO output with OCP/UVLO protection to provide power for the MCU and other peripheral components inside the system.

The ACT510x operation frequency can be configured from 125 kHz to 1MHz, makes the system design flexible for components size and efficiency optimization. The ACT510x has been optimized to reduce input current for applications which are sensitive to quiescent current draw, such as battery-powered devices.

The AC5101 is available in 32-pin, 4 x 4 mm FCOL QFN package.

# **ORDERING INFORMATION**

| PART NUMBER    | Fsw    | Feedback | ADC Converter Input |

|----------------|--------|----------|---------------------|

| ACT5101QI101-T | 500kHz | Internal | YES                 |

| ACT5102QI101-T | 500KHz | External | NO                  |

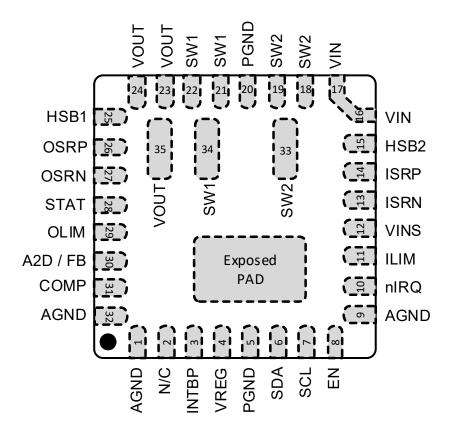

# **PIN CONFIGURATION**

Figure 1: Pin Configuration – Top View – QFN4x4-32

# **PIN DESCRIPTIONS**

| PIN             | NAME         | Туре | DESCRIPTION                                                                                                                                                                                                                                                          |  |

|-----------------|--------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1, 9, 32        | AGND         | Р    | Analog ground of the IC.                                                                                                                                                                                                                                             |  |

| 2               | NC           | Ι    | No connect                                                                                                                                                                                                                                                           |  |

| 3               | INTBP        | 0    | Internal Bypass - This should be connected to a 100nF ceramic capacitor                                                                                                                                                                                              |  |

| 4               | VREG         | I    | Internal VREG LDO output. The output voltage is programmable from 2V to 5V. Connect<br>a 1.0uF to this pin. The maximum current capability for this pin is 100mA. The internal<br>Overcurrent and over temp circuit shut down the converter when VREG is overloaded. |  |

| 5, 20           | PGND         | Р    | Power ground of the IC.                                                                                                                                                                                                                                              |  |

| 6               | SDA          | I/O  | I2C Interface data.                                                                                                                                                                                                                                                  |  |

| 7               | SCL          | Ι    | I2C Interface clock.                                                                                                                                                                                                                                                 |  |

| 8               | EN           | I    | Converter enable Input. The converter is active when this pin is pull low.                                                                                                                                                                                           |  |

| 10              | nIRQ         | Ι    | Interrupt IRQ open drain output.                                                                                                                                                                                                                                     |  |

| 11              | ILIM         | I    | Input maxim current setting pin. Connect a resistor from ILIM to AGND to program the maxim input current.                                                                                                                                                            |  |

| 12              | VINS         | Ι    | VIN Sense Input                                                                                                                                                                                                                                                      |  |

| 13              | ISRN         | Ι    | Negative input current sense amplifier inputs. Sense resistor is optional.                                                                                                                                                                                           |  |

| 14              | ISRP         | Ι    | Positive input current sense amplifier inputs.                                                                                                                                                                                                                       |  |

| 15              | HSB2         | Р    | High Side Bias Pin. This provides power to the internal high-side MOSFET gate driver.<br>Connect a 47nF capacitor from HSB2 pin to SW2 pin.                                                                                                                          |  |

| 16, 17          | VIN          | Р    | Input power pins. Decoupling capacitor should be placed from this pin to PGND.                                                                                                                                                                                       |  |

| 18, 19          | SW2          | Р    | Power switching output node to external inductor.                                                                                                                                                                                                                    |  |

| 21, 22          | SW1          | Р    | Power switching output node to external inductor.                                                                                                                                                                                                                    |  |

| 23, 24          | VOUT         | Р    | Output pins. Decoupling capacitor should be placed from this pin to PGND.                                                                                                                                                                                            |  |

| 25              | HSB1         | Р    | High Side Bias Pin. This provides power to the internal high-side MOSFET gate driver.<br>Connect a 47nF capacitor from HSB1 pin to SW1 pin.                                                                                                                          |  |

| 26              | OSRP         | Ι    | Output current sense resistor positive input.                                                                                                                                                                                                                        |  |

| 27              | OSRN         | Ι    | Output current sense resistor negative input.                                                                                                                                                                                                                        |  |

| 28              | STAT         | 0    | Open drain status output to indicate various charger operation. A LOW indicates converter is running. If converter is disabled for any reason, such as VOUT fault or VIN UV etc., STAT will go high.                                                                 |  |

| 29              | OLIM         | I    | Output constant current limit setting pin. Connect a resistor from OLIM to AGND to pro-<br>gram the output current.                                                                                                                                                  |  |

| 30<br>(ACT5101) | A2D          | I    | A2D Input Pin                                                                                                                                                                                                                                                        |  |

| 30<br>(ACT5102) | FB           | I    | Input FB pin                                                                                                                                                                                                                                                         |  |

| 31              | COMP         | 0    | Error Amplifier Output. This pin is used to compensate the converter.                                                                                                                                                                                                |  |

|                 | Power<br>Pad | Р    | Exposed pad. Must be shorted to ground on the PCB.                                                                                                                                                                                                                   |  |

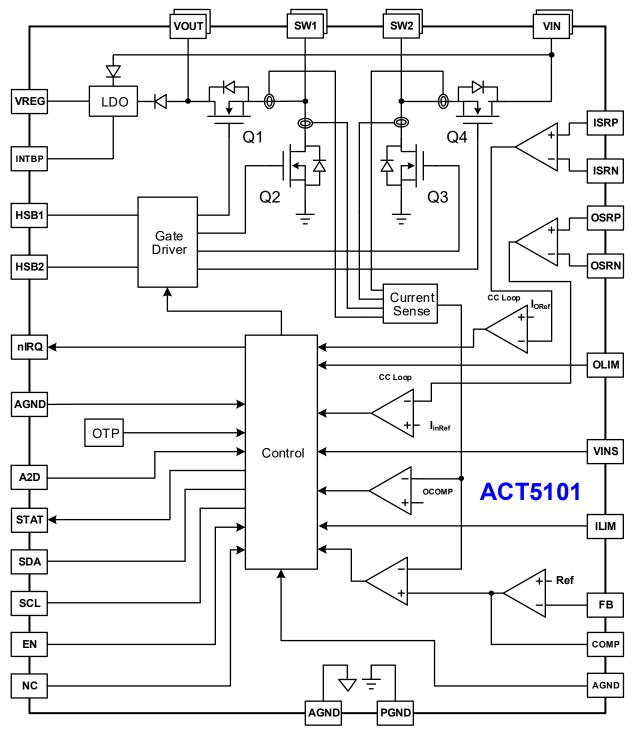

# FUNCTIONAL BLOCK DIAGRAM

Figure 2: Function Block Diagram

# **ABSOLUTE MAXIMUM RATINGS**

| PARAMETER                                                 | VALUE                                            | UNIT |

|-----------------------------------------------------------|--------------------------------------------------|------|

| VOUT                                                      | -0.3 to +24                                      | V    |

| OSRP, OSRN                                                | -0.3 to VIN + 0.3                                | V    |

| VIN                                                       | -0.3 to +23                                      | V    |

| ISRP, ISRN                                                | -0.3 to VBAT + 0.3                               | V    |

| VINS                                                      | -0.3 to ISRN + 0.3                               | V    |

| SW1                                                       | -0.3 to VOUT + 0.3                               | V    |

| SW2                                                       | -0.3 to VIN + 0.3                                | V    |

| HSB1                                                      | V <sub>SW1</sub> - 0.3 to V <sub>SW1</sub> + 5.5 | V    |

| HSB2                                                      | $V_{\text{SW2}}$ - 0.3 to $V_{\text{SW2}}$ + 5.5 | V    |

| VREG                                                      | -0.3 to +6V                                      | V    |

| SCL, SDA, VREG, STAT, EN, nIRQ, FB, COMP, ILIM, OLIM, A2D | -0.3 to +6                                       | V    |

| AGND to PGND                                              | -0.3 to +0.3                                     | V    |

| Junction to Ambient Thermal Resistance (θ <sub>JA</sub> ) | 35                                               | °C/W |

| Operating Junction Temperature (TJ)                       | -40 to 150                                       | °C   |

| Operating Ambient Temperature Range (T <sub>A</sub> )     | -40 to 85                                        | °C   |

| Store Temperature                                         | -55 to 150                                       | °C   |

| Lead Temperature (Soldering, 10 sec)                      | 300                                              | °C   |

|                                                           |                                                  |      |

Do not exceed these limits to prevent damage to the device. Exposure to absolute maximum rating conditions for long periods may affect device reliability.

# **ELECTRICAL CHARACTERISTICS**

(VIN = 5V,  $T_A$  = 25°C, unless otherwise specified)

|                                                                    | 1                  |                                                                                                      |       | -                        |       |      |

|--------------------------------------------------------------------|--------------------|------------------------------------------------------------------------------------------------------|-------|--------------------------|-------|------|

| PARAMETER                                                          | SYMBOL             | TEST CONDITIONS                                                                                      | MIN   | ТҮР                      | МАХ   | UNIT |

| Converter OPERATION                                                | 1                  |                                                                                                      |       |                          |       |      |

| Output Voltage Accuracy                                            | Vout_reg_acc       | Internal Feedback<br>VOUT_I2C Register = 1<br>Converter output in PWM Mode.<br>Measured at VOUT Pin  | -1    |                          | 1     | %    |

| FB Reference Voltage                                               | Vout_ref_acc       | External Feedback<br>VOUT_I2C Register = 0                                                           | 1.99  | 2                        | 2.01  | V    |

| Input UV Voltage                                                   | V <sub>IN_UV</sub> | VIN Rising<br>Measured at V <sub>IN_UV</sub> Register setting<br>Measured at VINS Pin                | -3.0  | Vin_uv                   | 3.0   | %    |

| Input UV Voltage Hysteresis                                        | VIN_UV_HSYT        | VIN Falling<br>Measured at V <sub>IN_UV</sub> measured value<br>Measured at VINS Pin                 | 3     | 4                        | 5     | %    |

| Input OV Threshold                                                 | VIN_OV             | VIN Rising<br>Measured at VINS Pin                                                                   | 22.75 | 23.5                     | 24.25 | V    |

| Input OV Hysteresis                                                | Vin_ov_hyst        | VIN Falling<br>Measured at VINS Pin                                                                  |       | 300                      |       | mV   |

| Output Current Range                                               | IOUT_RANGE         | With I <sub>CHG</sub> =100% register setting                                                         | 0.5   |                          | 5     | А    |

| Output Constant Current (measured at OSRN and OSRP pins)           |                    | $I_{OUT_{OCP}} = 0.5A$ to 1A                                                                         | -20   | I <sub>OUT</sub>         | +20   | %    |

| (10m $\Omega$ current sensing resistor)                            | IOUT_OCP           | IOUT_OCP = 1A to 2A                                                                                  | -15   | Іоит                     | +15   | %    |

| (20m $\Omega$ current sense resistor as option)                    |                    | Iout_ocp > 2A                                                                                        | -10   | Іоит                     | +10   | %    |

| Output Constant Current Undervolt-<br>age Protection Threshold     | Vout_uvp           | VOUT Falling, Enters Hiccup Mode<br>Internal or External Feedback<br>control<br>Measured at VOUT pin | 2.90  | 3.0                      | 3.10  | V    |

| Output Constant Current Undervolt-<br>age Protection Deglitch Time | tout_uvp           | Vout Falling                                                                                         |       | 7                        |       | us   |

| Hiccup Mode Off Time                                               | touт_ніссир        | Off time after V <sub>OUT</sub> falls below V <sub>OUT_UVP</sub>                                     |       | 3                        |       | sec  |

| Over-Voltage Threshold                                             | Vout_ovp_ext       | External Feedback<br>VOUT_I2C Register = 0<br>Voltage at FB Pin                                      | 2.18  | 2.24                     | 2.30  | V    |

| Over-Voltage Threshold Hysteresis                                  | Vout_ovp_hys       | Falling Threshold                                                                                    |       | 2                        |       | %    |

| Soft Start Time                                                    | tout_ss            | Measured at Soft Start Register<br>From 0 to 100%                                                    | -30   | SOFT<br>START<br>Setting | 30    | %    |

| Pulldown Current Source                                            | IOUT_PD            | V <sub>OUT</sub> Output > 2.0V                                                                       | 30    | 65                       | 120   | mA   |

| Pulldown Current Source                                            | IOUT_PD            | Vout Output > 2.0V                                                                                   | 30    | 65                       | 120   | n    |

#### Rev 1.0, 04-Apr-2018

|                               |                  |                                                                                                                                                   |      | ILEV                           | 1.0, 04- | Apr-2018 |

|-------------------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|------|--------------------------------|----------|----------|

| Off Delay Current Timer       | tout_off_dly     | EN_DLY Enabled                                                                                                                                    | -10  | OFF_DLY<br>Setting             | +10      | %        |

| Off Delay Current             |                  | OFF_LOAD=0<br>Converter in Buck Mode Only<br>V <sub>IN</sub> > V <sub>OUT</sub> + 0.5V                                                            | 0.5  | 1                              | 1.5      | mA       |

|                               | IOUT_OFF_LOAD    | OFF_LOAD=1<br>Converter in Buck Mode Only<br>V <sub>IN</sub> > V <sub>OUT</sub> + 0.5V                                                            | 4    | 5                              | 6        | mA       |

| Cord Compensation<br>Accuracy | Vout_cc          | Cord Compensation Enabled<br>CORD_COMP:<br>00: Disabled<br>01: 100mV<br>10: 200mV<br>11: 300mV<br>Measured at VOUT Pin                            | -15  | CORD_<br>COMP<br>Setting       | +15      | %        |

| Output Slew Accuracy          | tout_slew        | Output Slew Setting<br>OUTPUT_SLEW<br>00: 1.0V/ms<br>01: 0.5V/ms<br>10: 0.3V/ms<br>11: 0.1V/ms<br>Internal Feedback Only<br>VOUT_I2C Register = 1 | -20  | OUTPU<br>T_SLE<br>W<br>Setting | +20      | %        |

| Input Current ILIM            | Iilim            | IILIM = 0.5A to 1A                                                                                                                                | -20  | Iilim                          | +20      | %        |

| •                             |                  | I <sub>ILIM</sub> = 1A to 2A                                                                                                                      | -15  | I <sub>ILIM</sub>              | +15      | %        |

| PWM OPERATION                 |                  |                                                                                                                                                   |      |                                |          |          |

| Frequency Range               | fsw              |                                                                                                                                                   | 125  |                                | 1000     | kHz      |

| Operation Frequency Accuracy  | fsw              |                                                                                                                                                   | -10% |                                | +10%     | kHz      |

| Maximum PWM Duty Cycle        | D <sub>MAX</sub> |                                                                                                                                                   |      | 97                             |          | %        |

| VREG LDO                      | ·                |                                                                                                                                                   |      |                                |          |          |

| VREG Regulation Voltage       | VREG             |                                                                                                                                                   | 2    |                                | 5.1      | V        |

| VREG Regulation Accuracy      | VREGACC          | At Default Factory Setting                                                                                                                        | -2   |                                | 2        | %        |

| VREG Dropout                  | VREGDROPOUT      | Iout=100mA                                                                                                                                        |      |                                | 300      | mV       |

| VREG UVLO Threshold           | VREGUVLO         | VREG Falling                                                                                                                                      | 85   | 88                             | 91       | %        |

| VREG UVLO Hysteresis          | VREGUVLO_HYST    |                                                                                                                                                   |      | 2                              |          | %        |

| VREG Current Limit            | VREGILIM         | V <sub>VIN</sub> = 12V, VREG = 5V                                                                                                                 | 100  |                                | 200      | mA       |

| VREG Current Limit Deglitch   | VREGILIM_DG      | In current limit                                                                                                                                  |      | 50                             |          | us       |

| VREG Current Limit Off Time   | VREGILIM_OFF     | After Deglitch Time                                                                                                                               |      | 100                            |          | ms       |

| VREG Soft Start               | VREGss           |                                                                                                                                                   |      | 250                            |          | us       |

|                               |                  |                                                                                                                                                   |      |                                |          |          |

ACT510x Rev 1.0, 04-Apr-2018

|                                                       |                      |                                                                                                            |      | Rev              | ′ 1.0, 04- <i>I</i> | <u>Apr-201</u> |

|-------------------------------------------------------|----------------------|------------------------------------------------------------------------------------------------------------|------|------------------|---------------------|----------------|

| LOGIC I/O PIN CHARACTERISTICS                         | EN, STAT, nIRQ       |                                                                                                            |      |                  |                     |                |

| EN Input low threshold                                | VILO                 |                                                                                                            |      |                  | 0.4                 | V              |

| EN Input high threshold                               | VIHI                 |                                                                                                            | 1.25 |                  |                     | V              |

| STAT, nIRQ Output Low Voltage                         | Vol                  | Sink Current = 5 mA                                                                                        |      |                  | 0.4                 | V              |

| STAT, nIRQ High Level Leakage<br>Current              | Іон                  | Output = 5V                                                                                                |      |                  | 1                   | uA             |

| 12C INTERFACE CHARACTERISTIC                          | S                    | ·                                                                                                          |      |                  |                     |                |

| SCL, SDA Input low threshold                          | Vilo                 | Design Note: Need to be sure<br>supply current is 0 with 1.8V input<br>on pin                              |      |                  | 0.4                 | V              |

| SCL, SDA Input high threshold                         | VIHI                 | Design Note: Need to be sure<br>supply current is 0 with 1.8V input<br>on pin                              | 1.25 |                  |                     | V              |

| SDA Output Low                                        | Vol                  | Sink Current = 5 mA                                                                                        |      |                  | 0.4                 | V              |

| SDA High Level Leakage Current                        | Іон                  | Output = 5V                                                                                                |      |                  | 1                   | uA             |

| SCL Clock Frequency                                   | fscl                 |                                                                                                            | 0    |                  | 1000                | kHZ            |

| SCL Low Period                                        | t <sub>SCL_LOW</sub> |                                                                                                            | 0.5  |                  |                     | us             |

| SCL High Period                                       | t <sub>SCL_HI</sub>  |                                                                                                            | 0.26 |                  |                     | us             |

| SDA Data Setup Time                                   | t <sub>su</sub>      |                                                                                                            | 50   |                  |                     | ns             |

| SDA Data Hold Time                                    | t <sub>HD</sub>      |                                                                                                            | 0    |                  |                     | ns             |

| Start Setup Time                                      | ts⊤                  |                                                                                                            | 260  |                  |                     | ns             |

| Stop Setup Time                                       | t <sub>SP</sub>      |                                                                                                            | 260  |                  |                     | ns             |

| Capacitance on SCL or SDA PIN                         | CIN                  |                                                                                                            |      |                  | 10                  | pF             |

| Pulse Width of spikes suppressed on SCL and SDA       | <b>t</b> deglitch    |                                                                                                            |      |                  | 50                  | ns             |

| I2C Timeout Function                                  | t <sub>out</sub>     | Total time required for I <sup>2</sup> C communication to<br>cause I <sup>2</sup> C state machine to reset |      | 100              |                     | ms             |

| THERMAL REGULATION AND THE                            | RMAL SHUTDOW         | N                                                                                                          |      |                  |                     |                |

|                                                       |                      | Charger Mode                                                                                               |      |                  |                     |                |

|                                                       |                      | 00: 60 °C                                                                                                  |      |                  |                     |                |

| Charger Mode Junction Temperature Regulation Accuracy | T <sub>REG</sub>     | 01: 80 °C                                                                                                  | -20  | T <sub>REG</sub> | +20                 | °C             |

|                                                       |                      | 10: 100 °C                                                                                                 |      |                  |                     |                |

|                                                       |                      | 11: 120 °C                                                                                                 |      |                  |                     |                |

| Thermal Shutdown Rising<br>Temperature                | Тѕнит                | Temperature Increasing                                                                                     |      | 160              |                     | °C             |

|                                                       |                      | 1                                                                                                          |      |                  |                     |                |

#### Rev 1.0, 04-Apr-2018

| Thermal Shutdown Hysteresis | T <sub>SHUT_HYS</sub> |                                | 30   |     | °C  |

|-----------------------------|-----------------------|--------------------------------|------|-----|-----|

| Thermal Shutdown Deglitch   |                       | Enter or Exit Thermal Shutdown | 32   |     | us  |

| A2D Converter               |                       |                                |      |     |     |

| Total Error                 | A2D <sub>ERROR</sub>  | 12 Bit Range                   |      | 0.5 | LSB |

| Conversion Time             | A2D <sub>tCONV</sub>  | All 8 Channels                 |      | 100 | ms  |

| Conversion Time             | A2D <sub>tCONV</sub>  | 1 Channel                      |      | 15  | ms  |

| Input Capacitance           | A2D <sub>CIN</sub>    |                                | 5    |     | pF  |

| A2D Full Scale Input EXT_IN | A2D <sub>FS</sub>     |                                | 2.5  |     | V   |

| A2D Full Scale VOUT         | A2D <sub>VOUT</sub>   | Measurement input at VOUT pin  | 32.5 |     | V   |

| A2D Full Scale VIN          | A2D <sub>VIN</sub>    | Measurement input at VINS Pin  | 25   |     | V   |

| A2D Full Scale OLIM, ILIM   | A2Dolim, A2Dilim      |                                | 2.5  |     | V   |

# **FUNCTIONAL DESCRIPTION**

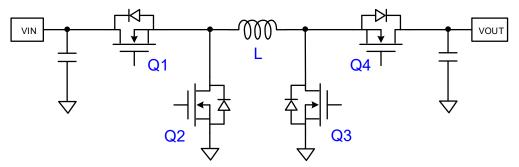

### 1. Buck-Boost Structure

The ACT510x is a monolithic buck-boost converter with integrated FETs. Four internal low resistance NMOS switches minimize the size of the application circuit and reduce power losses to maximize efficiency. Internal high side gate drivers, which require only the addition of two small external capacitors, further simplify the design process. An advanced switch control algorithm allows the buck-boost converter to maintain output voltage regulation with input voltages that are above, below or equal to the input voltage. Transitions between these operating modes are seamless and free of transients and subharmonic switching.

Figure 3: Diagram for 4-Switches Buck-Boost Converter

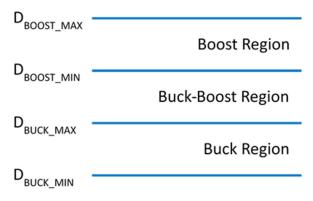

Figure 4: Operation Mode and Regions

Figure 3 shows a simplified diagram of how the four power switches are connected to the inductor, VIN, VOUT and GND. Figure 4 shows the regions of operation for the ACT510x as a function of duty cycle D. The power switches are properly controlled so the transfer between modes is continuous. When VIN approaches VOUT, the buck-boost region is reached.

Table 1: MOSFET Operation

| MODE | BUCK      | BUCK-BOOST | BOOST     |

|------|-----------|------------|-----------|

| Q1   | SWITCHING | SWITCHING  | ON        |

| Q2   | SWITCHING | SWITCHING  | OFF       |

| Q3   | OFF       | SWITCHING  | SWITCHING |

| Q4   | ON        | SWITCHING  | SWITCHING |

### 2. Operation States

#### 2.1. Reset State (RST)

The state machine for the converter always starts from the Reset State. The device waits until all the criteria below are met and then starts the Enable Delay Timer. This timer is controlled by *EN\_DLY[1:0]* Register 0x0F Bits 1:0. Once the timer has expired, it will jump out of the Reset state and move to the SS state

**Reset Faults:**

- 1. VIN below VIN\_UV voltage: This fault will self-clear and device will exit the Reset when the VIN is higher than the threshold.

- 2. VREG LDO OK This fault will automatically clear when the VREG LDO has exited the faulted condition and UVLO is low. This includes the 100msec timeout period. Once the VREG LDO regulator is at an acceptable level, the device will exit the Reset state. Note: This fault can be masked to allow the state machine to exit the Reset while there is a fault on the VREG LDO using the DIS\_VREG\_FLT Register 0x10 Bit 1.

- 3. Watchdog Timer Fault: If the watchdog timer is enabled and the timer ties out, the Watchdog fault will hold the charger in the RST state until the watchdog timer is reset or cleared. It can be reset with a write to of 1 to the *WATCHDOG\_RESET* Register bit or by disabling the Watchdog timer with *WATCHDOG[1:0]* Register = 00.

- 4. FET Overcurrent Fault: If a switching FET exceeds the cycle by cycle current limit for 8 (or 16) cycles, the FET\_OC fault is latched. To clear this latch, the device must exit the operation mode and enter HIZ mode, typically by toggling the EN pin or setting the *HIZ* register to HI.

- 5. VIN Overvoltage: If the VIN exceeds the  $V_{IN_OV}$ , the device will enter the Reset state. The OV fault will self-clear when the VIN is below the  $V_{IN_OV}$  and exit the Reset state.

- 6. Die Thermal Shutdown (TSD) If the die exceeds the T<sub>SHUT</sub> (160°C) this fault will hold the converter in the FAULT state until it cools down by the T<sub>SHUT\_HYST</sub> (T<sub>SHUT</sub> 30°C). This fault cannot be cleared or masked. The device must cool down before exiting the Reset state. Once the device cools down, it will automatically clear this fault and exit the Reset state and resume operation.

#### 2.2. Soft Start (SS)

The device enables the converter and ramps the soft start output in this mode. Soft start time is controllable by the *SOFT START* [1:0] Register. If a fault occurs during the soft start, it will jump back to the Reset state and disable the converter. Once the soft start is done, the device jumps to the Regulation state.

#### 2.3.Regulation State (REG)

The normal regulation occurs in the Regulation state. If a major fault occurs during the device will jump back to the Reset state and disable the converter. During this state, the converter can be disabled with light load condition. Additionally, if the output drops below  $V_{OUT\_UVP}$  (3.0V), the device will go into a hiccup mode to protect the output in a shorted condition.

#### 2.4.Light Load Disable State (LL\_DIS)

If the device senses light load in Regulation state, the converter will be disabled after the *OFF\_DLY[1:0]* timer expires. During this state, the converter is disabled and there is minimal load on the VIN. To exit this state, the device must exit converter mode by the EN pin or *HIZ* register. The light load disable function can be disabled in the register bit.

#### 2.5. Hiccup / Vout Fault State (HICCUP)

If the output cannot support the load and enters Constant Current mode in Regulation state, the output will eventually drop below the  $V_{OUT\_UVP}$  (3.0V). If this occurs, the converter is disabled for 3 secs, and then automatically re-enters the Reset mode to restart the output. If there is a fault on the output, this cycle will continue until the fault is removed.

### 3. Device Power Up

#### 3.1.Power-On-Reset (POR)

When VIN or VOUT is above 3.9V, the I2C bus is ready for communication and the VREF LDO is enabled. All registers are reset to the default value as listed in the register map.

#### 3.2.HIZ Mode

The device goes into HIZ mode when EN is pin HI, or *HIZ* Register 0x00 Bit 7 is set HI. At HIZ mode, the internal bias circuits are enabled, all registers are accessible and ADC functions can be enabled. If the VREG\_EN Register 0x01 Bit 2 is HI, then the VREG LDO will be enabled.

#### 3.3.VREG LDO

The VREG LDO is powered from VIN or VOUT with a smart active diode selector circuit.

To reduce power dissipation, the VREG LDO will be powered from the lower of the VIN or VOUT. However, if the lower supply cannot provide the headroom needed to regulate VREG output, it will select the higher supply.

This smart diode selector can be overridden and manual control can be selected using the *VREG\_OVERRIDE* and *VREG\_SELECT* Registers 0x0B, bits 1:0.

The VREG is enabled when all the conditions are valid:

- VIN or VOUT above UVLO (3.9V)

- VREG\_DIS Register is bit is set LO (Register 0x01 Bit 2)

- This register bit can be programmed from the factor to be HI or LO depending on the application requirements

The voltage of VREG LDO can be set by Register 0x11 [7:3] between 2V to 5.1V. The maximum output current is 100mA. If VREG LDO is overloaded or not within spec, converter will be shut down, and *VREG\_OC\_UVLO* fault bit Register 0x05 Bit 4 is set.

Additionally, if the VREG\_LDO is held in current limit for more than 50usec, it will shut down for 100msec to prevent damage. It will then re-try to start after 100msec. It will continue this cycle until the current limit condition is removed. Additionally, there is a UVLO detection for the VREG output set at 88%.

If the VREG output is in current limit, or below the UVLO threshold, the converter will be in a Fault state or Reset state and not operate. This can be overwritten with *DIS\_VREG\_FLT* Register 0x10 Bit 1.

To reduce inrush current, a 250usec soft-start is included. For stability, a 1uF ceramic capacitor is required on the output.

### 4. Host Mode and Default Mode

The ACT510x is a host controlled device, but it can operate in default mode without host management. In default mode, ACT510x can be used an autonomous converter with no host or with host in sleep. In this mode, the *WATCHDOG[1:0]* Register 0x01 Bits 1:0 must be set LO to disable the watchdog timer. Additional register bits may need to be set to allow this mode.

### 5. Converter Operation

The ACT510x can be enabled if the conditions are valid (see operating states for further details):

- 1. EN Pin is Low or EN\_OVERRIDE bit is HI

- 2. HIZ Register bit is low

- 3. EN Register bit is HI

The output voltage can be set by the internal resistor divider or the feedback resistor divider on the FB pin using the *VOUT\_I2C* Register 0X13 [3]. When the internal resistor divider network is used, the output voltage can be changed by

ACT510x

*VOUT[10:0]* voltage register. The ramp rate the output changes can be controlled by the *OUTPUT\_SLEW[1:0]* register. This allows the output to conform to QC2.0/QC3.0/4.0/USB PD functions for higher output voltages.

If external feedback is used, the reference voltage on FB is 2V. The COMP pin is used for the output compensation.

Input voltage must stay above V<sub>IN\_UV</sub> set by *VIN\_UV* Register 0x0F [7:5].

#### 5.1. Enable Delay

Once the condition has the valid conditions for startup, the Enable Delay timer is enabled. The timer options allow an immediate startup, or to wait between 200msec and 1sec before enables the converter. This timing is controlled by the *EN\_DLY[1:0]* register.

#### 5.2. Mode Soft Start

After the Enable Delay has completed, the device starts the output using a soft start function programmable by the *SS[1:0]* Register. The time is independent of the output voltage setting if using internal feedback and or resistor settings when using external feedback.

#### 5.3. Constant Current Output Regulation

After soft start is completed, the device monitors the current on sense resistor (OSRP and OSRN) to provide constant current regulation. When the output current exceeds threshold the value configured by the OLIM Pin and CC Register, the switching converter will regulate the maximum current in a "constant current" mode. In this case, the output voltage may drop. Constant current mode can be monitored in real time using the read only *Output\_CC* Register 0x20 [5].

The current can be controlled with the external resistor on the OLIM pin and by the CC [6:0] Register 0x17 [6:0]. Current is adjustable as a percentage of the full current level set by the OLIM resistor.

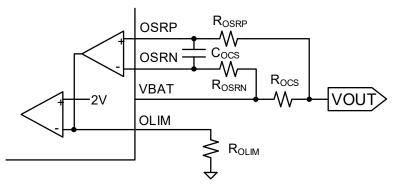

Figure 5: Charge Current Sensing and Current Limit Setting

This voltage on the OLIM pin is calculated by:

The voltage on this pin is regulated and clamped at 2V. The OLIM pin can also be used to monitor input current .The voltage on OLIM pin is proportional to the charge current.

The filter cap Cocs should be 470nF, and RosrP and RosrN should be  $30\Omega$ .

If the output drops below 2.72V, a fault on the output is assumed, and the converter will disable and wait 3 seconds in the HICCUP state. After 3 seconds, the device will return to the Reset state and attempt to restart the output. If a short or high current fault is present, it will cycle again through the states until the fault is removed.

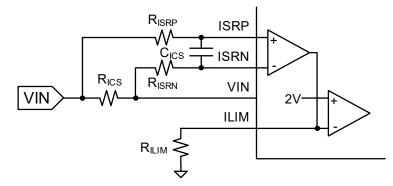

#### 5.4. Input Current Regulation

ACT510x monitors the current on input side sense resistor (ISRP and ISRN) to provide a current limit from the input. When the input current exceeds threshold the value configured by the ILIM Pin and *INPUT\_ILIM* Register 0x10 [3:2], the switching converter will regulate the output current in a "constant current" mode. In this case, the output voltage may drop. Input constant current mode can be monitored in real time using the read only *INPUT\_CC* Register 0x20 [6].

Input current limit can be set by the ILIM pin and INPUT\_ILIM [1:0] Registers 0x10 [3:2]

This voltage on the ILIM pin is calculated by:

$$V_{ILIM} = R_{ICS} \times I_{IN} \times R_{ILIM} \times 2 \times 10^{-3}$$

Equation 2

The voltage on this pin is regulated and the charger goes into input current limit mode and starts to reduce the charger current when this pin voltage reaches 2V. The ILIM pin can also be used to monitor input current .The voltage on ILIM pin is proportional to the input current.

The filter cap C<sub>ICS</sub> should be 470nF, and R<sub>ISRP</sub> and R<sub>ISRN</sub> should be  $30\Omega$ .

If input current limit function is not needed, it can be disabled in INPUT\_ILIM Register 0x10 [3:2].

#### 5.5. VOUT Over-Voltage Protection

ACT510x monitors the output voltage and immediately stop switching when senses an overvoltage condition. If the OV condition lasts for 100msec, then the device will enter HIZ state.

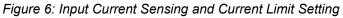

#### 5.6. Regulator Compensation and Inductor Selection

| Frequency<br>Setting | Inductor MIN<br>(uH) | Inductor TYP<br>(uH) | Inductor Max<br>(uH) | С <sub>сомр1</sub><br>(nF) | С <sub>сомР2</sub><br>(nF) | R <sub>сомР</sub><br>(KOhms) | С <sub>оυт</sub><br>(uF) |

|----------------------|----------------------|----------------------|----------------------|----------------------------|----------------------------|------------------------------|--------------------------|

| 125Khz               | 29                   | 42                   | 55                   | 82                         | 8.2                        | 20.0                         | 1000 / 47                |

| 250Khz               | 15                   | 22                   | 29                   | 39                         | 3.9                        | 20.0                         | 470 / 47                 |

| 500KHz               | 7                    | 10                   | 13                   | 22                         | 2.2                        | 20.0                         | 220 / 47                 |

| 1MHZ                 | 4                    | 5.6                  | 7.28                 | 10                         | 1.0                        | 20.0                         | 100 / 47                 |

Table 2: L/C Selection Table

47uF is low ESR Ceramic Type. 100uF to 1000uF is bulk electrolytic capacitor.

#### Figure 7: OTG Mode External Compensation Network

#### 5.7. Cord Compensation

ACT510x provides cord compensation at the output. The output voltage is increased with output current to compensate the potential voltage drop across output cable. The amount of cord compensation can be adjusted with the *CORD\_COMP[1:0]* register.

| CORD_COMP[1:0] | Cord Comp Value |

|----------------|-----------------|

| Setting        | At 2.4A Load    |

| 00             | 0 (Disabled)    |

| 01             | 100mV           |

| 10             | 200mV           |

| 11             | 300mV           |

| Table D. Outrust | <b>^</b> | O            | 0 - 41: |

|------------------|----------|--------------|---------|

| Table 3: Output  | Cora     | Compensation | Setting |

The cord compensation loop should be very slow to avoid potential disturbance to the voltage loop. The voltage loop should be sufficiently stable on various cord compensation setting.

#### 5.8. Light Load Disable

We the device is operating in BUCK mode and VIN is higher than VOUT by a minimum of 0.5V, the device can detect light load / no load case and disable the converter. The *OFF\_LOAD\_EN* should be set to 1 to enable this feature. The *OFF\_LOAD* controls the amount of load on the output that can be detected as light load. Finally, the detection time is set by the *OFF\_DLY[1:0]* setting. Once the state machine has detected a light load condition, it enters the LL\_DIS state, and the converter must be re-enabled to resume operation, such as toggling the EN pin.

#### 5.9. Output Ramp and Vout OV

To conform to various charging specification, such as QC2.0/3.0/4.0 or USB-PD, the VOUT can be dynamically changed by writing to the *VOUT[10:0]* Register, if internal feedback is used and VOUT\_I2C is set to 0. The *OUTPUT\_SLEW[1:0]* register is used to control the slew rate between settings when the *VOUT[10:0]* is changed. When the voltage is increased, the internal ramp and regulator can compensate and increase the voltage. However, when the voltage is decreased, and there is no external load on the output, the VOUT may not decrease fast enough to the meet the requirements of QC2.0/3.0/4.0 or USB-PD. To meet the requirement, if the *PULLDOWN\_RAMP*=1, an internal 70mA load will turn on when the VOUT is required to decrease from a change in the *VOUT[10:0]* register.

If external feedback is used, and the feedback resistor is changed, the *PULLDOWN\_OV* can be enabled. If this bit is set HI, whenever the VOUT goes into OV, the internal 70mA pulldown load will turn on to help regulate the output during a voltage transition.

#### 5.10. Die Thermal Regulation

The ACT510x monitors the internal junction temperature  $T_J$  to avoid overheat the chip and limits the IC junction temperature. When the internal junction temperature exceeds the preset thermal regulation limit set by *TREG [1:0]*, the device lowers down the output constant current limit threshold to reduce the output current. The wide thermal regulation range from 80°C to 120°C allows the user to optimize the system thermal performance. In addition, this function can be disabled using the *TREG[1:0]*.

#### 5.11. Status Output Pin (STAT)

The ACT510x can indicate converter state on the open drain STAT pin. The STAT pin is mainly used to drive an LED, it can be enabled/disabled by using the *EN\_STAT* Register 0x0F [4].

The table below shows the general operation:

ACT510x Rev 1.0, 04-Apr-2018

Table 4: STAT pin State

| State                                                       | STAT Output Pin |

|-------------------------------------------------------------|-----------------|

| Converter Enabled and Output Valid                          | LOW             |

| Converter Disabled                                          | HIZ             |

| Converter Enabled but in Fault, Hiccup or Light Load states | HIZ             |

# 6. Interrupt Output Pin (nIRQ)

The nIRQ output pin can be used to signal a fault or other system effects. The conditions below can active the nIRQ Pin and all of them can be masked individually using the IRQ Control Registers 0x1E and 0x1F. To clear the nIRQ and deassert the nIRQ pin, the nIRQ\_CLEAR must be written to a 1. The nIRQ\_CLEAR is a self-clearing register bit. If the nIRQ\_CLEAR is read, it will always be a 0, even if it has been written to 1.

- 1. **Watchdog Expired** If the watchdog timer expires at any time, it will active the nIRQ Pin. This is level sensitive function. The watchdog timer must be reset or disabled and *nIRQ\_CLEAR* must be written to 1 for the nIRQ to be de-asserted. No watchdog in HIZ so cannot be triggered HIZ mode.

- 2. **VREG LDO Overcurrent or Under-voltage Lockout** Any time the VREG LDO is in overcurrent or under-voltage lockout, the nIRQ will be asserted. This is a level sensitive function. The VREG LDO must be in regulation AND *nIRQ\_CLEAR* must be written to a 1 for nIRQ to be de-asserted. If the VREG LDO is in the 100msec shutdown wait period, it will not clear the nIRQ output. This fault WILL be valid in all modes, including HIZ Mode.

- Die Over Temperature Shut Down Any time the die temperature exceeds the T<sub>SHUT</sub> (160°C) threshold, the nIRQ will be asserted. This is a level sensitive function. The die temperature must be below the T<sub>SHUT\_HYST</sub> AND nIRQ\_CLEAR must be written to 1 for nIRQ to be de-asserted.

- FET Overcurrent Fault If the device is disabled from switching because of FET overcurrent fault, the nIRQ will be asserted. This is a level sensitive function. This fault is latched, so the latch must cleared AND *nIRQ\_CLEAR* must be written to 1 for nIRQ to be de-asserted.

- 5. **A2D Data Ready** If the A2D is enabled, and a conversion is completed the nIRQ pin will be asserted. This is an edge triggered event and only a write to1 of *nIRQ\_CLEAR* is needed to de-assert the nIRQ pin. This can be active in all modes, when the A2D is enabled.

- 6. **HIZ Enter** If the devices enters HIZ mode the nIRQ pin will be asserted. This is an edge triggered event and only a write to 1 of the *nIRQ\_CLEAR* is needed to de-assert the nIRQ pin. This is used to signal a fault or other condition that might have caused the device to jump out of operation mode un-expectantly.

- I2C Fault If the I2C command requires more than 100msec to complete, then a fault is latched on the rising edge of the error. This fault will get reset when another I2C command completes correctly, but is latched with the Reg 0x06 Bit 1.

- 8. **VOUT OV (30V)** If the VOUT is above V<sub>OUT\_OVP</sub> (30V), the nIRQ will be asserted. This is a level sensitive function.

- 9. VIN above V<sub>IN\_OV</sub> (23.5V) If the VIN is above V<sub>VIN\_OV</sub> (23.5V), the nIRQ will be asserted. This is a level sensitive function.

- 10. **VIN UV** Any time the VIN is below VIN\_UV threshold, the nIRQ will be asserted. This is a level sensitive function. VIN must be in the valid range AND nIRQ\_CLEAR must be written to 1 for nIRQ to be de-asserted.

- 11. Light Load Disable State Any time the device enters the LL\_DIS state, the nIRQ will be asserted until the nIRQ\_CLEAR Register is written to 1. The nIRQ is triggered with a "rising edge" of the LL\_DIS state and does not require exiting the state to de-assert the nIRQ pin.

- 12. Hiccup Mode / Vout Fault State Any time the device enters the HICCUP state, the nIRQ will be asserted until the nIRQ\_CLEAR Register is written to 1. The nIRQ is triggered with a "rising edge" of the HICCUP state and does not require exiting the state to de-assert the nIRQ pin.

### 7. Protections

#### 7.1. Thermal Shutdown

The device has thermal shutdown to disable the converter when IC junction temperature exceeds  $T_{SHUT}$  (160°C). The fault register *TSD* is set and latched when TSD fault is detected. The converter will restart automatically once the temperature of the DIE falls below the  $T_{SHUT_HYST}$  value. During this time, however, the TSD indicator register may still be latched until it is read.

#### 7.2. FET Over Current Protection

The ACT510x closely monitors the HSFETs and LSFETs current for safe operation. If any FET exceeds the FET\_ILIMIT value (8.5A or 10A), the FET will immediately be turned off for that cycle. If a FET detects the current limit for 8 continuous cycles, then the converter is latched off. This latch can be disabled by setting the *DIS\_OCP\_SHUTDOWN* Register. Once FET Overcurrent protection is latched, device must go back to the HIZ state to clear the Fault or set DIS\_OCP\_SHUTDOWN bit to 1. For example, EN pin must be toggled.

#### 7.3. Watchdog Timer

To ensure there is not system failure, a watchdog timer is included. The timeout is controlled by *WATCHDOG[1:0]* Register 0x01 [1:0]. The settings from 40sec to 160sec allow a wide range of timeout. It can also be disabled, such as for standalone operation with the *WATCHDOG[1:0]*=00.

If the watchdog timer is enabled, the *WATCHDOG\_RESET* needs to be written to a 1 before the timer times out. Note the WATCHDOG\_RESET is an auto-clearing register. If it is written to 1, it will automatically reset back to 0.

WATCHDOG is always disabled in HIZ Mode and cannot be enabled in HIZ. In addition, the reset counter is reset to 0 when entering HIZ mode and automatically restarted when exiting HIZ mode into regulation mode.

### 8. System ADC Monitor

The ACT510x includes an A2D Converter to provide various system parameters during the modes of operation.

| Channel | Channel Description      | ADC_CH_CONV[2:0] | ADC_CH_READ[2:0] | Value                                                     |

|---------|--------------------------|------------------|------------------|-----------------------------------------------------------|

| CH0     | Output Current (OLIM)    | 000              | 000              | I <sub>IN</sub> = (DOUT-2048)/(65000*R <sub>CS_IN</sub> ) |

| CH1     | Output Voltage<br>(VOUT) | 001              | 001              | V <sub>IN</sub> = 0.02035*(DOUT-2048)                     |

| CH2     | Input Current (ILIM)     | 010              | 010              | Iouт = (DOUT-2048)/(65000*Rcs_out)                        |

| CH3     | Input Voltage (VIN)      | 011              | 011              | V <sub>OUT</sub> = 0.02035*(DOUT-2048)                    |

| CH4     | ТН                       | 100              | 100              | V <sub>TH</sub> = 0.003053*(DOUT-2048)                    |

| CH5     | Die Temperature          | 101              | 101              | T <sub>J</sub> = 0.2707*DOUT - 809.49                     |

| CH6     | ADC Input                | 110              | 110              | V <sub>ADC</sub> = 0.001527*(DOUT-2048)                   |

The A2D Inputs are the following:

### 9. PFM/PWM Operation

At light load, ACT510x operates in the PFM (pulse skipping) mode to save the switching power loss. The PFM can be disabled by the register bit.

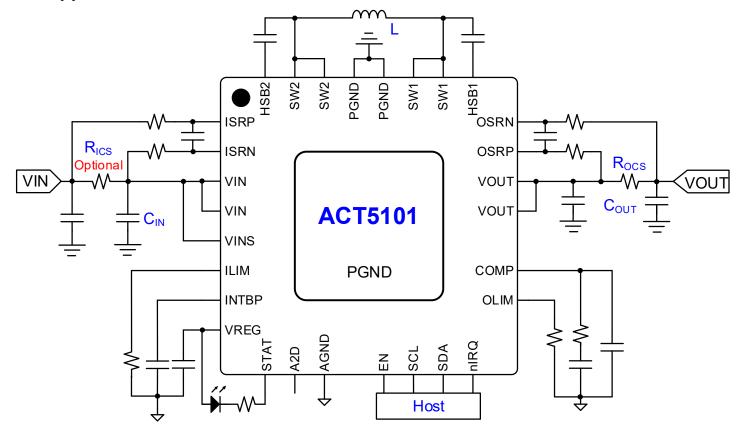

# **APPLICATION**

**Application Schematics**

# **I2C REGISTER**

# **Basic I<sup>2</sup>C Registers Summary**

| Reg  | Register Name        | Туре | R/W | Description                                 | Default |

|------|----------------------|------|-----|---------------------------------------------|---------|

| 0x00 | Master Control 1     | VM   | R/W | Configure verieue device entiene            | 00      |

| 0x01 | Master Control 2     | NVM  | R/W | Configure various device options            | 00      |

| 0x02 | General Status 1     | VM   | R   | Device status                               | 00      |

| 0x03 | Charger Status 2     | VM   | R   | Charger status                              | 00      |

| 0x04 | RFU                  | VM   | R   |                                             | 00      |

| 0x05 | Fault 1              | VM   | R   | Device Faults                               | 00      |

| 0x06 | Fault 2              | VM   | R   |                                             | 00      |

| 0x07 | ADC Output 1         | VM   | R   | ADC Output                                  | 00      |

| 0x08 | ADC Output 2         | VM   | R   |                                             | 00      |

| 0x09 | ADC Configuration 1  | VM   | R/W | ADC configuration bits                      | 00      |

| 0x0A | ADC Configuration 2  | VM   | R/W |                                             | 00      |

| 0x0B | VREG Input           | NVM  | R/W | Configure VREG Input Source                 |         |

| 0x0C | RFU                  | NVM  | R/W |                                             |         |

| 0x0D | RFU                  | NVM  | R/W |                                             |         |

| 0x0E | Converter Control 1  | NVM  | R/W |                                             |         |

| 0x0F | Converter Control 2  | NVM  | R/W | Configure Converter Operation               |         |

| 0x10 | Converter Control 3  | NVM  | R/W |                                             |         |

| 0x11 | VREG Voltage         | NVM  | R/W | 5bit, 2.0 ~ 5.1V, LSB = 100mV, Default = 5V |         |

| 0x12 | RFU                  | NVM  | R/W |                                             |         |

| 0x13 | Output Voltage 1     | NVM  | R/W | 11-bit, 3.6 ~ 24.07V, LSB = 10mV, Default = |         |

| 0x14 | Output Voltage 2     | NVM  | R/W | 5V                                          |         |

| 0x15 | RFU                  | NVM  | R/W |                                             |         |

| 0x16 | RFU                  | NVM  | R/W |                                             |         |

| 0x17 | Output Current Limit | NVM  | R/W | 7-bit, 0 ~ 100%, LSB = 1%, Default = 100%   |         |

| 0x18 | RFU                  | NVM  | R/W |                                             |         |

| 0x19 | RFU                  | NVM  | R/W |                                             |         |

| 0x1A | VIN UV OFFSET        | NVM  | R/W |                                             |         |

**ACT510x**

Rev 1.0, 04-Apr-2018

ACT510x Rev 1.0, 04-Apr-2018

| 0x1B | RFU                           | NVM | R/W |                                     |

|------|-------------------------------|-----|-----|-------------------------------------|

| 0x1C | RFU                           | NVM | R/W |                                     |

| 0x1D | Frequency                     | NVM |     |                                     |

| 0x1E | IRQ Control 1                 | VM  | R/W | IRQ Mask Control                    |

| 0x1F | IRQ Control 2                 | VM  | R/W |                                     |

| 0x20 | IRQ Control/ Converter Status | VM  | R   | IRQ Mask Control / Converter Status |

| 0x21 | Device ID                     | NVM | R   | Device ID and CMI numbers           |

### REG 0x00: Main Control 1 (R/W) (VM)

| Bit | Name                  | Default<br>Value | Reset by<br>REG_RST | Description                            | Comment                                                                                                                                                             |

|-----|-----------------------|------------------|---------------------|----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | HIZ                   | 0                | Y                   | 0: Not in HIZ mode<br>1: In HIZ mode   | Bit to control if IC is in HIZ mode.                                                                                                                                |

| 6   | RFU                   | 0                | Y                   |                                        |                                                                                                                                                                     |

| 5   | RFU                   | 0                | Y                   |                                        |                                                                                                                                                                     |

| 4   | RFU                   | 0                | Y                   |                                        |                                                                                                                                                                     |

| 3   | RFU                   | 0                | Y                   |                                        |                                                                                                                                                                     |

| 2   | WATCHDOG_RESET        | 0                | Y                   | <b>0: Normal</b><br>1: Reset           | I2C Watchdog Timer Reset<br>This must be written to 1 before Watchdog timer expires,<br>if Watchdog timer is enabled. This is auto clearing when<br>writing to a 1. |

| 1   | Audio Frequency Limit | 0                | Y                   | <b>0: No limit</b><br>1: Minimum 40kHz | <ul><li>0: No limit of switching frequency</li><li>1: Set minimum switching frequency to 40kHz to avoid audio noise</li></ul>                                       |

| 0   | REGISTER_RESET        | 0                | NA                  | 1: Reset Registers to<br>Default       | Register is self-clearing. Write to 1 resets registers and set reset register back to 0.                                                                            |

### REG 0x01: Main Control 2 (R/W) (NVM)

| Bit | Name                 | Default Value | Reset by<br>REG_RST | Description             | Comment                                                                                                                                                                                |

|-----|----------------------|---------------|---------------------|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | RFU                  | 1             | Y                   |                         |                                                                                                                                                                                        |

| 6   | DIS_OCP_SHUTDO<br>WN | 1             | Y                   | 0: Enable<br>1: Disable | If set to 0, the device will be disabled if FET cycle by cycle current limit is detected for 8 (or 16) continuous cycles. Uses the <i>FET_LIMIT</i> register setting for the FET ILIM. |

| 5   | DIS_VIN_OVP          | 0             | Y                   | 0: Enable<br>1: Disable | When set to 1, a VIN_OVP fault does not latch off the charger in a fault mode. Charger will restart automatically when the OVP condition is removed.                                   |

| 4   | FET_ILIMIT           | 1             | Y                   | 0: 8.5A<br>1: 10A       | This is the cycle by cycle current limit setting for ALL FETS in any operating mode:                                                                                                   |

Rev 1.0, 04-Apr-2018

**ACT510x**

| 3 | VOUT_OV_RESTART<br>_DELAY | 0 | Y | 0: 40ms<br>1: 100usec               | Delay time to restart in charger mode after Output OV fault has been removed          |

|---|---------------------------|---|---|-------------------------------------|---------------------------------------------------------------------------------------|

| 2 | VREG_DIS                  | 1 | Y | 0: Turn on VREG<br>1: Turn off VREG | Control VREG on/off<br>Default is on.                                                 |

| 1 | WATCHDOG[1]               | 0 | Y | 00: Disable timer<br>01: 40s        | I2C Watchdog Timer Setting<br>Watchdog timer is always disabled and reset to 0 in HIZ |

| 0 | WATCHDOG[0]               | 0 | Y | 10: 80s<br>11: 160s                 | Mode.<br>When Disabled, Watchdog timer is also reset to 0.                            |

# REG 0x02: General Status 1 (Read Only) (VM)

| Bit | Name              | Default Value | Reset by<br>REG_RST | Description                                                               | Comment                                                                                                                                                             |

|-----|-------------------|---------------|---------------------|---------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | RFU               | NA            | NA                  |                                                                           |                                                                                                                                                                     |

| 6   | nIRQ_PIN_Status   | NA            | NA                  | 0: Our device output<br>drive HIZ<br>1: Our device output<br>asserted Low | Device status of IRQ output<br>Not actual status of the IRQ pin – Open drain output so<br>other devices could be driving the pin low in a wired OR<br>configuration |

| 5   | EN_PIN_STATUS     | NA            | NA                  | 0: EN Pin Low<br>1: EN Pin High                                           | Real time status of the EN pin                                                                                                                                      |

| 4   | RFU               | NA            | NA                  |                                                                           |                                                                                                                                                                     |

| 3   | RFU               | NA            | NA                  |                                                                           |                                                                                                                                                                     |

| 2   | RFU               | NA            | NA                  |                                                                           |                                                                                                                                                                     |

| 1   | OPERATION_MODE[1] | NA            | NA                  | 00: HIZ Mode<br>01: not valid                                             | Current state machine status for overall system.                                                                                                                    |

| 0   | OPERATION_MODE[0] | NA            | NA                  | 10: Operation Mode<br>11: not valid                                       |                                                                                                                                                                     |

#### REG 0x03: General Status 2 (Read only) (VM)

| Bit | Name | Default Value | Reset by<br>REG_RST | Description | Comment |

|-----|------|---------------|---------------------|-------------|---------|

|-----|------|---------------|---------------------|-------------|---------|

| 7 | RFU            | NA | NA |                                                                    |                           |

|---|----------------|----|----|--------------------------------------------------------------------|---------------------------|

| 6 | THERMAL_ACTIVE | NA | NA | 0: Not in thermal<br>regulation<br>1: Thermal regulation<br>Active | Thermal Regulation Active |

| 5 | RFU            | NA | NA |                                                                    |                           |

| 4 | RFU            | NA | NA |                                                                    |                           |

| 3 | RFU            | NA | NA |                                                                    |                           |

| 2 | RFU            | NA | NA |                                                                    |                           |

| 1 | RFU            | NA | NA |                                                                    |                           |

| 0 | RFU            | NA | NA |                                                                    |                           |

### REG 0x04: RFU (Read Only) (VM)

# REG 0x05: Faults 1 (Read only) (VM)

| Bit | Name         | Default Value | Reset by<br>REG_RST | Description                             | Comment                                                                                                                                                                                                                                                                                                                                                                                    |

|-----|--------------|---------------|---------------------|-----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | nIRQ_Clear   | 0             | NA                  | 0: Normal Status<br>1: Clear IRQ output | Write this bit to 1 to clear the IRQ output. The bit will self-<br>clear to a 0 once the write occurs. If a fault still occurs,<br>then nIRQ pin may stay asserted low.<br>Register 0x02 Bit 6 provides a real time status of the<br>nIRQ output.                                                                                                                                          |

| 6   | RFU          | NA            | NA                  |                                         |                                                                                                                                                                                                                                                                                                                                                                                            |