Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

## Advanced Power Management Unit

### **FEATURES**

- Three Step-Down DC/DC Converters

- **Four Low-Dropout Linear Regulators**

- I<sup>2</sup>C<sup>™</sup> Serial Interface

- Advanced Enable/Disable Sequencing Controller

- **Minimal External Components**

- Tiny 4×4mm TQFN44-32 Package

- 0.75mm Package Height

- Pb-Free and RoHS Compliant

### GENERAL DESCRIPTION

The ACT8892 is a complete, cost effective, highlyefficient ActivePMU<sup>TM</sup> power management solution that is ideal for a wide range of high performance portable handheld applications such as tablet or pad devices.

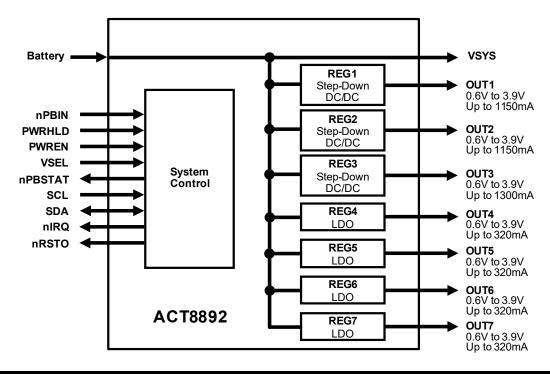

This device features three step-down DC/DC converters and four low-noise, low-dropout linear regulators.

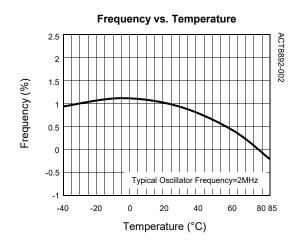

The three DC/DC converters utilize a highefficiency, fixed-frequency (2MHz), current-mode PWM control architecture that requires a minimum number of external components. Two DC/DCs are capable of supplying up to 1150mA of output current, while the third supports up to 1300mA. All four low-dropout linear regulators are highperformance, low-noise, regulators that supply up to 320mA.

The ACT8892 is available in a compact, Pb-Free and RoHS-compliant TQFN44-32 package.

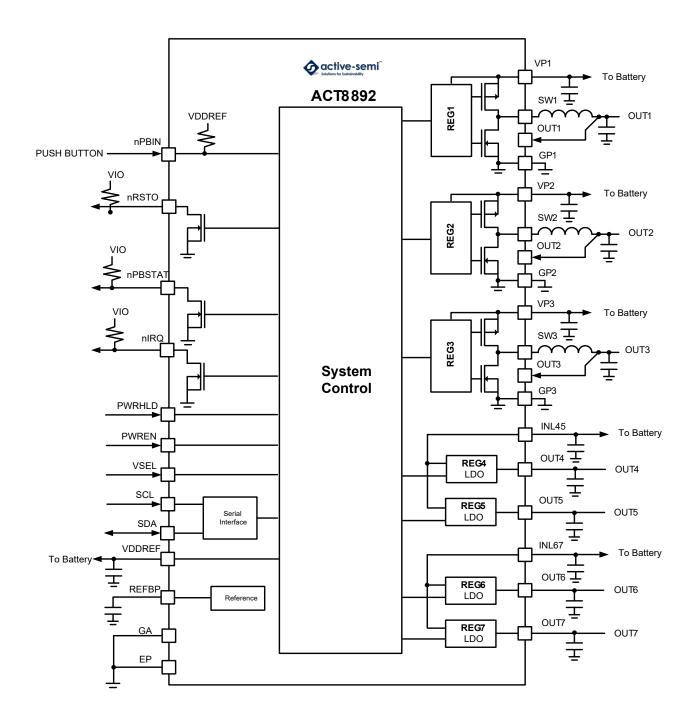

### TYPICAL APPLICATION DIAGRAM

## **TABLE OF CONTENTS**

| General Information                                   | p. 01 |

|-------------------------------------------------------|-------|

| Functional Block Diagram                              | p. 03 |

| Ordering Information                                  | p. 04 |

| Pin Configuration                                     | p. 04 |

| Pin Descriptions                                      | p. 05 |

| Absolute Maximum Ratings                              | p. 07 |

| 1 <sup>2</sup> C Interface Electrical Characteristics | p. 08 |

| Global Register Map                                   | p. 09 |

| Register and Bit Descriptions                         | p. 10 |

| System Control Electrical Characteristics             | р. 14 |

| Step-Down DC/DC Electrical Characteristics            |       |

| Low-Noise LDO Electrical Characteristics              |       |

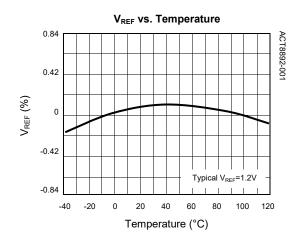

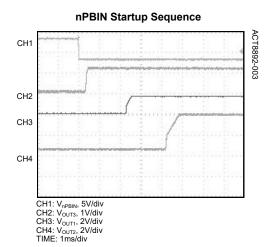

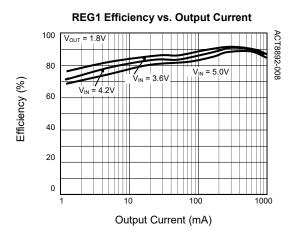

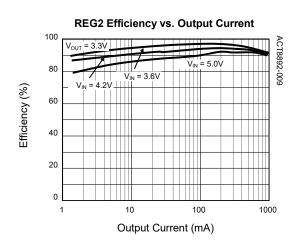

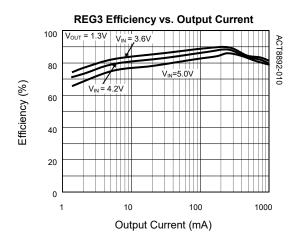

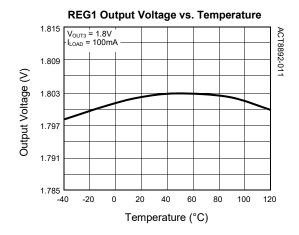

| Typical Performance Characteristics                   | p. 17 |

| System control information                            | ກ່ວວ  |

| Control Signals                                       |       |

| Push-Button Control                                   |       |

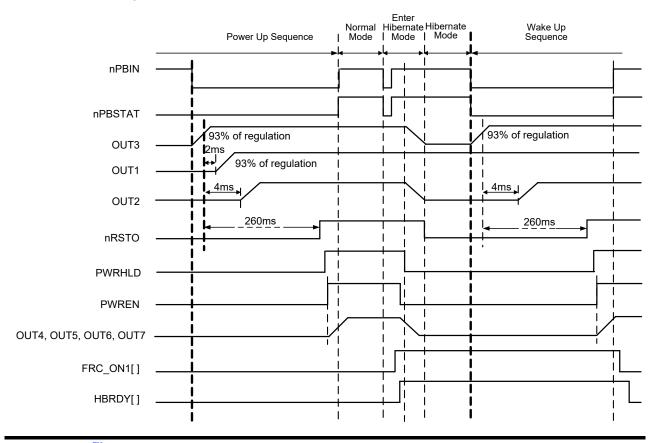

| Control Sequences                                     |       |

| ·                                                     | •     |

| Functional Description                                |       |

| Voltage Monitor and Interrupt                         |       |

| Thermal Shutdown                                      |       |

|                                                       | •     |

| Step-Down DC/DC Regulators                            |       |

| General Description                                   |       |

| 100% Duty Cycle OperationSynchronous Rectification    |       |

| Soft-Start                                            |       |

| Compensation                                          |       |

| Configuration Options                                 |       |

| OK[] and Output Fault Interrupt                       |       |

| PCB Layout Considerations                             |       |

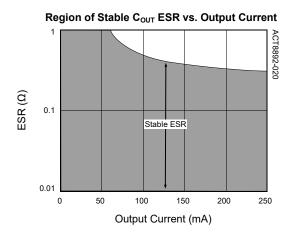

| Low-Noise, Low-Dropout Linear Regulators              | n 30  |

| General Description                                   |       |

| Output Current Limit                                  |       |

| Compensation                                          |       |

| Configuration Options                                 |       |

| OK[] and Output Fault Interrupt                       | р. 30 |

| PCB Layout Considerations                             | p. 31 |

| TOFN44-32 Package Outline and Dimensions              | n 32  |

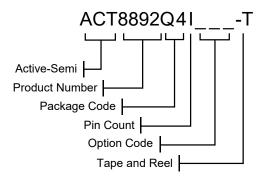

## ORDERING INFORMATION®

| PART NUMBER     | V <sub>OUT1</sub> /V <sub>STBY1</sub> | V <sub>OUT2</sub> /V <sub>STBY2</sub> | V <sub>OUT3</sub> /V <sub>STBY3</sub> | V <sub>OUT4</sub> | V <sub>OUT5</sub> | V <sub>OUT6</sub> | V <sub>OUT7</sub> | PACKAGE   | PINS | TEMPERATURE<br>RANGE |

|-----------------|---------------------------------------|---------------------------------------|---------------------------------------|-------------------|-------------------|-------------------|-------------------|-----------|------|----------------------|

| ACT8892Q4I134-T | 1.8V/1.6V                             | 3.0V/3.0V                             | 1.2V/0.95V                            | 2.8V              | 3.3V              | 3.0V              | 1.5V              | TQFN44-32 | 32   | -40°C to +85°C       |

| ACT8892Q4I185-T | 1.1V                                  | 2.5V                                  | 3.3V                                  | 1.5V              | 1.2V              | 1.8V              | 3.3V              | TQFN44-32 | 32   | -40°C to +85°C       |

- ①: All Active-Semi components are RoHS Compliant and with Pb-free plating unless specified differently. The term Pb-free means semiconductor products that are in compliance with current RoHS (Restriction of Hazardous Substances) standards.

- ②: Standard product options are identified in this table. Contact factory for custom options, minimum order quantity is 12,000 units.

- ③: To select  $V_{STBYX}$  as a output regulation voltage of REGx, drive VSEL to a logic high. The  $V_{STBYX}$  can be set by software via  $I^2C$  interface, refer to appropriate sections of this datasheet for  $V_{STBYX}$  setting.

**TOP VIEW**

## **PIN CONFIGURATION**

#### OUT1 OUT2 VDDREF GΑ SDA OUT4 OUT5 SCL active-semi<sup>®</sup> VSEL INL45 ACT8892 INL67 OUT3 OUT6 NC1 ΕP OUT7 **PWREN** nIRQ GP3

Thin - QFN (TQFN44-32)

## **FUNCTIONAL BLOCK DIAGRAM**

## **PIN DESCRIPTIONS**

| PIN | NAME    | DESCRIPTION                                                                                                                                                                                                                                                                                                       |

|-----|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | OUT1    | Output Feedback Sense for REG1. Connect this pin directly to the output node to connect the internal feedback network to the output voltage.                                                                                                                                                                      |

| 2   | GA      | Analog Ground. Connect GA directly to a quiet ground node. Connect GA, GP1,GP2 and GP3 together at a single point as close to the IC as possible.                                                                                                                                                                 |

| 3   | OUT4    | Output Voltage for REG4. Capable of delivering up to 320mA of output current. Connect a $3.3\mu F$ ceramic capacitor from OUT4 to GA. The output is discharged to GA with $1.5k\Omega$ resistor when disabled.                                                                                                    |

| 4   | OUT5    | Output Voltage for REG5. Capable of delivering up to 320mA of output current. Connect a $3.3\mu F$ ceramic capacitor from OUT5 to GA. The output is discharged to GA with $1.5k\Omega$ resistor when disabled.                                                                                                    |

| 5   | INL45   | Power Input for REG4 and REG5. Bypass to GA with a high quality ceramic capacitor placed as close to the IC as possible.                                                                                                                                                                                          |

| 6   | INL67   | Power Input for REG6 and REG7. Bypass to GA with a high quality ceramic capacitor placed as close to the IC as possible.                                                                                                                                                                                          |

| 7   | OUT6    | Output Voltage for REG6. Capable of delivering up to 320mA of output current. Connect a $3.3\mu F$ ceramic capacitor from OUT6 to GA. The output is discharged to GA with $1.5k\Omega$ resistor when disabled.                                                                                                    |

| 8   | OUT7    | Output Voltage for REG7. Capable of delivering up to 320mA of output current. Connect a $3.3\mu F$ ceramic capacitor from OUT7 to GA. The output is discharged to GA with $1.5k\Omega$ resistor when disabled.                                                                                                    |

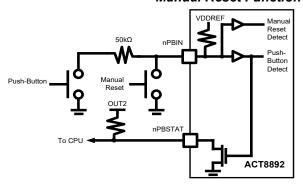

| 9   | nPBIN   | Master Enable Input. Drive nPBIN to GA through a $50k\Omega$ resistor to enable the IC, drive nPBIN directly to GA to assert a manual reset condition. Refer to the <i>nPBIN Multi-Function Input</i> section for more information. nPBIN is internally pulled up to $V_{VDDREF}$ through a $35k\Omega$ resistor. |

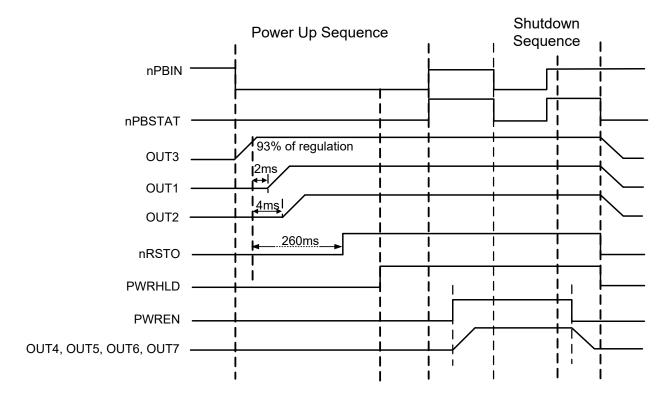

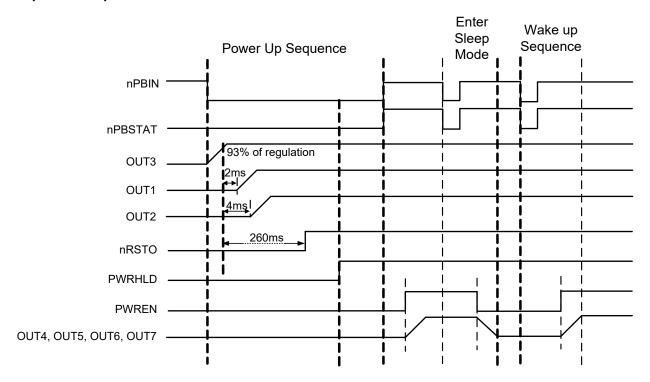

| 10  | PWRHLD  | Power Hold Input. Refer to the Control Sequences section for more information.                                                                                                                                                                                                                                    |

| 11  | nRSTO   | Active Low Reset Output. See the <i>nRSTO Output</i> section for more information.                                                                                                                                                                                                                                |

| 12  | nIRQ    | Open-Drain Interrupt Output. nIRQ asserts any time an unmasked fault condition exists or an interrupt occurs. See the <i>nIRQ Output</i> section for more information.                                                                                                                                            |

| 13  | nPBSTAT | Active-Low Open-Drain Push-Button Status Output. nPBSTAT is asserted low whenever the nPBIN is pushed, and is high-Z otherwise. See the <i>nPBSTAT Output</i> section for more information.                                                                                                                       |

| 14  | GP3     | Power Ground for REG3. Connect GA, GP1, GP2, and GP3 together at a single point as close to the IC as possible.                                                                                                                                                                                                   |

| 15  | SW3     | Switching Node Output for REG3. Connect this pin to the switching end of the inductor.                                                                                                                                                                                                                            |

| 16  | VP3     | Power Input for REG3. Bypass to GP3 with a high quality ceramic capacitor placed as close to the IC as possible.                                                                                                                                                                                                  |

| 17  | PWREN   | Power Enable Input. Refer to the Control Sequences section for more information.                                                                                                                                                                                                                                  |

| 18  | NC1     | Not Connected. Not internally connected.                                                                                                                                                                                                                                                                          |

| 19  | OUT3    | Output Feedback Sense for REG3. Connect this pin directly to the output node to connect the internal feedback network to the output voltage.                                                                                                                                                                      |

| 20  | VSEL    | Step-Down DC/DCs Output Voltage Selection. Drive to logic low to select default output voltage. Drive to logic high to select secondary output voltage. See the <i>Output Voltage Programming</i> section for more information.                                                                                   |

| 21  | SCL     | Clock Input for I <sup>2</sup> C Serial Interface.                                                                                                                                                                                                                                                                |

| 22  | SDA     | Data Input for I <sup>2</sup> C Serial Interface. Data is read on the rising edge of SCL.                                                                                                                                                                                                                         |

- 5 -

## PIN DESCRIPTIONS CONT'D

| PIN | NAME   | DESCRIPTION                                                                                                                                                                                                                     |

|-----|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 23  | VDDREF | Power supply for the internal reference. Connect this pin directly to the system power supply. Bypass VDDREF to GA with a 1µF capacitor placed as close to the IC as possible. Star connection with VP1, VP2 and VP3 preferred. |

| 24  | OUT2   | Output Feedback Sense for REG2. Connect this pin directly to the output node to connect the internal feedback network to the output voltage.                                                                                    |

| 25  | NC2    | Not Connected. Not internally connected.                                                                                                                                                                                        |

| 26  | VP2    | Power Input for REG2 and System Control. Bypass to GP2 with a high quality ceramic capacitor placed as close to the IC as possible.                                                                                             |

| 27  | SW2    | Switching Node Output for REG2. Connect this pin to the switching end of the inductor.                                                                                                                                          |

| 28  | GP2    | Power Ground for REG2. Connect GA, GP1,GP2 and GP3 together at a single point as close to the IC as possible.                                                                                                                   |

| 29  | GP1    | Power Ground for REG1. Connect GA, GP1,GP2 and GP3 together at a single point as close to the IC as possible.                                                                                                                   |

| 30  | SW1    | Switching Node Output for REG1. Connect this pin to the switching end of the inductor.                                                                                                                                          |

| 31  | VP1    | Power Input for REG1. Bypass to GP1 with a high quality ceramic capacitor placed as close to the IC as possible.                                                                                                                |

| 32  | REFBP  | Reference Bypass. Connect a 0.047μF ceramic capacitor from REFBP to GA. This pin is discharged to GA in shutdown.                                                                                                               |

| EP  | EP     | Exposed Pad. Must be soldered to ground on PCB.                                                                                                                                                                                 |

## **ABSOLUTE MAXIMUM RATINGS®**

| PARAMETER                                                 | VALUE                               | UNIT |

|-----------------------------------------------------------|-------------------------------------|------|

| VP1 to GP1, VP2 to GP2, VP3 to GP3                        | -0.3 to + 6                         | V    |

| INL, VDDREF to GA                                         | -0.3 to + 6                         | V    |

| nPBIN, SCL, SDA, REFBP, PWRHLD, PWREN, VSEL to GA         | -0.3 to (V <sub>VDDREF</sub> + 0.3) | V    |

| nRSTO, nIRQ, nPBSTAT to GA                                | -0.3 to + 6                         | V    |

| SW1, OUT1 to GP1                                          | -0.3 to (V <sub>VP1</sub> + 0.3)    | V    |

| SW2, OUT2 to GP2                                          | -0.3 to (V <sub>VP2</sub> + 0.3)    | V    |

| SW3, OUT3 to GP3                                          | -0.3 to (V <sub>VP3</sub> + 0.3)    | V    |

| OUT4, OUT5, OUT6, OUT7 to GA                              | -0.3 to (V <sub>INL</sub> + 0.3)    | V    |

| GP1, GP2, GP3 to GA                                       | -0.3 to + 0.3                       | V    |

| Junction to Ambient Thermal Resistance (θ <sub>JA</sub> ) | 27.5                                | °C/W |

| Operating Ambient Temperature                             | -40 to 85                           | °C   |

| Maximum Junction Temperature                              | 125                                 | °C   |

| Storage Temperature                                       | -65 to 150                          | °C   |

| Lead Temperature (Soldering, 10 sec)                      | 300                                 | °C   |

①: Do not exceed these limits to prevent damage to the device. Exposure to absolute maximum rating conditions for long periods may affect device reliability.

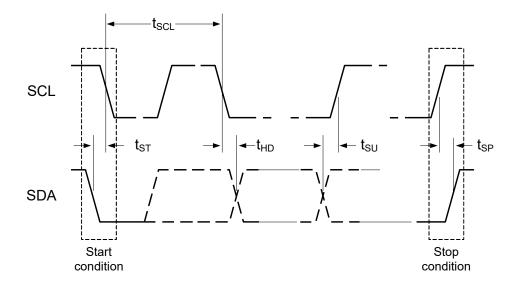

# I<sup>2</sup>C INTERFACE ELECTRICAL CHARACTERISTICS

( $V_{VP1}$  =  $V_{VP2}$  =  $V_{VP3}$  = 3.6V,  $T_A$  = 25°C, unless otherwise specified.)

| PARAMETER                            | TEST CONDITIONS                                    | MIN  | TYP | MAX  | UNIT |

|--------------------------------------|----------------------------------------------------|------|-----|------|------|

| SCL, SDA Input Low                   | $V_{VDDREF}$ = 3.1V to 5.5V, $T_A$ = -40°C to 85°C |      |     | 0.35 | V    |

| SCL, SDA Input High                  | $V_{VDDREF}$ = 3.1V to 5.5V, $T_A$ = -40°C to 85°C | 1.55 |     |      | V    |

| SDA Leakage Current                  |                                                    |      |     | 1    | μA   |

| SCL Leakage Current                  |                                                    |      | 1   | 2    | μA   |

| SDA Output Low                       | I <sub>OL</sub> = 5mA                              |      |     | 0.35 | V    |

| SCL Clock Period, t <sub>SCL</sub>   |                                                    | 1.5  |     |      | μs   |

| SDA Data Setup Time, t <sub>SU</sub> |                                                    | 100  |     |      | ns   |

| SDA Data Hold Time, t <sub>HD</sub>  |                                                    | 300  |     |      | ns   |

| Start Setup Time, t <sub>ST</sub>    | For Start Condition                                | 100  |     |      | ns   |

| Stop Setup Time, t <sub>SP</sub>     | For Stop Condition                                 | 100  |     |      | ns   |

Figure 1: I<sup>2</sup>C Compatible Serial Bus Timing

## **GLOBAL REGISTER MAP**

| CUITDUIT | 4000500                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                      | BITS     |          |            |          |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                     |           |  |  |  |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|----------|----------|------------|----------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|--|--|--|

| OUTPUT   | ADDRESS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                      | D7       | D6       | D5         | D4       | D3        | D2                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1 HBRDY 0 VSET1[1] 0 VSET2[1] 0 nFLTMSK 0 VSET2[1] 1 nFLTMSK 0 VSET1[1] 0 VSET2[1] 1 nFLTMSK 0 VSET1[1] 0 VSET[1] 1 nFLTMSK 0 VSET[1] 1 nFLTMSK 0 VSET[1] 0 nFLTMSK 0 VSET[1] 1 nFLTMSK 0 VSET[1] 0 nFLTMSK 0 VSET[1] 1 nFLTMSK                     | D0        |  |  |  |

| 0)/(0    | 000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | NAME                 | TRST     | nSYSMODE | nSYSLEVMSK | nSYSSTAT | SYSLEV[3] | SYSLEV[2]                                                                                                                                                                                                                                                                                                                                                                                                                                                             | SYSLEV[1]                                                                                                                                                                                                                                           | SYSLEV[0] |  |  |  |

| 515      | UXUU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | DEFAULT <sup>®</sup> | 0        | 1        | 0          | R        | 0         | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1                                                                                                                                                                                                                                                   | 1         |  |  |  |

| CVC      | YS 0x00 YS 0x01 EG1 0x20 EG1 0x21 EG1 0x22 EG2 0x30 EG2 0x31 EG2 0x32 EG3 0x40 EG3 0x41 EG3 0x42 EG4 0x50 EG4 0x51 EG5 0x54 EG5 0x60 EG6 0x61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | NAME                 | Reserved | FRC_ON1  | Reserved   | Reserved | SCRATCH   | SCRATCH                                                                                                                                                                                                                                                                                                                                                                                                                                                               | HBRDY                                                                                                                                                                                                                                               | SCRATCH   |  |  |  |

| 515      | UXUT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | DEFAULT <sup>®</sup> | 0        | 0        | 0          | 0        | 0         | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0                                                                                                                                                                                                                                                   | 0         |  |  |  |

| DEC1     | YS 0x00 YS 0x01 EG1 0x20 EG1 0x21 EG2 0x30 EG2 0x31 EG2 0x32 EG3 0x40 EG3 0x41 EG3 0x42 EG4 0x50 EG4 0x51 EG5 0x54 EG5 0x60 EG6 0x60 EG6 0x61 EG7 0x64                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | NAME                 | Reserved | Reserved | VSET1[5]   | VSET1[4] | VSET1[3]  | VSET1[2]                                                                                                                                                                                                                                                                                                                                                                                                                                                              | VSET1[1]                                                                                                                                                                                                                                            | VSET1[0]  |  |  |  |

| REGI     | UXZU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | DEFAULT <sup>®</sup> | 0        | 0        | 1          | 0        | 0         | SYSLEV[2] SYSL  1 SCRATCH HBF 0 VSET1[2] VSE 1 VSET2[2] VSE 0 DELAY[0] nFLT 1 VSET2[2] VSE 1 VSET2[2] VSE 1 VSET2[2] VSE 1 VSET2[2] VSE 1 DELAY[0] nFLT 0 VSET1[2] VSE 1 DELAY[0] nFLT 0 VSET2[2] VSE 1 DELAY[0] nFLT 0 VSET[2] VSE 1 DELAY[0] nFLT | 0                                                                                                                                                                                                                                                   | 0         |  |  |  |

| DEC1     | /S     0x00       /S     0x01       G1     0x20       G1     0x21       G1     0x22       G2     0x30       G2     0x31       G2     0x32       G3     0x40       G3     0x41       G3     0x42       G4     0x50       G4     0x54       G5     0x54       G5     0x60       G6     0x61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | NAME                 | Reserved | Reserved | VSET2[5]   | VSET2[4] | VSET2[3]  | VSET2[2]                                                                                                                                                                                                                                                                                                                                                                                                                                                              | VSET2[1]                                                                                                                                                                                                                                            | VSET2[0]  |  |  |  |

| KEGI     | UXZI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | DEFAULT <sup>®</sup> | 0        | 0        | 1          | 0        | 0         | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0                                                                                                                                                                                                                                                   | 0         |  |  |  |

| DEC1     | 61 0x22<br>62 0x30<br>62 0x31<br>62 0x32<br>63 0x40<br>63 0x41<br>63 0x42                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | NAME                 | ON       | PHASE    | MODE       | DELAY[2] | DELAY[1]  | DELAY[0]                                                                                                                                                                                                                                                                                                                                                                                                                                                              | nFLTMSK                                                                                                                                                                                                                                             | OK        |  |  |  |

| KEGT     | UXZZ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | DEFAULT <sup>®</sup> | 0        | 0        | 0          | 0        | 0         | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0                                                                                                                                                                                                                                                   | R         |  |  |  |

| DEC2     | YS         0x01           EG1         0x20           EG1         0x21           EG1         0x22           EG2         0x30           EG2         0x31           EG2         0x32           EG3         0x40           EG3         0x41           EG3         0x42           EG4         0x50           EG4         0x51           EG5         0x55           EG6         0x60           EG6         0x61           EG7         0x64                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | NAME                 | Reserved | Reserved | VSET1[5]   | VSET1[4] | VSET1[3]  | VSET1[2]                                                                                                                                                                                                                                                                                                                                                                                                                                                              | VSET1[1]                                                                                                                                                                                                                                            | VSET1[0]  |  |  |  |

| INLUZ    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | DEFAULT <sup>®</sup> | 0        | 0        | 1          | 1        | 0         | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1                                                                                                                                                                                                                                                   | 0         |  |  |  |

| REG2     | 0v31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | NAME                 | Reserved | Reserved | VSET2[5]   | VSET2[4] | VSET2[3]  | VSET2[2]                                                                                                                                                                                                                                                                                                                                                                                                                                                              | VSET2[1]                                                                                                                                                                                                                                            | VSET2[0]  |  |  |  |

| INLOZ    | 0,01                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | DEFAULT <sup>®</sup> | 0        | 0        | 1          | 1        | 0         | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1                                                                                                                                                                                                                                                   | 0         |  |  |  |

| REG2     | 0v32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | NAME                 | ON       | PHASE    | MODE       | DELAY[2] | DELAY[1]  | DELAY[0]                                                                                                                                                                                                                                                                                                                                                                                                                                                              | nFLTMSK                                                                                                                                                                                                                                             | OK        |  |  |  |

| INLOZ    | 0,02                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | DEFAULT <sup>®</sup> | 0        | 0        | 0          | 0        | 1         | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0                                                                                                                                                                                                                                                   | R         |  |  |  |

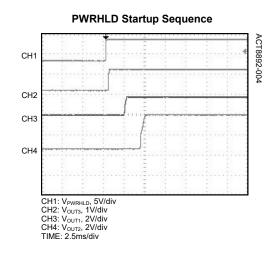

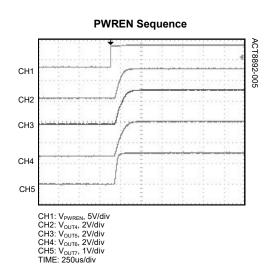

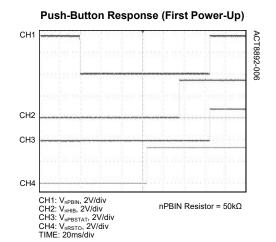

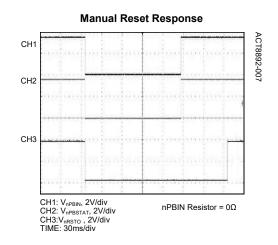

| REG3     | 0v40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | NAME                 | Reserved | Reserved | VSET1[5]   | VSET1[4] | VSET1[3]  | VSET1[2]                                                                                                                                                                                                                                                                                                                                                                                                                                                              | VSET1[1]                                                                                                                                                                                                                                            | VSET1[0]  |  |  |  |