Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# **Linear Output Magnetic Field Sensor**

AD22151

#### **FEATURES**

Adjustable Offset to Unipolar or Bipolar Operation Low Offset Drift over Temperature Range Gain Adjustable over Wide Range Low Gain Drift over Temperature Range **Adjustable First Order Temperature Compensation** Ratiometric to V<sub>cc</sub>

**APPLICATIONS Automotive Throttle Position Sensing Pedal Position Sensing Suspension Position Sensing** Valve Position Sensing Industrial **Absolute Position Sensing Proximity Sensing**

## GENERAL DESCRIPTION

The AD22151 is a linear magnetic field transducer. The sensor output is a voltage proportional to a magnetic field applied perpendicularly to the package top surface.

The sensor combines integrated bulk Hall cell technology and instrumentation circuitry to minimize temperature related drifts associated with silicon Hall cell characteristics. The architecture maximizes the advantages of a monolithic implementation while allowing sufficient versatility to meet varied application requirements with a minimum number of components.

Principal features include dynamic offset drift cancellation and a built-in temperature sensor. Designed for single 5 V supply operation, the AD22151 achieves low drift offset and gain operation over -40°C to +150°C. Temperature compensation can accommodate a number of magnetic materials commonly utilized in economic position sensor assemblies.

The transducer can be configured for specific signal gains to meet various application requirements. Output voltage can be adjusted from fully bipolar (reversible) field operation to fully unipolar field sensing.

The voltage output achieves near rail-to-rail dynamic range, capable of supplying 1 mA into large capacitive loads. The signal is ratiometric to the positive supply rail in all configurations.

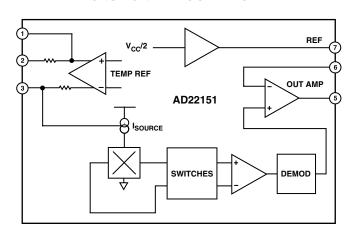

#### FUNCTIONAL BLOCK DIAGRAM

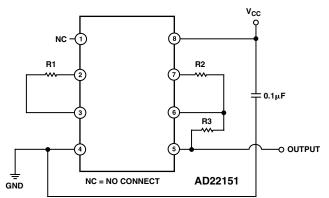

Figure 1. Typical Bipolar Configuration with Low (< -500 ppm) Compensation

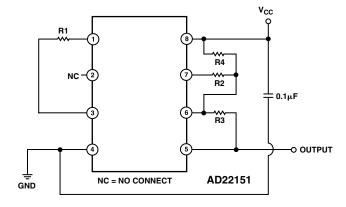

Figure 2. Typical Unipolar Configuration with High (≈ –2000 ppm) Compensation

## REV. A

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective companies.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781/329-4700 www.analog.com Fax: 781/326-8703

© 2003 Analog Devices, Inc. All rights reserved.

## AD22151—SPECIFICATIONS ( $T_A = 25^{\circ}C$ and $V_+ = 5$ V, unless otherwise noted.)

| Parameter                                    | Min | Тур                        | Max  | Unit                 |

|----------------------------------------------|-----|----------------------------|------|----------------------|

| OPERATION                                    |     |                            |      |                      |

| V <sub>CC</sub> Operating                    | 4.5 | 5.0                        | 6.0  | V                    |

| I <sub>CC</sub> Operating                    |     | 6.0                        | 10   | mA                   |

| INPUT                                        |     |                            |      |                      |

| TC3 (Pin 3) Sensitivity/Volt                 |     | 160                        |      | μV/G/V               |

| Input Range <sup>1</sup>                     |     | $\frac{V_{CC}}{2} \pm 0.5$ |      | V                    |

| OUTPUT <sup>2</sup>                          |     |                            |      |                      |

| Sensitivity (External Adjustment, Gain = +1) |     | 0.4                        |      | mV/G                 |

| Linear Output Range                          | 10  |                            | 90   | % of V <sub>CC</sub> |

| Output Min                                   |     | 5.0                        |      | % of V <sub>CC</sub> |

| Output Max (Clamp)                           |     | 93                         |      | % of V <sub>CC</sub> |

| Drive Capability                             |     | 1.0                        |      | mA                   |

| Offset @ 0 Gauss                             |     | $rac{V_{CC}}{2}$          |      | V                    |

| Offset Adjust Range                          | 5.0 |                            | 95   | % of V <sub>CC</sub> |

| Output Short Circuit Current                 |     | 5.0                        |      | mA                   |

| ACCURACIES                                   |     |                            |      |                      |

| Nonlinearity (10% to 90% Range)              |     | 0.1                        |      | % FS                 |

| Gain Error (Over Temperature Range)          |     | ±1                         |      | %                    |

| Offset Error (Over Temperature Range)        |     | $\pm 6.0$                  |      | G                    |

| Uncompensated Gain TC (G <sub>TCU</sub> )    |     | 950                        |      | ppm                  |

| RATIOMETRICITY ERROR                         |     |                            | 1.0  | %V/V <sub>CC</sub>   |

| 3 dB ROLL-OFF (5 mV/G)                       |     | 5.7                        |      | kHz                  |

| OUTPUT NOISE FIGURE (6 kHz BW)               |     | 2.4                        |      | mV/rms               |

| PACKAGE                                      |     | 8-Lead SOIC                |      |                      |

| OPERATING TEMPERATURE RANGE                  | -40 |                            | +150 | °C                   |

NOTES

$^{1}$ –40°C to +150°C.

$^2$ R<sub>L</sub> = 4.7 k $\Omega$ .

Specifications subject to change without notice.

## **ABSOLUTE MAXIMUM RATINGS\***

| Supply Voltage                        | . 12 V |

|---------------------------------------|--------|

| Package Power Dissipation2            | 5 mW   |

| Storage Temperature50°C to +1         | 160°C  |

| Output Sink Current, I <sub>O</sub> 1 | 5 mA   |

| Magnetic Flux Density Unli            | mited  |

| Lead Temperature (Soldering 10 sec)   | 300°C  |

<sup>\*</sup>Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to the absolute maximum rating conditions for extended periods may affect device reliability.

## ORDERING GUIDE

|                |                 | Package<br>Description | Package<br>Option |

|----------------|-----------------|------------------------|-------------------|

| AD22151YR      | -40°C to +150°C | 8-Lead SOIC            | R-8               |

| AD22151YR-REEL | -40°C to +150°C | 8-Lead SOIC            | R-8               |

## **CAUTION**

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although the AD22151 features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

-2- REV. A

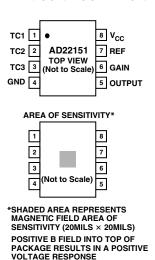

## PIN CONFIGURATION

## PIN FUNCTION DESCRIPTIONS

| Pin No. | Description                | Connection   |

|---------|----------------------------|--------------|

| 1       | Temperature Compensation 1 | Output       |

| 2       | Temperature Compensation 2 | Output       |

| 3       | Temperature Compensation 3 | Input/Output |

| 4       | Ground                     |              |

| 5       | Output                     | Output       |

| 6       | Gain                       | Input        |

| 7       | Reference                  | Output       |

| 8       | Positive Power Supply      |              |

## CIRCUIT OPERATION

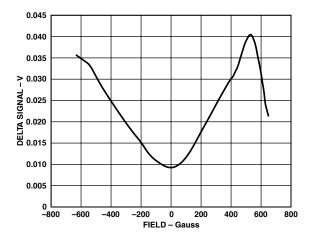

The AD22151 consists of epi Hall plate structures located at the center of the die. The Hall plates are orthogonally sampled by commutation switches via a differential amplifier. The two amplified Hall signals are synchronously demodulated to provide a resultant offset cancellation (see Figure 3). The demodulated signal passes through a noninverting amplifier to provide final gain and drive capability. The frequency at which the output signal is refreshed is 50 kHz.

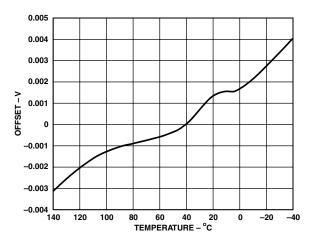

Figure 3. Relative Quiescent Offset vs. Temperature

## **TEMPERATURE DEPENDENCIES**

The uncompensated gain temperature coefficient ( $G_{TCU}$ ) of the AD22151 is the result of fundamental physical properties associated with silicon bulk Hall plate structures. Low doped Hall plates operated in current bias mode exhibit a temperature relationship determined by the action of scattering mechanisms and doping concentration.

The relative value of sensitivity to magnetic field can be altered by the application of mechanical force upon silicon. The mechanism is principally the redistribution of electrons throughout the "valleys" of the silicon crystal. Mechanical force on the sensor is attributable to package-induced stress. The package material acts to distort the encapsulated silicon, altering the Hall cell gain by  $\pm 2\%$  and  $G_{TCU}$  by  $\pm 200$  ppm.

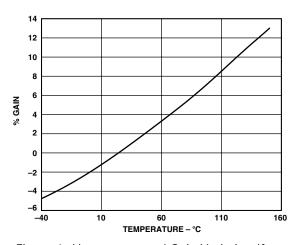

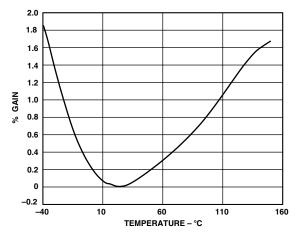

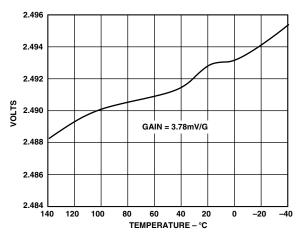

Figure 4 shows the typical  $G_{TCU}$  characteristic of the AD22151. This is the observable alteration of gain with respect to temperature with Pin 3 (TC3) held at a constant 2.5 V (uncompensated).

If a permanent magnet source used in conjunction with the sensor also displays an intrinsic TC ( $B_{TC}$ ), it will require factoring into the total temperature compensation of the sensor assembly.

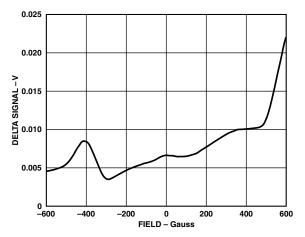

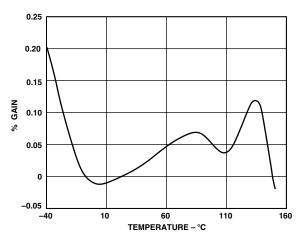

Figures 5 and 6 represent typical overall temperature/gain performance for a sensor and field combination ( $B_{TC} = -200$  ppm). Figure 5 is the total drift in volts over a  $-40^{\circ}$ C to  $+150^{\circ}$ C temperature range with respect to applied field. Figure 6 represents typical percentage gain variation from 25°C. Figures 7 and 8 show similar data for a  $B_{TC} = -2000$  ppm.

Figure 4. Uncompensated Gain Variation (from 25°C) vs. Temperature

REV. A -3-

Figure 5. Signal Drift over Temperature (-40°C to +150°C) vs. Field (-200 ppm); 5 V Supply

Figure 6. Gain Variation from 25°C vs. Temperature (–200 ppm) Field; R1 –15  $k\Omega$

Figure 7. Signal Drift over Temperature (–40°C to +150°C) vs. Field (–2000 ppm); 5 V Supply

Figure 8. Gain Variation (from 25°C) vs. Temperature (-2000 ppm Field; R1 = 12 k $\Omega$ )

## TEMPERATURE COMPENSATION

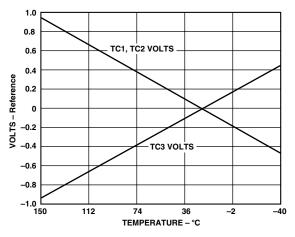

The AD22151 incorporates a "thermistor" transducer that detects relative chip temperature within the package. This function provides a compensation mechanism for the various temperature dependencies of the Hall cell and magnet combinations. The temperature information is accessible at Pins 1 and 2 ( $\approx$  +2900 ppm/°C) and Pin 3 ( $\approx$  -2900 ppm/°C), as represented by Figure 9. The compensation voltages are trimmed to converge at  $V_{\rm CC}/2$  at 25°C. Pin 3 is internally connected to the negative TC voltage via an internal resistor (see the Functional Block Diagram). An external resistor connected between Pin 3 and Pins 1 or 2 will produce a potential division of the two complementary TC voltages to provide optimal compensation. The Pin 3 internal resistor provides a secondary TC designed to reduce second order Hall cell temperature sensitivity.

Figure 9. TC1, TC2, and TC3 with Respect to Reference vs. Temperature

The voltages present at Pins 1, 2, and 3 are proportional to the supply voltage. The presence of the Pin 2 internal resistor distinguishes the effective compensation ranges of Pins 1 and 2. (See temperature configuration in Figures 1 and 2, and typical resistor values in Figures 10 and 11.)

Variation occurs in the operation of the gain temperature compensation for two reasons. First, the die temperature within the package is somewhat higher than the ambient temperature due

-4- REV. A

to self-heating as a function of power dissipation. Second, package stress effect alters the specific operating parameters of the gain compensation, particularly the specific crossover temperature of TC1, TC3 ( $\approx \pm 10$ °C).

## CONFIGURATION AND COMPONENT SELECTION

There are three areas of sensor operation that require external component selection: temperature compensation (R1), signal gain (R2 and R3), and offset (R4).

## **Temperature**

If the internal gain compensation is used, an external resistor is required to complete the gain TC circuit at Pin 3. A number of factors contribute to the value of this resistor:

- a. The intrinsic Hall cell sensitivity  $TC \approx 950$  ppm.

- b. Package induced stress variation in a.  $\approx \pm 150$  ppm.

- c. Specific field TC ≈ -200 ppm (Alnico), -2000 ppm (Ferrite), 0 ppm (electromagnet), and so on.

- d. R1, TC.

The final value of target compensation also dictates the use of either Pin 1 or Pin 2. Pin 1 is provided to allow for large negative field TC devices such as ferrite magnets; thus, R1 would be connected to Pins 1 and 3.

Pin 2 uses an internal resistive TC to optimize smaller field coefficients such as Alnico down to 0 ppm coefficients when only the sensor gain TC itself is dominant. Because the TC of R1 itself will also affect the compensation, a low TC resistor (±50 ppm) is recommended.

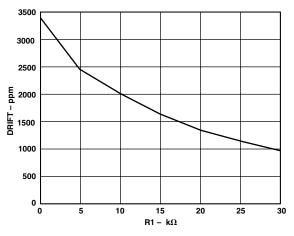

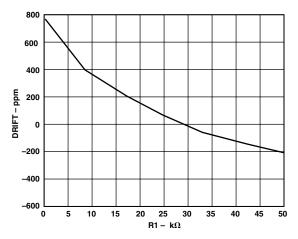

Figures 10 and 11 indicate R1 resistor values and their associated effectiveness for Pins 1 and 2, respectively. Note that the indicated drift response in both cases incorporates the intrinsic Hall sensitivity TC ( $B_{TCU}$ ).

For example, the AD22151 sensor is to be used in conjunction with an Alnico material permanent magnet. The TC of such magnets is  $\approx$  –200 ppm (see Figures 5 and 6). Figure 11 indicates that a compensating drift of 200 ppm at Pin 3 requires a nominal value of R1 = 18 k $\Omega$  (assuming negligible drift of R1 itself).

Figure 10. Drift Compensation (Pins 1 and 3) vs. Typical Resistor Value R1

Figure 11. Drift Compensation (Pins 2 and 3) vs. Typical Resistor Value R1

## **GAIN AND OFFSET**

The operation of the AD22151 can be bipolar (i.e., 0 Gauss =  $V_{\rm CC}/2$ ), or a ratiometric offset can be implemented to position Zero Gauss point at some other potential (i.e., 0.25 V).

The gain of the sensor can be set by the appropriate R2 and R3 resistor values (see Figure 1) such that:

$$Gain = 1 + \frac{R3}{R2} \times 0.4 \ mV / G$$

(1)

However, if an offset is required to position the quiescent output at some other voltage, the gain relationship is modified to:

$$Gain = 1 + \frac{R3}{(R2||R4)} \times 0.4 \ mV / G$$

(2)

The offset that R4 introduces is:

$$Offset = 1 + \frac{R3}{(R2 + R4)} \times (V_{CC} - V_{OUT})$$

(3)

For example, at  $V_{\rm CC}$  = 5 V at room temperature, the internal gain of the sensor is approximately 0.4 mV/Gauss. If a sensitivity of 6 mV/Gauss is required with a quiescent output voltage of 1 V, the calculations below apply (see Figure 2).

A value would be selected for R3 that complied with the various considerations of current and power dissipation, trim ranges (if applicable), and so on. For the purpose of example, assume a value of 85 k $\Omega$ .

To achieve a quiescent offset of 1 V requires a value for R4 as:

$$\frac{\left(\frac{V_{CC}}{2}\right) - 1}{V_{CC}} = 0.375\tag{4}$$

Thue

$$R4 = \left(\frac{85 \, k\Omega}{0.375}\right) - 85 \, k\Omega = 141.666 \, k\Omega \tag{5}$$

The gain required would be 6/0.4 (mV/Gauss) = 15.

REV. A \_5-

Knowing the values of R3 and R4 and noting Equation 2, the parallel combination of R2 and R4 required is:

$$\frac{85 \, k\Omega}{\left(15 - 1\right)} = 6.071 \, k\Omega$$

Thus:

$$R2 = \left(\frac{1}{\left(\frac{1}{6.071 \, k\Omega}\right) - \left(\frac{1}{141.666 \, k\Omega}\right)}\right) = 6.342 \, k\Omega$$

#### **NOISE**

The principal noise component in the sensor is thermal noise from the Hall cell. Clock feedthrough into the output signal is largely suppressed with application of a supply bypass capacitor.

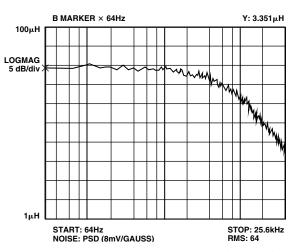

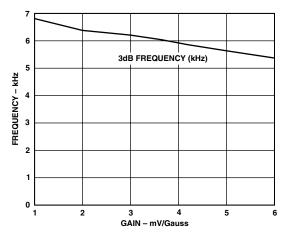

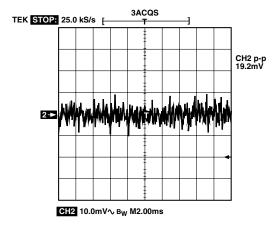

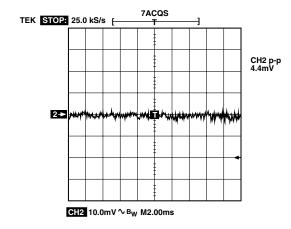

Figure 12 shows the power spectral density (PSD) of the output signal for a gain of 5 mV/Gauss. The effective bandwidth of the sensor is approximately 5.7 kHz, as shown in Figure 13. The PSD indicates an rms noise voltage of 2.8 mV within the 3 dB bandwidth of the sensor. A wideband measurement of 250 MHz indicates 3.2 mV rms (see Figure 14a).

In many position sensing applications, bandwidth requirements can be as low as 100 Hz. Passing the output signal through a 100 Hz LP filter, for example, would reduce the rms noise voltage to  $\approx\!1$  mV. A dominant pole may be introduced into the output amplifier response by connection of a capacitor across feedback resistor R3 as a simple means of reducing noise at the expense of bandwidth. Figure 14b indicates the output signal of a 5 mV/G sensor bandwidth limited to 180 Hz with a 0.01  $\mu F$  feedback capacitor.

Note: Measurements were taken with a 0.1  $\mu F$  decoupling capacitor between  $V_{CC}$  and GND at 25°C.

Figure 12. Power Spectral Density (5 mV/G)

Figure 13. Small Signal Gain Bandwidth vs. Gain

Figure 14a. Peak-to-Peak Full Bandwidth (10 mV/Division)

Figure 14b. Peak-to-Peak 180 Hz Bandwidth (10 mV/Division)

–6– REV. A

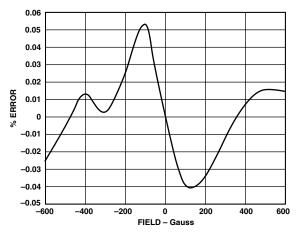

Figure 15. Integral Nonlinearity vs. Field

Figure 16. Absolute Offset Volts vs. Temperature

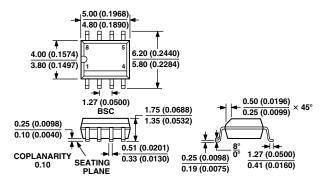

## **OUTLINE DIMENSIONS**

## 8-Lead Standard Small Outline Package [SOIC] Narrow Body

(R-8)

Dimensions shown in millimeters and (inches)

COMPLIANT TO JEDEC STANDARDS MS-012AA

CONTROLLING DIMENSIONS ARE IN MILLIMETERS; INCH DIMENSIONS

(IN PARENTHESES) ARE ROUNDED-OFF MILLIMETER EQUIVALENTS FOR

REFERENCE ONLY AND ARE NOT APPROPRIATE FOR USE IN DESIGN

REV. A -7-

# C00675-0-2/03(A)

# PRINTED IN U.S.A.

# AD22151

# **Revision History**

| Location                                       | Page |

|------------------------------------------------|------|

| 2/03—Data Sheet changed from REV. 0 to REV. A. |      |

| Change to ORDERING GUIDE                       | 2    |

| Updated OUTLINE DIMENSIONS                     | 7    |

-8- REV. A