# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

### Quad-Channel, 12-Bit, Serial Input, 4 mA to 20 mA Output DAC with Dynamic Power Control and HART Connectivity

### **Data Sheet**

# AD5737

### FEATURES

12-bit resolution and monotonicity Dynamic power control for thermal management or external PMOS mode Current output ranges: 0 mA to 20 mA, 4 mA to 20 mA, and 0 mA to 24 mA ±0.1% total unadjusted error (TUE) maximum User-programmable offset and gain On-chip diagnostics On-chip reference: ±10 ppm/°C maximum -40°C to +105°C temperature range

### **APPLICATIONS**

Process control Actuator control PLCs HART network connectivity

### **GENERAL DESCRIPTION**

The AD5737 is a quad-channel current output DAC that operates with a power supply range from 10.8 V to 33 V. On-chip dynamic power control minimizes package power dissipation by regulating the voltage on the output driver from 7.4 V to 29.5 V using a dc-to-dc boost converter optimized for minimum on-chip power dissipation. Each channel has a corresponding CHART pin so that HART signals can be coupled onto the current output of the AD5737.

The AD5737 uses a versatile 3-wire serial interface that operates at clock rates of up to 30 MHz and is compatible with standard SPI, QSPI<sup>∞</sup>, MICROWIRE<sup>\*</sup>, DSP, and microcontroller interface standards. The serial interface also features optional CRC-8 packet error checking, as well as a watchdog timer that monitors activity on the interface.

### **PRODUCT HIGHLIGHTS**

- 1. Dynamic power control for thermal management.

- 2. 12-bit performance.

- 3. Quad channel.

- 4. HART compliant.

### **COMPANION PRODUCTS**

Product Family: AD5755, AD5755-1, AD5757, AD5735 HART Modem: AD5700, AD5700-1 External References: ADR445, ADR02 Digital Isolators: ADuM1410, ADuM1411 Power: ADP2302, ADP2303 Additional companion products on the AD5737 product page

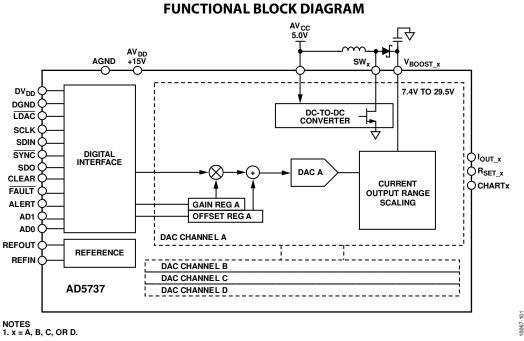

Figure 1.

Rev. E Document Feedback Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781.329.4700 ©2011–2014 Analog Devices, Inc. All rights reserved. Technical Support www.analog.com

# **AD5737\* PRODUCT PAGE QUICK LINKS**

Last Content Update: 02/23/2017

### COMPARABLE PARTS

View a parametric search of comparable parts.

### EVALUATION KITS

• AD5757 Evaluation Board

### DOCUMENTATION

### **Application Notes**

AN-1289: Using the AD5755 and Similar Dynamic Power Control DACs in Applications Without Dynamic Power Control

### **Data Sheet**

AD5737: Quad-Channel, 12-Bit, Serial Input, 4 mA to 20 mA Output DAC with Dynamic Power Control and HART Connectivity Datasheet

### SOFTWARE AND SYSTEMS REQUIREMENTS

AD5755 IIO Multi-Channel DAC Linux Driver

### REFERENCE MATERIALS

### **Solutions Bulletins & Brochures**

Digital to Analog Converters ICs Solutions Bulletin

### DESIGN RESOURCES

- AD5737 Material Declaration

- PCN-PDN Information

- Quality And Reliability

- Symbols and Footprints

### DISCUSSIONS

View all AD5737 EngineerZone Discussions.

### SAMPLE AND BUY

Visit the product page to see pricing options.

### TECHNICAL SUPPORT

Submit a technical question or find your regional support number.

### DOCUMENT FEEDBACK

Submit feedback for this data sheet.

# TABLE OF CONTENTS

| Features                                      |

|-----------------------------------------------|

| Applications                                  |

| General Description                           |

| Product Highlights 1                          |

| Companion Products 1                          |

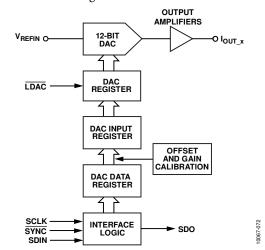

| Functional Block Diagram 1                    |

| Revision History                              |

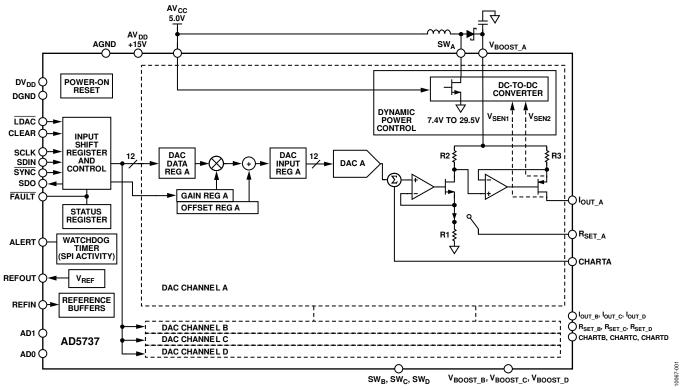

| Detailed Functional Block Diagram             |

| Specifications                                |

| AC Performance Characteristics7               |

| Timing Characteristics7                       |

| Absolute Maximum Ratings                      |

| Thermal Resistance                            |

| ESD Caution10                                 |

| Pin Configuration and Function Descriptions11 |

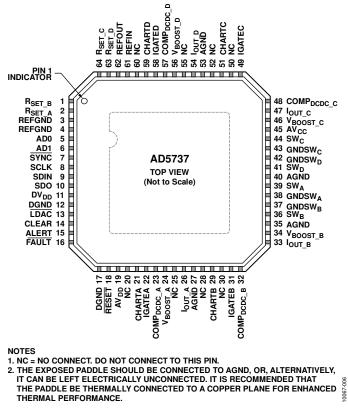

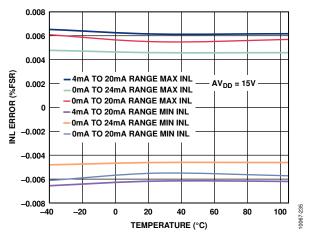

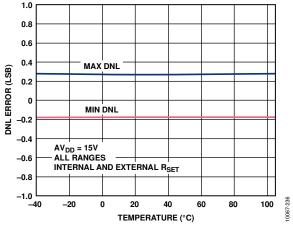

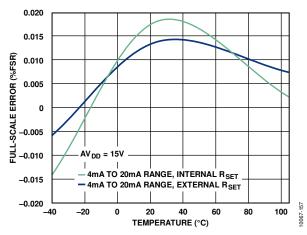

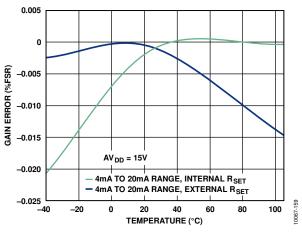

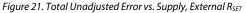

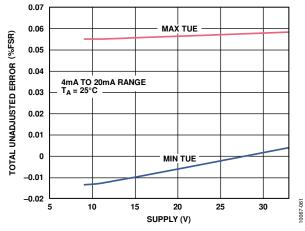

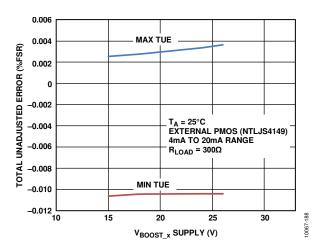

| Typical Performance Characteristics           |

| Current Outputs14                             |

| DC-to-DC Converter                            |

| Reference                                     |

| General                                       |

| Terminology                                   |

| Theory of Operation                           |

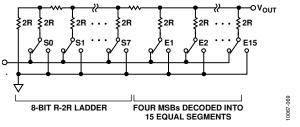

| DAC Architecture                              |

| Power-On State of the AD5737                  |

| Serial Interface                              |

| Transfer Function                             |

| Registers                                     |

| Enabling the Output                           |

| Reprogramming the Output Range                |

| Data Registers                                |

| Control Registers                             |

| -                                             |

|   | Readback Operation                                 | 31 |

|---|----------------------------------------------------|----|

| D | evice Features                                     | 34 |

|   | Fault Output                                       | 34 |

|   | Digital Offset and Gain Control                    | 34 |

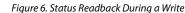

|   | Status Readback During a Write                     | 34 |

|   | Asynchronous Clear                                 | 34 |

|   | Packet Error Checking                              | 35 |

|   | Watchdog Timer                                     | 35 |

|   | Alert Output                                       | 35 |

|   | Internal Reference                                 | 35 |

|   | External Current Setting Resistor                  | 35 |

|   | HART Connectivity                                  | 36 |

|   | Digital Slew Rate Control                          | 36 |

|   | Dynamic Power Control                              | 37 |

|   | DC-to-DC Converters                                | 37 |

|   | AI <sub>CC</sub> Supply Requirements—Static        | 38 |

|   | AICC Supply Requirements—Slewing                   | 39 |

|   | External PMOS Mode                                 | 40 |

| A | pplications Information                            | 41 |

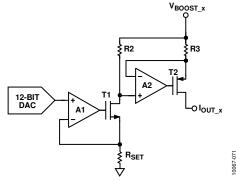

|   | Current Output Mode with Internal R <sub>SET</sub> | 41 |

|   | Precision Voltage Reference Selection              | 41 |

|   | Driving Inductive Loads                            | 41 |

|   | Transient Voltage Protection                       | 42 |

|   | Microprocessor Interfacing                         | 42 |

|   | Layout Guidelines                                  | 42 |

|   | Galvanically Isolated Interface                    | 43 |

|   | Industrial HART Capable Analog Output Application  | 44 |

| 0 | utline Dimensions                                  | 45 |

|   | Ordering Guide                                     | 45 |

|   |                                                    |    |

### **REVISION HISTORY**

### 9/14—Rev. D to Rev. E

| Changes to Table 37                                             |

|-----------------------------------------------------------------|

| Changes to Software Register and Status Register                |

| Descriptions                                                    |

| Changes to Software Register Section, Table 24, and Table 25 30 |

| Changes to Status Register Section and Table 34                 |

| Changes to Packet Error Checking Section35                      |

### 6/14—Rev. C to Rev. D

| Change to Thermal Hysteresis Parameter, Table 16               |

|----------------------------------------------------------------|

| Changes to Table 37                                            |

| Changes to Figure 5 and Added Figure 6; Renumbered             |

| Sequentially9                                                  |

| Changes to Table 510                                           |

| Changes to Figure 33, Figure 34, Figure 35, and Figure 3618    |

| Changes to Terminology Section                                 |

| Changes to Table 8 and Table 924                               |

| Changes to Software Register Section, Table 24, and Table 2530 |

| Changes to Readback Operation Section and Table 34, Added      |

| Table 30 and Table 31; Renumbered Sequentially                 |

| Changes to Status Readback During a Write Section              |

| Changes to Packet Error Checking Section                       |

| Changes to Table 36                                            |

| Changes to Figure 62                                           |

|                                                                |

### 11/12—Rev. B to Rev. C

| Changed Thermal Impedance from 20°C/W to 28°C/W         | 10 |

|---------------------------------------------------------|----|

| Changes to Pin 6 Description                            | 11 |

| Changes to DUT_AD1, DUT_AD0 Description, Table 11       | 26 |

| Changes to Changes to Packet Error Checking Section and |    |

| Internal Reference Section                              | 34 |

| Changes to Figure 56                                    | 36 |

| Changes to Figure 62                                    | 41 |

| Changes to Figure 65                                    |    |

| Updated Outline Dimensions                              |    |

### 5/12—Rev. A to Rev. B

| Changes to Companion Products Section1                  |

|---------------------------------------------------------|

| Change to Table 512                                     |

| Added Industrial HART Capable Analog Output Application |

| Section and Figure 65, Renumbered Sequentially42        |

| Updated Outline Dimensions                              |

| 11/11—Rev. 0 to Rev. A                                  |

###

#### 7/11—Revision 0: Initial Version

# **DETAILED FUNCTIONAL BLOCK DIAGRAM**

Figure 2.

# **SPECIFICATIONS**

$AV_{DD} = V_{BOOST_x} = 15 \text{ V}; DV_{DD} = 2.7 \text{ V}$  to 5.5 V;  $AV_{CC} = 4.5 \text{ V}$  to 5.5 V; dc-to-dc converter disabled;  $AGND = DGND = GNDSW_x = 0 \text{ V};$  REFIN = 5 V;  $R_L = 300 \Omega$ ; all specifications  $T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted.

Table 1.

| Min    | Тур                                                                                                                                    | Max                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Unit                                                 | Test Conditions/Comments                                                                                                                                                           |

|--------|----------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        |                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                      |                                                                                                                                                                                    |

| 0      |                                                                                                                                        | 24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | mA                                                   |                                                                                                                                                                                    |

| 0      |                                                                                                                                        | 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | mA                                                   |                                                                                                                                                                                    |

| 4      |                                                                                                                                        | 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | mA                                                   |                                                                                                                                                                                    |

| 12     |                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Bits                                                 |                                                                                                                                                                                    |

|        |                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                      | Assumes ideal resistor (see the External Current Setting Resistor section for more information)                                                                                    |

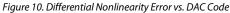

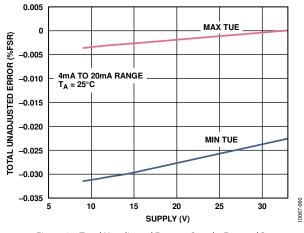

| -0.1   | ±0.019                                                                                                                                 | +0.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | % FSR                                                |                                                                                                                                                                                    |

|        | 100                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ppm FSR                                              | Drift after 1000 hours, TJ = 150°C                                                                                                                                                 |

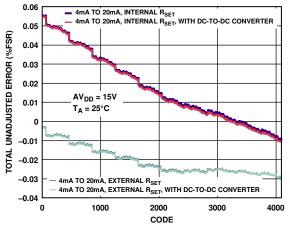

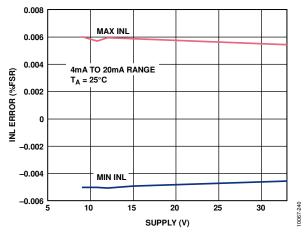

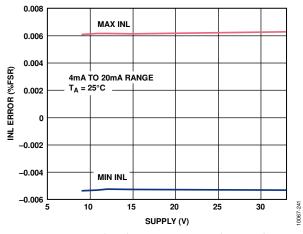

| -0.032 | ±0.006                                                                                                                                 | +0.032                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | % FSR                                                |                                                                                                                                                                                    |

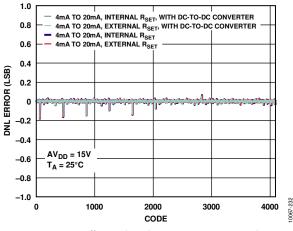

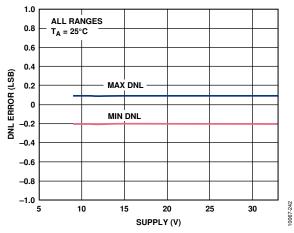

| -1     |                                                                                                                                        | +1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | LSB                                                  | Guaranteed monotonic                                                                                                                                                               |

| -0.1   | ±0.012                                                                                                                                 | +0.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | % FSR                                                |                                                                                                                                                                                    |

|        | ±4                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ppm FSR/°C                                           |                                                                                                                                                                                    |

| -0.1   | ±0.004                                                                                                                                 | +0.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | % FSR                                                |                                                                                                                                                                                    |

|        | ±3                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ppm FSR/°C                                           |                                                                                                                                                                                    |

| -0.1   | ±0.014                                                                                                                                 | +0.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | % FSR                                                |                                                                                                                                                                                    |

|        | ±5                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ppm FSR/°C                                           |                                                                                                                                                                                    |

|        | 0.0005                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | % FSR                                                | External R <sub>SET</sub>                                                                                                                                                          |

|        |                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                      |                                                                                                                                                                                    |

| -0.14  | ±0.022                                                                                                                                 | +0.14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | % FSR                                                |                                                                                                                                                                                    |

|        | 180                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ppm FSR                                              | Drift after 1000 hours, TJ = 150°C                                                                                                                                                 |

| -0.032 | ±0.006                                                                                                                                 | +0.032                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | % FSR                                                |                                                                                                                                                                                    |

| -1     |                                                                                                                                        | +1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | LSB                                                  | Guaranteed monotonic                                                                                                                                                               |

| -0.1   | ±0.017                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                      |                                                                                                                                                                                    |

|        |                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                      |                                                                                                                                                                                    |

| -0.12  |                                                                                                                                        | +0.12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                      |                                                                                                                                                                                    |

|        |                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                      |                                                                                                                                                                                    |

| -0.14  |                                                                                                                                        | +0.14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                      |                                                                                                                                                                                    |

|        |                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                      |                                                                                                                                                                                    |

|        |                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                      | Internal R <sub>SET</sub>                                                                                                                                                          |

|        |                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                      |                                                                                                                                                                                    |

|        | VBOOST x -                                                                                                                             | VBOOST x -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | v                                                    |                                                                                                                                                                                    |

|        | 2.4                                                                                                                                    | 2.7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                      |                                                                                                                                                                                    |

|        |                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                      | Drift after 1000 hours, $\frac{3}{4}$ scale output, T <sub>J</sub> = 150°C                                                                                                         |

|        | 90                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ppm FSR                                              | External R <sub>SET</sub>                                                                                                                                                          |

|        | 140                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ppm FSR                                              | Internal R <sub>SET</sub>                                                                                                                                                          |

|        |                                                                                                                                        | 1000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Ω                                                    | The dc-to-dc converter has been characterized with a maximum load of 1 k $\Omega$ , chosen such that compliance is not exceeded; see Figure 31 and the DC-DC MaxV bits in Table 27 |

|        | 100                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | MΩ                                                   |                                                                                                                                                                                    |

|        | 0.02                                                                                                                                   | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | μA/V                                                 |                                                                                                                                                                                    |

| ł      |                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | -                                                    |                                                                                                                                                                                    |

|        |                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                      |                                                                                                                                                                                    |

| 4.95   | 5                                                                                                                                      | 5.05                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | V                                                    | For specified performance                                                                                                                                                          |

| 45     | 150                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | MΩ                                                   |                                                                                                                                                                                    |

| 1      |                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                      |                                                                                                                                                                                    |

|        |                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                      |                                                                                                                                                                                    |

| 4.995  | 5                                                                                                                                      | 5.005                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | V                                                    | T <sub>A</sub> = 25°C                                                                                                                                                              |

|        | $ \begin{array}{c} 0\\ 0\\ 4\\ 12\\ -0.1\\ -0.032\\ -1\\ -0.1\\ -0.1\\ -0.1\\ -0.14\\ -0.032\\ -1\\ -0.12\\ -0.14\\ \end{array} $ 4.95 | $\begin{array}{c} 0\\ 0\\ 4\\ 12\\ \hline\\ -0.1 \\ \pm 0.019\\ 100\\ \hline\\ -0.032 \\ \pm 0.006\\ \hline\\ -1\\ -0.1 \\ \pm 0.012\\ \\ \pm 4\\ -0.1 \\ \pm 0.012\\ \\ \pm 4\\ \hline\\ -0.1 \\ \pm 0.004\\ \\ \pm 3\\ \hline\\ -0.1 \\ \pm 0.004\\ \\ \pm 3\\ \hline\\ -0.1 \\ \pm 0.004\\ \\ \pm 5\\ 0.0005\\ \hline\\ -0.12 \\ \pm 0.006\\ \hline\\ -1\\ \hline\\ -0.1 \\ \pm 0.017\\ \\ \pm 6\\ \hline\\ -0.12 \\ \pm 0.004\\ \\ \pm 9\\ \hline\\ -0.14 \\ \pm 0.02\\ \\ \pm 14\\ \hline\\ -0.011\\ \hline\\ \end{array}$ | $\begin{array}{cccccccccccccccccccccccccccccccccccc$ | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                              |

# AD5737

| Parameter <sup>1</sup>                      | Min                    | Тур   | Max  | Unit   | Test Conditions/Comments                                                          |

|---------------------------------------------|------------------------|-------|------|--------|-----------------------------------------------------------------------------------|

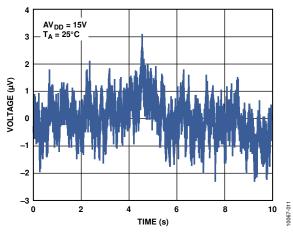

| Output Noise (0.1 Hz to 10 Hz) <sup>2</sup> |                        | 7     |      | μV p-p |                                                                                   |

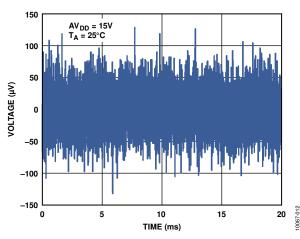

| Noise Spectral Density <sup>2</sup>         |                        | 100   |      | nV/√Hz | At 10 kHz                                                                         |

| Output Voltage Drift vs. Time <sup>2</sup>  | 180                    |       |      | ppm    | Drift after 1000 hours, TJ = 150°C                                                |

| Capacitive Load <sup>2</sup>                |                        | 1000  |      | nF     |                                                                                   |

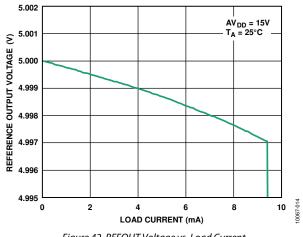

| Load Current                                |                        | 9     |      | mA     | See Figure 42                                                                     |

| Short-Circuit Current                       |                        | 10    |      | mA     |                                                                                   |

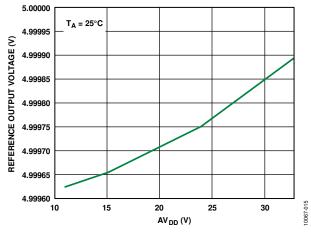

| Line Regulation <sup>2</sup>                |                        | 3     |      | ppm/V  | See Figure 43                                                                     |

| Load Regulation <sup>2</sup>                |                        | 95    |      | ppm/mA | See Figure 42                                                                     |

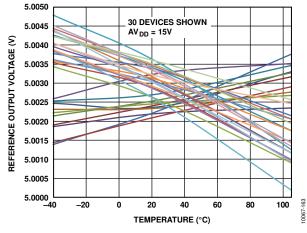

| Thermal Hysteresis <sup>2</sup>             |                        | 200   |      | ppm    |                                                                                   |

| DC-TO-DC CONVERTER                          |                        |       |      |        |                                                                                   |

| Switch                                      |                        |       |      |        |                                                                                   |

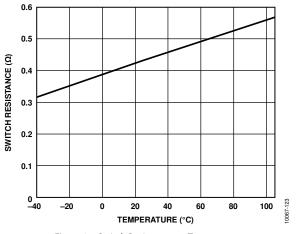

| Switch On Resistance                        |                        | 0.425 |      | Ω      |                                                                                   |

| Switch Leakage Current                      |                        | 10    |      | nA     |                                                                                   |

| Peak Current Limit                          |                        | 0.8   |      | А      |                                                                                   |

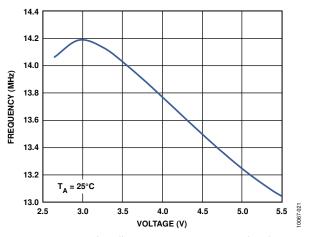

| Oscillator                                  |                        |       |      |        |                                                                                   |

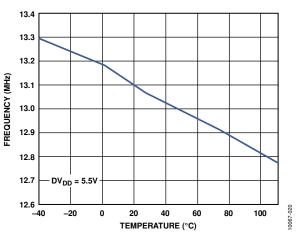

| Oscillator Frequency                        | 11.5                   | 13    | 14.5 | MHz    | This oscillator is divided down to provide the                                    |

|                                             |                        |       |      |        | dc-to-dc converter switching frequency                                            |

| Maximum Duty Cycle                          |                        | 89.6  |      | %      | At 410 kHz dc-to-dc switching frequency                                           |

| DIGITAL INPUTS <sup>2</sup>                 | 1                      |       |      |        | JEDEC compliant                                                                   |

| Input High Voltage, V <sub>IH</sub>         | 2                      |       |      | V      |                                                                                   |

| Input Low Voltage, V <sub>IL</sub>          |                        |       | 0.8  | V      |                                                                                   |

| Input Current                               | -1                     |       | +1   | μA     | Per pin                                                                           |

| Pin Capacitance                             |                        | 2.6   |      | pF     | Per pin                                                                           |

| DIGITAL OUTPUTS <sup>2</sup>                |                        |       |      |        |                                                                                   |

| SDO, ALERT Pins                             |                        |       |      |        |                                                                                   |

| Output Low Voltage, Vol                     |                        |       | 0.4  | v      | Sinking 200 μA                                                                    |

| Output High Voltage, Voн                    | DV <sub>DD</sub> - 0.5 |       |      | v      | Sourcing 200 µA                                                                   |

| High Impedance Leakage<br>Current           | -1                     |       | +1   | μΑ     |                                                                                   |

|                                             |                        | 25    |      | - F    |                                                                                   |

| High Impedance Output<br>Capacitance        |                        | 2.5   |      | pF     |                                                                                   |

| FAULT Pin                                   |                        |       |      |        |                                                                                   |

| Output Low Voltage, Vol                     |                        |       | 0.4  | V      | 10 k $\Omega$ pull-up resistor to DV <sub>DD</sub>                                |

| Output Low Voltage, Vol                     |                        | 0.6   | 0.4  | V      | At 2.5 mA                                                                         |

| Output High Voltage V                       | 3.6                    | 0.0   |      | V      |                                                                                   |

| Output High Voltage, V <sub>OH</sub>        | 5.0                    |       |      | v      | 10 kΩ pull-up resistor to DV <sub>DD</sub>                                        |

| POWER REQUIREMENTS                          |                        |       | 22   | N      |                                                                                   |

|                                             | 9                      |       | 33   | V      |                                                                                   |

|                                             | 2.7                    |       | 5.5  | V      |                                                                                   |

| AVcc                                        | 4.5                    | -     | 5.5  | V      |                                                                                   |

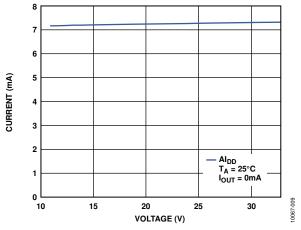

|                                             |                        | 7     | 7.5  | mA     |                                                                                   |

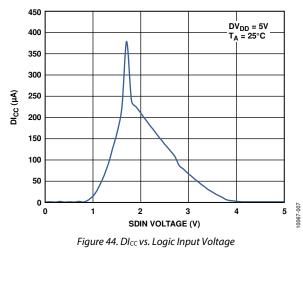

| Dlcc                                        |                        | 9.2   | 11   | mA     | $V_{IH} = DV_{DD}$ , $V_{IL} = DGND$ , internal oscillator running, over supplies |

| Alcc                                        |                        |       | 1    | mA     | Outputs unloaded, over supplies                                                   |

| BOOST <sup>5</sup>                          |                        |       | 1    | mA     | Per channel, 0 mA output                                                          |

| Power Dissipation                           |                        | 155   |      | mW     | $AV_{DD} = 15 V$ , $DV_{DD} = 5 V$ , dc-to-dc converter enabled, outputs disabled |

<sup>1</sup> Temperature range: -40°C to +105°C; typical at +25°C.

<sup>2</sup> Guaranteed by design and characterization; not production tested.

<sup>3</sup> For current outputs with internal R<sub>SET</sub>, the offset, full-scale, and TUE measurements exclude dc crosstalk. The measurements are made with all four channels enabled and loaded with the same code.

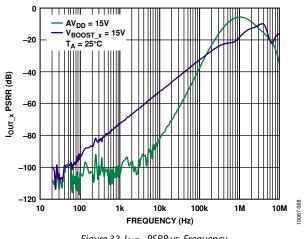

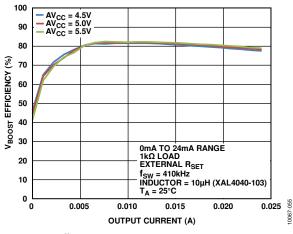

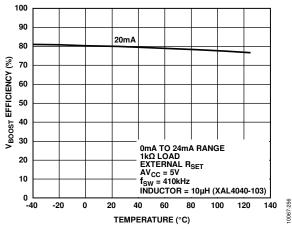

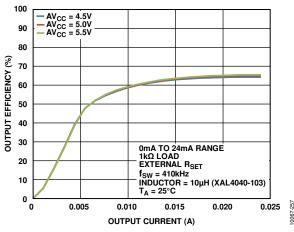

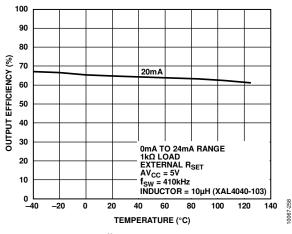

<sup>4</sup> See the Current Output Mode with Internal R<sub>SET</sub> section for more information about dc crosstalk. <sup>5</sup> Efficiency plots in Figure 33 through Figure 36 include the I<sub>BOOST</sub> quiescent current.

### AC PERFORMANCE CHARACTERISTICS

$AV_{DD} = V_{BOOST_x} = 15 \text{ V}; DV_{DD} = 2.7 \text{ V}$  to 5.5 V;  $AV_{CC} = 4.5 \text{ V}$  to 5.5 V; dc-to-dc converter disabled;  $AGND = DGND = GNDSW_x = 0 \text{ V};$ REFIN = 5 V;  $R_L = 300 \Omega$ ; all specifications  $T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted.

#### Table 2.

| Parameter <sup>1</sup>                      | Min     | Тур          | Max        | Unit   | Test Conditions/Comments                                                                           |

|---------------------------------------------|---------|--------------|------------|--------|----------------------------------------------------------------------------------------------------|

| DYNAMIC PERFORMANCE, CURRENT<br>OUTPUT      |         |              |            |        |                                                                                                    |

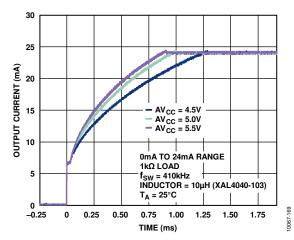

| Output Current Settling Time                |         | 15           |            | μs     | To 0.1% FSR, 0 mA to 24 mA range                                                                   |

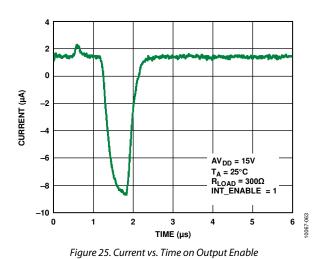

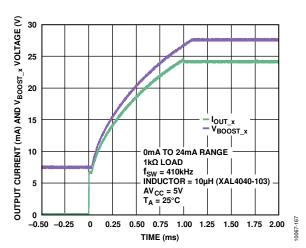

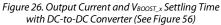

|                                             | See Tes | st Condition | s/Comments | ms     | For settling times when using the dc-to-dc con-<br>verter, see Figure 26, Figure 27, and Figure 28 |

| Output Noise (0.1 Hz to 10 Hz<br>Bandwidth) | 0.15    |              | 0.15       |        | 12-bit LSB, 0 mA to 24 mA range                                                                    |

| Output Noise Spectral Density               |         | 0.5          |            | nA/√Hz | Measured at 10 kHz, midscale output, 0 mA to 24 mA range                                           |

<sup>1</sup> Guaranteed by design and characterization; not production tested.

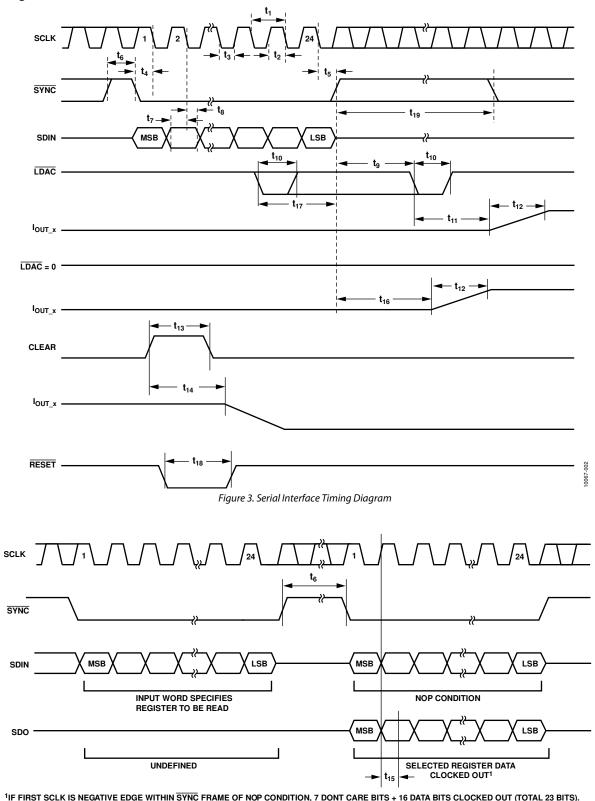

### TIMING CHARACTERISTICS

$AV_{DD} = V_{BOOST_x} = 15 \text{ V}; DV_{DD} = 2.7 \text{ V}$  to 5.5 V;  $AV_{CC} = 4.5 \text{ V}$  to 5.5 V; dc-to-dc converter disabled;  $AGND = DGND = GNDSW_x = 0 \text{ V};$ REFIN = 5 V;  $R_L = 300 \Omega$ ; all specifications  $T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted.

| Parameter <sup>1, 2, 3</sup> | Limit at T <sub>MIN</sub> , T <sub>MAX</sub> | Unit   | Description                                                                                                            |  |  |  |

|------------------------------|----------------------------------------------|--------|------------------------------------------------------------------------------------------------------------------------|--|--|--|

| t1                           | 33                                           | ns min | SCLK cycle time                                                                                                        |  |  |  |

| t <sub>2</sub>               | 13                                           | ns min | SCLK high time                                                                                                         |  |  |  |

| t <sub>3</sub>               | 13                                           | ns min | SCLK low time                                                                                                          |  |  |  |

| t4                           | 13                                           | ns min | SYNC falling edge to SCLK falling edge setup time                                                                      |  |  |  |

| t <sub>5</sub>               | 13                                           | ns min | 24th/32nd SCLK falling edge to SYNC rising edge (see Figure 54)                                                        |  |  |  |

| t <sub>6</sub>               | 198                                          | ns min | SYNC high time following a configuration write                                                                         |  |  |  |

|                              | 5                                            | µs min | SYNC high time following a DAC update write                                                                            |  |  |  |

| t <sub>7</sub>               | 5                                            | ns min | Data setup time                                                                                                        |  |  |  |

| t <sub>8</sub>               | 5                                            | ns min | Data hold time                                                                                                         |  |  |  |

| t9                           | 20                                           | µs min | SYNC rising edge to LDAC falling edge (applies to any channel with digital slew                                        |  |  |  |

|                              |                                              |        | rate control enabled; single DAC updated)                                                                              |  |  |  |

|                              | 5                                            | μs min | SYNC rising edge to LDAC falling edge (single DAC updated)                                                             |  |  |  |

| t <sub>10</sub>              | 10                                           | ns min | LDAC pulse width low                                                                                                   |  |  |  |

| t11                          | 500                                          | ns max | LDAC falling edge to DAC output response time                                                                          |  |  |  |

| t <sub>12</sub>              | See Table 2                                  | µs max | DAC output settling time                                                                                               |  |  |  |

| t <sub>13</sub>              | 10                                           | ns min | CLEAR high time                                                                                                        |  |  |  |

| t <sub>14</sub>              | 5                                            | µs max | CLEAR activation time                                                                                                  |  |  |  |

| t15                          | 40                                           | ns max | SCLK rising edge to SDO valid                                                                                          |  |  |  |

| t <sub>16</sub>              | 5                                            | µs min | $\overline{\text{SYNC}}$ rising edge to DAC output response time ( $\overline{\text{LDAC}} = 0$ ) (single DAC updated) |  |  |  |

| t <sub>17</sub>              | 500                                          | ns min | LDAC falling edge to SYNC rising edge                                                                                  |  |  |  |

| t <sub>18</sub>              | 800                                          | ns min | RESET pulse width                                                                                                      |  |  |  |

| <b>t</b> 19                  | 20                                           | µs min | SYNC rising edge to next SYNC low (falling edge (digital slew rate control enabled;                                    |  |  |  |

|                              |                                              |        | single DAC updated)                                                                                                    |  |  |  |

|                              | 5                                            | µs min | SYNC rising edge to next SYNC low (falling edge (digital slew rate control disabled;                                   |  |  |  |

|                              |                                              |        | single DAC updated)                                                                                                    |  |  |  |

<sup>1</sup> Guaranteed by design and characterization; not production tested.

$^{2}$  All input signals are specified with t<sub>RISE</sub> = t<sub>FALL</sub> = 5 ns (10% to 90% of DV<sub>DD</sub>) and timed from a voltage level of 1.2 V.

<sup>3</sup> See Figure 3, Figure 4, Figure 5, and Figure 7.

# AD5737

0067-003

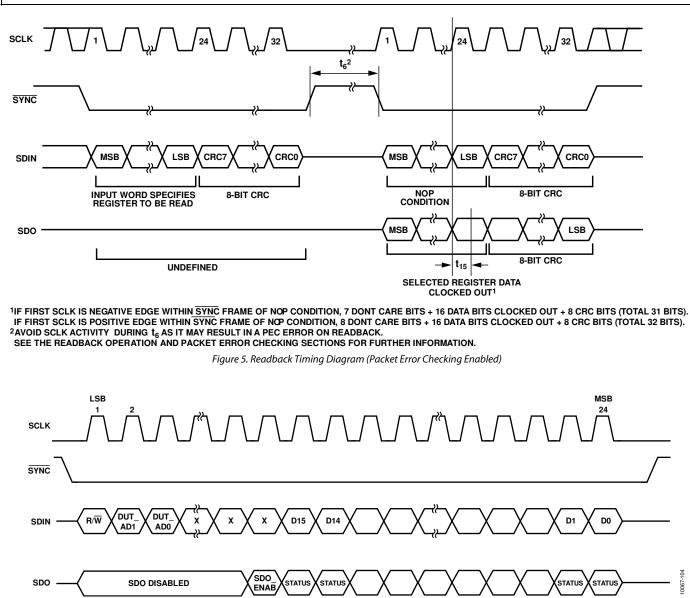

### **Timing Diagrams**

<sup>1</sup>IF FIRST SCLK IS NEGATIVE EDGE WITHIN SYNC FRAME OF NOP CONDITION, 7 DONT CARE BITS + 16 DATA BITS CLOCKED OUT (TOTAL 23 BITS). IF FIRST SCLK IS POSITIVE EDGE WITHIN SYNC FRAME OF NOP CONDITION, 8 DONT CARE BITS + 16 DATA BITS CLOCKED OUT (TOTAL 24 BITS). SEE THE READBACK OPERATION SECTION FOR FURTHER INFORMATION.

Figure 4. Readback Timing Diagram (Packet Error Checking Disabled)

10067-004

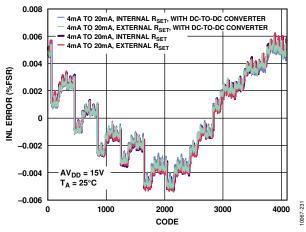

Figure 7. Load Circuit for SDO Timing Diagrams

### **ABSOLUTE MAXIMUM RATINGS**

$T_A = 25^{\circ}$ C, unless otherwise noted. Transient currents of up to 100 mA do not cause SCR latch-up.

#### Table 4.

| Parameter                                             | Rating                                                               |  |  |

|-------------------------------------------------------|----------------------------------------------------------------------|--|--|

| AV <sub>DD</sub> , V <sub>BOOST_x</sub> to AGND, DGND | –0.3 V to +33 V                                                      |  |  |

| AVcc to AGND                                          | –0.3 V to +7 V                                                       |  |  |

| DV <sub>DD</sub> to DGND                              | –0.3 V to +7 V                                                       |  |  |

| Digital Inputs to DGND                                | -0.3 V to DV <sub>DD</sub> + 0.3 V or +7 V<br>(whichever is less)    |  |  |

| Digital Outputs to DGND                               | -0.3 V to DV <sub>DD</sub> + 0.3 V or +7 V<br>(whichever is less)    |  |  |

| REFIN, REFOUT to AGND                                 | -0.3 V to AV <sub>DD</sub> + 0.3 V or +7 V<br>(whichever is less)    |  |  |

| IouT_x to AGND                                        | AGND to V <sub>BOOST_x</sub> or 33 V if using the dc-to-dc converter |  |  |

| SW <sub>x</sub> to AGND                               | –0.3 V to +33 V                                                      |  |  |

| AGND, GNDSW <sub>x</sub> to DGND                      | –0.3 V to +0.3 V                                                     |  |  |

| Operating Temperature Range (T <sub>A</sub> )         |                                                                      |  |  |

| Industrial <sup>1</sup>                               | -40°C to +105°C                                                      |  |  |

| Storage Temperature Range                             | –65°C to +150°C                                                      |  |  |

| Junction Temperature (TJ max)                         | 125°C                                                                |  |  |

| Power Dissipation                                     | $(T_J max - T_A)/\theta_{JA}$                                        |  |  |

| Lead Temperature                                      | JEDEC industry standard                                              |  |  |

| Soldering                                             | J-STD-020                                                            |  |  |

$^{\rm 1}$  Power dissipated on chip must be derated to keep the junction temperature below 125°C.

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### THERMAL RESISTANCE

Junction-to-air thermal resistance ( $\theta_{JA}$ ) is specified for a JEDEC 4-layer test board.

#### Table 5. Thermal Resistance

| Package Type            | θ <sub>JA</sub> | Unit |

|-------------------------|-----------------|------|

| 64-Lead LFCSP (CP-64-3) | 28              | °C/W |

### ESD CAUTION

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

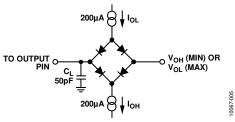

## PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Figure 8. Pin Configuration

| Table 6 | Pin | Function | D | escriptions |

|---------|-----|----------|---|-------------|

|---------|-----|----------|---|-------------|

| Pin No. | Mnemonic           | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|---------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|