Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# **Lithium Ion Battery Monitoring System**

**AD7280A**

#### **FEATURES**

12-bit ADC, 1 µs per channel conversion time 6 analog input channels, common-mode range 0.5 V to 27.5 V **6 auxiliary ADC inputs** ±1.6 mV cell voltage accuracy On-chip voltage regulator **Cell balancing interface Daisy-chain interface** Internal reference: ±3 ppm/°C 1.8 µA power-down current High input impedance Serial interface with alert function 1 SPI interface for up to 48 channels

On-chip registers for channel sequencing **VDD operating range: 8 V to 30 V**

CRC protection on read and write commands

Temperature range: -40°C to +105°C 48-lead LQFP

**Qualified for automotive applications**

#### **APPLICATIONS**

Lithium ion battery monitoring **Electric and hybrid electric vehicles** Power supply backup **Power tools**

#### **GENERAL DESCRIPTION**

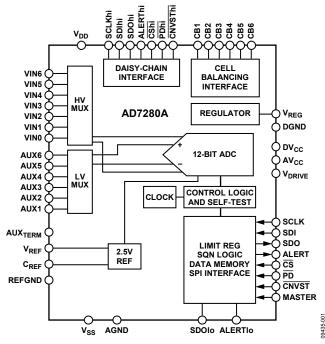

The AD7280A1 contains all the functions required for generalpurpose monitoring of stacked lithium ion batteries as used in hybrid electric vehicles, battery backup applications, and power tools. The part has multiplexed cell voltage and auxiliary ADC measurement channels for up to six cells of battery management. An internal ±3 ppm/°C reference is provided that allows a cell voltage accuracy of ±1.6 mV. The ADC resolution is 12 bits and allows conversion of up to 48 cells within 7 µs.

The AD7280A operates from a single V<sub>DD</sub> supply that has a range of 8 V to 30 V (with an absolute maximum rating of 33 V). The part provides six differential analog input channels to accommodate large common-mode signals across the full V<sub>DD</sub> range. Each channel allows an input signal range, VIN(+) - VIN(-), of 1 V to 5 V. The input pins assume a series stack of six cells. In addition, the part includes six auxiliary ADC input channels that can be used for temperature measurement or system diagnostics.

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

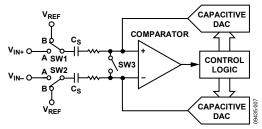

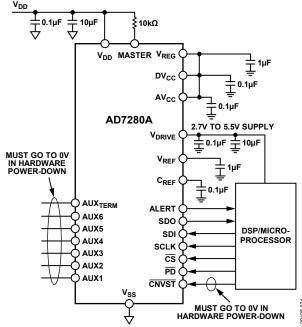

#### FUNCTIONAL BLOCK DIAGRAM

Fiaure 1.

The AD7280A includes on-chip registers that allow a sequence of channel measurements to be programmed to suit the application requirements.

The AD7280A also includes a dynamic alert function that can detect whether the cell voltages or auxiliary ADC inputs exceed an upper or lower limit defined by the user. The AD7280A has cell balancing interface outputs designed to control external FET transistors to allow discharging of individual cells.

The AD7280A includes a built-in self-test feature that internally applies a known voltage to the ADC inputs.

A daisy-chain interface allows up to eight parts to be stacked without the need for individual device isolation.

The AD7280A requires only one supply pin that accepts 6.9 mA under normal operation while converting at 1 MSPS.

All this functionality is provided in a 48-lead LQFP package operating over a temperature range of -40°C to +105°C.

Fax: 781.461.3113 ©2011 Analog Devices, Inc. All rights reserved.

<sup>&</sup>lt;sup>1</sup> Patents pending.

# AD7280A\* PRODUCT PAGE QUICK LINKS

Last Content Update: 02/23/2017

## COMPARABLE PARTS 🖵

View a parametric search of comparable parts.

### **EVALUATION KITS**

· AD7280A Evaluation Board

### **DOCUMENTATION**

#### **Data Sheet**

AD7280A: Lithium Ion Battery Monitoring System Data Sheet

#### **User Guides**

UG-252: Evaluation Board for the AD7280A Lithium Ion Battery Monitoring System

## SOFTWARE AND SYSTEMS REQUIREMENTS 🖳

AD7280A IIO Lithium Ion Battery Monitoring System Linux Driver

### REFERENCE DESIGNS $\Box$

- CN0197

- CN0235

# **DESIGN RESOURCES**

- · AD7280A Material Declaration

- PCN-PDN Information

- · Quality And Reliability

- Symbols and Footprints

### **DISCUSSIONS**

View all AD7280A EngineerZone Discussions.

### SAMPLE AND BUY

Visit the product page to see pricing options.

## **TECHNICAL SUPPORT**

Submit a technical question or find your regional support number.

### DOCUMENT FEEDBACK $\Box$

Submit feedback for this data sheet.

# **TABLE OF CONTENTS**

| Features                                                                 | 1  |

|--------------------------------------------------------------------------|----|

| Applications                                                             | 1  |

| Functional Block Diagram                                                 | 1  |

| General Description                                                      | 1  |

| Revision History                                                         | 2  |

| Specifications                                                           | 3  |

| Power Specifications                                                     | 5  |

| Timing Specifications                                                    | 6  |

| Absolute Maximum Ratings                                                 | 7  |

| Thermal Resistance                                                       | 7  |

| ESD Caution                                                              | 7  |

| Pin Configuration and Function Descriptions                              | 8  |

| Typical Performance Characteristics                                      | 11 |

| Terminology                                                              | 14 |

| Theory of Operation                                                      | 15 |

| Circuit Information                                                      | 15 |

| Converter Operation                                                      | 15 |

| Analog Input Structure                                                   | 16 |

| Transfer Function                                                        | 16 |

| Typical Connection Diagrams                                              | 17 |

| Reference                                                                | 19 |

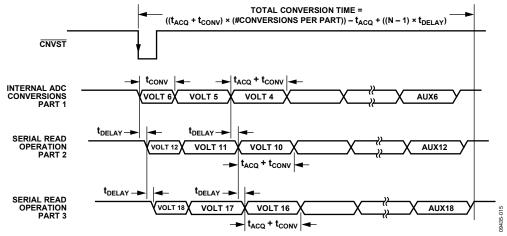

| Converting Cell Voltages and Auxiliary ADC Inputs                        | 19 |

| Converting Cell Voltages and Auxiliary ADC Inputs in a Chain of AD7280As | 21 |

| Conversion Window                                                        | 22 |

| Self-Test Conversion                                                     | 22 |

| Connection of Fewer Than Six Voltage Cells                               | 22 |

| Auxiliary ADC Inputs                                                     | 23 |

| Power Requirements                                                       | 23 |

| Power-Down                                                               | 24 |

| Power-Up Time                                                            | 25 |

| Cell Balancing Outputs                                                   | 25 |

| Alert Output                                                             | 27 |

|                                                                          |    |

| Г | egister map                                                           | 20 |

|---|-----------------------------------------------------------------------|----|

|   | Cell Voltage Registers                                                | 28 |

|   | Auxiliary ADC Registers                                               | 28 |

|   | Self-Test Register                                                    | 28 |

|   | Control Register                                                      | 28 |

|   | Cell Overvoltage Register                                             | 29 |

|   | Cell Undervoltage Register                                            | 30 |

|   | AUX ADC Overvoltage Register                                          | 30 |

|   | AUX ADC Undervoltage Register                                         | 30 |

|   | Alert Register                                                        | 30 |

|   | Cell Balance Register                                                 | 30 |

|   | CBx Timer Registers                                                   | 30 |

|   | PD Timer Register                                                     | 31 |

|   | Read Register                                                         | 31 |

|   | CNVST Control Register                                                | 31 |

| S | erial Interface                                                       | 32 |

|   | Writing to the AD7280A                                                | 32 |

|   | Reading from the AD7280A                                              | 33 |

| D | aisy-Chain Interface                                                  | 34 |

|   | Addressing the AD7280A While Reading Back Conversion or Register Data |    |

|   | Initializing the AD7280A                                              | 34 |

|   | Write Acknowledge                                                     | 35 |

|   | Cyclic Redundancy Check                                               | 35 |

| E | xamples of Interfacing with the AD7280A                               | 38 |

|   | Convert and Readback Routine                                          | 38 |

|   | Examples                                                              | 38 |

| E | MC Guidelines                                                         | 44 |

|   | Schematic and Layout Guidelines                                       | 44 |

|   | Operation in a Noisy Environment                                      | 44 |

|   | Software Flowchart                                                    | 45 |

| О | outline Dimensions                                                    | 46 |

|   | Ordering Guide                                                        | 46 |

|   | Automotive Products                                                   | 46 |

### **REVISION HISTORY**

4/11—Revision 0: Initial Version

# **SPECIFICATIONS**

$V_{DD} = 8 \ V \ to \ 30 \ V, \ V_{SS} = 0 \ V, \ DV_{CC} = AV_{CC} = V_{REG}, \ V_{DRIVE} = 2.7 \ V \ to \ 5.5 \ V, \ T_A = -40 ^{\circ}C \ to \ +105 ^{\circ}C, \ unless \ otherwise \ noted.$

Table 1.

| Parameter                                    | Min                                | Тур        | Max                                | Unit              | Test Conditions/Comments                                       |

|----------------------------------------------|------------------------------------|------------|------------------------------------|-------------------|----------------------------------------------------------------|

| DC ACCURACY (VIN0 TO VIN6)1                  |                                    | •          |                                    |                   |                                                                |

| Resolution                                   | 12                                 |            |                                    | Bits              | No missing codes                                               |

| Integral Nonlinearity                        |                                    | ±1         |                                    | LSB               |                                                                |

| Differential Nonlinearity                    |                                    | ±0.8       |                                    | LSB               |                                                                |

| Offset Error                                 |                                    | ±1         |                                    | LSB               |                                                                |

| Offset Error Match                           |                                    | 1          |                                    | LSB               |                                                                |

| Gain Error                                   |                                    | ±1         |                                    | LSB               |                                                                |

| Gain Error Match                             |                                    | 1          |                                    | LSB               |                                                                |

| ADC Unadjusted Error <sup>2, 3</sup>         |                                    | ±1.2       |                                    | mV                |                                                                |

| Total Unadjusted Error <sup>4, 5</sup>       |                                    |            | ±9                                 | mV                | $V_{IN}$ range <sup>6</sup> = 1 V to 4.1 V, -10°C to +85°C     |

| •                                            |                                    |            | ±10                                | mV                | $V_{IN}$ range <sup>6</sup> = 1 V to 4.1 V, -40°C to +85°C     |

|                                              |                                    | ±1.6       | ±14.5                              | mV                | $V_{IN}$ range <sup>6</sup> = 1 V to 4.1 V, -40°C to +105°C    |

| CELL VOLTAGE INPUTS (VIN0 TO VIN6)           |                                    |            |                                    |                   | ,                                                              |

| Pseudo Differential Input Voltage            |                                    |            |                                    |                   |                                                                |

| VIN(x) - VIN(x - 1)                          | 1                                  |            | $2 \times V_{REF}$                 | V                 |                                                                |

| Absolute Input Voltage                       | V <sub>CM</sub> — V <sub>REF</sub> |            | V <sub>CM</sub> + V <sub>REF</sub> | V                 |                                                                |

| Common-Mode Input Voltage                    | 0.5                                |            | 27.5                               | V                 |                                                                |

| Static Leakage Current <sup>7</sup>          |                                    | ±5         | ±70                                | nA                |                                                                |

| Dynamic Leakage Current <sup>7</sup>         |                                    |            | ±3                                 | nA                | CNVST pulse every 100 ms                                       |

| Input Capacitance                            |                                    | 15         | _5                                 | pF                | control pulse every recomme                                    |

| DC ACCURACY (AUX1 TO AUX6) <sup>1, 8</sup>   |                                    | 13         |                                    | Pi                |                                                                |

| Resolution                                   | 12                                 |            |                                    | Bits              | No missing codes                                               |

| Integral Nonlinearity                        | 12                                 | ±1         |                                    | LSB               | No missing codes                                               |

| Differential Nonlinearity                    |                                    | ±0.8       |                                    | LSB               |                                                                |

| Offset Error                                 |                                    | ±0.8<br>±2 |                                    | LSB               |                                                                |

| Offset Error Match                           |                                    | 2          |                                    | LSB               |                                                                |

| Gain Error                                   |                                    | ±2         |                                    | LSB               |                                                                |

| Gain Error Match                             |                                    | 2          |                                    | LSB               |                                                                |

| ADC Unadjusted Error <sup>9</sup>            |                                    | ±1.2       |                                    | mV                |                                                                |

| Total Unadjusted Error <sup>10</sup>         |                                    | ±1.∠       | ±20                                | mV                | _40°C to +85°C                                                 |

| Total Olladjusted Ellol                      |                                    | ±1.6       | ±22                                | mV                | -40°C to +105°C                                                |

| AUXILIARY ADC INPUTS (AUX1 TO AUX6)          |                                    | ±1.0       | 122                                | 1110              | -40 C to +103 C                                                |

| Input Voltage Range                          | 0                                  |            | $2 \times V_{REF}$                 | V                 |                                                                |

| Static Leakage Current <sup>7</sup>          | 0                                  | ±15        | Z X V REF                          |                   |                                                                |

| Dynamic Leakage Current <sup>7</sup>         |                                    | ±13        | ±3                                 | nA<br>nA          | CNVST pulse every 100 ms                                       |

| -                                            |                                    | 1.5        | ±3                                 |                   | Civisi puise every 100 ms                                      |

| Input Capacitance REFERENCE                  |                                    | 15         |                                    | pF                |                                                                |

|                                              | 2.404                              | 2.5        | 2.506                              |                   | 409C to 1059C                                                  |

| Reference Voltage                            | 2.494                              | 2.5        | 2.506                              | V                 | -40°C to +85°C                                                 |

| Deference Veltage Towns                      | 2.494                              | 2.5        | 2.509                              | V                 | -40°C to +105°C                                                |

| Reference Voltage Temperature<br>Coefficient |                                    | ±3         | ±15                                | ppm/°C            | −40°C to +85°C                                                 |

|                                              |                                    | ±11        |                                    | ppm/°C            | -40°C to +105°C                                                |

| Output Voltage Hysteresis                    |                                    | 50         |                                    | ppm               | -40°C to +105°C                                                |

| Long-Term Drift                              |                                    | 150        |                                    | ppm/1000<br>hours |                                                                |

| Line Regulation                              |                                    | ±5         |                                    | ppm/V             |                                                                |

| Turn-On Settling Time 11, 12                 |                                    | 5.5        | 10                                 | ms                | $V_{REG} = 1 \mu F$ , $V_{REF} = 1 \mu F$ , $C_{REF} = 100 nF$ |

| Parameter                                      | Min                    | Тур          | Max                    | Unit  | Test Conditions/Comments     |

|------------------------------------------------|------------------------|--------------|------------------------|-------|------------------------------|

| REGULATOR OUTPUT (V <sub>REG</sub> )           |                        |              |                        |       |                              |

| Input Voltage Range                            | 8                      |              | 30                     | V     |                              |

| Output Voltage, V <sub>REG</sub> 13            | 4.9                    | 5.2          | 5.5                    | V     | 5 mA external load           |

| Output Current <sup>14</sup>                   |                        |              | 5                      | mA    |                              |

| Line Regulation                                |                        | 0.5          |                        | mV/V  |                              |

| Load Regulation                                |                        | 2.5          |                        | mV/mA |                              |

| Internal Short Protection Limit                |                        | 25           |                        | mA    | For a 10 Ω short             |

| CELL BALANCING OUTPUTS <sup>15</sup>           |                        |              |                        |       |                              |

| Output High Voltage, V <sub>OH</sub>           | V <sub>REG</sub> – 1   | 5            | $V_{\text{REG}} + 0.2$ | V     | I <sub>SOURCE</sub> = 415 nA |

| Output Low Voltage, Vol                        | 0                      |              |                        | V     |                              |

| CB1 Output Ramp-Up Time <sup>16</sup>          |                        | 30           |                        | μs    | For an 80 pF load            |

| CB1 Output Ramp-Down Time <sup>17</sup>        |                        | 30           |                        | μs    | For an 80 pF load            |

| CB2 to CB6 Output Ramp-Up Time16               |                        | 380          |                        | μs    | For an 80 pF load            |

| CB2 to CB6 Output Ramp-Down Time <sup>17</sup> |                        | 30           |                        | μs    | For an 80 pF load            |

| LOGIC INPUTS                                   |                        |              |                        |       |                              |

| Input High Voltage, V <sub>INH</sub>           | 2.4                    |              |                        | V     |                              |

| Input Low Voltage, V <sub>INL</sub>            |                        |              | 0.4                    | V     |                              |

| Input Current, I <sub>IN</sub>                 |                        |              | ±10                    | μΑ    |                              |

| Input Capacitance, C <sub>IN</sub>             |                        | 5            |                        | pF    |                              |

| LOGIC OUTPUTS                                  |                        |              |                        |       |                              |

| Output High Voltage, Vон                       | $V_{DRIVE} \times 0.9$ | )            |                        | V     | I <sub>SOURCE</sub> = 200 μA |

| Output Low Voltage, V <sub>OL</sub>            |                        |              | 0.4                    | V     | $I_{SINK} = 200  \mu A$      |

| Floating State Leakage Current                 |                        |              | ±10                    | μΑ    |                              |

| Floating State Output Capacitance              |                        | 5            |                        | pF    |                              |

| Output Coding                                  |                        | Straight bir | nary                   |       |                              |

<sup>&</sup>lt;sup>1</sup> For dc accuracy specifications, the LSB size for cell voltage measurements is  $(2 \times V_{REF} - 1 \text{ V})/4096$ . The LSB size for auxiliary ADC input voltage measurements is  $(2 \times V_{REF})/4096$ .

<sup>&</sup>lt;sup>2</sup> ADC unadjusted error includes the INL of the ADC and the gain and offset errors of the VIN0 to VIN6 input channels.

<sup>&</sup>lt;sup>3</sup> The conversion accuracy during cell balancing is decreased due to the activation of the cell balance circuitry. The ADC unadjusted error increases by a factor of 4.

<sup>&</sup>lt;sup>4</sup> Total unadjusted error includes the INL of the ADC and the gain and offset errors of the VIN0 to VIN6 input channels, as well as the reference error, that is, the difference between the ideal and actual reference voltage and the temperature coefficient of the 2.5 V reference.

<sup>&</sup>lt;sup>5</sup> The conversion accuracy during cell balancing is decreased due to the activation of the cell balance circuitry. The total unadjusted error increases by a factor of 4.

$<sup>^6</sup>$  For the full analog input range, that is, 1 V to  $2 \times V_{REF}$ , the total unadjusted error increases by 20%.

<sup>&</sup>lt;sup>7</sup> The total current measured on the input pins while converting is the sum of the static and dynamic leakage currents. See the Terminology section.

<sup>&</sup>lt;sup>8</sup> Bit D3 of the control register is set to 0 (thermistor termination resistor function is not in use).

<sup>&</sup>lt;sup>9</sup> ADC unadjusted error includes the INL of the ADC and the gain and offset errors of the AUXx input channels.

<sup>&</sup>lt;sup>10</sup> Total unadjusted error includes the INL of the ADC and the gain and offset errors of the AUXx input channels, as well as the reference error, that is, the difference between the ideal and actual reference voltage and the temperature coefficient of the 2.5 V reference.

<sup>11</sup> The turn-on settling time is the time from the rising edge of the  $\overline{PD}$  signal until the conversion result settles to the specified accuracy. This includes the time required to power up the regulator and the reference. Note that a rising edge on the  $\overline{CNVST}$  input is also required to power up the reference. This rising edge should occur after the rising edge on  $\overline{PD}$ .

<sup>&</sup>lt;sup>12</sup> Sample tested during initial release to ensure compliance.

<sup>&</sup>lt;sup>13</sup> The regulator output voltage is specified with an external 5 mA load in addition to the current required to drive the AV<sub>CC</sub>, DV<sub>CC</sub>, and V<sub>DRIVE</sub> supplies of the AD7280A.

<sup>&</sup>lt;sup>14</sup> This specification refers to the maximum regulator output current that is available for external use.

<sup>&</sup>lt;sup>15</sup> The CBx outputs can be set to 0 V or V<sub>REG</sub> with respect to the negative terminal <u>of</u> the cell being balanced.

<sup>16</sup> The CB1 to CB6 output ramp-up times are defined from the rising edge of the CS command until the CB output exceeds V<sub>REG</sub> − 1 V with respect to the negative terminal of the cell being balanced.

<sup>&</sup>lt;sup>17</sup> The CB1 to CB6 output ramp-down times are defined from the rising edge of the CS command until the CB output falls below 50 mV with respect to the negative terminal of the cell being balanced.

### **POWER SPECIFICATIONS**

$V_{DD} = 8 \ V \ to \ 30 \ V, V_{SS} = 0 \ V, DV_{CC} = AV_{CC} = V_{REG}, V_{DRIVE} = 2.7 \ V \ to \ 5.5 \ V, T_A = -40 ^{\circ}C \ to \ +105 ^{\circ}C, unless \ otherwise \ noted.$

Table 2.

| Parameter                            | Min | Тур | Max | Unit | Test Conditions/Comments |

|--------------------------------------|-----|-----|-----|------|--------------------------|

| POWER REQUIREMENTS                   |     |     |     |      |                          |

| $V_{DD}$                             | 8   |     | 30  | V    |                          |

| Master Device                        |     |     |     |      |                          |

| I <sub>DD</sub> During Conversion    |     | 5.6 | 7.3 | mA   |                          |

| IDD During Data Readback             |     | 5.3 | 7.0 | mA   |                          |

| IDD During Cell Balancing            |     | 5.1 | 6.8 | mA   |                          |

| I <sub>DD</sub> Software Power-Down  |     | 2.5 | 2.9 | mA   |                          |

| I <sub>DD</sub> Full Power-Down Mode |     | 1.8 | 5   | μΑ   |                          |

| Slave Device                         |     |     |     |      |                          |

| IDD During Conversion                |     | 6.9 | 8.7 | mA   |                          |

| IDD During Data Readback             |     | 6.5 | 8.2 | mA   |                          |

| IDD During Cell Balancing            |     | 6.4 | 8.0 | mA   |                          |

| I <sub>DD</sub> Software Power-Down  |     | 3.8 | 4.2 | mA   |                          |

| IDD Full Power-Down Mode             |     | 1.8 | 5   | μΑ   |                          |

| POWER DISSIPATION                    |     |     |     |      |                          |

| Master Device                        |     |     |     |      | $V_{DD} = 30 \text{ V}$  |

| During Conversion                    |     | 170 | 220 | mW   |                          |

| During Data Readback                 |     | 160 | 210 | mW   |                          |

| During Cell Balancing                |     | 155 | 205 | mW   |                          |

| Software Power-Down                  |     | 75  | 90  | mW   |                          |

| Full Power-Down Mode                 |     | 54  | 150 | μW   |                          |

| Slave Device                         |     |     |     |      | $V_{DD} = 30 \text{ V}$  |

| During Conversion                    |     | 210 | 265 | mW   |                          |

| During Data Readback                 |     | 195 | 250 | mW   |                          |

| During Cell Balancing                |     | 192 | 240 | mW   |                          |

| Software Power-Down                  |     | 115 | 130 | mW   |                          |

| Full Power-Down Mode                 |     | 54  | 150 | μW   |                          |

#### **TIMING SPECIFICATIONS**

$V_{DD} = 8 \text{ V}$  to 30 V,  $V_{SS} = 0 \text{ V}$ ,  $DV_{CC} = AV_{CC} = V_{REG}$ ,  $V_{DRIVE} = 2.7 \text{ V}$  to 5.5 V,  $T_A = -40^{\circ}\text{C}$  to  $+105^{\circ}\text{C}$ , unless otherwise noted.

Table 3.

| Parameter <sup>1</sup> | Min                    | Тур  | Max  | Unit | Description                                                                                          |

|------------------------|------------------------|------|------|------|------------------------------------------------------------------------------------------------------|

| t <sub>CONV</sub>      |                        |      |      |      | ADC conversion time                                                                                  |

|                        | 425                    | 560  | 695  | ns   | -40°C to +85°C                                                                                       |

|                        | 425                    |      | 720  | ns   | -40°C to +105°C                                                                                      |

| t <sub>ACQ</sub>       |                        |      |      |      | ADC acquisition time, Bits[D6:D5] of the control register set to 00                                  |

|                        | 340                    | 400  | 465  | ns   | -40°C to +85°C                                                                                       |

|                        | 340                    |      | 470  | ns   | -40°C to +105°C                                                                                      |

| $t_{ACQ}$              |                        |      |      |      | ADC acquisition time, Bits[D6:D5] of the control register set to 01                                  |

|                        | 665                    | 800  | 1010 | ns   | -40°C to +85°C                                                                                       |

|                        | 665                    |      | 1030 | ns   | -40°C to +105°C                                                                                      |

| t <sub>ACQ</sub>       |                        |      |      |      | ADC acquisition time, Bits[D6:D5] of the control register set to 10                                  |

|                        | 1005                   | 1200 | 1460 | ns   | −40°C to +85°C                                                                                       |

|                        | 1005                   |      | 1510 | ns   | -40°C to +105°C                                                                                      |

| $t_{ACQ}$              |                        |      |      |      | ADC acquisition time, Bits[D6:D5] of the control register set to 11                                  |

|                        | 1340                   | 1600 | 1890 | ns   | −40°C to +85°C                                                                                       |

|                        | 1340                   |      | 1945 | ns   | −40°C to +105°C                                                                                      |

| t <sub>DELAY</sub>     |                        | 200  | 250  | ns   | Propagation delay between the falling edges of CNVST of adjacent parts in the daisy chain            |

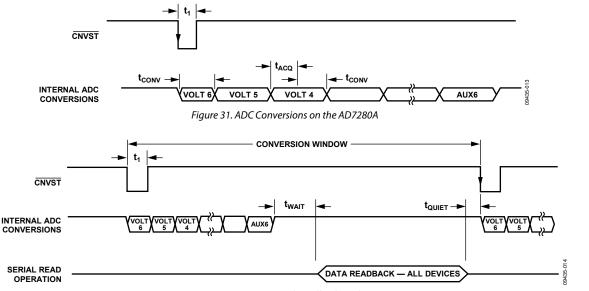

| twait                  | 5                      |      |      | μs   | Time required between the end of conversions and the beginning of readback of the conversion results |

| f <sub>SCLK</sub>      |                        |      | 1    | MHz  | Frequency of serial read clock                                                                       |

| <b>t</b> quiet         | 200                    |      |      | ns   | Minimum quiet time required between the end of a serial read and the start of the next conversion    |

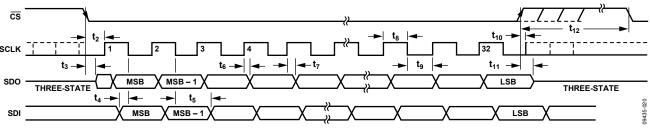

| $t_1^2$                | 0.4                    |      | 50   | μs   | CNVST low pulse                                                                                      |

| $t_2$                  | 10                     |      |      | ns   | CS falling edge to SCLK rising edge                                                                  |

| t <sub>3</sub>         |                        |      | 20   | ns   | Delay from CS falling edge until SDO is three-state disabled                                         |

| t <sub>4</sub>         | 5                      |      |      | ns   | SDI setup time prior to SCLK falling edge                                                            |

| <b>t</b> <sub>5</sub>  | 4                      |      |      | ns   | SDI hold time after SCLK falling edge                                                                |

| $t_6$ <sup>3</sup>     |                        |      | 28   | ns   | Data access time after SCLK rising edge                                                              |

| <b>t</b> <sub>7</sub>  | 20                     |      |      | ns   | SCLK to data valid hold time                                                                         |

| t <sub>8</sub>         | $0.45 \times t_{SCLK}$ |      |      | ns   | SCLK high pulse width                                                                                |

| t <sub>9</sub>         | $0.45 \times t_{SCLK}$ |      |      | ns   | SCLK low pulse width                                                                                 |

| $t_{10}^{4}$           | 100                    |      |      | ns   | CS rising edge to SCLK rising edge                                                                   |

| t <sub>11</sub>        |                        |      | 10   | ns   | CS rising edge to SDO high impedance                                                                 |

| t <sub>12</sub>        | 3                      |      |      | μs   | CS high time required between each 32-bit write/read command                                         |

<sup>&</sup>lt;sup>1</sup> Sample tested during initial release to ensure compliance. All input signals are specified with  $t_R = t_F = 5$  ns (10% to 90% of  $V_{DRIVE}$ ) and timed from a voltage level of 1.6 V. All timing specifications given are with a 25 pF load capacitance.

<sup>2</sup> Maximum allowed CNVST low pulse time to ensure that a software power-down state is not entered when the CNVST pin is not gated.

#### **Timing Diagram**

Figure 2. Serial Interface Timing Diagram

<sup>&</sup>lt;sup>3</sup> Time required for the output to cross 0.4 V or 2.4 V.

$<sup>^4\,</sup>t_{10}$  applies when using a continuous SCLK. Guaranteed by design.

## **ABSOLUTE MAXIMUM RATINGS**

$T_A = 25$ °C, unless otherwise noted.

Table 4.

| Parameter                                                | Rating                                              |

|----------------------------------------------------------|-----------------------------------------------------|

| V <sub>DD</sub> to V <sub>SS</sub> , AGND                | -0.3 V to +33 V                                     |

| V <sub>SS</sub> to AGND, DGND                            | −0.3 V to +0.3 V                                    |

| VINO to VIN5 Voltage to Vss, AGND                        | $V_{SS} - 0.3 \text{ V to } V_{DD} + 0.3 \text{ V}$ |

| VIN6 Voltage to Vss, AGND                                | $V_{DD} - 0.3 V \text{ to } V_{DD} + 1 V$           |

| CB1 Output to Vss, AGND                                  | −0.3 V to DV <sub>CC</sub> + 0.3 V                  |

| CBx Output to $VIN(x - 1)^1$                             | $-0.3 \text{ V to VIN}(x-1)^1 + 7 \text{ V}$        |

| AUX1 to AUX6 Voltage to Vss, AGND                        | -0.3 V to AV <sub>CC</sub> + 0.3 V                  |

| AUX <sub>TERM</sub> Voltage to V <sub>SS</sub> , AGND    | $-0.3 \text{ V to AV}_{CC} + 0.3 \text{ V}$         |

| AVcc to Vss, AGND, DGND                                  | −0.3 V to +7 V                                      |

| $DV_{CC}$ to $AV_{CC}$                                   | −0.3 V to +0.3 V                                    |

| DV <sub>CC</sub> to V <sub>SS</sub> , DGND               | −0.3 V to +7 V                                      |

| V <sub>DRIVE</sub> to V <sub>SS</sub> , AGND             | −0.3 V to +7 V                                      |

| AGND to DGND                                             | −0.3 V to +0.3 V                                    |

| Digital Input Voltage to Vss, DGND                       | -0.3 V to V <sub>DRIVE</sub> + 0.3 V                |

| Digital Output Voltage to Vss, DGND                      | -0.3 V to V <sub>DRIVE</sub> + 0.3 V                |

| Input Current to Any Pin Except Supply Pins <sup>2</sup> | ±10 mA                                              |

| Operating Temperature Range                              | -40°C to +105°C                                     |

| Storage Temperature Range                                | −65°C to +150°C                                     |

| Junction Temperature                                     | 150°C                                               |

| Pb-Free Temperature,<br>Soldering Reflow                 | 260(+0)°C                                           |

| ESD                                                      | 2 kV                                                |

$<sup>^{1}</sup>$  x = 2 to 6.

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

To conform with IPC 2221 industrial standards, it is advisable to use conformal coating on the high voltage pins.

#### THERMAL RESISTANCE

$\theta_{JA}$  is specified for the worst-case conditions, that is, a device soldered in a circuit board for surface-mount packages.

**Table 5. Thermal Resistance**

| Package Type         | θ <sub>JA</sub> | θις | Unit |

|----------------------|-----------------|-----|------|

| 48-Lead LQFP (ST-48) | 76.2            | 17  | °C/W |

#### **ESD CAUTION**

**ESD (electrostatic discharge) sensitive device.**Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

<sup>&</sup>lt;sup>2</sup> Transient currents of up to 100 mA do not cause SCR latch-up.

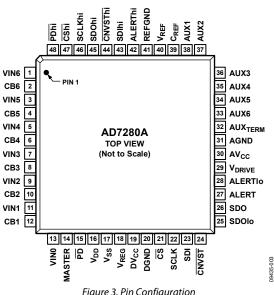

# PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

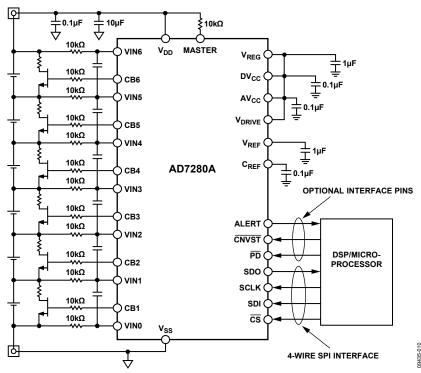

Figure 3. Pin Configuration

**Table 6. Pin Function Descriptions**

| Pin No.                  | Mnemonic         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|--------------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

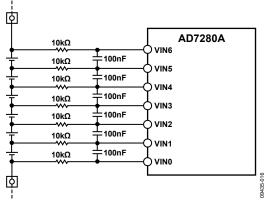

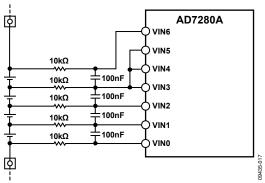

| 1, 3, 5, 7, 9,<br>11, 13 | VIN6 to VIN0     | Analog Input 6 to Analog Input 0. VIN0 should be connected to the base of the series-connected battery cells. VIN1 should be connected to the top of Cell 1, VIN2 should be connected to the top of Cell 2, and so on (see Figure 28 and Figure 29).                                                                                                                                                                                                                                                                                         |

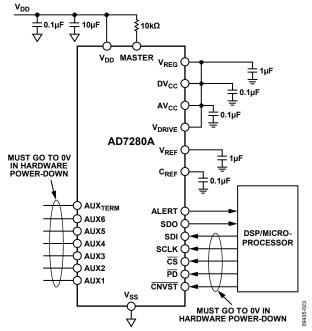

| 2, 4, 6, 8,<br>10, 12    | CB6 to CB1       | Cell Balance Output 6 to Cell Balance Output 1. These pins provide a voltage output that can be used to supply the gate drive of an external cell balancing transistor. Each CBx output provides a 0 V or 5 V voltage output referenced to the absolute amplitude of the negative terminal of the battery cell that is being balanced.                                                                                                                                                                                                       |

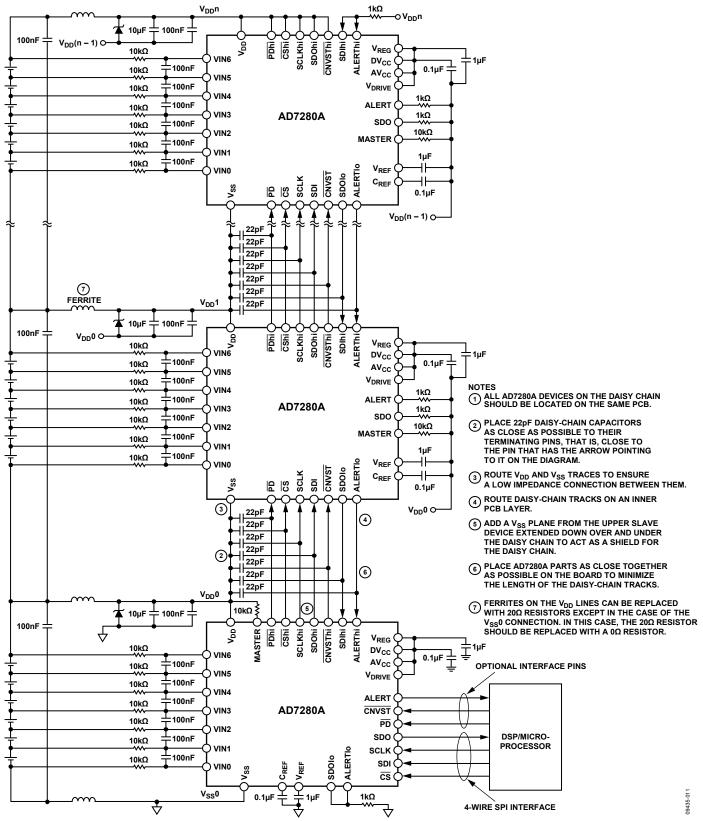

| 14                       | MASTER           | Voltage Input. Connect the MASTER pin of the AD7280A that is connected directly to the DSP/microprocessor to the $V_{DD}$ supply pin through a 10 k $\Omega$ resistor. In an application with two or more AD7280As in a daisy chain, the MASTER pins of the remaining AD7280As in the daisy chain should be tied to their respective $V_{SS}$ supply pins through 10 k $\Omega$ resistors.                                                                                                                                                   |

| 15                       | PD               | Power-Down Input. This input is used to power down the AD7280A. When the AD7280A acts as a master, the PD input is supplied from the DSP/microprocessor. When the AD7280A acts as a slave in a daisy chain, the PD input should be connected to the PDhi output of the AD7280A immediately below it in potential in the daisy chain.                                                                                                                                                                                                         |

| 16                       | V <sub>DD</sub>  | Positive Power Supply Voltage for the High Voltage Analog Input Structure of the AD7280A. The supply must be greater than the minimum voltage of 8 V. $V_{\rm DD}$ can be supplied directly from the cell with the highest potential of the four, five, or six cell battery stacks that the AD7280A is monitoring. The maximum voltage that should be applied between $V_{\rm DD}$ and $V_{\rm SS}$ is 30 V. Place 10 $\mu$ F and 100 nF decoupling capacitors on the $V_{\rm DD}$ pin.                                                      |

| 17                       | V <sub>SS</sub>  | Negative Power Supply Voltage for the High Voltage Analog Input Structure of the AD7280A. This input should be at the same potential as the AGND/DGND voltage.                                                                                                                                                                                                                                                                                                                                                                               |

| 18                       | V <sub>REG</sub> | Analog Voltage Output, 5.2 V. The internally generated $V_{REG}$ voltage, which provides the supply voltage for the ADC core, is available on this pin for use external to the AD7280A. Place 1 $\mu$ F and 100 nF decoupling capacitors on the $V_{REG}$ pin.                                                                                                                                                                                                                                                                               |

| 19                       | DVcc             | Digital Supply Voltage, 4.9 V to 5.5 V. The DV <sub>CC</sub> and AV <sub>CC</sub> voltages should ideally be at the same potential. For best performance, it is recommended that the DV <sub>CC</sub> and AV <sub>CC</sub> pins be shorted together to ensure that the voltage difference between them never exceeds 0.3 V, even on a transient basis. This supply should be decoupled to DGND. Place 100 nF decoupling capacitors on the DV <sub>CC</sub> pin. The DV <sub>CC</sub> supply pin should be connected to the $V_{REG}$ output. |

| 20                       | DGND             | Digital Ground. Ground reference point for all digital circuitry on the AD7280A. The DGND and AGND voltages should ideally be at the same potential and must not be more than 0.3 V apart, even on a transient basis.                                                                                                                                                                                                                                                                                                                        |

| Pin No.  | Mnemonic            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|----------|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 21       | <u>cs</u>           | Chip Select Input. The CS input is used to frame the input and output data on the SPI and daisy-chain interfaces. On the master AD7280A device, the CS input is supplied from the DSP/microprocessor. When the AD7280A acts as a slave in a daisy chain, this input should be connected to the CShi output of the AD7280A immediately below it in potential in the daisy chain.                                                                                                                                                                                                                               |

| 22       | SCLK                | Serial Clock Input. On the master AD7280A device, the SCLK input is supplied from the DSP/microprocessor.  When the AD7280A acts as a slave in a daisy chain, this input should be connected to the SCLKhi output of the AD7280A immediately below it in potential in the daisy chain.                                                                                                                                                                                                                                                                                                                        |

| 23       | SDI                 | Serial Data Input. Data to be written to the on-chip registers is provided on this input and is clocked into the AD7280A on the falling edge of the SCLK input. On the master AD7280A device, SDI is the data input of the SPI interface. When the AD7280A acts as a slave in a daisy chain, this input accepts data from the SDOhi output of the AD7280A immediately below it in potential in the daisy chain.                                                                                                                                                                                               |

| 24       | CNVST               | Convert Start Input. The conversion is initiated on the falling edge of CNVST. On the master AD7280A, the CNVST pulse is supplied from the DSP/microprocessor; this input can also be tied to DV <sub>CC</sub> and the conversion initiated through the serial interface. When the AD7280A acts as a slave in a daisy chain, this input should be connected to the CNVSThi output of the AD7280A immediately below it in potential in the daisy chain.                                                                                                                                                        |

| 25       | SDOlo               | Serial Data Output in Daisy-Chain Mode. On the master AD7280A device, this output should be connected to $V_{SS}$ either directly or through a pull-down, 1 k $\Omega$ resistor. When the AD7280A acts as a slave in a daisy chain, this output should be connected to the SDIhi input of the AD7280A immediately below it in potential in the daisy chain.                                                                                                                                                                                                                                                   |

| 26       | SDO                 | Serial Data Output. The conversion output data or the register output data is supplied to this pin as a serial data stream. The bits are clocked out on the rising edge of the SCLK input; 32 SCLKs are required to access the data. On the master AD7280A device, the SDO output should be connected to the DSP/microprocessor. The SDO outputs of the remaining AD7280As in the daisy chain should be connected to $V_{SS}$ either directly or through a pull-down, 1 k $\Omega$ resistor.                                                                                                                  |

| 27       | ALERT               | Digital Output. This flag indicates cell or auxiliary ADC input overvoltage or undervoltage. The ALERT output of the master AD7280A should be connected to the DSP/microprocessor. The ALERT outputs of the remaining AD7280As in the daisy chain should be connected to $V_{SS}$ either directly or through a pull-down, 1 k $\Omega$ resistor.                                                                                                                                                                                                                                                              |

| 28       | ALERTIO             | Alert Output in Daisy-Chain Mode. On the master AD7280A, this output should be connected to $V_{SS}$ either directly or through a pull-down, 1 k $\Omega$ resistor. When the AD7280A acts as a slave in a daisy chain, this output should be connected to the ALERThi input of the AD7280A immediately below it in potential in the daisy chain.                                                                                                                                                                                                                                                              |

| 29       | V <sub>DRIVE</sub>  | Logic Power Supply Input. The voltage supplied at this pin determines the voltage at which the SPI interface operates. This pin should be decoupled to DGND. On the master AD7280A device, the voltage range on this pin is 2.7 V to 5.5 V. The VDRIVE voltage can be different from the voltage at AVCC and DVCC, but it should never exceed either by more than 0.3 V. The VDRIVE pin of the remaining AD7280As in the daisy chain should be connected to VREG.                                                                                                                                             |

| 30       | AVcc                | Analog Supply Voltage for the ADC Core, $4.9 \text{ V}$ to $5.5 \text{ V}$ . The AV <sub>CC</sub> and DV <sub>CC</sub> voltages should ideally be at the same potential. For best performance, it is recommended that the AV <sub>CC</sub> and DV <sub>CC</sub> pins be shorted together to ensure that the voltage difference between them never exceeds $0.3 \text{ V}$ , even on a transient basis. This supply should be decoupled to AGND. Place $100 \text{ nF}$ decoupling capacitors on the AV <sub>CC</sub> pin. The AV <sub>CC</sub> supply pin should be connected to the V <sub>REG</sub> output. |

| 31       | AGND                | Analog Ground. This pin is the ground reference point for all analog circuitry on the AD7280A. This input should be at the same potential as the base of the series-connected battery cells. The AGND and DGND voltages should ideally be at the same potential and must not be more than 0.3 V apart, even on a transient basis.                                                                                                                                                                                                                                                                             |

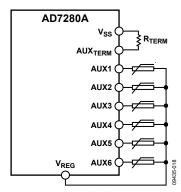

| 32       | AUX <sub>TERM</sub> | Thermistor Termination Resistor Input. If this function is not required in the application, it is recommended that this pin be connected to $V_{REG}$ through a 10 k $\Omega$ resistor.                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 33 to 38 | AUX6 to AUX1        | Auxiliary, Single-Ended 5 V ADC Inputs. If any of these inputs is not required in the application, it is recommended that the pin be connected to $V_{REG}$ through a 10 k $\Omega$ resistor.                                                                                                                                                                                                                                                                                                                                                                                                                 |

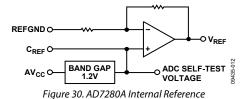

| 39       | CREF                | Reference Capacitor. A 100 nF decoupling capacitor to REFGND should be placed on this pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 40       | V <sub>REF</sub>    | Reference Output, 2.5 V. The on-chip reference is available on this pin for use external to the AD7280A. A 1 $\mu$ F decoupling capacitor to REFGND is recommended on this pin.                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 41       | REFGND              | Reference Ground. This pin is the ground reference point for the internal band gap reference circuitry on the AD7280A. The REFGND voltage should be at the same potential as the AGND voltage.                                                                                                                                                                                                                                                                                                                                                                                                                |

| 42       | ALERThi             | Alert Input in Daisy-Chain Mode. The alert signal from each AD7280A in the daisy chain is passed through the ALERTIo output and the ALERThi input of each AD7280A in the chain and is supplied to the DSP/micro-processor through the ALERT output of the master AD7280A. This input should be connected to the ALERTIo output of the AD7280A immediately above it in potential in the daisy chain. The AD7280A at the highest potential in the stack does not require an alert input; in this case, the pin should be connected to $V_{\text{DD}}$ through a 1 k $\Omega$ resistor.                          |

| Pin No. | Mnemonic | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|---------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 43      | SDIhi    | Serial Data Input in Daisy-Chain Mode. The data from each AD7280A in the daisy chain is passed through the SDOlo output and the SDIhi input of each AD7280A in the chain and is supplied to the DSP/microprocessor through the SDO output of the master AD7280A. This input should be connected to the SDOlo output of the AD7280A immediately above it in potential in the daisy chain. The AD7280A at the highest potential in the stack does not require a serial data input in daisy-chain mode; in this case, the pin should be connected to $V_{\text{DD}}$ through a 1 k $\Omega$ resistor.             |

| 44      | CNVSThi  | Conversion Start Output in Daisy-Chain Mode. The convert start signal from the DSP/microprocessor supplied to the $\overline{\text{CNVST}}$ input of the master AD7280A is passed through each AD7280A by means of the $\overline{\text{CNVST}}$ input and the $\overline{\text{CNVSThi}}$ output. This output should be connected to the $\overline{\text{CNVST}}$ pin of the AD7280A immediately above it in potential in the daisy chain. The AD7280A at the highest potential in the stack does not require a daisy-chain conversion start output; in this case, the pin should be connected to $V_{DD}$ . |

| 45      | SDOhi    | Serial Data Output in Daisy-Chain Mode. The serial data input from the DSP/microprocessor supplied to the SDI input of the master AD7280A is passed through each AD7280A by means of the SDI input and the SDOhi output. This output should be connected to the SDI input of the AD7280A immediately above it in potential in the daisy chain. The AD7280A at the highest potential in the stack does not require a daisy-chain serial data output; in this case, the pin should be connected to $V_{\rm DD}$ .                                                                                                |

| 46      | SCLKhi   | Serial Clock Output in Daisy-Chain Mode. The clock signal from the DSP/microprocessor supplied to the SCLK input of the master AD7280A is passed through each AD7280A by means of the SCLK input and the SCLKhi output. This output should be connected to the SCLK input of the AD7280A immediately above it in potential in the daisy chain. The AD7280A at the highest potential in the stack does not require a daisy-chain serial clock output; in this case, the pin should be connected to V <sub>DD</sub> .                                                                                            |

| 47      | CShi     | Chip Select Output in Daisy-Chain Mode. The chip select signal from the DSP/microprocessor supplied to the CS input of the master AD7280A is passed through each AD7280A by means of the CS input and the CShi output. This output should be connected to the CS input of the AD7280A immediately above it in potential in the daisy chain. The AD7280A at the highest potential in the stack does not require a daisy-chain chip select output; in this case, the pin should be connected to V <sub>DD</sub> .                                                                                                |

| 48      | PDhi     | Power-Down Output in Daisy-Chain Mode. The power-down signal from the DSP/microprocessor supplied to the PD input of the master AD7280A is passed through each AD7280A by means of the PD input and the PDhi output. This output should be connected to the PD input of the AD7280A immediately above it in potential in the daisy chain. The AD7280A at the highest potential in the stack does not require a daisy-chain power-down output; in this case, the pin should be connected to V <sub>DD</sub> .                                                                                                   |

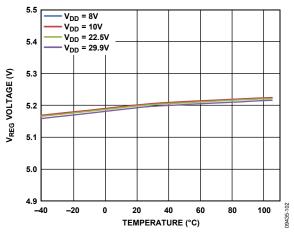

## TYPICAL PERFORMANCE CHARACTERISTICS

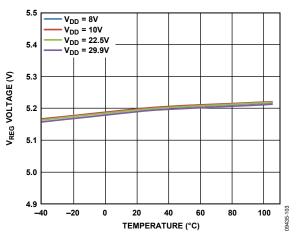

Figure 4.  $V_{REG}$  vs. Temperature for Different Supply Voltages,  $V_{REG}$  Connected to  $AV_{CC}$  and  $DV_{CC}$

Figure 5.  $V_{REG}$  vs. Temperature for Different Supply Voltages,  $V_{REG}$  Connected to  $AV_{CC}$  and  $DV_{CG}$ , 5 mA External Load

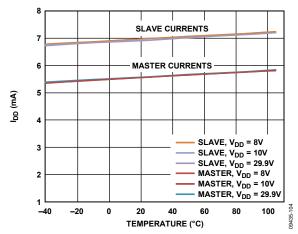

Figure 6. IDD During Conversion vs. Temperature for Different Supply Voltages

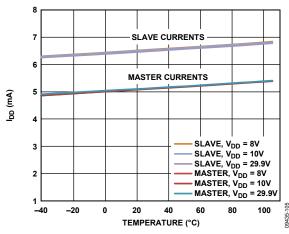

Figure 7. IDD During Cell Balancing vs. Temperature for Different Supply Voltages

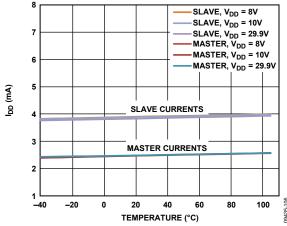

Figure 8. I<sub>DD</sub> During Software Power-Down vs. Temperature for Different Supply Voltages

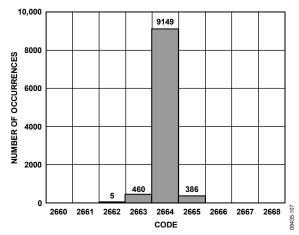

Figure 9. Histogram of Codes for 10,000 Samples, Odd Cell Voltage Channels

Figure 10. Histogram of Codes for 10,000 Samples, Even Cell Voltage Channels

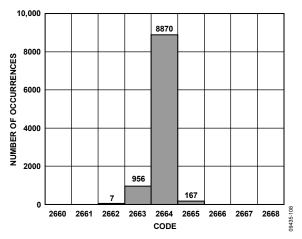

Figure 11. Histogram of Codes for 10,000 Samples, Auxiliary Channels

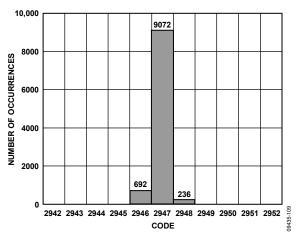

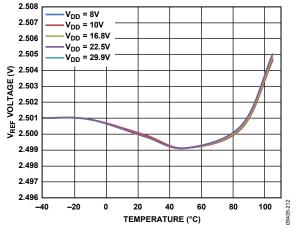

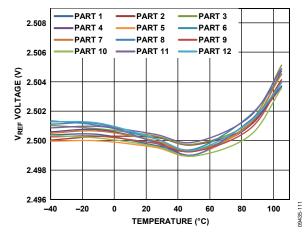

Figure 12. V<sub>REF</sub> vs. Temperature for Different Supply Voltages

Figure 13.  $V_{REF}$  vs. Temperature for Different Parts

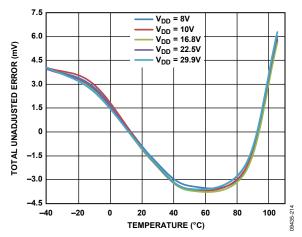

Figure 14. Total Unadjusted Error for Even Cell Voltage Channels (Absolute Value) vs. Temperature for Different Supply Voltages

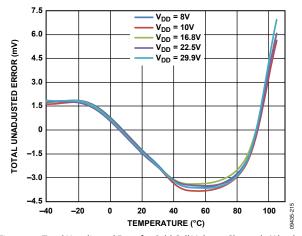

Figure 15. Total Unadjusted Error for Odd Cell Voltage Channels (Absolute Value) vs. Temperature for Different Supply Voltages

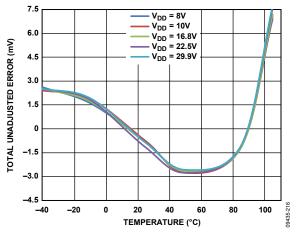

Figure 16. Total Unadjusted Error for Auxiliary Channels (Absolute Value) vs. Temperature for Different Supply Voltages

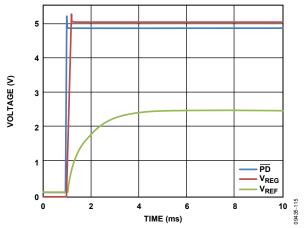

Figure 17. Power-Up Time, 1  $\mu$ F Capacitor on the  $V_{REF}$  and  $V_{REG}$  Pins

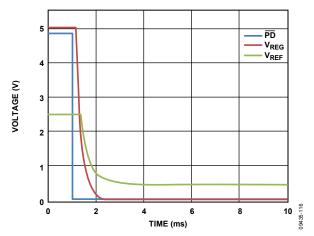

Figure 18. Power-Down Time, 1  $\mu$ F Capacitor on the  $V_{\text{REF}}$  and  $V_{\text{REG}}$  Pins

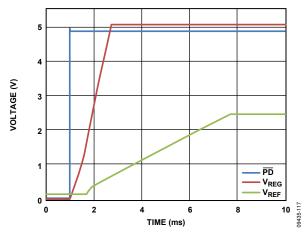

Figure 19. Power-Up Time, 10  $\mu$ F Capacitor on the  $V_{REF}$  and  $V_{REG}$  Pins

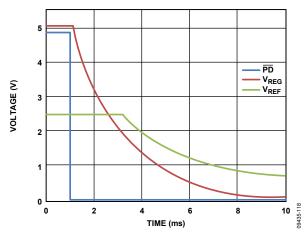

Figure 20. Power-Down Time, 10  $\mu$ F Capacitor on the  $V_{REF}$  and  $V_{REG}$  Pins

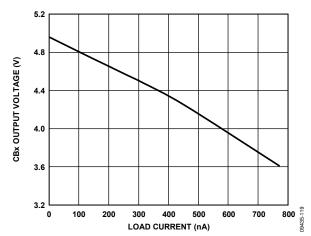

Figure 21. CBx Output Voltage vs. Load Current

### **TERMINOLOGY**

#### Differential Nonlinearity (DNL)

DNL is the difference between the measured and the ideal 1 LSB change between any two adjacent codes in the ADC.

#### Integral Nonlinearity (INL)

INL is the maximum deviation from a straight line passing through the endpoints of the ADC transfer function. The endpoints of the transfer function are zero scale (a point 1 LSB below the first code transition) and full scale (a point 1 LSB above the last code transition).

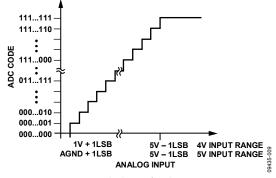

#### Offset Error

Offset error applies to straight binary output coding. It is the deviation of the first code transition (000 ... 000) to (000 ... 001) from the ideal, that is, AGND + 1 LSB for AUX1 to AUX6 and 1 V + AGND + 1 LSB for VIN0 to VIN6.

#### **Offset Error Match**

Offset error match is the difference in zero code error across all six channels.

#### **Gain Error**

Gain error applies to straight binary output coding. It is the deviation of the last code transition (111 ... 110) to (111 ... 111) from the ideal (that is,  $2 \times V_{REF} - 1$  LSB) after adjusting for the offset error.

#### **Gain Error Match**

Gain error match is the difference in gain error across all six channels.

#### **ADC Unadjusted Error**

ADC unadjusted error includes the INL error and the offset and gain errors of the ADC and measurement channel.

#### **Total Unadjusted Error (TUE)**

TUE is the maximum deviation of the output code from the ideal. Total unadjusted error includes the INL error, the offset and gain errors, and the reference errors. Reference errors include the difference between the actual and ideal reference voltage (that is, 2.5 V) and the reference voltage temperature coefficient.

### Reference Voltage Temperature Coefficient

The reference voltage temperature coefficient is derived from the maximum and minimum reference output voltage ( $V_{\text{REF}}$ ) measured between  $T_{\text{MIN}}$  and  $T_{\text{MAX}}$ . It is expressed in ppm/°C using the following equation:

$$TCV_{REF}(\text{ppm/}^{\circ}\text{C}) = \left(\frac{V_{REF}(Max) - V_{REF}(Min)}{2.5 \text{ V} \times (T_{MAX} - T_{MIN})}\right) \times 10^{6}$$

where:

$V_{REF}(Max)$  is the maximum  $V_{REF}$  between  $T_{MIN}$  and  $T_{MAX}$ .  $V_{REF}(Min)$  is the minimum  $V_{REF}$  between  $T_{MIN}$  and  $T_{MAX}$ .  $T_{MAX} = +85$ °C or +105°C.

$T_{MIN} = -40$ °C.

#### **Output Voltage Hysteresis**

Output voltage hysteresis, or thermal hysteresis, is defined as the absolute maximum change of reference output voltage after the device is cycled through temperature from either T\_HYS+ or T\_HYS-, where:

$$T_{HYS+} = +25^{\circ}\text{C}$$

to  $T_{MAX}$  to  $+25^{\circ}\text{C}$

$T_{HYS-} = +25^{\circ}\text{C}$  to  $T_{MIN}$  to  $+25^{\circ}\text{C}$

Output voltage hysteresis is expressed in ppm using the following equation:

$$V_{HYS}(\text{ppm}) = \left(\frac{V_{REF}(25^{\circ}\text{C}) - V_{REF}(T_{HYS})}{V_{REF}(25^{\circ}\text{C})}\right) \times 10^{6}$$

where:

$V_{REF}(25^{\circ}\text{C}) = V_{REF} \text{ at } 25^{\circ}\text{C}.$

$V_{REF}(T\_HYS)$  is the maximum change of  $V_{REF}$  at  $T\_HYS+$  or  $T\_HYS-$ .

#### Static Leakage Current

Static leakage current is the current measured on the cell voltage and/or the auxiliary ADC inputs when the device is static, that is, not converting.

#### **Dynamic Leakage Current**

Dynamic leakage current is the current measured on the cell voltage and/or the auxiliary ADC inputs when the device is converting, with the static leakage current subtracted. Dynamic leakage current is specified with a convert start pulse frequency of 10 Hz, that is, every 100 ms. The dynamic leakage current for a different conversion rate can be calculated using the following equation:

$$I_{DYN(B)} = \left(\frac{I_{DYN(A)} \times f_{CNVST(B)}}{f_{CNVST(A)}}\right)$$

where:

$I_{DYN(A)}$  is the dynamic leakage current at the convert start frequency,  $f_{CNVST(A)}$  (see Table 1).

$I_{DYN(B)}$  is the dynamic leakage current at the desired convert start frequency,  $f_{CNVST(B)}$ .

# THEORY OF OPERATION CIRCUIT INFORMATION

The AD7280A is a lithium ion (Li-Ion) battery monitoring chip that can monitor the voltage and temperature of four, five, or six series-connected Li-Ion battery cells. The AD7280A also provides an interface that can be used to control external transistors for cell balancing.

The  $V_{\text{DD}}$  and  $V_{\text{SS}}$  supplies required by the AD7280A should be taken from battery cells being monitored by the part. An internal  $V_{\text{REG}}$  rail is generated to provide power for the ADC and the internal interface circuitry. This  $V_{\text{REG}}$  voltage is available on an output pin for use external to the AD7280A.

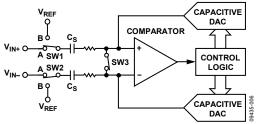

The AD7280A consists of a high voltage input multiplexer, a low voltage input multiplexer, and a SAR ADC. The high voltage multiplexer allows four, five, or six series-connected Li-Ion battery cells to be measured. The low voltage multiplexer provides the user with six single-ended ADC inputs that can be used in combination with external thermistors to measure the temperature of each battery cell. The auxiliary ADC inputs can also be used for external diagnostics in the application. Initiating conversions on all 12 channels, that is, the six cell voltage channels and the six auxiliary ADC channels, requires only a single  $\overline{\text{CNVST}}$  pulse. Alternatively, the conversion can be initiated through the rising edge of  $\overline{\text{CS}}$ . Each conversion result is stored in an individual result register (see Table 13).

Each individual cell voltage and auxiliary ADC measurement requires a minimum of 1  $\mu s$  to acquire and complete a conversion. Depending on the external components connected to the analog inputs of the AD7280A, additional acquisition time may be required. A higher acquisition time can be selected through the control register. The AD7280A also provides a conversion averaging option that can be selected through the control register. This option allows the user to complete two, four, or eight averages on each cell voltage and auxiliary ADC measurement. The averaged conversion results are stored in the result registers. On power-up, the default combined acquisition and conversion time is 1  $\mu s$ , with the averaging register set to 0, that is, a single conversion per channel.

The results of the cell voltage and auxiliary ADC conversions are read back via the 4-wire serial peripheral interface (SPI). The SPI is also used to write to and read from the internal registers.

The AD7280A features an alert function that can be triggered if the voltage conversion results or the auxiliary ADC conversion results exceed the maximum and minimum voltage thresholds selected by the user. The alert modes and threshold levels are selected by writing to internal registers.

The AD7280A provides six analog output voltages that can be used to control external transistors as part of a cell balancing circuit. Each cell balance output provides a 0 V or 5 V voltage, with respect to the potential on the base of each individual cell, that can be applied to the gate of the external cell balancing transistors.

The AD7280A features a daisy-chain interface. Individual AD7280A devices can monitor the cell voltages and temperatures of six cells. A chain of AD7280As can be used to monitor the cell voltages and temperatures of a larger number of cells. The conversion data from each AD7280A in the chain passes to the system controller via a single SPI interface. Control data can similarly be passed via the SPI up the chain to each individual AD7280A

The AD7280A includes an on-chip 2.5 V reference. The reference voltage is available for use external to the AD7280A.

The AD7280A also has a  $V_{DRIVE}$  feature to control the voltage at which the serial interface operates.  $V_{DRIVE}$  allows the ADC to easily interface to both 3 V and 5 V processors. For example, in the recommended configuration, the AD7280A is operated with a supply of 5 V; however, the  $V_{DRIVE}$  pin can be powered from a 3 V supply, allowing a large dynamic range with low voltage digital processors.

#### **CONVERTER OPERATION**

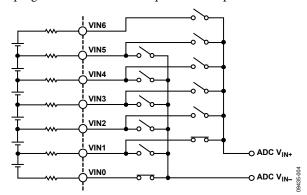

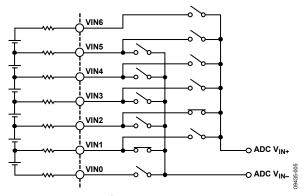

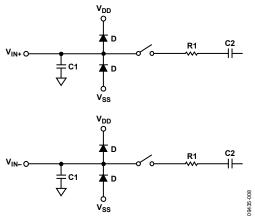

The conversion paths of the AD7280A consist of a high voltage input multiplexer or a low voltage input multiplexer and a SAR ADC. The high voltage multiplexer selects the pair of analog inputs, VIN0 to VIN6, that is to be converted. The voltage of each individual cell is measured by converting the difference between adjacent analog inputs, that is, VIN1 – VIN0, VIN2 – VIN1, and so on (see Figure 22 and Figure 23). The low voltage multiplexer selects the auxiliary ADC input, AUX1 to AUX6, that is to be converted. The conversion results for each cell voltage and auxiliary ADC input can be accessed t<sub>WAIT</sub> after the programmed conversion sequence is completed.

Figure 22. Mux Configuration During VIN1 to VIN0 Sampling

Figure 23. Mux Configuration During VIN2 to VIN1 Sampling