# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# 16-Bit, Isolated Sigma-Delta Modulator

### **Enhanced Product**

# AD7403-EP

#### **FEATURES**

5 MHz to 16 MHz external clock input rate 16 bits, no missing codes Signal-to-noise ratio (SNR): 88 dB typical Effective number of bits (ENOB): 14.2 bits typical Offset drift vs. temperature: 1.6 μV/°C typical On-board digital isolator On-board reference Full-scale analog input range: ±320 mV High common-mode transient immunity: >25 kV/μs Wide-body SOIC with increased creepage package Slew rate limited output for low EMI

#### Safety and regulatory approvals

UL recognition 5000 V rms for 1 minute per UL 1577 CSA Component Acceptance Notice 5A VDE Certificate of Conformity DIN V VDE V 0884-10 (VDE V 0884-10):2006-12 VIORM = 1250 VPEAK

#### ENHANCED PRODUCT FEATURES

Defense and aerospace applications (AQEC standard) Military temperature range: -55°C to +125°C Controlled manufacturing baseline One assembly/test site One fabrication site Enhanced product change notification Qualification data available on request

#### **APPLICATIONS**

Shunt current monitoring AC motor controls Power and solar inverters Wind turbine inverters Data acquisition systems Analog-to-digital and optoisolator replacements

#### **GENERAL DESCRIPTION**

The AD7403-EP<sup>1</sup> is a high performance, second-order,  $\Sigma$ - $\Delta$  modulator that converts an analog input signal into a high speed, single-bit data stream, with on-chip digital isolation based on Analog Devices, Inc., *i*Coupler<sup>\*</sup> technology. The device operates from a 5 V (V<sub>DD1</sub>) power supply and accepts a differential input signal of ±250 mV (±320 mV full-scale). The differential input is ideally suited to shunt voltage monitoring in high voltage applications where galvanic isolation is required.

<sup>1</sup> Protected by U.S. Patents 5,952,849; 6,873,065; and 7,075,329.

Rev. 0

Document Feedback

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

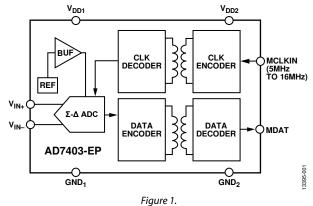

#### FUNCTIONAL BLOCK DIAGRAM

The analog input is continuously sampled by a high performance analog modulator, and converted to a ones density digital output stream with a data rate of up to 16 MHz. The original

information can be reconstructed with an appropriate digital filter to achieve 88 dB signal to noise ratio (SNR) at 78.1 kSPS.

The serial interface is digitally isolated. High speed complementary metal oxide semiconductor (CMOS) technology, combined with monolithic transformer technology, means the on-chip isolation provides outstanding performance characteristics, superior to alternatives such as optocoupler devices. The AD7403-EP device is offered in a 16-lead, wide-body SOIC package and has an operating temperature range of  $-55^{\circ}$ C to  $+125^{\circ}$ C.

Additional application and technical information can be found in the AD7403 data sheet.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781.329.4700 ©2016 Analog Devices, Inc. All rights reserved. Technical Support www.analog.com

# TABLE OF CONTENTS

| Features                                      |

|-----------------------------------------------|

| Enhanced Product Features1                    |

| Applications1                                 |

| General Description1                          |

| Functional Block Diagram1                     |

| Revision History                              |

| Specifications                                |

| Timing Specifications4                        |

| Package Characteristics 5                     |

| Insulation and Safety Related Specifications5 |

| Regulatory Information                        |

| DIN V VDE V 0884-10 (VDE V 0884-10):2006-12 Insulation |

|--------------------------------------------------------|

| Characteristics                                        |

| Absolute Maximum Ratings7                              |

| ESD Caution7                                           |

| Pin Configurations and Function Descriptions           |

| Typical Performance Characteristics9                   |

| Outline Dimensions                                     |

| Ordering Guide 12                                      |

#### **REVISION HISTORY**

4/16—Revision 0: Initial Version

### **SPECIFICATIONS**

$V_{\rm DD1} = 4.5 \ V \ to \ 5.5 \ V, \\ V_{\rm DD2} = 4.5 \ V \ to \ 5.5 \ V, \\ V_{\rm IN+} = -250 \ mV \ to \ +250 \ mV, \\ V_{\rm IN-} = 0 \ V, \\ T_{\rm A} = -55^{\circ}C \ to \ +125^{\circ}C, \\ f_{\rm MCLKIN} = 5 \ MHz \ to \ 16 \ MHz, \ tested \ NHz \ to \ 16 \ MHz, \ tested \ NHz \ to \ 16 \ MHz, \ tested \ NHz \ to \ 16 \ MHz, \ tested \ NHz \ to \ 16 \ MHz, \ tested \ NHz \ to \ 16 \ MHz, \ tested \ NHz \ to \ 16 \ MHz, \ tested \ NHz \ to \ 16 \ MHz, \ tested \ NHz \ to \ 16 \ MHz, \ tested \ NHz \ to \ 16 \ MHz, \ tested \ NHz \ to \ 16 \ MHz, \ tested \ NHz \ to \ 16 \ MHz, \ tested \ NHz \ to \ 16 \ MHz, \ tested \ NHz \ to \ 16 \ MHz, \ tested \ NHz \ to \ 16 \ MHz, \ tested \ NHz \ to \ 16 \ MHz, \ tested \ NHz \ to \ 16 \ MHz, \ tested \ NHz \ to \ 16 \ MHz, \ tested \ NHz \ to \ 16 \ MHz, \ tested \ NHz \ to \ 16 \ NHz \ to \ 16 \ NHz \ to \ 16 \ NHz, \ tested \ NHz \ to \ 16 \ NHz \ t$ with sinc3 filter, 256 decimation rate, as defined by Verilog code, unless otherwise noted. All voltages are relative to their respective ground.

| Table 1.                                                      |                        |              |                      |            |                                                       |

|---------------------------------------------------------------|------------------------|--------------|----------------------|------------|-------------------------------------------------------|

| Parameter                                                     | Min                    | Тур          | Max                  | Unit       | Test Conditions/Comments                              |

| STATIC PERFORMANCE                                            |                        |              |                      |            |                                                       |

| Resolution                                                    | 16                     |              |                      | Bits       | Filter output truncated to 16 bits                    |

| Integral Nonlinearity (INL) <sup>1</sup>                      |                        | ±2           | ±12                  | LSB        |                                                       |

| Differential Nonlinearity (DNL) <sup>1</sup>                  |                        |              | ±0.99                | LSB        | Guaranteed no missed codes to 16 bits                 |

| Offset Error <sup>1</sup>                                     |                        | ±0.2         | ±0.9                 | mV         |                                                       |

| Offset Drift vs. Temperature <sup>2</sup>                     |                        | 1.6          | 3.8                  | μV/°C      |                                                       |

| ·                                                             |                        | 1.3          | 3.1                  | '<br>μV/°C | 0°C to 85°C                                           |

| Offset Drift vs. V <sub>DD1</sub> <sup>2</sup>                |                        | 50           |                      | μV/V       |                                                       |

| Gain Error <sup>1</sup>                                       |                        | ±0.2         | ±0.95                | % FSR      |                                                       |

| Gain Error Drift vs. Temperature <sup>2</sup>                 |                        | 65           | 95                   | ppm/°C     |                                                       |

|                                                               |                        | 40           | 60                   | μV/°C      |                                                       |

| Gain Error Drift vs. $V_{DD1}^2$                              |                        | ±0.6         |                      | mV/V       |                                                       |

| ANALOG INPUT                                                  |                        |              |                      |            |                                                       |

| Input Voltage Range                                           | -320                   |              | +320                 | mV         | Full-scale range                                      |

|                                                               | -250                   |              | +250                 | mV         | For specified performance                             |

| Input Common-Mode Voltage Range                               |                        | -200 to +300 |                      | mV         |                                                       |

| Dynamic Input Current                                         |                        | ±45          | ±50                  | μA         | $V_{IN+} = \pm 250 \text{ mV}, V_{IN-} = 0 \text{ V}$ |

|                                                               |                        | 0.05         | _00                  | μΑ         | $V_{IN+} = 0 V, V_{IN-} = 0 V$                        |

| DC Leakage Current                                            |                        | ±0.01        | ±0.6                 | μΑ         |                                                       |

| Input Capacitance                                             |                        | 14           | ±0.0                 | рF         |                                                       |

| DYNAMIC SPECIFICATIONS <sup>1</sup>                           |                        | 17           |                      | μ          | $V_{\rm IN+} = 1 \rm kHz$                             |

| Signal-to-Noise-and-Distortion Ratio (SINAD)                  | 82                     | 87           |                      | dB         |                                                       |

| Signal-to-Noise Ratio (SNR)                                   | 86                     | 88           |                      | dB         |                                                       |

| Total Harmonic Distortion (THD)                               | 00                     | 00<br>-94    |                      | dB         |                                                       |

|                                                               |                        | -94<br>-95   |                      | dB         |                                                       |

| Peak Harmonic or Spurious Noise (SFDR)                        | 12.1                   |              |                      |            |                                                       |

| Effective Number of Bits (ENOB)<br>Noise Free Code Resolution | 13.1                   | 14.2         |                      | Bits       |                                                       |

|                                                               | 14                     | 20           |                      | Bits       |                                                       |

| ISOLATION TRANSIENT IMMUNITY <sup>1</sup>                     | 25                     | 30           |                      | kV/μs      |                                                       |

| LOGIC INPUTS                                                  |                        |              |                      |            | CMOS with Schmitt trigger                             |

| Input Voltage                                                 |                        |              |                      |            |                                                       |

| High (V⊩)                                                     | $0.8 \times V_{DD2}$   |              |                      | V          |                                                       |

| Low (V <sub>IL</sub> )                                        |                        |              | $0.2 \times V_{DD2}$ | V          |                                                       |

| Input Current (I <sub>IN</sub> )                              |                        |              | ±0.6                 | μA         |                                                       |

| Input Capacitance (C <sub>IN</sub> )                          |                        |              | 10                   | pF         |                                                       |

| LOGIC OUTPUTS                                                 |                        |              |                      |            |                                                       |

| Output Voltage                                                |                        |              |                      |            |                                                       |

| High (V <sub>он</sub> )                                       | V <sub>DD2</sub> - 0.1 |              |                      | V          | $I_0 = -200 \ \mu A$                                  |

| Low (V <sub>OL</sub> )                                        |                        |              | 0.4                  | V          | $I_0 = 200 \ \mu A$                                   |

| POWER REQUIREMENTS                                            |                        |              |                      |            |                                                       |

| V <sub>DD1</sub>                                              | 4.5                    |              | 5.5                  | V          |                                                       |

| V <sub>DD2</sub>                                              | 4.5                    |              | 5.5                  | V          |                                                       |

| IDD1                                                          |                        | 30           | 36                   | mA         | $V_{DD1} = 5.5 V$                                     |

| I <sub>DD2</sub>                                              |                        | 12           | 18                   | mA         | $V_{DD2} = 5.5 V$                                     |

| Power Dissipation                                             | 1                      | 231          | 297                  | mW         | $V_{DD1} = V_{DD2} = 5.5 V$                           |

<sup>1</sup> See the Terminology section of the AD7403 datasheet.

<sup>2</sup> Not production tested. Sample tested during initial release to ensure compliance.

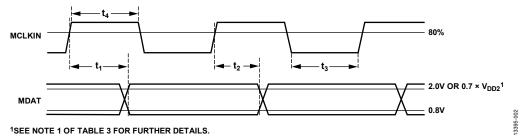

#### TIMING SPECIFICATIONS

$V_{DD1} = 4.5 V$  to 5.5 V,  $V_{DD2} = 4.5 V$  to 5.5 V,  $T_A = -55^{\circ}C$  to  $+125^{\circ}C$ , unless otherwise noted. Sample tested during initial release to ensure compliance. It is recommended to read MDAT on the MCLKIN rising edge.

#### Table 2.

|                     | Limit a                        | Limit at T <sub>MIN</sub> , T <sub>MAX</sub> |     |      |                                           |

|---------------------|--------------------------------|----------------------------------------------|-----|------|-------------------------------------------|

| Parameter           | Min                            | Тур                                          | Max | Unit | Description                               |

| f <sub>MCLKIN</sub> | 5                              |                                              | 16  | MHz  | Master clock input frequency              |

| $t_1^1$             |                                |                                              | 45  | ns   | Data access time after MCLKIN rising edge |

| $t_2^1$             | 12                             |                                              |     | ns   | Data hold time after MCLKIN rising edge   |

| t <sub>3</sub>      | $0.45 	imes t_{\text{MCLKIN}}$ |                                              |     | ns   | Master clock low time                     |

| t4                  | $0.45 	imes t_{\text{MCLKIN}}$ |                                              |     | ns   | Master clock high time                    |

<sup>1</sup> Defined as the time required from an 80% MCLKIN input level to when the output crosses 0.8 V or 2.0 V for  $V_{DD2} = 3$  V to 3.6 V or when the output crosses 0.8 V or 0.7 ×  $V_{DD2}$  for  $V_{DD2} = 4.5$  V to 5.5 V as outlined in Figure 2. Measured with a ±200  $\mu$ A load and a 25 pF load capacitance.

Figure 2. Data Timing

#### **PACKAGE CHARACTERISTICS**

#### Table 3.

| Parameter                                  | Symbol           | Min | Тур              | Max | Unit | Test Conditions/Comments                                                                              |

|--------------------------------------------|------------------|-----|------------------|-----|------|-------------------------------------------------------------------------------------------------------|

| Resistance (Input to Output) <sup>1</sup>  | R <sub>I-O</sub> |     | 10 <sup>12</sup> |     | Ω    |                                                                                                       |

| Capacitance (Input to Output) <sup>1</sup> | CI-O             |     | 2.2              |     | pF   | f = 1 MHz                                                                                             |

| IC Junction to Ambient Thermal Resistance  | ALθ              |     | 45               |     | °C/W | Thermocouple located at center of package underside, test conducted on 4-layer board with thin traces |

<sup>1</sup> The device is considered a 2-terminal device. For AD7403-EP, Pin 1 to Pin 8 are shorted together and Pin 9 to Pin 16 are shorted together.

#### INSULATION AND SAFETY RELATED SPECIFICATIONS

#### Table 4.

| Parameter                                        | Symbol | Value                   | Unit | Test Conditions/Comments                                                             |

|--------------------------------------------------|--------|-------------------------|------|--------------------------------------------------------------------------------------|

| Input to Output Momentary Withstand Voltage      | VISO   | 5000 min                | V    | 1 minute duration                                                                    |

| Minimum External Air Gap (Clearance)             | L(I01) | 8.3 min <sup>1, 2</sup> | mm   | Measured from input terminals to output terminals, shortest distance through air     |

| Minimum External Tracking (Creepage)             | L(102) | 8.3 min <sup>1</sup>    | mm   | Measured from input terminals to output terminals, shortest distance path along body |

| Minimum Internal Gap (Internal Clearance)        |        | 0.034 min               | mm   | Distance through insulation                                                          |

| Tracking Resistance (Comparative Tracking Index) | СТІ    | >400                    | V    | DIN IEC 112/VDE 0303 Part 1 <sup>3</sup>                                             |

| Isolation Group                                  |        | П                       |      | Material Group (DIN VDE 0110, 1/89, Table I) <sup>3</sup>                            |

<sup>1</sup> In accordance with IEC 60950-1 guidelines for the measurement of creepage and clearance distances for a pollution degree of 2 and altitudes <2000 m.

<sup>2</sup> Consideration must be given to pad layout to ensure the minimum required distance for clearance is maintained. <sup>3</sup> CSA CTI rating for the AD7403-EP is >575 V and therefore Material Group II isolation group.

#### **REGULATORY INFORMATION**

#### Table 5.

| UL <sup>1</sup>                                                        | CSA                                                                                                                                                                                                                                                                          | VDE <sup>2</sup>                                                                                 |

|------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|

| Recognized under 1577<br>Component Recognition<br>Program <sup>1</sup> | Approved under CSA Component Acceptance Notice 5A                                                                                                                                                                                                                            | Certified according to DIN V VDE V 0884-10<br>(VDE V 0884-10):2006-12 <sup>2</sup>               |

| 5000 V rms Isolation Voltage<br>Single Protection                      | Basic insulation per CSA 60950-1-07 and IEC 60950-1,<br>830 V rms (1173 V <sub>PEAK</sub> ), maximum working voltage <sup>3</sup><br>Reinforced insulation per CSA 60950-1-07 and<br>IEC 60950-1. 415 V rms (586 V <sub>PEAK</sub> ) maximum working<br>voltage <sup>3</sup> | Reinforced insulation per DIN V VDE V 0884-10<br>(VDE V 0884-10):2006-12, 1250 V <sub>PEAK</sub> |

|                                                                        | Reinforced insulation per IEC 60601-1, 250 V rms<br>(353 V <sub>PEAK</sub> ) maximum working voltage                                                                                                                                                                         |                                                                                                  |

| File E214100                                                           | File 205078                                                                                                                                                                                                                                                                  | File 2471900-4880-0001                                                                           |

<sup>1</sup> In accordance with UL 1577, each AD7403-EP is proof tested by applying an insulation test voltage  $\geq$  6000 V rms for 1 second (current leakage detection limit = 15  $\mu$ A).

<sup>2</sup> In accordance with DIN V VDE V 0884-10, each AD7403-EP is proof tested by applying an insulation test voltage ≥ 2344 V<sub>FEAK</sub> for 1 second (partial discharge detection limit = 5 pC). <sup>3</sup> Rating is calculated for a pollution degree of 2 and a Material Group III. The AD7403-EP RI-16-2 package material is rated by CSA to a CTI of >575 V and therefore Material Group II.

#### DIN V VDE V 0884-10 (VDE V 0884-10):2006-12 INSULATION CHARACTERISTICS

This isolator is suitable for reinforced electrical isolation only within the safety limit data. Maintenance of the safety data is ensured by means of protective circuits.

| Table 6.                                                                                            | 1                  |                |       |

|-----------------------------------------------------------------------------------------------------|--------------------|----------------|-------|

| Description                                                                                         | Symbol             | Characteristic | Unit  |

| INSTALLATION CLASSIFICATION PER DIN VDE 0110                                                        |                    |                |       |

| For Rated Mains Voltage ≤300 V rms                                                                  |                    | I to IV        |       |

| For Rated Mains Voltage ≤450 V rms                                                                  |                    | I to IV        |       |

| For Rated Mains Voltage ≤600 V rms                                                                  |                    | l to IV        |       |

| For Rated Mains Voltage ≤1000 V rms                                                                 |                    | l to IV        |       |

| CLIMATIC CLASSIFICATION                                                                             |                    | 40/105/21      |       |

| POLLUTION DEGREE (DIN VDE 0110, TABLE 1)                                                            |                    | 2              |       |

| MAXIMUM WORKING INSULATION VOLTAGE                                                                  | VIORM              | 1250           | VPEAK |

| INPUT TO OUTPUT TEST VOLTAGE, METHOD B1                                                             |                    |                |       |

| $V_{IORM} \times 1.875 = V_{PR}$ , 100% Production Test, $t_m = 1$ Second, Partial Discharge < 5 pC | V <sub>PD(M)</sub> | 2344           | VPEAK |

| INPUT TO OUTPUT TEST VOLTAGE, METHOD A                                                              | V <sub>PR(M)</sub> |                |       |

| After Environmental Test Subgroup 1                                                                 |                    |                |       |

| $V_{IORM} \times 1.6 = V_{PR}$ , $t_m = 60$ Seconds, Partial Discharge < 5 pC                       |                    | 2000           | VPEAK |

| After Input and/or Safety Test Subgroup 2/ Safety Test Subgroup 3                                   |                    |                |       |

| $V_{IORM} \times 1.2 = V_{PR}$ , $t_m = 60$ Seconds, Partial Discharge < 5 pC                       |                    | 1500           | VPEAK |

| HIGHEST ALLOWABLE OVERVOLTAGE (TRANSIENT OVERVOLTAGE, $t_{TR} = 10$ Seconds)                        | VIOTM              | 8000           | VPEAK |

| SURGE ISOLATION VOLTAGE                                                                             | VIOSM              |                | VPEAK |

| 1.2 μs Rise Time, 50 μs, 50% Fall Time                                                              |                    | 7500           | VPEAK |

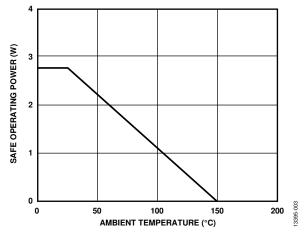

| SAFETY LIMITING VALUES (MAXIMUM VALUE ALLOWED IN THE EVENT OF A FAILURE, SEE Figure 3)              |                    |                |       |

| Case Temperature                                                                                    | Ts                 | 150            | °C    |

| Side 1 (Pvdd1) and Side 2 (Pvdd2) Power Dissipation                                                 | Pso                | 2.78           | W     |

| INSULATION RESISTANCE AT $T_{s_r} V_{IO} = 500 V$                                                   | R <sub>IO</sub>    | >109           | Ω     |

Figure 3. Thermal Derating Curve, Dependence of Safety Limiting Values with Case Temperature per DIN V VDE V 0884-10

# **ABSOLUTE MAXIMUM RATINGS**

$T_A = 25^{\circ}$ C, unless otherwise noted. All voltages are relative to their respective ground.

#### Table 7.

| Parameter                                             | Rating                                |

|-------------------------------------------------------|---------------------------------------|

| V <sub>DD1</sub> to GND <sub>1</sub>                  | –0.3 V to +6.5 V                      |

| V <sub>DD2</sub> to GND <sub>2</sub>                  | –0.3 V to +6.5 V                      |

| Analog Input Voltage to GND1                          | -1 V to V <sub>DD1</sub> + 0.3 V      |

| Digital Input Voltage to GND <sub>2</sub>             | -0.3 V to V <sub>DD2</sub> + 0.5 V    |

| Output Voltage to GND <sub>2</sub>                    | $-0.3V$ to $V_{\text{DD2}}$ + 0.3 $V$ |

| Input Current to Any Pin Except Supplies <sup>1</sup> | ±10 mA                                |

| Operating Temperature Range                           | -55°C to +125°C                       |

| Storage Temperature Range                             | -65°C to +150°C                       |

| Junction Temperature                                  | 150°C                                 |

| Pb-Free Temperature, Soldering                        |                                       |

| Reflow                                                | 260°C                                 |

| ESD                                                   | 2 kV                                  |

| FICDM <sup>2</sup>                                    | ±1250 V                               |

| HBM <sup>3</sup>                                      | ±4000 V                               |

#### <sup>1</sup> Transient currents of up to 100 mA do not cause SCR to latch up.

<sup>2</sup> JESD22-C101; RC network: 1 Ω, Cpkg; Class: IV. <sup>3</sup> ESDA/JEDEC JS-001-2011; RC network: 1.5 kΩ, 100 pF; Class: 3A.

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

#### Table 8. Maximum Continuous Working Voltage<sup>1</sup>

| Table 6. Maximum Continuous Working Voltage |      |                   |                                                               |  |  |  |

|---------------------------------------------|------|-------------------|---------------------------------------------------------------|--|--|--|

| Parameter                                   | Max  | Unit              | Constraint                                                    |  |  |  |

| AC Voltage                                  |      |                   |                                                               |  |  |  |

| Bipolar Waveform                            | 1250 | Vpeak             | 20-year minimum<br>lifetime (VDE approved<br>working voltage) |  |  |  |

| Unipolar Waveform                           | 1250 | V <sub>PEAK</sub> | 20-year minimum<br>lifetime                                   |  |  |  |

| DC Voltage                                  | 1250 | VPEAK             | 20-year minimum<br>lifetime                                   |  |  |  |

<sup>1</sup> Maximum continuous working voltage refers to continuous voltage magnitude imposed across the isolation barrier.

#### **ESD CAUTION**

ESD (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

# AD7403-EP

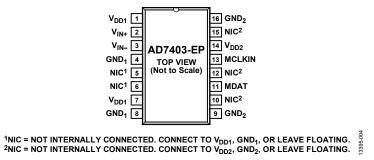

# **PIN CONFIGURATIONS AND FUNCTION DESCRIPTIONS**

Figure 4. Pin Configuration

#### **Table 9. Pin Function Descriptions**

| Pin No.    | Mnemonic          | Description                                                                                                                                                                                                                                                                                                                   |

|------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 7       | V <sub>DD1</sub>  | Supply Voltage, 4.5 V to 5.5 V. This is the supply voltage for the isolated side of the AD7403-EP and is relative to GND <sub>1</sub> . For device operation, connect the supply voltage to both Pin 1 and Pin 7. Decouple each supply pin to GND <sub>1</sub> with a 10 $\mu$ F capacitor in parallel with a 1 nF capacitor. |

| 2          | V <sub>IN+</sub>  | Positive Analog Input.                                                                                                                                                                                                                                                                                                        |

| 3          | V <sub>IN</sub> - | Negative Analog Input. Normally connected to GND <sub>1</sub> .                                                                                                                                                                                                                                                               |

| 4, 8       | GND <sub>1</sub>  | Ground 1. This pin is the ground reference point for all circuitry on the isolated side.                                                                                                                                                                                                                                      |

| 5, 6       | NIC               | Not Internally Connected. These pins are not internally connected. Connect to VDD1, GND1, or leave floating.                                                                                                                                                                                                                  |

| 9, 16      | GND <sub>2</sub>  | Ground 2. This pin is the ground reference point for all circuitry on the nonisolated side.                                                                                                                                                                                                                                   |

| 10, 12, 15 | NIC               | Not Internally Connected. These pins are not internally connected. Connect to VDD2, GND2, or leave floating.                                                                                                                                                                                                                  |

| 11         | MDAT              | Serial Data Output. The single bit modulator output is supplied to this pin as a serial data stream. The bits are clocked out on the rising edge of the MCLKIN input and are valid on the following MCLKIN rising edge.                                                                                                       |

| 13         | MCLKIN            | Master Clock Logic Input. 5 MHz to 20 MHz frequency range. The bit stream from the modulator is propagated on the rising edge of the MCLKIN.                                                                                                                                                                                  |

| 14         | V <sub>DD2</sub>  | Supply Voltage, 3 V to 5.5 V. This is the supply voltage for the nonisolated side and is relative to GND <sub>2</sub> . Decouple this supply to GND <sub>2</sub> with a 100 nF capacitor.                                                                                                                                     |

# **TYPICAL PERFORMANCE CHARACTERISTICS**

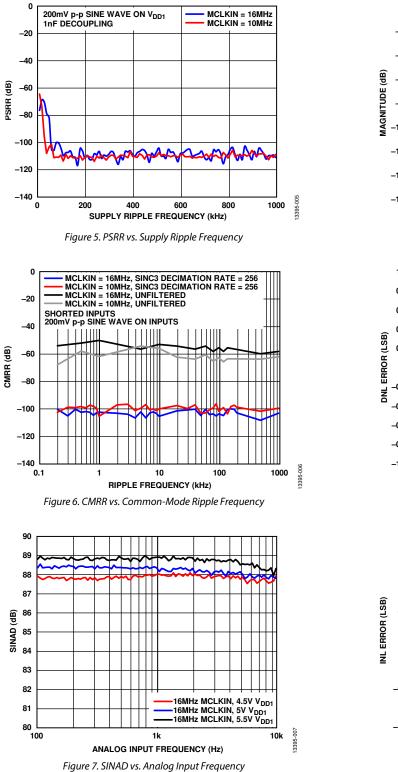

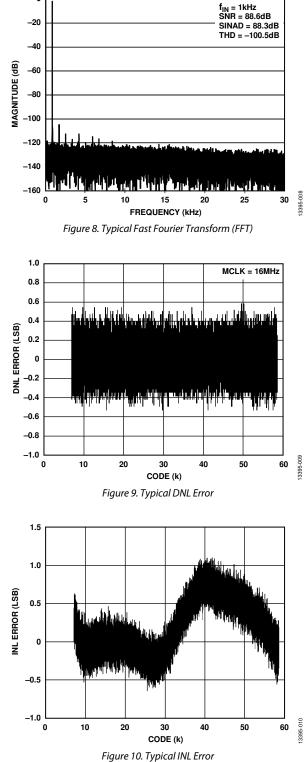

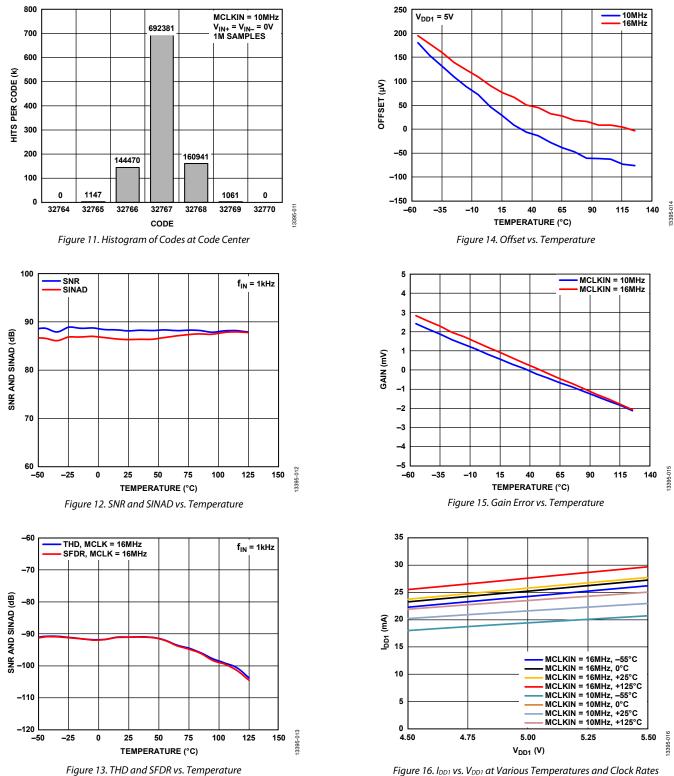

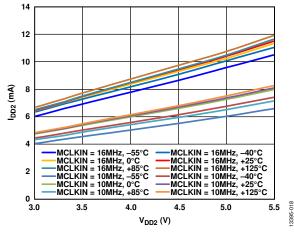

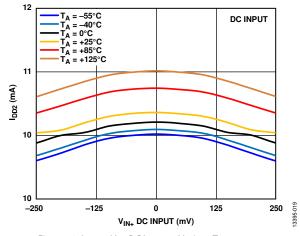

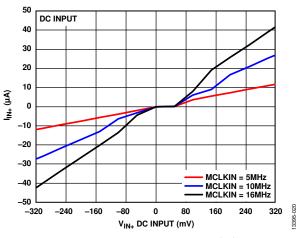

$T_A = 25^{\circ}$ C,  $V_{DD1} = 5$  V,  $V_{DD2} = 5$  V,  $V_{IN+} = -250$  mV to +250 mV,  $V_{IN-} = 0$  V,  $f_{MCLKIN} = 16$  MHz, using a sinc3 filter with a 256 oversampling ratio (OSR), unless otherwise noted.

0

# AD7403-EP

# **Enhanced Product**

Figure 16. IDD1 vs. VDD1 at Various Temperatures and Clock Rates

# **Enhanced Product**

# AD7403-EP

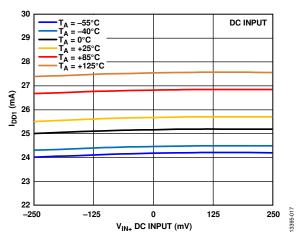

Figure 17. IDD1 vs. VIN+ DC Input at Various Temperatures

Figure 18. IDD2 vs. VDD2 at Various Temperatures and Clock Rates

Figure 19. IDD2 vs. VIN+ DC Input at Various Temperatures

Figure 20. I<sub>IN+</sub> vs. V<sub>IN+</sub> DC Input at Various Clock Rates

# AD7403-EP

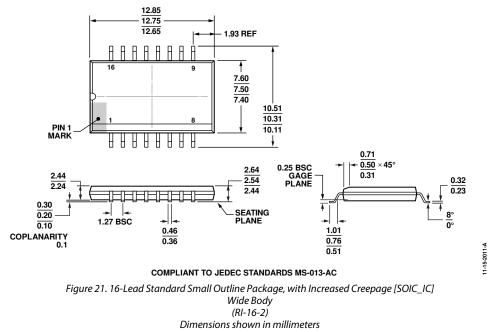

### **OUTLINE DIMENSIONS**

#### **ORDERING GUIDE**

| Model <sup>1</sup> | Temperature Range | Package Description                                                       | Package Option |

|--------------------|-------------------|---------------------------------------------------------------------------|----------------|

| AD7403TRIZ-EP      | -55°C to +125°C   | 16-Lead Standard Small Outline Package, with Increased Creepage [SOIC_IC] | RI-16-2        |

| AD7403TRIZ-EP-RL7  | –55°C to +125°C   | 16-Lead Standard Small Outline Package, with Increased Creepage [SOIC_IC] | RI-16-2        |

| EVAL-AD7403FMCZ    |                   | AD7403 Evaluation Board                                                   |                |

| EVAL-SDP-CH1Z      |                   | System Demonstration Platform                                             |                |

$^{1}$  Z = RoHS Compliant Part.

©2016 Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective owners. D13395-0-4/16(0)

www.analog.com

Rev. 0 | Page 12 of 12