# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# CMOS µP-Compatible 8-Bit, 8-Channel DAS

# AD7581

#### **FEATURES**

#### 8-Bit Resolution On-Chip 8 X 8 Dual-Port Memory No Missed Codes Over Full Temperature Range Interfaces Directly to Z80/8085/6800 CMOS, TTL Compatible Digital Inputs Three-State Data Drivers Ratiometric Capability Interleaved DMA Operation Fast Conversion A/D Process Totally Transparent to μP Low Cost

#### **GENERAL DESCRIPTION**

The AD7581 is a microprocessor compatible 8 bit, 8 channel, memory buffered, data-acquisition system on a monolithic CMOS chip. It consists of an 8 bit successive approximation A/D converter, an 8 channel multiplexer,  $8 \times 8$  dual-port RAM, three-state DATA drivers (for interface), address latches and microprocessor compatible control logic. The device interfaces directly to 8080, 8085, Z80, 6800 and other microprocessor systems.

The successive approximation conversion takes place on a continuous, channel sequencing, basis using microprocessor control signals for the clock. Data is automatically transferred to its proper location in the  $8 \times 8$  dual-port RAM at the end of each conversion. When under microprocessor control, a READ DATA operation is allowed at any time for any channel since on-chip logic provides interleaved DMA. The facility to latch the address inputs (A<sub>0</sub> - A<sub>2</sub>) with ALE enables the AD7581 to interface with  $\mu$ P systems which feature either shared or separate address and data buses.

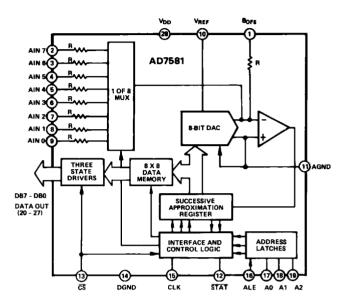

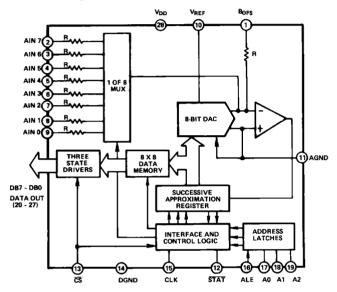

#### FUNCTIONAL BLOCK DIAGRAM

#### REV. A

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel:

617/329-4700

Fax:

617/326-8703

Twx:

710/394-6577

Telex:

924491

Cable:

ANALOG NORWOODMASS

# AD7581\* PRODUCT PAGE QUICK LINKS

Last Content Update: 02/23/2017

# COMPARABLE PARTS

View a parametric search of comparable parts.

## DOCUMENTATION

#### Data Sheet

AD7581: CMOS, uP-Compatible 8-Bit, 8-Channel DAS Data Sheet

## REFERENCE MATERIALS

#### **Technical Articles**

• MS-2210: Designing Power Supplies for High Speed ADC

# DESIGN RESOURCES

- AD7581 Material Declaration

- PCN-PDN Information

- Quality And Reliability

- Symbols and Footprints

## DISCUSSIONS

View all AD7581 EngineerZone Discussions.

## SAMPLE AND BUY

Visit the product page to see pricing options.

## TECHNICAL SUPPORT

Submit a technical question or find your regional support number.

### DOCUMENT FEEDBACK

Submit feedback for this data sheet.

#

| Parameter                                                                          | Version <sup>1</sup> | Typical at<br>+25°C                  | Limit Over<br>Temperature   | Units                  | Conditions/Comments                      |

|------------------------------------------------------------------------------------|----------------------|--------------------------------------|-----------------------------|------------------------|------------------------------------------|

|                                                                                    | v c131011            | +230                                 | 1 emperature                |                        | Conditions/Comments                      |

| ACCURACY                                                                           |                      |                                      |                             |                        |                                          |

| Resolution                                                                         | All                  | 8                                    | 8                           | Bits                   |                                          |

| Relative Accuracy                                                                  | JN, AQ               | ±1 7/8                               | ±1 7/8 max                  | LSB                    |                                          |

|                                                                                    | KN, BQ               | ±3/4                                 | $\pm 3/4 \max$              | LSB                    |                                          |

|                                                                                    | LN, CQ               | $\pm 1/2$                            | $\pm 1/2 \max$              | LSB                    |                                          |

| Differential Nonlinearity                                                          | JN, AQ               | ±1 7/8                               | ±1 7/8 max                  | LSB                    |                                          |

|                                                                                    | KN, BQ               | ±7/8                                 | $\pm 7/8 \text{ max}$       | LSB                    |                                          |

|                                                                                    | LN, CQ               | ±3/4                                 | $\pm 3/4 \max$              | LSB                    |                                          |

| Offset Error <sup>2</sup>                                                          | JN, AQ               | 200                                  | 200 max                     | mV                     | Adjustable to zero, See Figure 7a.       |

|                                                                                    | KN, BQ               | 80                                   | 80 max                      | mV                     | ,                                        |

|                                                                                    | LN, CQ               | 50                                   | 50 max                      | mV                     |                                          |

| Gain Error                                                                         |                      |                                      |                             |                        |                                          |

| Worst Channel                                                                      | JN, AQ               | ±3                                   | $\pm 6 \text{ max}$         | LSB                    | Adjustable to zero, See Figure 7a.       |

|                                                                                    | KN, BQ               | ±2                                   | $\pm 4 \max$                | LSB                    |                                          |

|                                                                                    |                      | ±1                                   |                             |                        | Gain Error Is Measured After Offse       |

|                                                                                    | LN, CQ               | <u> </u>                             | ±2 max                      | LSB                    | Calibration. Max Full Scale Change       |

|                                                                                    |                      |                                      |                             |                        | for Any Channel from +25°C to            |

| Coin Match Dataset Of                                                              | <b>n</b> ,           |                                      |                             |                        | $T_{\min}$ or $T_{\max}$ Is $\pm 2LSB$ . |

| Gain Match Between Channels                                                        | JN, AQ               | 2                                    | 3 max                       | LSB                    | Adjustable to zero, See Figure 7a.       |

|                                                                                    | KN, BQ               | 1 1/2                                | 2 max                       | LSB                    |                                          |

|                                                                                    | LN, CQ               | 1                                    | l max                       | LSB                    |                                          |

| B <sub>OFS</sub> Gain Error                                                        | All                  | -2 1/2                               | -                           | LSB                    |                                          |

| ANALOG INPUTS                                                                      | +                    | 1                                    |                             |                        |                                          |

| Input Resistance                                                                   |                      |                                      |                             |                        |                                          |

| At $V_{\text{REF}}$ (Pin 10)                                                       | All                  | 10/20/30                             | 10/20/30                    | bo minter (            |                                          |

| At $B_{OFS}$ (Pin 1) <sup>3</sup>                                                  |                      |                                      |                             | $k\Omega \min/typ/max$ |                                          |

|                                                                                    |                      | 10/20/30                             | 10/20/30                    | $k\Omega \min/typ/max$ |                                          |

| At Any Analog Input (Pins 2–9)                                                     | All                  | 10/20/30                             | 10/20/30                    | kΩ min/typ/max         |                                          |

| V <sub>REF</sub> (For Specified Performance)                                       | All                  | -10                                  | -10                         | V                      | ±5%                                      |

| V <sub>REF</sub> Range <sup>4</sup>                                                | All                  | -5 to -15                            | -5 to -15                   | V                      |                                          |

| Nominal Analog Input Range                                                         |                      |                                      |                             |                        |                                          |

| Unipolar Mode                                                                      | All                  | 0 to $+V_{REF}$                      | 0 to $+V_{REF}$             | V                      | See Figure 7 and 8.                      |

|                                                                                    | 1                    | 0 to $-V_{REF}$                      | 0 to -V <sub>REF</sub>      | v                      |                                          |

| Bipolar Mode                                                                       | All                  | −VB <sub>OFS</sub> ≤VA <sub>IP</sub> | $\leq  V_{REF}  - VB_{OFS}$ |                        | See Figure 9                             |

| DIGITAL INPUTS                                                                     |                      |                                      |                             |                        |                                          |

| $\overline{\text{CS}}$ (Pin 13), ALE (Pin 16) $A_0 - A_2$                          |                      |                                      |                             |                        |                                          |

| (Pin 17-19), CLK (Pin 15)                                                          |                      |                                      |                             |                        |                                          |

| V <sub>INH</sub> Logic HIGH Input Voltage                                          | All                  | +2.2                                 | +2.4 min                    | 37                     |                                          |

|                                                                                    |                      |                                      | +2.4 min                    | V                      |                                          |

| V <sub>INL</sub> Logic LOW Input Voltage                                           | All                  | +1.2                                 | +0.8 max                    | V                      |                                          |

| I <sub>IN</sub> Input Current                                                      | All                  | 0.01                                 | l max                       | μΑ                     | $V_{IN} = 0V, V_{DD}$                    |

| C <sub>IN</sub> Input Capacitance <sup>5</sup>                                     | All                  | 4                                    | 5 max                       | pF                     |                                          |

| DIGITAL OUTPUTS                                                                    |                      |                                      |                             |                        |                                          |

| $\overline{\text{STAT}}$ (Pin 12), DB <sub>7</sub> to DB <sub>0</sub> (Pins 20-27) | }                    |                                      |                             |                        |                                          |

| VOH Output HIGH Voltage                                                            | All                  | +4.8                                 | +4.5 min                    | v                      | $I_{SOURCE} = 40 \mu A$                  |

| Vol Output LOW Voltage                                                             | All                  | +0.4                                 | +0.6 max                    | v                      |                                          |

| $I_{LKG}$ DB <sub>7</sub> to DB <sub>0</sub> Floating State                        |                      |                                      | 10.0 max                    | ¥                      | $I_{SINK} = 1.6mA$                       |

| Leakage                                                                            | All                  | 0.3                                  | 10 max                      |                        |                                          |

| Floating State Output Capacitance                                                  | <u>''''</u>          | 0.5                                  | 10 Шах                      | μA                     |                                          |

| $(DB_7 - DB_0)$                                                                    | A11                  | 5                                    | 10                          |                        |                                          |

|                                                                                    | All                  | 5                                    | 10 max                      | pF                     | $V_{OUT} = 0V$ to $V_{DD}$               |

| Output Code                                                                        | All                  | Unipolar Binary                      |                             |                        |                                          |

|                                                                                    |                      |                                      | Binary Figure 8             |                        |                                          |

|                                                                                    |                      | Offset Binary F                      | igure 9                     |                        |                                          |

| OWER REQUIREMENTS                                                                  |                      |                                      |                             |                        |                                          |

| V <sub>DD</sub>                                                                    | All                  | +5                                   | +5                          | v                      |                                          |

| $I_{DD}$ – Static                                                                  | All                  | 3 typ                                | 5 max                       | mA                     |                                          |

| $I_{DD}$ – Dynamic                                                                 | All                  | 3 typ                                | 8 max                       |                        | 6 _1MH_                                  |

| IOTES                                                                              | 111                  | Jtyp                                 |                             | mA                     | f <sub>CLK</sub> =1MHz                   |

NOTES

NOTES <sup>1</sup>Temperature range as follows: JN, KN, LN (0 to +70°C); AQ, BQ, CQ (-25°C to +85°C). <sup>2</sup>Typical offset temperature coefficient is ±150µV/°C. <sup>3</sup>R<sub>BOF5</sub>/R<sub>AIN</sub> (0-7) mismatch causes transfer function rotation about positive full scale. The effect is an offset and a gain term when using the circuits of Figure 8a and Figure 9a. <sup>4</sup>Typical value, not guaranteed or subject to test. <sup>5</sup>Guaranteed but not tested

<sup>5</sup>Guaranteed but not tested.

<sup>6</sup>Typical change in B<sub>OFS</sub> gain from  $+25^{\circ}$ C to T<sub>min</sub> to T<sub>max</sub> is  $\pm 2$ LSBs. Specifications subject to change without notice.

# AD7581 GENERAL CIRCUIT INFORMATION

#### BASIC CIRCUIT DESCRIPTION

The AD7581 accepts eight analog inputs and sequentially converts each input into an eight-bit binary word using the successive approximation technique. The conversion results are stored in an  $8 \times 8$  bit dual-port RAM. The device runs either directly from the microprocessor clock (in 6800 type systems) or from some suitable signal (e.g. ALE in 8085 type systems). Most applications require only a -10V reference and a +5V supply. Start-up logic is included on the device to establish the correct sequences on power-up. A maximum of 800 clock pulses are required for this period. Figure 1 shows the AD7581 functional diagram.

Figure 1. AD7581 Functional Diagram

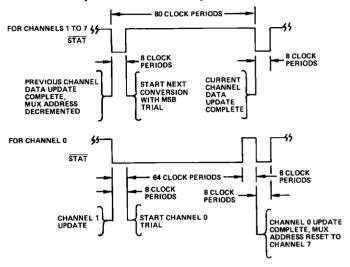

Conversion of a single channel requires 80 input clock periods and a complete scan through all channels requires 640 input clock periods. When a channel conversion is complete, the successive approximation register contents are loaded into the proper channel location of the  $8 \times 8$  RAM. At this time a status signal output, STAT (pin 12), gives a short negative going pulse (8 clock periods). This negative going STAT pulse is extended to 72 clock periods when channel 1 conversion is complete. An external pulse-width detector connected to the status pin can be used to derive conversion-related timing signals for microprocessor interrupts (see Channel Identification opposite page). Simultaneous with STAT going low, the MUX address is decremented. Eight clock periods later the next conversion is started. Automatic interleaved DMA is provided by on-chip logic to ensure that memory updates take place at instants when the microprocessor is not addressing memory. Memory locations are addressed by  $A_0$ ,  $A_1$  and  $A_2$ . This address may be latched by ALE for systems which feature a multiplexed address/data bus or alternatively, for systems which have separate address and data buses, the address latches can be made transparent by tying ALE (pin 16) HIGH.  $\overline{CS}$  (pin 13) activates three-state buffers to place addressed data on the DB<sub>0</sub> – DB<sub>7</sub> data output pins.

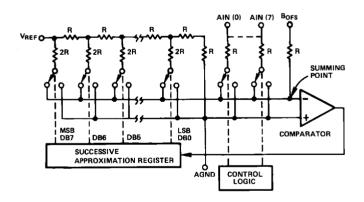

#### A/D CIRCUIT DETAILS

In the successive approximation technique, successive bits, starting with the most significant bit (DB<sub>7</sub>), are applied to the input of the D/A converter. The DAC output is then compared to the unknown analog input voltage,  $A_{IN}$  (n), using a comparator. If the DAC output is greater than  $A_{IN}$ (n), the data latch for the trial bit is reset to zero, and the next smaller data bit is tried. If the DAC output is less than  $A_{IN}$ (n), the trial data bit stays in the "1" state, and the next smaller data bit is tried. Each successive bit is tried, compared to  $A_{IN}$ (n), and set or reset in this manner until the least significant bit (DB<sub>0</sub>) decision is made. The successive approximation register now contains a valid digital representation of  $A_{IN}$ (n).  $A_{IN}$ (n) is assumed to be stable during conversion.

The current weighting D/A converter is a precision multiplying DAC. Figure 2 shows the functional diagram of the DAC as used in the AD7581. It consists of a precision Silicon Chromium thin film R/2R ladder network and 8 N-channel MOSFET switches operated in single-pole-double-throw.

The currents in each 2R shunt arm are binarily weighted i.e., the current in the MSB arm is  $V_{REF}$  divided by 2R, in the second arm is  $V_{REF}$  divided by 4R, etc. Depending on the D/A logic input (A/D output) from the successive approximation register, the current in the individual shunt arms is steered either to  $A_{GND}$  or to the comparator summing point.

Figure 2. D/A Converter as Used in AD7581

# AC SPECIFICATIONS ( $V_{DD} = +5V$ , $V_{REF} = -10V$ , Unipolar Operation, unless otherwise stated.)

| Symbol         | Specification                                     | Typical at<br>+25°C | Limit Over<br>Temperature                            | Units               | Conditions                           |

|----------------|---------------------------------------------------|---------------------|------------------------------------------------------|---------------------|--------------------------------------|

| t <sub>H</sub> | ALE pulse width                                   | 50                  | 80 min                                               | ns                  | See "Switching Terminology"          |

| ALS            | Address valid to latch set-up time                | 45                  | 70 min                                               | ns                  |                                      |

| ALH            | Address valid to latch hold time                  | 10                  | 20 min                                               | ns                  |                                      |

| LCS            | Address latch to $\overline{CS}$ set-up time      | 10                  | 20 min                                               | ns                  |                                      |

| ACC            | $\overline{CS}$ to output propagation delay       | 200                 | 250 max                                              | ns                  | $C_{I_{1}} = 100 p F$                |

| CW             | CS pulse width                                    | 250                 | 280 min                                              | ns                  |                                      |

| CF             | $\overline{CS}$ to output float propagation delay | 50                  | 80 max                                               | ns                  |                                      |

| CLZ            | CS to low impedance bus                           | 100                 | 150 max                                              | ns                  |                                      |

| CLK            | Clock frequency for stated accuracy               | 1600                | 1200 max <sup>1</sup><br><sup>1</sup> Guaranteed cor | kHz<br>nversion tim | e of 66.6µs/channel with 1200kHz clo |

#### **ABSOLUTE MAXIMUM RATINGS**

| $V_{DD}$ to AGND                                                                                                                                    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| $V_{DD}$ to DGND                                                                                                                                    |

| AGND to DGND                                                                                                                                        |

| Digital Input Voltage to DGND                                                                                                                       |

| (Pins 13, 16–19)                                                                                                                                    |

| Digital Output Voltage to DGND                                                                                                                      |

| (Pins 12, 20–27)                                                                                                                                    |

| CLK (Pin 15) Input Voltage to DGND . $-0.3V$ , $V_{DD} + 0.3V$                                                                                      |

| $V_{REF}$ (Pin 10) to AGND                                                                                                                          |

| $V_{BOFS}$ (Pin 1) to AGND                                                                                                                          |

| AIN (0-7)(Pin 9-2)                                                                                                                                  |

| Operating Temperature Range                                                                                                                         |

| Commercial (J, K, L Versions) $\ldots \ldots \ldots 0$ to $+70^{\circ}$ C                                                                           |

| Industrial (A, B, C Versions) $\ldots \ldots \ldots -25^{\circ}$ C to $+85^{\circ}$ C                                                               |

| Storage Temperature $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots -65^{\circ}C$ to $+150^{\circ}C$                                |

| Lead Temperature (Soldering, 10secs) + 300°C                                                                                                        |

| Power Dissipation (Any Package)                                                                                                                     |

| to $+75^{\circ}$ C                                                                                                                                  |

| Derate above $+75^{\circ}$ C by $\dots \dots \dots$ |

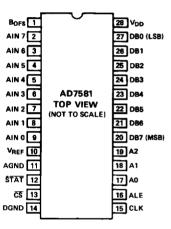

#### PIN CONFIGURATION

#### **CAUTION** -

ESD (electrostatic discharge) sensitive device. The digital control inputs are diode protected; however, permanent damage may occur on unconnected devices subject to high energy electrostatic fields. Unused devices must be stored in conductive foam or shunts. The protective foam should be discharged to the destination socket before devices are removed.

#### **ORDERING GUIDE**

| Model    | Temperature<br>Range | Differential<br>Nonlinearity (LSB) | Package<br>Option* |  |

|----------|----------------------|------------------------------------|--------------------|--|

| AD7581JN | 0 to +70°C           | ±1 7/8 max                         | N-28               |  |

| AD7581KN | 0 to +70°C           | ±7/8 max                           | N-28               |  |

| AD7581LN | 0 to +70°C           | ± 3/4 max                          | N-28               |  |

| AD7581AQ | -25°C to +85°C       | ±1 7/8 max                         | Q-28               |  |

| AD7581BQ | -25°C to +85°C       | ±7/8 max                           | Q-28               |  |

| AD7581CQ | -25°C to +85°C       | ±3/4 max                           | Q-28               |  |

#### NOTE

\*N = Plastic DIP; Q = Cerdip. For outline information see Package Information section.

#### TIMING AND CONTROL OF THE AD7581 CHANNEL SELECTION

Table I shows the truth table for the address inputs. The input address is latched when ALE goes LOW. When ALE is HIGH the address input latch is transparent.

| A2 | A1 | A0 | ALE _ | Channel Data<br>To Be Read |

|----|----|----|-------|----------------------------|

| 0  | 0  | 0  | 1     | Channel 0                  |

| 0  | 0  | 1  | 1     | Channel 1                  |

| 0  | 1  | 0  | 1     | Channel 2                  |

| 0  | 1  | 1  | 1     | Channel 3                  |

| 1  | 0  | 0  | 1     | Channel 4                  |

| 1  | 0  | 1  | 1     | Channel 5                  |

| 1  | 1  | 0  | 1     | Channel 6                  |

| 1  | 1  | 1  | 1     | Channel 7                  |

#### TIMING AND CONTROL

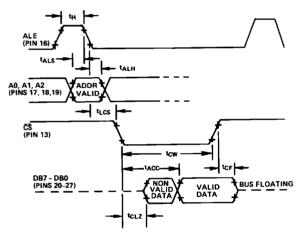

A typical timing diagram is shown in Figure 3. When  $\overline{CS}$  is HIGH, the three-state data drivers are in the high-impedance state. When  $\overline{CS}$  goes LOW the data drivers switch to the lowimpedance state (i.e., low impedance to DGND or to  $V_{DD}$ ). Output data is valid after time  $t_{ACC}$ .

Figure 3. Timing Diagram for the AD7581

#### SWITCHING TERMINOLOGY

$\begin{array}{ll} t_H: & ALE \ pulse \ width \ requirement. \\ t_{ALH}: Address \ Valid \ to \ latch \ hold \ time. \\ t_{ALS}: \ Address \ Valid \ to \ latch \ set-up \ time. \\ t_{LCS}: \ Address \ Valid \ to \ Chip \ Select \ set-up \ time. \\ t_{CW}: \ Chip \ Select \ pulse \ width \ requirement. \\ t_{ACC}: Chip \ Select \ to \ valid \ data \ propagation \ delay. \\ t_{CF}: \ Chip \ Select \ to \ output \ data \ float \ propagation \ delay. \\ t_{CLZ}: Chip \ Select \ to \ low \ impedance \ data \ bus. \end{array}$

#### CHANNEL IDENTIFICATION

In some real-time applications, it may be necessary to provide an interrupt signal when a particular channel receives updated data. To achieve this, it is necessary to identify which channel is currently under conversion. The STAT output provides an identifying signal by staying low for an additional 64 clock periods over normal (8 clock periods) when channel 0 is active. This is illustrated in Figure 4. Memory update takes place on a rising edge of a clock pulse and is completed in 200ns. This occurs 6 clock periods before STAT goes low.

Figure 4. STAT Output for Channel Identification

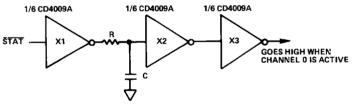

One simple circuit using the  $\overline{STAT}$  output is shown in Figure 5. The time constant RC is chosen such that  $X_2$  ignores the normal  $\overline{STAT}$  low pulse width (8 clock periods wide) but respond to the much wider  $\overline{STAT}$  low pulse width (72 clock periods wide) occurring during channel 0 conversion. Typically for a 1 $\mu$ s clock period C = 0.022 $\mu$ F, R = 1.8k $\Omega$ .

Figure 5. Hardware Channel Identification

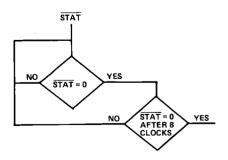

Another possibility is to use the microprocessor to interrogate the STAT output and hence determine channel identity. A simple routine is shown in Figure 6.

Figure 6. Software Channel Identification

# AD7581 OPERATING THE AD7581

#### UNIPOLAR BINARY OPERATION

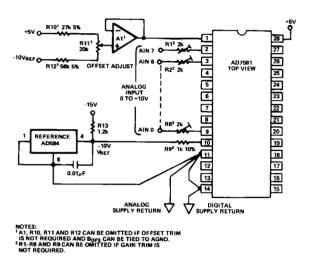

Figures 7a and 7b show the analog circuit connections and typical transfer characteristic for unipolar operation (0V to +10V). An AD584 is used for the -10V reference. Calibration is as follows (device clocked i.e., continuous conversions); OFFSET:

Comparator offset is trimmed out via the bipolar offset pin  $B_{OFS}$ . R10, R11 and R12 comprise a simple voltage tap buffered by A1 and feeding into  $B_{OFS}$ .

- 1. Since comparator offset will be the same regardless of which channel is active, take A<sub>0</sub>, A<sub>1</sub> and A<sub>2</sub> LOW and and exercise ALE to latch the address.

- 2. With AIN 0 = 19.5mV (1/2LSB) adjust R11, i.e., the offset voltage on B<sub>OFS</sub>, until DB<sub>7</sub> DB<sub>1</sub> are LOW and DB<sub>0</sub> (LSB) flickers.

Figure 7a. AD7581 Unipolar (OV to +10V) Operation (Output Code is Straight Binary)

#### **GAIN (FULL SCALE)**

In many applications gain adjustment is not required thus removing the need for trimmers in the analog channels. For channels requiring gain trim, the following procedure is recommended. Offset adjustment must be performed before gain adjustment.

- 1. Apply +9.941V (FS 3/2LSB) to all input channels AIN (0-7).

- 2. Select required channel n via A<sub>0</sub>, A<sub>1</sub>, A<sub>2</sub> and latch the Address using ALE.

- 3. Adjust trimmer RN of selected channel until DB<sub>7</sub> DB<sub>1</sub> are HIGH and the LSB (DB<sub>0</sub>) flickers.

- 4. Select next channel requiring gain trim and repeat steps 2 and 3.

INPUT VOLTAGE, VOLTS (REFERRED TO ANALOG GROUND) NOTE: APPROXIMATE BIT WEIGHTS ARE SHOWN FOR ILLUSTRATION. BIT WEIGHT FOR A -10V REFERENCE IS ≈ 39.1mV.

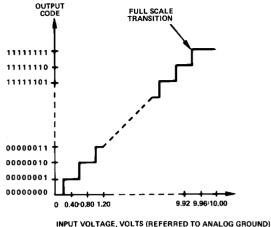

Figure 7b. Transfer Characteristic for Unipolar Circuit of Figure 7a

#### UNIPOLAR (COMPLEMENTARY BINARY) OPERATION

Figures 8a and 8b show the analog circuit connections and typical transfer characteristic for unipolar (complementary binary) operation.

Calibration is as follows (continuous conversions);

#### OFFSET:

Comparator offset is trimmed out via the bipolar offset pin B<sub>OFS</sub>. R10, R11 and R12 comprise a simple voltage tap buffered by A1 and feeding into B<sub>OFS</sub>.

- 1. Since comparator offset will be the same regardless of which channel is active, take  $A_0$ ,  $A_1$  and  $A_2$  LOW and exercise ALE to latch the address.

- 2. With AIN 0 = -9.98V (-FS + 1/2LSB) adjust R11, i.e., the offset voltage on  $B_{OFS}$ , until  $DB_7 DB_1$  are LOW and the LSB ( $DB_0$ ) flickers.

Figure 8a. AD7581 (0V to -10V) Operation (Output Code is Complementary Binary)

#### GAIN (FULL SCALE)

In many applications gain adjustment is not required thus removing the need for trimmers in the analog channels. For channels requiring gain trim, the following procedure is recommended. Offset adjustment must be performed before gain adjustment.

- 1) Apply -58.6mV (3/2LSB) to all input channels AIN (0-7).

- 2) Select required channel n via A<sub>0</sub>, A<sub>1</sub>, A<sub>2</sub> and exercise ALE to latch the address.

- 3) Adjust trimmer RN of selected channel until DB<sub>7</sub> DB1 are HIGH and the LSB (DB<sub>0</sub>) flickers.

- 4) Select next channel requiring gain trim and repeat step 2 and 3.

Figure 8b. Transfer Characteristic for Unipolar Circuit of Figure 8a

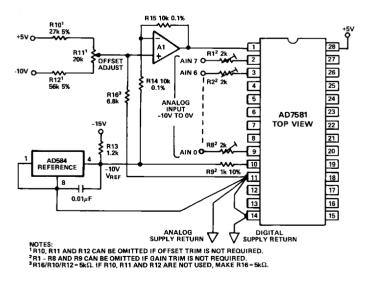

#### **BIPOLAR (OFFSET BINARY) OPERATION**

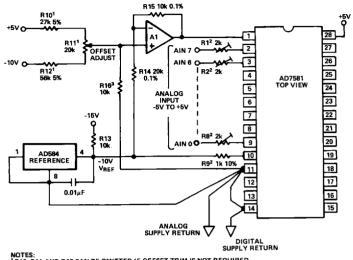

Figures 9a and 9b illustrate the analog circuitry and transfer characteristic for  $\pm 5V$  bipolar operation. Output coding is offset binary. Comparator offset correction is again applied to the BOFS pin.

Calibration is as follows (continuous conversions);

#### **OFFSET**:

- 1. Apply -4.980V (-FS/2 + 1/2LSB) to all input channels AIN (0-7).

- 2. Trim R11 of the comparator offset circuit until DB<sub>7</sub>-DB<sub>1</sub> are LOW and the LSB (DB<sub>0</sub>) flickers.

#### GAIN (FULL SCALE)

- 1. Apply +4.941V (+FS/2 -3/2LSB) to all input channels, A<sub>IN</sub> (0-7).

- 2. Select required channel n via A<sub>0</sub>, A<sub>1</sub>, A<sub>2</sub>, and latch the address using ALE.

- 3. Adjust trimmer RN of selected channel until DB7 DB1 are HIGH and the LSB (DB0) flickers.

- 4. Select next channel requiring gain trim and repeat steps 2 and 3.

- 5. Apply -19.5mV to each gain-trimmed channel. If the ADC output code does not flicker between 01111111 and 10000000 repeat the calibration procedure.

NOTES: <sup>1</sup> R10, R11 AND R12 CAN BE OMITTED IF OFFSET TRIM IS NOT REQUIRED. <sup>2</sup> R1 - R8 AND R9 CAN BE OMITTED IF GAIN TRIM IS NOT REQUIRED. <sup>3</sup> R16/R10/R12 = 6.8kΩ. IF R10, R11 AND R12 ARE NOT USED, MAKE R16 = 6.8kΩ.

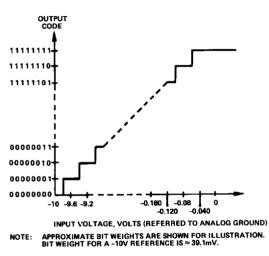

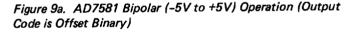

NOTE: APPROXIMATE BIT WEIGHTS ARE SHOWN FOR ILLUSTRATION. BIT WEIGHT FOR 10V FULL SCALE IS  $\approx$  39.1mV.

Figure 9b. Transfer Characteristic Around Major Carry for. Bipolar Circuit of Figure 9a

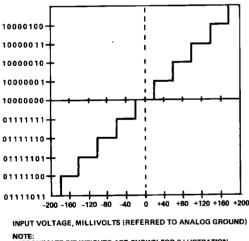

# AD7581 INTERFACING THE AD7581

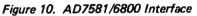

#### Figure 11. AD7581/8085 Interface

#### NOTES:

1. ANALOG AND DIGITAL GROUND

It is recommended that  $A_{GND}$  and  $D_{GND}$  be connected locally to prevent the possibility of injecting noise into the AD7581. In systems where the  $A_{GND} - D_{GND}$  intertie is not local, connect back-to-back diodes (1N914 or equivalent) between the AD7581  $A_{GND}$  and  $D_{GND}$  pins.

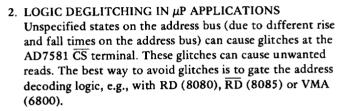

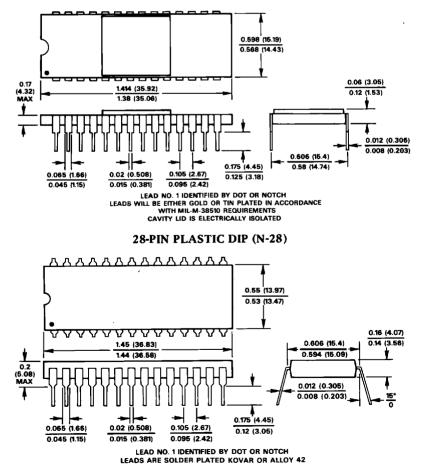

#### **MECHANICAL INFORMATION**

#### OUTLINE DIMENSIONS

Dimensions shown in inches and (mm).

28-PIN CERAMIC DIP (D-28)

C575c-2-5/89