# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

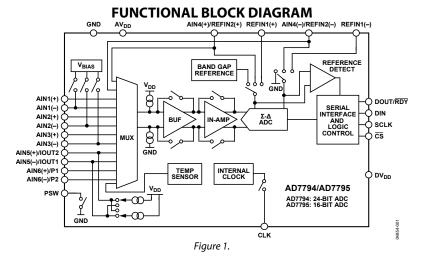

# 6-Channel, Low Noise, Low Power, 24-/16-Bit $\Sigma$ - $\Delta$ ADC with On-Chip In-Amp and Reference

# AD7794/AD7795

#### FEATURES

Up to 23 effective bits RMS noise: 40 nV @ 4.17 Hz, 85 nV @ 16.7 Hz Current: 400 µA typical Power-down: 1 µA maximum Low noise, programmable gain, instrumentation amp Band gap reference with 4 ppm/°C drift typical Update rate: 4.17 Hz to 470 Hz Six differential analog inputs Internal clock oscillator Simultaneous 50 Hz/60 Hz rejection **Reference detect Programmable current sources On-chip bias voltage generator Burnout currents** Low-side power switch Power supply: 2.7 V to 5.25 V **Temperature range:** B grade: -40°C to +105°C C grade: -40°C to +125°C Independent interface power supply 24-lead TSSOP 3-wire serial interface SPI®, QSPI™, MICROWIRE™, and DSP compatible Schmitt trigger on SCLK

#### **APPLICATIONS**

Temperature measurement Pressure measurement Weigh scales Strain gage transducers Gas analysis Industrial process control Instrumentation Blood analysis Smart transmitters Liquid/gas chromatography 6-digit DVM

#### **GENERAL DESCRIPTION**

The AD7794/AD7795 are low power, low noise, complete analog front ends for high precision measurement applications. They contain a low noise, 24-/16-bit  $\Sigma$ - $\Delta$  ADC with six differential inputs. The on-chip low noise instrumentation amplifier means that signals of small amplitude can be interfaced directly to the ADC.

Each device contains a precision, low noise, low drift internal band gap reference, and can also accept up to two external differential references. Other on-chip features include programmable excitation current sources, burnout currents, and a bias voltage generator that is used to set the common-mode voltage of a channel to  $AV_{DD}/2$ . The low-side power switch can be used to power down bridge sensors between conversions, minimizing the system's power consumption. The AD7794/AD7795 can operate with either an internal clock or an external clock. The output data rate from each part can vary from 4.17 Hz to 470 Hz.

Both parts operate with a power supply from 2.7 V to 5.25 V. The B-grade parts (AD7794 and AD7795) are specified for a temperature range of  $-40^{\circ}$ C to  $+105^{\circ}$ C while the C-grade part (AD7794) is specified for a temperature range of  $-40^{\circ}$ C to  $+125^{\circ}$ C. They consume a current of 400  $\mu$ A typical and are housed in a 24-lead TSSOP.

#### Rev. D

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700

www.analog.com

Fax: 781.461.3113

©2004–2007 Analog Devices, Inc. All rights reserved.

# **TABLE OF CONTENTS**

| Features                                    |    |

|---------------------------------------------|----|

| Applications                                | 1  |

| General Description                         | 1  |

| Functional Block Diagram                    | 1  |

| Revision History                            | 2  |

| Specifications                              |    |

| Timing Characteristics                      |    |

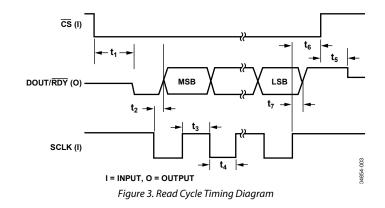

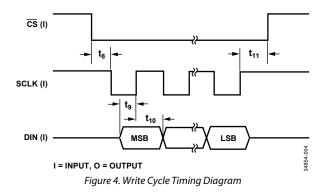

| Timing Diagrams                             | 9  |

| Absolute Maximum Ratings                    |    |

| ESD Caution                                 |    |

| Pin Configuration and Function Descriptions | 11 |

| RMS Noise and Resolution Specifications     |    |

| Chop Enabled                                | 13 |

| Chop Disabled                               | 15 |

| Typical Performance Characteristics         |    |

| On-Chip Registers                           | 17 |

| Communications Register                     | 17 |

| Status Register                             |    |

| Mode Register                               | 19 |

| Configuration Register                      |    |

| Data Register                               | 24 |

| ID Register                                 | 24 |

| IO Register                                 | 24 |

| Offset Register                             | 25 |

|                                             |    |

#### **REVISION HISTORY**

#### 3/07—Rev. C to Rev. D

| Changes to Specifications Endnote 1 | 7 |

|-------------------------------------|---|

| Changes to Status Register Section  |   |

| Changes to Ordering Guide           |   |

#### 10/06—Rev. B to Rev. C

| Updated Format            | Universal |

|---------------------------|-----------|

| Added AD7794 C-Grade Part | Universal |

| Changes to Specifications |           |

| Changes to Ordering Guide |           |

|                           |           |

#### 6/06—Rev. A to Rev. B

| Added AD7795                               | Universal |

|--------------------------------------------|-----------|

| Changes to Features                        | 1         |

| Changes to Table 1                         |           |

| Changes to RMS Noise and Resolution        |           |

| Specifications Section                     |           |

| Changes to Table 19                        |           |

| Changes to ADC Circuit Information Section |           |

| Changes to Ordering Guide                  |           |

| Full-Scale Register            |

|--------------------------------|

| ADC Circuit Information        |

| Overview                       |

| Digital Interface              |

| Circuit Description            |

| Analog Input Channel           |

| Instrumentation Amplifier31    |

| Bipolar/Unipolar Configuration |

| Data Output Coding             |

| Burnout Currents               |

| Excitation Currents            |

| Bias Voltage Generator         |

| Reference                      |

| Reference Detect               |

| Reset                          |

| AV <sub>DD</sub> Monitor       |

| Calibration                    |

| Grounding and Layout           |

| Applications Information 35    |

| Flowmeter                      |

| Outline Dimensions             |

| Ordering Guide                 |

#### 4/05—Rev. 0 to Rev. A

| Changes to Absolute Maximum Ratings   | 9  |

|---------------------------------------|----|

| Changes to Figure 21                  |    |

| Changes to Data Output Coding Section |    |

| Changes to Calibration Section        |    |

| Changes to Ordering Guide             | 33 |

| 5 5                                   |    |

#### 10/04—Revision 0: Initial Version

# **SPECIFICATIONS**

$AV_{DD}$  = 2.7 V to 5.25 V,  $DV_{DD}$  = 2.7 V to 5.25 V, GND = 0 V, all specifications  $T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted.

| Parameter <sup>1</sup>                          | AD7794/AD7795             | Unit              | Test Conditions/Comments                                                          |

|-------------------------------------------------|---------------------------|-------------------|-----------------------------------------------------------------------------------|

| CHOP ENABLED                                    |                           |                   | •                                                                                 |

| Output Update Rate                              | 4.17 to 470               | Hz nom            | Settling time = 2/output update rate                                              |

| No Missing Codes <sup>2</sup>                   |                           |                   |                                                                                   |

| AD7794                                          | 24                        | Bits min          | $f_{ADC} \leq 242 \text{ Hz}$                                                     |

| AD7795                                          | 16                        | Bits min          |                                                                                   |

| Resolution                                      |                           |                   | See the RMS Noise and Resolution Specifications section                           |

| RMS Noise and Update Rates                      |                           |                   | See the RMS Noise and Resolution Specifications section                           |

| Integral Nonlinearity                           | ±15                       | ppm of FSR<br>max |                                                                                   |

| Offset Error <sup>3</sup>                       | ±1                        | μV typ            |                                                                                   |

| Offset Error Drift vs. Temperature <sup>4</sup> | ±10                       | nV/°C typ         |                                                                                   |

| Full-Scale Error <sup>3, 5</sup>                | ±10                       | μV typ            |                                                                                   |

| Gain Drift vs. Temperature <sup>4</sup>         | ±1                        | ppm/°C typ        | Gain = 1 to 16, external reference                                                |

|                                                 | ±3                        | ppm/°C typ        | Gain = 32 to 128, external reference                                              |

| Power Supply Rejection                          | 100                       | dB min            | AIN = 1 V/gain, gain ≥ 4, external reference                                      |

| ANALOG INPUTS                                   |                           |                   |                                                                                   |

| Differential Input Voltage Ranges               | ±VREF/gain                | V nom             | V <sub>REF</sub> = REFIN(+) – REFIN(–), or internal reference,<br>gain = 1 to 128 |

| Absolute AIN Voltage Limits <sup>2</sup>        |                           |                   |                                                                                   |

| Unbuffered Mode                                 | GND – 30 mV               | V min             | Gain = 1 or 2                                                                     |

|                                                 | AV <sub>DD</sub> + 30 mV  | V max             |                                                                                   |

| Buffered Mode                                   | GND + 100 mV              | V min             | Gain = 1 or 2                                                                     |

|                                                 | AV <sub>DD</sub> – 100 mV | V max             |                                                                                   |

| In-Amp Active                                   | GND + 300 mV              | V min             | Gain = 4 to 128                                                                   |

|                                                 | AV <sub>DD</sub> – 1.1    | V max             |                                                                                   |

| Common-Mode Voltage, V <sub>CM</sub>            | 0.5                       | V min             | VCM = (AIN(+) + AIN(-))/2, gain = 4 to 128                                        |

| Analog Input Current                            |                           |                   |                                                                                   |

| Buffered Mode or In-Amp<br>Active               |                           |                   |                                                                                   |

| Average Input Current <sup>2</sup>              |                           |                   |                                                                                   |

| AD7794B/AD7795B                                 | ±1                        | nA max            | Gain = 1 or 2, update rate < 100 Hz                                               |

|                                                 | ±250                      | pA max            | Gain = 4 to 128, update rate < 100 Hz                                             |

|                                                 | ±1                        | nA max            | AIN6(+)/AIN6(-)                                                                   |

| AD7794C                                         | ±3                        | nA max            | Gain = 1 or 2, update rate < 100 Hz                                               |

|                                                 | ±2                        | nA max            | Gain = 4 to 128, update rate < 100 Hz                                             |

|                                                 | ±3                        | nA max            | AIN6(+)/AIN6(-)                                                                   |

| Average Input Current Drift                     | ±2                        | pA/°C typ         |                                                                                   |

| Unbuffered Mode                                 |                           |                   | Gain = 1 or 2                                                                     |

| Average Input Current                           | ±400                      | nA/V typ          | Input current varies with input voltage                                           |

| Average Input Current Drift                     | ±50                       | pA/V/°C typ       |                                                                                   |

| Normal Mode Rejection <sup>2, 6</sup>           |                           |                   |                                                                                   |

| Internal Clock                                  |                           |                   |                                                                                   |

| @ 50 Hz, 60 Hz                                  | 65                        | dB min            | 80 dB typ, 50 ± 1 Hz, 60 ± 1 Hz, FS[3:0] = 1010                                   |

| @ 50 Hz                                         | 80                        | dB min            | 90 dB typ, 50 ± 1 Hz, FS[3:0] = 1001                                              |

| @ 60 Hz                                         | 90                        | dB min            | 100 dB typ, 60 ± 1 Hz, FS[3:0] = 1000                                             |

| External Clock                                  |                           |                   |                                                                                   |

| @ 50 Hz, 60 Hz                                  | 80                        | dB min            | 90 dB typ, 50 ± 1 Hz, 60 ± 1 Hz, FS[3:0] = 1010                                   |

| @ 50 Hz                                         | 94                        | dB min            | 100 dB typ, 50 ± 1 Hz, FS[3:0] = 1001                                             |

| @ 60 Hz                                         | 90                        | dB min            | 100 dB typ, 60 ± 1 Hz, FS[3:0] = 1000                                             |

| Parameter <sup>1</sup>                          | AD7794/AD7795                                       | Unit        | Test Conditions/Comments                                                    |

|-------------------------------------------------|-----------------------------------------------------|-------------|-----------------------------------------------------------------------------|

| Common-Mode Rejection                           |                                                     |             |                                                                             |

| AD7794B/AD7795B                                 |                                                     |             |                                                                             |

| @ DC                                            | 100                                                 | dB min      | $AIN = 1 V/gain, gain \ge 4$                                                |

| @ 50 Hz, 60 Hz <sup>2</sup>                     | 100                                                 | dB min      | 50 ± 1 Hz, 60 ± 1 Hz, FS[3:0] = 1010                                        |

| @ 50 Hz, 60 Hz <sup>2</sup>                     | 100                                                 | dB min      | 50 ± 1 Hz, FS[3:0] = 1001; 60 ± 1 Hz, FS[3:0] = 1000                        |

| AD7794C                                         |                                                     |             |                                                                             |

| @ DC                                            | 97                                                  | dB min      | $AIN = 1 V/gain, gain \ge 4$                                                |

| @ 50 Hz, 60 Hz <sup>2</sup>                     | 97                                                  | dB min      | 50 ± 1 Hz, 60 ± 1 Hz, FS[3:0] = 1010                                        |

| @ 50 Hz, 60 Hz <sup>2</sup>                     | 97                                                  | dB min      | 50 ± 1 Hz, FS[3:0] = 1001; 60 ± 1 Hz, FS[3:0] = 1000                        |

| CHOP DISABLED                                   |                                                     |             |                                                                             |

| Output Update Rate                              | 4.17 to 470                                         | Hz nom      | Settling time = 1/output update rate                                        |

| No Missing Codes <sup>2</sup>                   |                                                     |             |                                                                             |

| AD7794                                          | 24                                                  | Bits min    | $f_{ADC} \le 123 \text{ Hz}$                                                |

| AD7795                                          | 16                                                  | Bits min    |                                                                             |

| Resolution                                      |                                                     |             | See the RMS Noise and Resolution Specifications section                     |

| RMS Noise and Update Rates                      |                                                     |             | See the RMS Noise and Resolution Specifications section                     |

| Integral Nonlinearity                           | ±15                                                 | ppm of FSR  | see the finis hoise and hesolation specifications seedon                    |

| integraritorinicality                           |                                                     | max         |                                                                             |

| Offset Error <sup>3</sup>                       | ±100/gain                                           | μV typ      | Without calibration                                                         |

| Offset Error Drift vs. Temperature <sup>4</sup> | ±100/gain                                           | nV/°C typ   | Gain = 1 to 16                                                              |

|                                                 | 10                                                  | nV/°C typ   | Gain = 32 to 128                                                            |

| Full-Scale Error <sup>3, 5</sup>                | ±10                                                 | μV typ      |                                                                             |

| Gain Drift vs. Temperature <sup>4</sup>         | ±1                                                  | ppm/°C typ  | Gain = 1 to 16, external reference                                          |

|                                                 | ±3                                                  | ppm/°C typ  | Gain = 32 to 128, external reference                                        |

| Power Supply Rejection                          | 100                                                 | dB typ      | AIN = 1 V/gain, gain $\ge$ 4, external reference                            |

| ANALOG INPUTS                                   |                                                     |             |                                                                             |

| Differential Input Voltage Ranges               | ±V <sub>REF</sub> /gain                             | V nom       | $V_{REF} = REFIN(+) - REFIN(-)$ , or internal reference,<br>gain = 1 to 128 |

| Absolute AIN Voltage Limits <sup>2</sup>        |                                                     |             |                                                                             |

| Unbuffered Mode                                 | GND – 30 mV                                         | V min       | Gain = 1 or 2                                                               |

|                                                 | $AV_{DD} + 30 \text{ mV}$                           | V max       |                                                                             |

| Buffered Mode                                   | GND + 100  mV                                       | V min       | Gain = 1 or 2                                                               |

| Dancied mode                                    | $AV_{DD} - 100 \text{ mV}$                          | V max       |                                                                             |

| In-Amp Active                                   | GND + 300 mV                                        | V min       | Gain = 4 to 128                                                             |

| in Amp Active                                   | AV <sub>DD</sub> - 1.1                              | V max       | Suit - + to 120                                                             |

| Common-Mode Voltage, $V_{CM}$                   | $0.2 + (gain/2 \times (AIN(+) - AIN(-)))$           | V min       | AMP - CM = 1, VCM = (AIN(+) + AIN(-))/2, gain = 4 to 128                    |

|                                                 | $AV_{DD} - 0.2 - (gain/2 \times (AIN(+) - AIN(-)))$ | V max       |                                                                             |

| Analog Input Current                            |                                                     |             |                                                                             |

| Buffered Mode or In-Amp<br>Active               |                                                     |             |                                                                             |

| Average Input Current <sup>2</sup>              |                                                     |             |                                                                             |

| AD7794B/AD7795B                                 | ±1                                                  | nA max      | Gain = 1 or 2                                                               |

|                                                 | ±250                                                | pA max      | Gain = 4 to 128                                                             |

|                                                 | ±1                                                  | nA max      | AIN6(+)/AIN6(-)                                                             |

| AD7794C                                         | ±3                                                  | nA max      | Gain = 1  or  2                                                             |

|                                                 | ±2                                                  | nA max      | Gain = 4 to 128                                                             |

|                                                 | ±2<br>±3                                            | nA max      | AIN6(+)/AIN6(-)                                                             |

| Average logut Current Drift                     | ±3<br>±2                                            | pA/°C typ   |                                                                             |

| Average Input Current Drift<br>Unbuffered Mode  | <u><u> </u></u>                                     | prv C typ   | Gain = 1 or 2                                                               |

|                                                 | 400                                                 | ····        |                                                                             |

| Average Input Current                           | ±400                                                | nA/V typ    | Input current varies with input voltage                                     |

| Average Input Current Drift                     | ±50                                                 | pA/V/°C typ |                                                                             |

| Parameter <sup>1</sup>                     | AD7794/AD7795                       | Unit        | Test Conditions/Comments                                                                                                |

|--------------------------------------------|-------------------------------------|-------------|-------------------------------------------------------------------------------------------------------------------------|

| Normal Mode Rejection <sup>2, 6</sup>      |                                     |             |                                                                                                                         |

| Internal Clock                             |                                     |             |                                                                                                                         |

| @ 50 Hz, 60 Hz                             | 60                                  | dB min      | 70 dB typ, 50 ± 1 Hz, 60 ± 1 Hz, FS[3:0] = 1010                                                                         |

| @ 50 Hz                                    | 78                                  | dB min      | 90 dB typ, 50 ± 1 Hz, FS[3:0] = 1001                                                                                    |

| @ 60 Hz                                    | 86                                  | dB min      | 100 dB typ, 60 ± 1 Hz, FS[3:0] = 1000                                                                                   |

| External Clock                             |                                     |             |                                                                                                                         |

| @ 50 Hz, 60 Hz                             | 60                                  | dB min      | 70 dB typ, 50 ± 1 Hz, 60 ± 1 Hz, FS[3:0] = 1010                                                                         |

| @ 50 Hz                                    | 94                                  | dB min      | 100 dB typ, 50 ± 1 Hz, FS[3:0] = 1001                                                                                   |

| @ 60 Hz                                    | 90                                  | dB min      | 100 dB typ, 60 ± 1 Hz, FS[3:0] = 1000                                                                                   |

| Common-Mode Rejection<br>AD7794B/AD7795B   |                                     |             |                                                                                                                         |

| @ DC                                       | 100                                 | dB min      | AIN = 1 V/gain, with gain = 4, AMP-CM Bit = 1                                                                           |

| @ 50 Hz, 60 Hz <sup>2</sup>                | 100                                 | dB min      | 50 ± 1 Hz, 60 ± 1 Hz, FS[3:0] = 1010                                                                                    |

| @ 50 Hz, 60 Hz <sup>2</sup>                | 100                                 | dB min      | 50 ± 1 Hz, FS[3:0] = 1001; 60 ± 1 Hz, FS[3:0] = 1000                                                                    |

| AD7794C                                    |                                     |             |                                                                                                                         |

| @ DC                                       | 97                                  | dB min      | AIN = 1 V/gain, with gain = 4, AMP-CM Bit = 1                                                                           |

| @ 50 Hz, 60 Hz <sup>2</sup>                | 97                                  | dB min      | $50 \pm 1$ Hz, $60 \pm 1$ Hz, FS[3:0] = 1010                                                                            |

| @ 50 Hz, 60 Hz <sup>2</sup>                | 97                                  | dB min      | $50 \pm 1$ Hz, FS[3:0] = 1001; $60 \pm 1$ Hz, FS[3:0] = 1000                                                            |

| CHOP ENABLED or DISABLED                   |                                     |             |                                                                                                                         |

| REFERENCE INPUT                            |                                     |             |                                                                                                                         |

| Internal Reference                         |                                     |             |                                                                                                                         |

| Internal Reference Initial<br>Accuracy     | 1.17 ± 0.01%                        | V min/max   | $AV_{DD} = 4 V, T_A = 25^{\circ}C$                                                                                      |

| Internal Reference Drift <sup>2</sup>      | 4                                   | ppm/°C typ  |                                                                                                                         |

|                                            | 15                                  | ppm/°C max  |                                                                                                                         |

| Power Supply Rejection                     | 85                                  | dB typ      |                                                                                                                         |

| External Reference                         |                                     |             |                                                                                                                         |

| External REFIN Voltage                     | 2.5                                 | V nom       | REFIN = REFIN(+) - REFIN(-)                                                                                             |

| Reference Voltage Range <sup>2</sup>       | 0.1                                 | V min       |                                                                                                                         |

|                                            | AV <sub>DD</sub>                    | V max       | When $V_{REF} = AV_{DD}$ , the differential input must be limited to $0.9 \times V_{REF}$ /gain if the in-amp is active |

| Absolute REFIN Voltage Limits <sup>2</sup> | GND – 30 mV                         | V min       | ······································                                                                                  |

| /                                          | $AV_{DD} + 30 \text{ mV}$           | V max       |                                                                                                                         |

| Average Reference Input<br>Current         | 400                                 | nA/V typ    |                                                                                                                         |

| Average Reference Input<br>Current Drift   | ±0.03                               | nA/V/°C typ |                                                                                                                         |

| Normal Mode Rejection <sup>2</sup>         |                                     |             | Same as for analog inputs                                                                                               |

| Common-Mode Rejection                      | 100                                 | dB typ      |                                                                                                                         |

| Reference Detect Levels                    | 0.3                                 | V min       |                                                                                                                         |

|                                            | 0.65                                | V max       | NOXREF bit active if $V_{REF} < 0.3 V$                                                                                  |

| EXCITATION CURRENT SOURCES                 |                                     |             |                                                                                                                         |

| (IEXC1 and IEXC2)                          |                                     |             |                                                                                                                         |

| Output Current                             | 10/210/1000                         | μA nom      |                                                                                                                         |

| Initial Tolerance at 25°C                  | ±5                                  | % typ       |                                                                                                                         |

| Drift                                      | 200                                 | ppm/°C typ  |                                                                                                                         |

| Current Matching                           | ±0.5                                | % typ       | Matching between IEXC1 and IEXC2, $V_{OUT} = 0 V$                                                                       |

| Drift Matching                             | 50                                  | ppm/°C typ  |                                                                                                                         |

| Line Regulation (AV <sub>DD</sub> )        | 2                                   | %/V typ     | $AV_{DD} = 5 V \pm 5\%$                                                                                                 |

| Load Regulation                            | 0.2                                 | %/V typ     |                                                                                                                         |

| Output Compliance                          | AV <sub>DD</sub> – 0.65             | V max       | Current sources programmed to 10 $\mu$ A or 210 $\mu$ A                                                                 |

| output compliance                          | $AV_{DD} = 0.05$<br>$AV_{DD} = 1.1$ | V max       | Current sources programmed to 1 mA                                                                                      |

|                                            | GND – 30 mV                         | V min       |                                                                                                                         |

| Parameter <sup>1</sup>                             | AD7794/AD7795          | Unit      | Test Conditions/Comments                                             |

|----------------------------------------------------|------------------------|-----------|----------------------------------------------------------------------|

| BIAS VOLTAGE GENERATOR                             |                        |           |                                                                      |

| V <sub>BIAS</sub>                                  | AV <sub>DD</sub> /2    | V nom     |                                                                      |

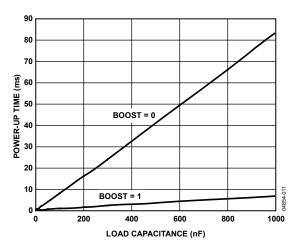

| V <sub>BIAS</sub> Generator Start-Up Time          |                        | ms/nF typ | Dependent on the capacitance connected to AIN;                       |

| -                                                  |                        |           | See Figure 11                                                        |

| TEMPERATURE SENSOR                                 |                        |           |                                                                      |

| Accuracy                                           | ±2                     | °C typ    | Applies if user calibrates the temperature sensor                    |

| Sensitivity                                        | 0.81                   | mV/°C typ |                                                                      |

| LOW-SIDE POWER SWITCH                              |                        |           |                                                                      |

| Ron                                                | 7                      | Ωmax      | $AV_{DD} = 5 V$                                                      |

|                                                    | 9                      | Ωmax      | $AV_{DD} = 3 V$                                                      |

| Allowable Current <sup>2</sup>                     | 30                     | mA max    | Continuous current                                                   |

| DIGITAL OUTPUTS (P1 and P2)                        |                        |           |                                                                      |

| V <sub>OH</sub> , Output High Voltage <sup>2</sup> | AV <sub>DD</sub> - 0.6 | V min     | $AV_{DD} = 3 V$ , $I_{SOURCE} = 100 \mu A$                           |

| V <sub>OL</sub> , Output Low Voltage <sup>2</sup>  | 0.4                    | V max     | $AV_{DD} = 3 \text{ V}, \text{ I}_{\text{SINK}} = 100 \ \mu\text{A}$ |

| V <sub>он</sub> , Output High Voltage <sup>2</sup> | 4                      | V min     | $AV_{DD} = 5 V$ , $I_{SOURCE} = 200 \mu A$                           |

| V <sub>OL</sub> , Output Low Voltage <sup>2</sup>  | 0.4                    | V max     | $AV_{DD} = 5 V$ , $I_{SINK} = 800 \mu A$                             |

| INTERNAL/EXTERNAL CLOCK                            |                        |           |                                                                      |

| Internal Clock                                     |                        |           |                                                                      |

| Frequency <sup>2</sup>                             | 64 ± 3%                | kHz       |                                                                      |

| requercy                                           | 012070                 | min/max   |                                                                      |

| Duty Cycle                                         | 50:50                  | % typ     |                                                                      |

| External Clock                                     |                        |           |                                                                      |

| Frequency                                          | 64                     | kHz nom   | A 128 kHz external clock can be used if the divide-by-2              |

|                                                    | •••                    |           | function is used (Bit CLK1 = CLK0 = 1)                               |

| Duty Cycle                                         | 45:55 to 55:45         | % typ     | Applies for external 64 kHz clock, a 128 kHz clock can               |

|                                                    |                        |           | have a less stringent duty cycle                                     |

| LOGIC INPUTS                                       |                        |           |                                                                      |

| $\overline{CS}^2$                                  |                        |           |                                                                      |

| V <sub>INL</sub> , Input Low Voltage               | 0.8                    | V max     | $DV_{DD} = 5 V$                                                      |

|                                                    | 0.4                    | V max     | $DV_{DD} = 3 V$                                                      |

| V <sub>INH</sub> , Input High Voltage              | 2.0                    | V min     | $DV_{DD} = 3 V \text{ or } 5 V$                                      |

| SCLK (Schmitt-Triggered Input),                    |                        |           |                                                                      |

| CLK, and DIN <sup>2</sup>                          |                        |           |                                                                      |

| AD7794B/AD7795B                                    |                        |           |                                                                      |

| $V_{T}(+)$                                         | 1.4/2                  | V min/max | $DV_{DD} = 5 V$                                                      |

| V <sub>T</sub> (-)                                 | 0.8/1.7                | V min/max | $DV_{DD} = 5 V$                                                      |

| V <sub>T</sub> (+) to V <sub>T</sub> (–)           | 0.1/0.17               | V min/max | $DV_{DD} = 5 V$                                                      |

| V <sub>T</sub> (+)                                 | 0.9/2                  | V min/max | $DV_{DD} = 3 V$                                                      |

| V <sub>T</sub> (-)                                 | 0.4/1.35               | V min/max | $DV_{DD} = 3 V$                                                      |

| V <sub>T</sub> (+) to V <sub>T</sub> (–)           | 0.06/0.13              | V min/max | $DV_{DD} = 3 V$                                                      |

| AD7794C                                            |                        |           |                                                                      |

| V <sub>T</sub> (+)                                 | 1.35/2.05              | V min/max | $DV_{DD} = 5 V$                                                      |

| V <sub>T</sub> ()                                  | 0.8/1.9                | V min/max | $DV_{DD} = 5 V$                                                      |

| V <sub>T</sub> (+) to V <sub>T</sub> (–)           | 0.1/0.19               | V min/max | $DV_{DD} = 5 V$                                                      |

| V <sub>T</sub> (+)                                 | 0.9/2                  | V min/max | $DV_{DD} = 3 V$                                                      |

| V <sub>T</sub> (-)                                 | 0.4/1.35               | V min/max | $DV_{DD} = 3 V$                                                      |

| $V_{T}(+)$ to $V_{T}(-)$                           | 0.06/0.15              | V min/max | $DV_{DD} = 3 V$                                                      |

| Input Currents                                     | ±10                    | μA max    | $V_{\rm IN} = DV_{\rm DD}$ or GND                                    |

| Input Capacitance                                  | 10                     | pF typ    | All digital inputs                                                   |

| Parameter <sup>1</sup>                             | AD7794/AD7795          | Unit      | Test Conditions/Comments                                                                                                                |

|----------------------------------------------------|------------------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------|

| LOGIC OUTPUT (INCLUDING CLK)                       |                        |           |                                                                                                                                         |

| V <sub>OH</sub> , Output High Voltage <sup>2</sup> | DV <sub>DD</sub> - 0.6 | V min     | $DV_{DD} = 3 V$ , $I_{SOURCE} = 100 \mu A$                                                                                              |

| Vol, Output Low Voltage <sup>2</sup>               | 0.4                    | V max     | $DV_{DD} = 3 V$ , $I_{SINK} = 100 \mu A$                                                                                                |

| V <sub>OH</sub> , Output High Voltage <sup>2</sup> | 4                      | V min     | $DV_{DD} = 5 V$ , $I_{SOURCE} = 200 \mu A$                                                                                              |

| Vol, Output Low Voltage <sup>2</sup>               | 0.4                    | V max     | $DV_{DD} = 5 \text{ V}, I_{SINK} = 1.6 \text{ mA} (DOUT/\overline{RDY}), 800 \ \mu\text{A} (CLK)$                                       |

| Floating-State Leakage Current                     | ±10                    | μA max    |                                                                                                                                         |

| Floating-State Output Capacitance                  | 10                     | pF typ    |                                                                                                                                         |

| Data Output Coding                                 | Offset binary          |           |                                                                                                                                         |

| SYSTEM CALIBRATION <sup>2</sup>                    |                        |           |                                                                                                                                         |

| Full-Scale Calibration Limit                       | 1.05 × FS              | V max     |                                                                                                                                         |

| Zero-Scale Calibration Limit                       | $-1.05 \times FS$      | V min     |                                                                                                                                         |

| Input Span                                         | $0.8 \times FS$        | V min     |                                                                                                                                         |

|                                                    | $2.1 \times FS$        | V max     |                                                                                                                                         |

| POWER REQUIREMENTS <sup>7</sup>                    |                        |           |                                                                                                                                         |

| Power Supply Voltage                               |                        |           |                                                                                                                                         |

| AV <sub>DD</sub> to GND                            | 2.7/5.25               | V min/max |                                                                                                                                         |

| DVDD to GND                                        | 2.7/5.25               | V min/max |                                                                                                                                         |

| Power Supply Currents                              |                        |           |                                                                                                                                         |

| IDD Current                                        | 140                    | μA max    | 110 $\mu$ A typ @ AV <sub>DD</sub> = 3 V, 125 $\mu$ A typ @ AV <sub>DD</sub> = 5 V, unbuffered mode, external reference                 |

|                                                    | 185                    | μA max    | 130 $\mu$ A typ @ AV <sub>DD</sub> = 3 V, 165 $\mu$ A typ @ AV <sub>DD</sub> = 5 V,<br>buffered mode, gain = 1 or 2, external reference |

|                                                    | 400                    | μA max    | 300 $\mu$ A typ @ AV <sub>DD</sub> = 3 V, 350 $\mu$ A typ @ AV <sub>DD</sub> = 5 V, gain = 4 to 128, external reference                 |

|                                                    | 500                    | μA max    | 400 $\mu$ A typ @ AV <sub>DD</sub> = 3 V, 450 $\mu$ A typ @ AV <sub>DD</sub> = 5 V, gain = 4 to 128, internal reference                 |

| I <sub>DD</sub> (Power-Down Mode)                  | 1                      | μA max    | AD7794B, AD7795B                                                                                                                        |

|                                                    | 2                      | μA max    | AD7794C                                                                                                                                 |

<sup>1</sup> Temperature range: B Grade: -40°C to +105°C, C Grade: -40°C to +125°C. At the 19.6 Hz and 39.2 Hz update rates, the INL, power supply rejection (PSR), commonmode rejection (CMR), and normal mode rejection (NMR) do not meet the data sheet specification if the voltage on the AIN(+) or AIN(-) pins exceeds AV<sub>DD</sub> – 1.6 V typically. In addition, the offset error and offset error drift degrade at these update rates when chopping is disabled. When this voltage is exceeded, the INL, for example, is reduced to 18 ppm of FS typically while the PSR is reduced to 69 dB typically. Therefore, for guaranteed performance at these update rates, the absolute voltage on the analog input pins needs to be below AVDD – 1.6 V.

<sup>2</sup> Specification is not production tested but is supported by characterization data at initial product release.

<sup>3</sup> Following a calibration, this error is in the order of the noise for the programmed gain and update rate selected.

<sup>4</sup> Recalibration at any temperature removes these errors.

<sup>5</sup> Full-scale error applies to both positive and negative full-scale, and applies at the factory calibration conditions (AV<sub>DD</sub> = 4 V, gain = 1, T<sub>A</sub> = 25°C).

<sup>6</sup> FS[3:0] are the four bits used in the mode register to select the output word rate.

<sup>7</sup> Digital inputs equal to DV<sub>DD</sub> or GND with excitation currents and bias voltage generator disabled.

## TIMING CHARACTERISTICS

$AV_{DD} = 2.7$  V to 5.25 V,  $DV_{DD} = 2.7$  V to 5.25 V, GND = 0 V, Input Logic 0 = 0 V, Input Logic  $1 = DV_{DD}$ , unless otherwise noted.

#### Table 2.

| Parameter <sup>1, 2</sup>   | Limit at T <sub>MIN</sub> , T <sub>MAX</sub> (B Version) | Unit   | Conditions/Comments                                         |

|-----------------------------|----------------------------------------------------------|--------|-------------------------------------------------------------|

| t <sub>3</sub>              | 100                                                      | ns min | SCLK high pulse width                                       |

| t4                          | 100                                                      | ns min | SCLK low pulse width                                        |

| Read Operation              |                                                          |        |                                                             |

| t1                          | 0                                                        | ns min | CS falling edge to DOUT/RDY active time                     |

|                             | 60                                                       | ns max | $DV_{DD} = 4.75 V$ to 5.25 V                                |

|                             | 80                                                       | ns max | $DV_{DD} = 2.7 V \text{ to } 3.6 V$                         |

| t <sub>2</sub> <sup>3</sup> | 0                                                        | ns min | SCLK active edge to data valid delay <sup>4</sup>           |

|                             | 60                                                       | ns max | $DV_{DD} = 4.75 V \text{ to } 5.25 V$                       |

|                             | 80                                                       | ns max | $DV_{DD} = 2.7 V \text{ to } 3.6 V$                         |

| t5 <sup>5,6</sup>           | 10                                                       | ns min | Bus relinquish time after CS inactive edge                  |

|                             | 80                                                       | ns max |                                                             |

| t <sub>6</sub>              | 0                                                        | ns min | SCLK inactive edge to CS inactive edge                      |

| t <sub>7</sub>              | 10                                                       | ns min | SCLK inactive edge to DOUT/RDY high                         |

| Write Operation             |                                                          |        |                                                             |

| t <sub>8</sub>              | 0                                                        | ns min | CS falling edge to SCLK active edge setup time <sup>4</sup> |

| t9                          | 30                                                       | ns min | Data valid to SCLK edge setup time                          |

| <b>t</b> 10                 | 25                                                       | ns min | Data valid to SCLK edge hold time                           |

| t11                         | 0                                                        | ns min | CS rising edge to SCLK edge hold time                       |

<sup>1</sup> Sample tested during initial release to ensure compliance. All input signals are specified with  $t_R = t_F = 5$  ns (10% to 90% of DV<sub>DD</sub>) and timed from a voltage level of 1.6 V. <sup>2</sup> See Figure 3 and Figure 4.

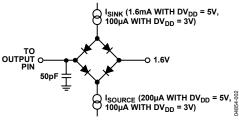

<sup>3</sup> These numbers are measured with the load circuit shown in Figure 2 and defined as the time required for the output to cross the  $V_{OL}$  or  $V_{OH}$  limits.

<sup>4</sup> SCLK active edge is falling edge of SCLK.

<sup>5</sup> These numbers are derived from the measured time taken by the data output to change 0.5 V when loaded with the circuit shown in Figure 2. The measured number is then extrapolated back to remove the effects of charging or discharging the 50 pF capacitor. This means that the times quoted in the timing characteristics are the true bus relinquish times of the part and, therefore, are independent of external bus loading capacitances.

<sup>6</sup> RDY returns high after a read of the ADC. In single conversion mode and continuous conversion mode, the same data can be read again, if required, while RDY is high, although care should be taken to ensure that subsequent reads do not occur close to the next output update. In continuous read mode, the digital word can be read only once.

Figure 2. Load Circuit for Timing Characterization

# TIMING DIAGRAMS

### **ABSOLUTE MAXIMUM RATINGS**

$T_A = 25^{\circ}$ C, unless otherwise noted.

#### Table 3.

| Parameter                       | Rating                              |

|---------------------------------|-------------------------------------|

| AV <sub>DD</sub> to GND         | –0.3 V to +7 V                      |

| DV <sub>DD</sub> to GND         | –0.3 V to +7 V                      |

| Analog Input Voltage to GND     | $-0.3$ V to AV_{\text{DD}} + 0.3 V  |

| Reference Input Voltage to GND  | $-0.3$ V to AV_{\text{DD}} + 0.3 V  |

| Digital Input Voltage to GND    | $-0.3V$ to $DV_{\text{DD}}$ + 0.3 V |

| Digital Output Voltage to GND   | -0.3 V to DV <sub>DD</sub> + 0.3 V  |

| AIN/Digital Input Current       | 10 mA                               |

| Operating Temperature Range     |                                     |

| B Grade                         | -40°C to +105°C                     |

| C Grade                         | -40°C to +125°C                     |

| Storage Temperature Range       | –65°C to +150°C                     |

| Maximum Junction Temperature    | 150°C                               |

| TSSOP                           |                                     |

| $\theta_{JA}$ Thermal Impedance | 97.9°C/W                            |

| $\theta_{JC}$ Thermal Impedance | 14°C/W                              |

| Lead Temperature, Soldering     |                                     |

| Vapor Phase (60 sec)            | 215°C                               |

| Infrared (15 sec)               | 220°C                               |

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those listed in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

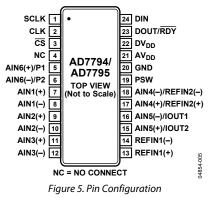

# **PIN CONFIGURATION AND FUNCTION DESCRIPTIONS**

#### **Table 4. Pin Function Descriptions**

| Pin No. | Mnemonic          | Description                                                                                                                                                                                                                                                                                                                                                                                                                               |

|---------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | SCLK              | Serial Clock Input. This serial clock input is for data transfers to and from the ADC. The SCLK has a Schmitt-<br>triggered input, making the interface suitable for opto-isolated applications. The serial clock can be<br>continuous with all data transmitted in a continuous train of pulses. Alternatively, it can be a noncontinuous<br>clock with the information being transmitted to or from the ADC in smaller batches of data. |

| 2       | CLK               | Clock In/Clock Out. The internal clock can be made available at this pin. Alternatively, the internal clock can be disabled, and the ADC can be driven by an external clock. This allows several ADCs to be driven from a common clock, allowing simultaneous conversions to be performed.                                                                                                                                                |

| 3       | <u>c</u>          | Chip Select Input. This is an active low logic input used to select the ADC. $\overline{CS}$ can be used to select the ADC in systems with more than one device on the serial bus or as a frame synchronization signal in communicating with the device. $\overline{CS}$ can be hardwired low, allowing the ADC to operate in 3-wire mode with SCLK, DIN, and DOUT used to interface with the device.                                     |

| 4       | NC                | No Connect.                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 5       | AIN6(+)/P1        | Analog Input/Digital Output Pin. AIN6(+) is the positive terminal of the differential analog input pair, AIN6(+)/AIN6(–). This pin can also function as a general-purpose output bit referenced between AV <sub>DD</sub> and GND.                                                                                                                                                                                                         |

| 6       | AIN6(-)/P2        | Analog Input/Digital Output Pin. AIN6(–) is the negative terminal of the differential analog input pair, AIN6(+)/AIN6(–). This pin can also function as a general-purpose output bit referenced between AV <sub>DD</sub> and GND.                                                                                                                                                                                                         |

| 7       | AIN1(+)           | Analog Input. AIN1(+) is the positive terminal of the differential analog input pair, AIN1(+)/AIN1(–).                                                                                                                                                                                                                                                                                                                                    |

| 8       | AIN1(-)           | Analog Input. AIN1(–) is the negative terminal of the differential analog input pair, AIN1(+)/AIN1(–).                                                                                                                                                                                                                                                                                                                                    |

| 9       | AIN2(+)           | Analog Input. AIN2(+) is the positive terminal of the differential analog input pair, AIN2(+)/AIN2(–).                                                                                                                                                                                                                                                                                                                                    |

| 10      | AIN2(-)           | Analog Input. AIN2(–) is the negative terminal of the differential analog input pair, AIN2(+)/AIN2(–).                                                                                                                                                                                                                                                                                                                                    |

| 11      | AIN3(+)           | Analog Input. AIN3(+) is the positive terminal of the differential analog input pair, AIN3(+)/AIN3(–).                                                                                                                                                                                                                                                                                                                                    |

| 12      | AIN3(–)           | Analog Input. AIN3(–) is the negative terminal of the differential analog input pair, AIN3(+)/AIN3(–).                                                                                                                                                                                                                                                                                                                                    |

| 13      | REFIN1(+)         | Positive Reference Input. An external reference can be applied between REFIN1(+) and REFIN1(-). REFIN1(+) can lie anywhere between AV <sub>DD</sub> and GND + 0.1 V. The nominal reference voltage, (REFIN1(+) – REFIN1(-)), is 2.5 V, but the part functions with a reference from 0.1 V to AV <sub>DD</sub> .                                                                                                                           |

| 14      | REFIN1(-)         | Negative Reference Input. This reference input can lie anywhere between GND and $AV_{DD} - 0.1$ V.                                                                                                                                                                                                                                                                                                                                        |

| 15      | AIN5(+)/IOUT2     | Analog Input/Output of Internal Excitation Current Source. AIN5(+) is the positive terminal of the differential analog input pair AIN5(+)/AIN5(–). Alternatively, the internal excitation current source can be made available at this pin and is programmable so that the current can be 10 $\mu$ A, 210 $\mu$ A, or 1 mA. Either IEXC1 or IEXC2 can be switched to this output.                                                         |

| 16      | AIN5(-)/IOUT1     | Analog Input/Output of Internal Excitation Current Source. AIN5(–) is the negative terminal of the differential analog input pair, AIN5(+)/AIN5(–). Alternatively, the internal excitation current source can be made available at this pin and is programmable so that the current can be 10 μA, 210 μA, or 1 mA. Either IEXC1 or IEXC2 can be switched to this output.                                                                  |

| 17      | AIN4(+)/REFIN2(+) | Analog Input/Positive Reference Input. AIN4(+) is the positive terminal of the differential analog input pair AIN4(+)/AIN4(-). This pin also functions as a positive reference input for REFIN2. REFIN2(+) can lie anywhere between AV <sub>DD</sub> and GND + 0.1 V. The nominal reference voltage (REFIN2(+) to REFIN2(-)) is 2.5 V, but the part functions with a reference from 0.1 V to AV <sub>DD</sub> .                           |

| Pin No. | Mnemonic          | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|---------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 18      | AIN4(-)/REFIN2(-) | Analog Input/Negative Reference Input. AIN4(–) is the negative terminal of the differential analog input pair AIN4(+)/AIN4(–). This pin also functions as the negative reference input for REFIN2. This reference input can lie anywhere between GND and AV <sub>DD</sub> – 0.1 V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 19      | PSW               | Low-Side Power Switch to GND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 20      | GND               | Ground Reference Point.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 21      | AV <sub>DD</sub>  | Supply Voltage, 2.7 V to 5.25 V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 22      | DV <sub>DD</sub>  | Serial Interface Supply Voltage, 2.7 V to 5.25 V. $DV_{DD}$ is independent of $AV_{DD}$ . Therefore, the serial interface operates at 3 V with $AV_{DD}$ at 5 V or vice versa.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 23      | DOUT/RDY          | Serial Data Output/Data Ready Output. DOUT/RDY serves a dual purpose. It functions as a serial data output pin to access the output shift register of the ADC. The output shift register can contain data from any of the on-chip data or control registers. In addition, DOUT/RDY operates as a data ready pin, going low to indicate the completion of a conversion. If the data is not read after the conversion, the pin goes high before the next update occurs. The DOUT/RDY falling edge can also be used as an interrupt to a processor, indicating that valid data is available. With an external serial clock, the data can be read using the DOUT/RDY pin. With CS low, the data/control word information is placed on the DOUT/RDY pin on the SCLK falling edge and is valid on the SCLK rising edge. |

| 24      | DIN               | Serial Data Input to the Input Shift Register on the ADC. Data in this shift register is transferred to the control registers within the ADC with the register selection bits of the communications register identifying the appropriate register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

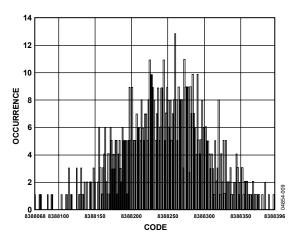

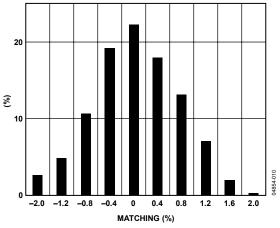

# **RMS NOISE AND RESOLUTION SPECIFICATIONS**