Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# 500 MHz, G = +1 and +2 Triple Video Buffers with Disable

# AD8074/AD8075

#### **FEATURES**

Dual Supply ±5 V **High-Speed Fully Buffered Inputs and Outputs** 600 MHz Bandwidth (-3 dB) 200 mV p-p 500 MHz Bandwidth (-3 dB) 2 V p-p 1600 V/ $\mu$ s Slew Rate, G = +1 1350 V/ $\mu$ s Slew Rate, G = +2 Fast Settling Time: 4 ns Low Supply Current: <30 mA Excellent Video Specifications ( $R_1 = 150 \Omega$ ): Gain Flatness of 0.1 dB to 50 MHz 0.01% Differential Gain Error 0.01° Differential Phase Error "All Hostile" Crosstalk -80 dB @ 10 MHz -50 dB @ 100 MHz High "OFF" Isolation of 90 dB @ 10 MHz **Low Cost Fast Output Disable Feature APPLICATIONS RGB Buffer in LCD and Plasma Displays**

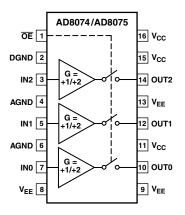

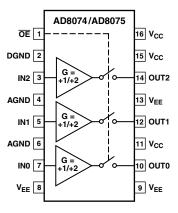

#### FUNCTIONAL BLOCK DIAGRAM

#### PRODUCT DESCRIPTION

RGB Driver Video Routers

The AD8074/AD8075 are high-speed triple video buffers with G = +1 and +2 respectively. They have a -3 dB full signal bandwidth in excess of 450 MHz, along with slew rates in excess of 1400 V/ $\mu$ s. With better than -80 dB of all hostile crosstalk and 90 dB isolation, they are useful in many high-speed applications. The differential gain and differential phase error are 0.01% and 0.01°. Gain flatness of 0.1 dB up to 50 MHz makes the AD8074/AD8075 ideal for RGB buffering or driving. They consume less than 30 mA on a  $\pm 5$  V supply.

Both devices offer a high-speed disable feature that allows the outputs to be put into a high impedance state. This allows the building of larger input arrays while minimizing "OFF" channel output loading. The AD8074/AD8075 are offered in a 16-lead TSSOP package.

Table I. Truth Table

| <del>OE</del> | OUT0, 1, 2    |

|---------------|---------------|

| 0             | IN0, IN1, IN2 |

| 1             | High Z        |

# $\label{eq:AD8074} AD8075 — SPECIFICATIONS \ (T_A = 25^{\circ}C, \ V_S = \pm 5 \ V, \ unless \ otherwise \ noted.)$

| Parameter                             | Conditions                                                                 | Min                    | Typ               | Max                 | Unit      |

|---------------------------------------|----------------------------------------------------------------------------|------------------------|-------------------|---------------------|-----------|

| DYNAMIC PERFORMANCE                   |                                                                            |                        |                   |                     |           |

| -3 dB Bandwidth (Small Signal)        | $V_{IN} = 200 \text{ mV p-p, } C_L = 5 \text{ pF}$                         | 330/310                | 600/550           |                     | MHz       |

| ` ' '                                 | $V_{IN} = 200 \text{ mV p-p}, R_L = 150 \Omega$                            | 250/230                | 400/400           |                     | MHz       |

| -3 dB Bandwidth (Large Signal)        | $V_{IN} = 2 \text{ V p-p, } C_L = 5 \text{ pF}$                            | 330/300                | 500/500           |                     | MHz       |

| \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ | $V_{IN} = 2 \text{ V p-p}, R_L = 150 \Omega$                               | 250/230                | 350/350           |                     | MHz       |

| 0.1 dB Bandwidth                      | $V_{IN} = 200 \text{ mV p-p, } C_{L} = 5 \text{ pF}$                       |                        | 70/65             |                     | MHz       |

|                                       | $V_{IN} = 200 \text{ mV p-p}, R_L = 150 \Omega$                            |                        | 70/65             |                     | MHz       |

| Slew Rate                             | 2 V Step, $R_L = 1 k\Omega/150 \Omega$                                     |                        | 1600/1350         |                     | V/µs      |

| Settling Time to 0.1%                 | 2 V Step, $R_L = 1 k\Omega/150 \Omega$                                     |                        | 4/7.5             |                     | ns        |

| NOISE/DISTORTION PERFORMANCE          |                                                                            |                        |                   |                     |           |

| Differential Gain                     | $V = 3.58 \text{ MHz}, 150 \Omega$                                         |                        | 0.01              |                     | %         |

| Differential Phase                    | $V = 3.58 \text{ MHz}, 150 \Omega$                                         |                        | 0.01              |                     | Degree    |

| All Hostile Crosstalk                 | $V = 10 \text{ MHz}, R_L = 1 \text{ k}\Omega$                              |                        | -80/-74           |                     | dB        |

| Im Hoome Grosswan                     | $V = 100 \text{ MHz}, R_L = 1 \text{ k}\Omega$                             |                        | -50/-44           |                     | dB        |

| OFF Isolation                         | $V = 10 \text{ MHz}, R_L = 150 \Omega$                                     |                        | 90                |                     | dB        |

| Voltage Noise                         | V= 10 kHz to 100 MHz                                                       |                        | 19.5/22           |                     | nV/√Hz    |

|                                       |                                                                            |                        |                   |                     |           |

| DC PERFORMANCE                        | N. T. and                                                                  |                        | 101/102           | 10.15/10.65         | 0/        |

| Voltage Gain Error                    | No Load                                                                    |                        | $\pm 0.1/\pm 0.2$ | $\pm 0.15/\pm 0.65$ | %         |

| Input Offset Voltage                  | T T.                                                                       |                        | 2.5               | 27/40               | mV        |

| I                                     | ${ m T_{MIN}}$ to ${ m T_{MAX}}$                                           |                        | 3                 |                     | mV        |

| Input Offset Drift                    |                                                                            |                        | 10                | 0.5/10              | μV/°C     |

| Input Bias Current                    |                                                                            |                        | 5                 | 9.5/10              | μA        |

| INPUT CHARACTERISTICS                 |                                                                            |                        |                   |                     |           |

| Input Resistance                      |                                                                            |                        | 10                |                     | $M\Omega$ |

| Input Capacitance                     | Channel Enabled                                                            |                        | 1.5               |                     | pF        |

|                                       | Channel Disabled                                                           |                        | 1.5               |                     | pF        |

| Input Voltage Range                   |                                                                            |                        | $\pm 2.8/\pm 1.4$ |                     | V         |

| OUTPUT CHARACTERISTICS                |                                                                            |                        |                   |                     |           |

| Output Voltage Swing                  | $R_L = 1 \text{ k}\Omega$                                                  | +V <sub>S</sub> - 1.95 | $+V_{S}-1.8$      |                     | V         |

|                                       |                                                                            | $-V_S + 2.1$           |                   |                     | V         |

|                                       | $R_L = 150 \Omega$                                                         | $+V_S - 2.35$          | $+V_S - 2.2$      |                     | V         |

|                                       |                                                                            | $-V_S + 2.30$          | $-V_S + 2.2$      |                     | V         |

| Short Circuit Current (Protected)     |                                                                            |                        | 70                |                     | mA        |

| Output Resistance                     | Enabled                                                                    |                        | 0.5               |                     | Ω         |

|                                       | Disabled                                                                   | 3.5                    | 7.5               |                     | ΜΩ        |

| Output Capacitance                    | Disabled                                                                   |                        | 2.2               |                     | pF        |

| POWER SUPPLY                          |                                                                            |                        |                   |                     |           |

| Operating Range                       |                                                                            | ±4.5                   |                   | ±5.5                | V         |

| Power Supply Rejection Ratio          | +PSRR: $+V_S = +4.5 \text{ V}$ to $+5.5 \text{ V}$ , $-V_S = -5 \text{ V}$ | 60                     | 74                |                     | dB        |

|                                       | $-PSRR: -V_S = -4.5 \text{ V to } -5.5 \text{ V}, +V_S = +5 \text{ V}$     | 56                     | 64                |                     | dB        |

| Quiescent Current                     | All Channels "ON"                                                          |                        | 21.5/24           | 30                  | mA        |

|                                       | All Channels "OFF"                                                         |                        | 3/4               | 5.5                 | mA        |

|                                       | $\mathrm{T_{MIN}}$ to $\mathrm{T_{MAX}}$                                   |                        | 23/26             |                     | mA        |

| DIGITAL INPUT                         |                                                                            |                        |                   |                     |           |

| Logic "1" Voltage                     | OE Input                                                                   | 2.0                    |                   |                     | v         |

| Logic "0" Voltage                     | OE Input                                                                   |                        |                   | 0.8                 | v         |

| Logic "1" Input Current               | $\frac{\partial E}{\partial E} = 4 \text{ V}$                              |                        | 100               | 3.0                 | nA        |

| Logic "0" Input Current               | $\frac{\partial E}{\partial E} = 0.4 \text{ V}$                            |                        | 1                 |                     | μA        |

| OPERATING TEMPERATURE RANGE           |                                                                            |                        |                   |                     | •         |

|                                       | Operating (Still Air)                                                      | 40                     |                   | 105                 | °C        |

| Temperature Range                     | Operating (Still Air)                                                      | -40                    | 150.4             | +85                 | _         |

| $\theta_{ m JA}$                      | Operating (Still Air)                                                      |                        | 150.4             |                     | °C/W      |

| $	heta_{ m JC}$                       | Operating                                                                  |                        | 27.6              |                     | °C/W      |

Specifications subject to change without notice.

-2- Rev. B

#### ABSOLUTE MAXIMUM RATINGS<sup>1</sup>

| Supply Voltage                                                        |

|-----------------------------------------------------------------------|

| Internal Power Dissipation <sup>2, 3</sup>                            |

| AD8074/AD8075 16-Lead TSSOP (RU) 1 W                                  |

| Input Voltage                                                         |

| IN0, IN1, IN2 $V_{EE} \le V_{IN} \le V_{CC}$                          |

| $\overline{\text{OE}}$ $DGND \le V_{IN} \le V_{CC}$                   |

| Output Short Circuit Duration Indefinite <sup>3</sup>                 |

| Storage Temperature Range $\ \dots \ -65^{\circ}C$ to $+150^{\circ}C$ |

| Lead Temperature Range (Soldering 10 sec) 300°C                       |

| NOTES                                                                 |

<sup>1</sup>Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

<sup>2</sup>Specification is for device in free air ( $T_A = 25$ °C).

#### PIN CONFIGURATION

#### CAUTION\_

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although the AD8074/AD8075 features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high-energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

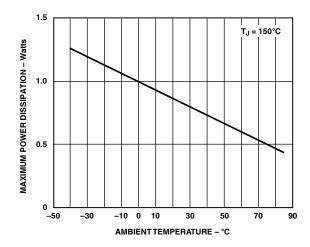

#### MAXIMUM POWER DISSIPATION

The maximum power that can be safely dissipated by the AD8074/ AD8075 is limited by the associated rise in junction temperature. The maximum safe junction temperature for plastic encapsulated devices is determined by the glass transition temperature of the plastic, approximately 150°C. Temporarily exceeding this limit may cause a shift in parametric performance due to a change in the stresses exerted on the die by the package. Exceeding a junction temperature of 175°C for an extended period can result in device failure.

While the AD8074/AD8075 is internally short circuit protected, this may not be sufficient to guarantee that the maximum junction temperature (150°C) is not exceeded under all conditions. To ensure proper operation, it is necessary to observe the maximum power derating curves shown in Figure 1.

Figure 1. Maximum Power Dissipation vs. Temperature

Rev. B -3-

$<sup>^3\</sup>text{16}\text{-lead plastic TSSOP}; \, \theta_{JA} = 150.4^\circ\text{C/W}.$  Maximum internal power dissipation  $(P_D)$  should be derated for ambient temperature  $(T_A)$  such that  $P_D < (150^\circ\text{C} - T_A)/\theta_{JA}.$

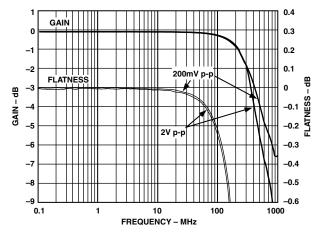

# **AD8074/AD8075—Typical Performance Characteristics**

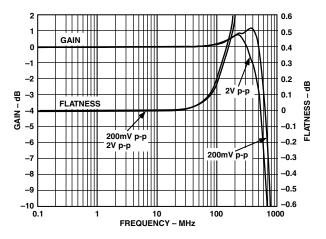

TPC 1. AD8074 Frequency Response;  $R_L = 150 \Omega$

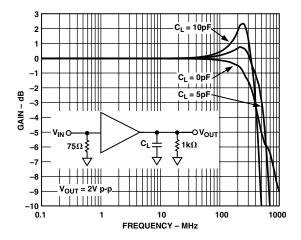

TPC 2. AD8074 Frequency Response;  $R_L = 1 \text{ k}\Omega$ ,  $C_L = 5 \text{ pF}$

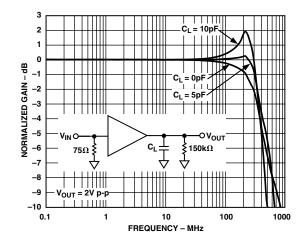

TPC 3. AD8074 Frequency Response vs. Capacitive Load

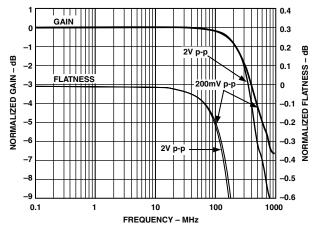

TPC 4. AD8075 Frequency Response;  $R_L = 150 \Omega$

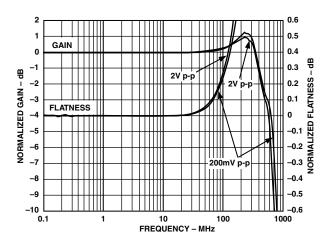

TPC 5. AD8075 Frequency Response;  $R_L = 1 \text{ k}\Omega$ ,  $C_L = 5 \text{ pF}$

TPC 6. AD8075 Frequency Response vs. Capacitive Load

-4- Rev. B

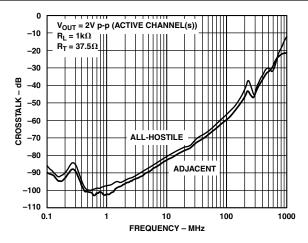

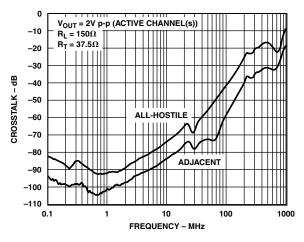

TPC 7. AD8074 Crosstalk vs. Frequency (All Hostile and Adjacent  $R_L=1~k\Omega$ )

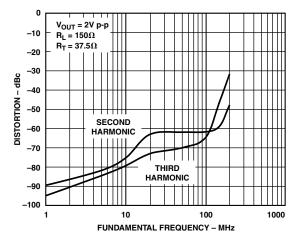

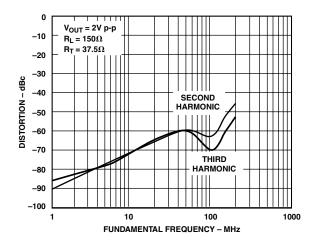

TPC 8. AD8074 Distortion vs. Frequency

TPC 9. AD8075 Crosstalk vs. Frequency (All Hostile and Adjacent  $R_L = 150~\Omega$ )

TPC 10. AD8075 Distortion vs. Frequency

Rev. B –5–

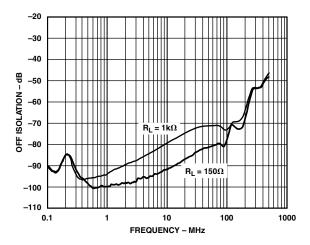

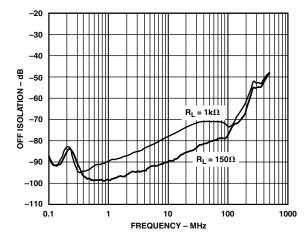

TPC 11. AD8074 Off Isolation vs. Frequency

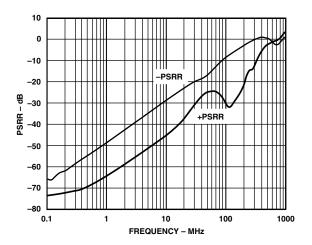

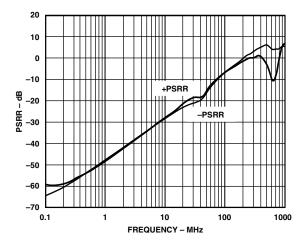

TPC 12. AD8074 PSRR vs. Frequency

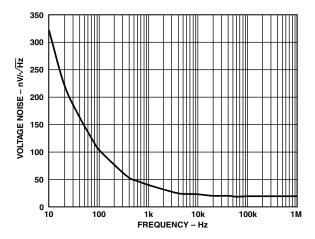

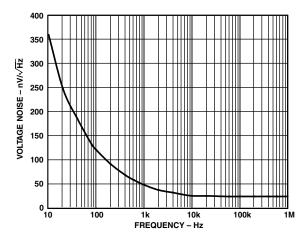

TPC 13. AD8074 Voltage Noise vs. Frequency

TPC 14. AD8075 Off Isolation vs. Frequency

TPC 15. AD8075 PSRR vs. Frequency

TPC 16. AD8075 Voltage Noise vs. Frequency

-6- Rev. B

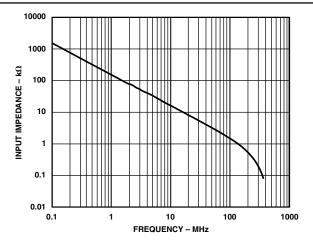

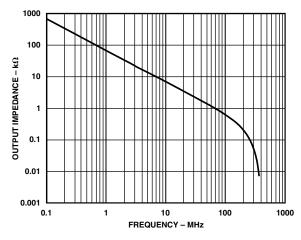

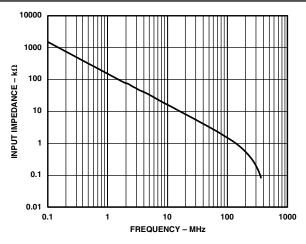

TPC 17. AD8074 Input Impedance vs. Frequency

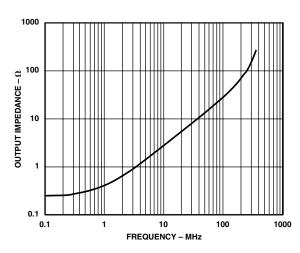

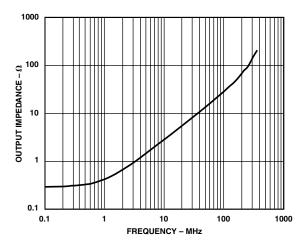

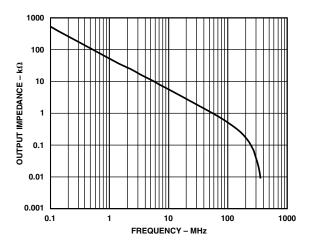

TPC 18. AD8074 Output Impedance vs. Frequency; Enabled

TPC 19. AD8074 Output Impedance vs. Frequency; Disabled

TPC 20. AD8075 Input Impedance vs. Frequency

TPC 21. AD8075 Output Impedance vs. Frequency; Enabled

TPC 22. AD8075 Output Impedance vs. Frequency; Disabled

Rev. B -7-

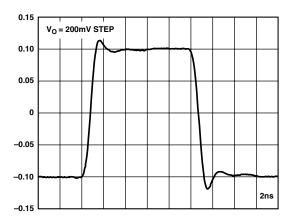

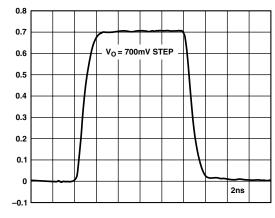

TPC 23. AD8074 Small Signal Pulse Response (R<sub>L</sub> = 1 k $\Omega$ , C<sub>L</sub> = 5 pF)

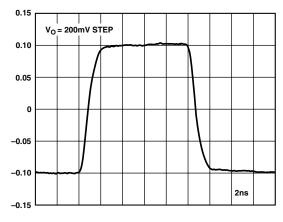

TPC 26. AD8075 Small Signal Pulse Response ( $R_L = 150 \text{ k}\Omega$ )

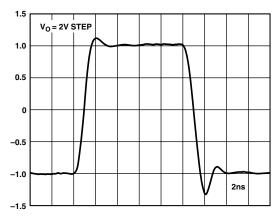

TPC 24. AD8074 Video Amplitude Pulse Response ( $R_L = 1 \text{ k}\Omega$ ,  $C_L = 5 \text{ pF}$ )

TPC 27. AD8075 Video Amplitude Pulse Response ( $R_L = 150~\Omega$ )

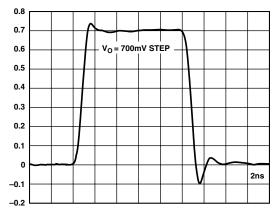

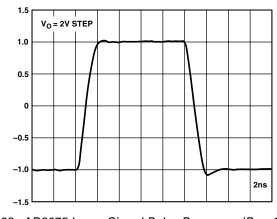

TPC 25. AD8074 Large Signal Pulse Response  $(R_L = 1 \text{ k}\Omega, C_L = 5 \text{ pF})$

TPC 28. AD8075 Large Signal Pulse Response ( $R_L = 150 \Omega$ )

-8- Rev. B

#### THEORY OF OPERATION

The AD8074 (G = +1) and AD8075 (G = +2) are triple-channel, high-speed buffers with TTL-compatible output enable control. Optimized for buffering RGB (red, green, blue) video sources, the devices have high peak slew rates, maintaining their bandwidth for large signals. Additionally, the buffers are compensated for high phase margin, minimizing overshoot for good pixel resolution. The buffers also have video specifications that are suitable for buffering NTSC or PAL composite signals.

The buffers are organized as three independent channels, each with an input transconductance stage and an output transimpedance stage. Each channel is characterized by low input capacitance and high input impedance. The transconductance stages, NPN differential pairs, source signal current into the folded cascode output stages. Each output stage contains a compensating network and emitter follower output buffer. Internal voltage feedback sets the gain, the AD8074 being configured as a unity gain follower, and the AD8075 as a gain-of-two amplifier with a feedback network. The architecture provides drive for a reverse-terminated video load (150  $\Omega$ ) with low differential gain and phase error for relatively low power consumption. Careful chip design and layout allow excellent crosstalk isolation between channels.

One logic pin,  $\overline{OE}$ , controls whether the three outputs are enabled, or disabled to a high-impedance state. The high impedance disable allows larger matrices to be built when busing the outputs together. When disabled, the AD8074 and AD8075 consume a fifth the power as when enabled. In the case of the AD8075 (G = +2), a feedback isolation scheme is used so that the impedance of the gain-of-two feedback network does not load the output.

Full power bandwidth for an undistorted sinusoid is often calculated using peak slew rate from the equation:

$$Full\ Power\ Bandwidth = \frac{Peak\ Slew\ Rate}{2 \times \pi \times Sinusoidal\ Amplitude}$$

Peak slew rate is not the same as average slew rate (25% to 75%) which is typically specified. For a natural response, peak slew rate may be 2.7 times larger than average slew rate. Therefore, calculating a full power bandwidth with a specified average slew rate will give a pessimistic result.

The primary cause of overshoot in these amplifiers is the presence of large reactive loads at the output and insufficient series isolation of the load. However, it is possible to overdrive these amplifiers with 1 V, subnanosecond input-pulse edges. The ensuing dynamics may give rise to subnanosecond overshoot. To reduce these effects, an edge-rate limiting network at the input should be considered for input transition times less than 0.5 ns.

#### **APPLICATIONS**

#### **Response Tuning**

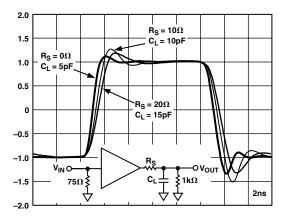

It has been mentioned in passing that the primary cause of overshoot for the AD8074 and AD8075 is the presence of large reactive loads at the output. If the system exhibits excessive ringing while settling, a  $10~\Omega-50~\Omega$  series resistor may be used at the output to isolate the emitter-follower output buffer from the reactive load. If the output exhibits an overdamped response, the system designer may add a few pF shunt capacitance at the output to tune for a faster edge transition. A system with a small degree of overshoot will settle faster than an overdamped system.

Figure 2. Driving Capacitive Loads

#### **Single Supply Operation**

The AD8074 and AD8075 may be operated from a single 10 V supply. In this configuration, the AD8075's AGND pins must be tied near midsupply, as AGND provides the reference for the ground buffer, to which the internal gain network is terminated.

Logic is referenced to DGND. The buffers are disabled in single supply operation for  $V_{\overline{OE}} > V_{DGND} + \sim 2.0 \text{ V}$  and enabled for  $V_{\overline{OE}} < V_{DGND} + 0.8 \text{ V}$ . TTL logic levels are expected. The following restrictions are placed upon the digital ground potential:

$$3.5 V \le V_{AVCC} - V_{DGND} \le 12 V$$

$V_{DGND} \ge V_{AVFE}$

The architecture of the output buffer is such that the output voltage can swing to within ~2.3 V of either rail. For example, if the output need swing only 2 V, then the buffers could be operated on dual 3.5 V or single 7 V supplies. It is cautioned that saturation effects may become noticeable when the output swings within 2.6 V of either rail. The system designer may opt to use this characteristic to his or her advantage by using the soft-saturation regime, (2.2 V–2.6 V from the supply rails), to tame excessive overshoot. The designer is cautioned that a charge storage associated time delay of several nanoseconds is incurred when recovering from soft-saturation. This effect results in longer settling tails.

Rev. B –9–

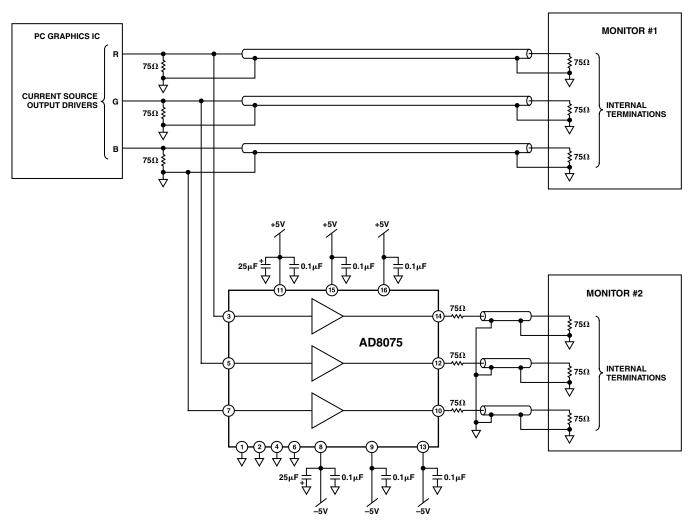

#### **RGB Buffer for Second Monitor**

The RGB signals for PC monitors are driven through coax cables whose characteristic impedance is 75  $\Omega$ . The graphics chip will generally have current-source output drivers that should be double terminated with a 75  $\Omega$  shunt termination at each end. On the transmit end, the shunt terminations are provided to ground close to the graphics IC, while the monitor terminates its end via internal termination resistors. While this scheme works well and is virtually foolproof for a single monitor, it leaves no means for passively connecting a second monitor to the same source.

A second monitor that is connected simply in parallel will provide an extra set of terminations that will upset the signal levels. To keep costs low, most computer monitors do not have the ability to open-circuit the terminations in order that an additional monitor

can be connected to the same signal, as is done in some studiotype TV monitors.

A way around this problem is to connect the first monitor to the RGB channels in the standard fashion, and then to provide a triple gain-of-two buffer to drive the second monitor. The AD8075 is designed to provide this function and also provide excellent high-frequency performance for high-resolution graphics signals. Figure 3 shows a schematic of this circuit.

The outputs of the AD8075 are low impedance voltage sources and are therefore series-terminated with 75  $\Omega$  resistors. The internal resistors in Monitor #2 provide the terminations at its end. The overall effect of this type of termination scheme is to divide the signal amplitude by two. This is compensated by the gain of two provided by the AD8075.

Figure 3. Buffer

-10- Rev. B

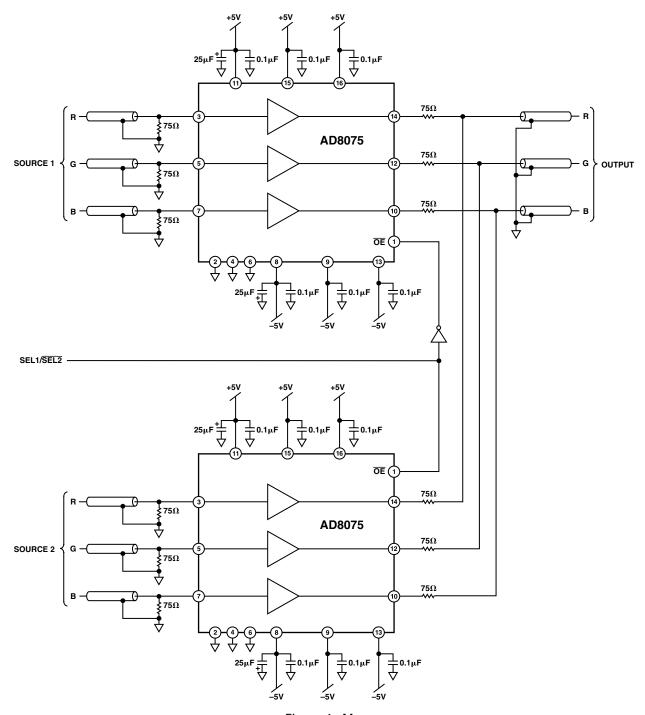

#### Triple Video Multiplexer

The AD8074 and AD8075 each have an output-enable function that can be used to disable the outputs and put them in a high-impedance state. Usually, for a unity-gain device, it is relatively easy to provide high disabled impedance, because the feedback path is from the output to a high-impedance input. However, for a non-unity-gain part, the feedback provides a resistive path to ground. This will usually dominate the disabled output impedance, and make it a much lower value than the unity-gain device.

The AD8075 has an internal buffer that provides a low-impedance, ground level output that terminates the feedback path during enabled operation. In the disabled state, both this buffer output

and the amplifier output are disabled to a high impedance to provide a high-impedance disabled state.

To construct a multiplexer, the outputs from one or more devices are connected in parallel and only one device is enabled at a time while all of the others are disabled. The two sets of inputs are applied individually to each of the separate device inputs.

Figure 4 shows the circuit details for this function. The first RGB Source 1 is input to the first AD8075. Each of the individual signals is terminated to ground with 75  $\Omega$  to provide proper termination for the input cables. In a similar fashion, the Source 2 signals are input to the second AD8075.

Figure 4. Mux

Each of the six outputs has a 75  $\Omega$  series resistor that is used to reverse-terminate the output transmission line. The corresponding outputs are then wired in parallel and delivered to the output cable. The termination resistors in this position help to isolate the off capacitance of the disabled device's outputs from loading the enabled device's outputs. The gain-of-two of the AD8075 compensates for the signal halving that occurs as a result of the output terminations.

A select signal is provided directly to the  $\overline{OE}$  of the second AD8075 and an inverted version is used to drive the other device's  $\overline{OE}$ . This will ensure that only one device is active at a time. Since there is a total of 150  $\Omega$  in series between any two outputs, it is not essential to be overly concerned about the exact timing of the making and breaking of the enable signals.

Additional inputs can easily be added to the circuit shown to make wider multiplexers. The outputs of all of the devices will be wired in parallel, and the logic must allow that only one output be enabled at a time.

If it is desired to make a triple 3:1 multiplexer, a triple 2:1 multiplexer, like the AD8185 can be used along with the AD8075. The same general guidelines for input and output treatment should be followed and the logic must perform the proper function.

If it is desired to design such a multiplexer at unity gain, the AD8074 should be used. For a triple 3:1 multiplexer, an AD8183 (triple 2:1 mux) can be combined with an AD8074 to provide this function.

#### Layout and Grounding

The AD8074 and AD8075 are extreme bandwidth, high-slew-rate devices that are designed to drive up to the highest resolution monitors and provide excellent resolution. To realize their full performance potential, it is essential to adhere to the best practices of high-speed PCB layout.

A major area of focus should be the power distribution system. There should be a full ground plane that provides the reference and return paths for both the inputs and outputs. The ground also provides isolation between the input signals to minimize the crosstalk. This ground plane should cover as wide an area as possible and be minimally interrupted in order to keep its impedance to a minimum.

The power planes should also be as broad as possible to provide minimal inductance, which is required for high-slew-rate signals. These power planes layers should be spaced closely to the ground plane to increase the interplane capacitance between the supplies and ground.

Each supply pin should be bypassed with a low inductance 0.1  $\mu F$  ceramic capacitance with minimal excess circuit length to minimize the series impedance. A 25  $\mu F$  tantalum electrolytic capacitor will supply a charge reservoir for lower frequency, high-amplitude transitions.

The input and output signals should be run as directly as possible in order to minimize the effects of parasitics. If they must run over a longer distance of more than a few centimeters, controlled impedance PCB traces should be used to minimize the effect of reflections due to mismatches in impedance and the proper termination should be provided.

To avoid excess crosstalk, the above recommendations should be followed carefully. The power system and signal routing are the most important aspects of preventing excess crosstalk. Beyond these techniques, shielding can be provided by ground traces between adjacent signals, especially those that travel parallel over long distances.

-12- Rev. B

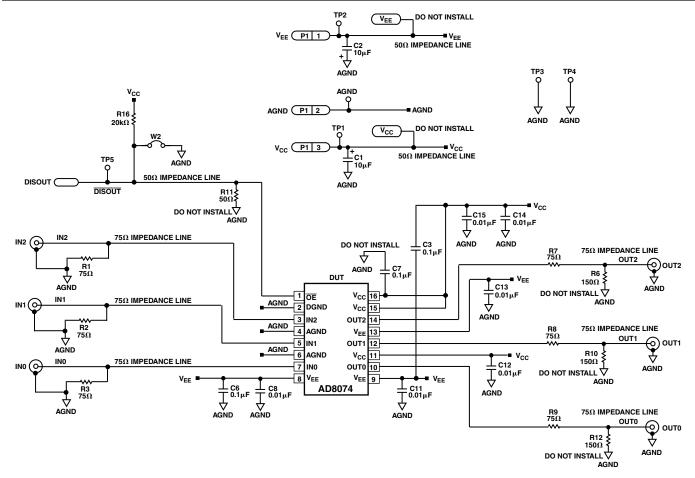

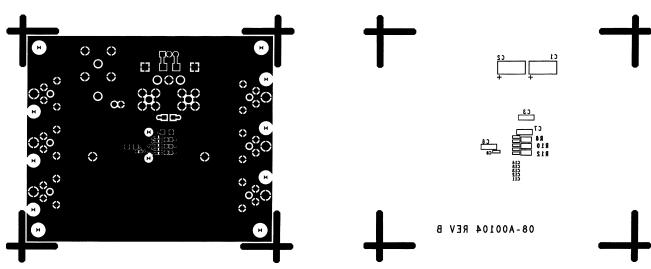

Figure 5. Evaluation Board Schematic

Rev. B –13–

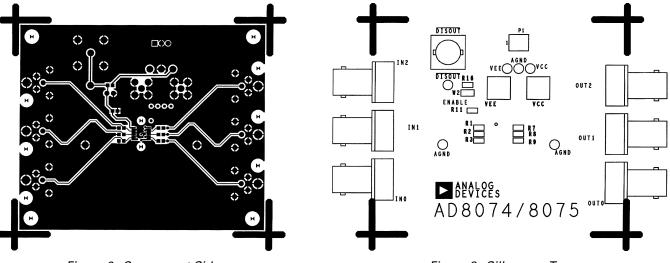

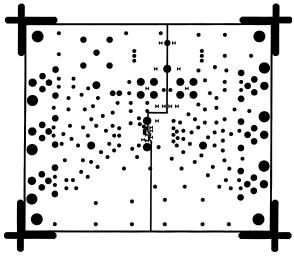

Figure 6. Component Side

Figure 8. Silkscreen Top

Figure 7. Circuit Side

Figure 9. Silkscreen Bottom

Figure 10. Internal 2

-14- Rev. B

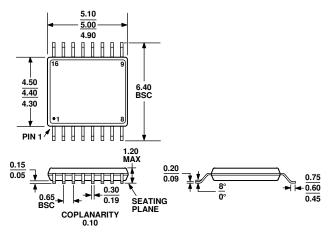

### **OUTLINE DIMENSIONS**

#### COMPLIANT TO JEDEC STANDARDS MO-153-AB

Figure 1. 16-Lead Thin Shrink Small Outline Package [TSSOP] (RU-16) Dimensions shown in millimeters

#### **ORDERING GUIDE**

| Model <sup>1</sup> | Temperature Range | Package Description                               | Package Option |

|--------------------|-------------------|---------------------------------------------------|----------------|

| AD8074ARU          | −40°C to +85°C    | 16-Lead Thin Shrink Small Outline Package [TSSOP] | RU-16          |

| AD8074ARUZ         | -40°C to +85°C    | 16-Lead Thin Shrink Small Outline Package [TSSOP] | RU-16          |

| AD8074ARUZ-REEL    | -40°C to +85°C    | 16-Lead Thin Shrink Small Outline Package [TSSOP] | RU-16          |

| AD8074ARUZ-REEL7   | -40°C to +85°C    | 16-Lead Thin Shrink Small Outline Package [TSSOP] | RU-16          |

| AD8075ARUZ         | −40°C to +85°C    | 16-Lead Thin Shrink Small Outline Package [TSSOP] | RU-16          |

| AD8075ARUZ-REEL    | -40°C to +85°C    | 16-Lead Thin Shrink Small Outline Package [TSSOP] | RU-16          |

| AD8075ARUZ-REEL7   | -40°C to +85°C    | 16-Lead Thin Shrink Small Outline Package [TSSOP] | RU-16          |

| AD8074Z-EVAL       |                   | Evaluation Board                                  |                |

| AD8075Z-EVAL       |                   | Evaluation Board                                  |                |

$<sup>^{1}</sup>$  Z = RoHS Compliant Part.

#### **REVISION HISTORY**