Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# 22 μA, RRIO, CMOS, 18 V Operational Amplifier

Data Sheet AD8546/AD8548

### **FEATURES**

Micropower at high voltage (18 V): 22 μA maximum

Low input bias current: 20 pA maximum

Gain bandwidth product: 240 kHz at  $A_V = 100$  typical

Unity-gain crossover: 240 kHz

-3 dB closed-loop bandwidth: 310 kHz

Slew rate: 80 V/ms

Large signal voltage gain: 110 dB minimum Single-supply operation: 2.7 V to 18 V Dual-supply operation: ±1.35 V to ±9 V

Unity-gain stable

**Excellent electromagnetic interference immunity**

#### **APPLICATIONS**

Portable medical equipment Remote sensors Transimpedance amplifiers Current monitors 4 mA to 20 mA loop drivers Buffer/level shifting

#### **GENERAL DESCRIPTION**

The AD8546 and AD8548 are dual and quad micropower, high input impedance amplifiers optimized for low power and wide operating supply voltage range applications.

The AD8546/AD8548 rail-to-rail input/output (RRIO) feature provides increased dynamic range to drive low frequency data converters, making these amplifiers ideal for dc gain and buffering of sensor front ends or high impedance input sources used in wireless or remote sensors or transmitters. The AD8546/AD8548 also have high immunity to electromagnetic interference.

The low supply current specification (22  $\mu$ A) of the AD8546/ AD8548 over a wide operating voltage range of 2.7 V to 18 V or dual supplies ( $\pm 1.35$  V to  $\pm 9$  V) makes these amplifiers useful for a variety of battery-powered, portable applications, such as ECGs, pulse monitors, glucose meters, smoke and fire detectors, vibration monitors, and backup battery sensors.

The AD8546/AD8548 are specified over the extended industrial temperature range of  $-40^{\circ}$ C to  $+125^{\circ}$ C. The AD8546 is available in an 8-lead MSOP package; the AD8548 is available in a 14-lead SOIC\_N package.

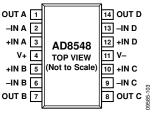

### **PIN CONFIGURATIONS**

Figure 1. AD8546 (8-Lead MSOP)

Figure 2. AD8548 (14-Lead SOIC\_N)

Table 1. Micropower Op Amps (<250 μA Typical)<sup>1</sup>

|           | Supply Voltage |              |           |  |  |

|-----------|----------------|--------------|-----------|--|--|

| Amplifier | 5 V            | 12 V to 18 V | 36 V      |  |  |

| Single    | AD8500         | AD8663       |           |  |  |

|           | AD8505         |              |           |  |  |

|           | AD8541         |              |           |  |  |

|           | AD8603         |              |           |  |  |

|           | ADA4505-1      |              |           |  |  |

| Dual      | AD8502         | AD8546       |           |  |  |

|           | AD8506         | AD8657       | ADA4062-2 |  |  |

|           | AD8542         | AD8667       | ADA4096-2 |  |  |

|           | AD8607         | OP281        |           |  |  |

|           | ADA4505-2      |              |           |  |  |

| Quad      | AD8504         | AD8548       |           |  |  |

|           | AD8508         | AD8669       | ADA4062-4 |  |  |

|           | AD8544         | OP481        | ADA4096-4 |  |  |

|           | AD8609         | AD8659       |           |  |  |

|           | ADA4505-4      |              |           |  |  |

<sup>&</sup>lt;sup>1</sup> See www.analog.com for the latest selection of micropower op amps.

Trademarks and registered trademarks are the property of their respective owners.

## **TABLE OF CONTENTS**

| Features 1                                                    | Typical Performance Characteristics                      | 7    |

|---------------------------------------------------------------|----------------------------------------------------------|------|

| Applications                                                  | Applications Information                                 | . 17 |

| Pin Configurations                                            | Input Stage                                              | .17  |

| General Description                                           | Output Stage                                             | 18   |

| Revision History                                              | Rail-to-Rail Input and Output                            | 18   |

| Specifications                                                | Resistive Load                                           | 18   |

| Electrical Characteristics—18 V Operation                     | Comparator Operation                                     | . 19 |

| Electrical Characteristics—10 V Operation 4                   | EMI Rejection Ratio                                      | 20   |

| Electrical Characteristics—2.7 V Operation5                   | 4 mA to 20 mA Process Control Current Loop Transmitter   | .20  |

| Absolute Maximum Ratings 6                                    | Outline Dimensions                                       | 21   |

| Thermal Resistance6                                           | Ordering Guide                                           | 21   |

| ESD Caution6                                                  |                                                          |      |

| REVISION HISTORY                                              |                                                          |      |

| 9/12—Rev. B to Rev. C                                         | Changes to Table 4                                       | 5    |

| Changes to Features Section, General Description Section, and | Changes to Table 6                                       |      |

| Table 1                                                       | Changes to Figure 4, Figure 5, Figure 7, and Figure 8    |      |

| Changes to Table 2                                            | Deleted Figure 8 and Figure 11                           |      |

| Changes to Table 34                                           | Changes to Figure 9, Figure 10, Figure 12, and Figure 13 |      |

| Changes to Table 45                                           | Changes to Figure 22 and Figure 25                       |      |

| Added EMI Rejection Ration Section                            |                                                          |      |

| 4/12—Rev. A to Rev. B                                         | Changes to Figure 63 and Figure 64                       |      |

| Added AD8548 and 14-Lead SOIC                                 | <u>.</u>                                                 |      |

| Changes to Product Title, Features Section, General           | Added Figure 72 Changes to Ordering Guide                |      |

| Description Section, and Table 1                              |                                                          | 41   |

| Added Figure 2; Renumbered Figures Sequentially               | 4/11—Rev. 0 to Rev. A                                    |      |

| Moved Electrical Characteristics—18 V Operation Section 3     | Changes to Product Title, Features Section, Applications |      |

| Changes to Table 2                                            | Section, General Description Section, and Table 1        | 1    |

| Changes to Table 3                                            | 1/11—Revision 0: Initial Version                         |      |

| Moved Electrical Characteristics—2.7 V Operation Section 5    | 1/11 ACTIONI O. INICIAL VELOCOL                          |      |

| 1710 rea Electrical Characteristics 2.7 v Operation Section 5 |                                                          |      |

## **SPECIFICATIONS**

## **ELECTRICAL CHARACTERISTICS—18 V OPERATION**

$\rm V_{SY}$  = 18 V,  $\rm V_{CM}$  =  $\rm V_{SY}/2$  ,  $\rm T_A$  = 25°C, unless otherwise noted.

Table 2.

| Parameter                    | Symbol                   | Test Conditions/Comments                                                                                 | Min   | Тур | Max | Unit    |

|------------------------------|--------------------------|----------------------------------------------------------------------------------------------------------|-------|-----|-----|---------|

| INPUT CHARACTERISTICS        |                          |                                                                                                          |       |     |     |         |

| Offset Voltage               | V <sub>os</sub>          | $V_{CM} = 0 \text{ V to } 18 \text{ V}$                                                                  |       |     | 3   | mV      |

|                              |                          | $V_{CM} = 0.3 \text{ V to } 17.7 \text{ V}; -40^{\circ}\text{C} \le T_{A} \le +125^{\circ}\text{C}$      |       |     | 7   | mV      |

|                              |                          | $V_{CM} = 0 \text{ V to } 18 \text{ V}; -40^{\circ}\text{C} \le T_{A} \le +125^{\circ}\text{C}$          |       |     | 12  | mV      |

| Offset Voltage Drift         | $\Delta V_{OS}/\Delta T$ |                                                                                                          |       | 3   |     | μV/°C   |

| Input Bias Current           | I <sub>B</sub>           |                                                                                                          |       | 5   | 20  | рА      |

|                              |                          | $-40$ °C $\leq T_A \leq +125$ °C                                                                         |       |     | 2.6 | nA      |

| Input Offset Current         | I <sub>os</sub>          |                                                                                                          |       |     | 40  | рА      |

|                              |                          | $-40$ °C $\leq T_A \leq +125$ °C                                                                         |       |     | 5.2 | nA      |

| Input Voltage Range          | IVR                      |                                                                                                          | 0     |     | 18  | V       |

| Common-Mode Rejection Ratio  | CMRR                     | $V_{CM} = 0 \text{ V to } 18 \text{ V}$                                                                  | 74    | 95  |     | dB      |

|                              |                          | $V_{CM} = 0.3 \text{ V to } 17.7 \text{ V}; -40^{\circ}\text{C} \le T_{A} \le +125^{\circ}\text{C}$      | 68    |     |     | dB      |

|                              |                          | $V_{CM} = 0 \text{ V to } 18 \text{ V}; -40^{\circ}\text{C} \le T_{A} \le +125^{\circ}\text{C}$          | 65    |     |     | dB      |

| Large Signal Voltage Gain    | A <sub>VO</sub>          | $R_L = 100 \text{ k}\Omega; V_O = 0.5 \text{ V to } 17.5 \text{ V}$                                      | 110   | 125 |     | dB      |

|                              |                          | $-40^{\circ}\text{C} \le \text{T}_{\text{A}} \le +125^{\circ}\text{C}$                                   | 105   |     |     | dB      |

| Input Resistance             | R <sub>IN</sub>          |                                                                                                          |       | 10  |     | GΩ      |

| Input Capacitance            |                          |                                                                                                          |       |     |     |         |

| Differential Mode            | C <sub>INDM</sub>        |                                                                                                          |       | 11  |     | pF      |

| Common Mode                  | C <sub>INCM</sub>        |                                                                                                          |       | 3.5 |     | pF      |

| OUTPUT CHARACTERISTICS       |                          |                                                                                                          |       |     |     |         |

| Output Voltage High          | V <sub>OH</sub>          | $R_{L} = 100 \text{ k}\Omega \text{ to } V_{CM}; -40^{\circ}\text{C} \le T_{A} \le +125^{\circ}\text{C}$ | 17.97 |     |     | V       |

| Output Voltage Low           | V <sub>OL</sub>          | $R_L = 100 \text{ k}\Omega \text{ to } V_{CM}; -40^{\circ}\text{C} \le T_A \le +125^{\circ}\text{C}$     |       |     | 30  | mV      |

| Short-Circuit Current        | I <sub>sc</sub>          |                                                                                                          |       | ±12 |     | mA      |

| Closed-Loop Output Impedance | Z <sub>out</sub>         | $f = 1 \text{ kHz; } A_V = +1$                                                                           |       | 15  |     | Ω       |

| POWER SUPPLY                 |                          |                                                                                                          |       |     |     |         |

| Power Supply Rejection Ratio | PSRR                     | $V_{SY} = 2.7 \text{ V to } 18 \text{ V}$                                                                | 95    | 115 |     | dB      |

|                              |                          | $-40$ °C $\leq$ T <sub>A</sub> $\leq$ $+125$ °C                                                          | 90    |     |     | dB      |

| Supply Current per Amplifier | I <sub>SY</sub>          | $I_0 = 0 \text{ mA}$                                                                                     |       | 18  | 22  | μΑ      |

|                              |                          | $-40^{\circ}\text{C} \le \text{T}_{A} \le +125^{\circ}\text{C}$                                          |       |     | 33  | μΑ      |

| DYNAMIC PERFORMANCE          |                          |                                                                                                          |       |     |     |         |

| Slew Rate                    | SR                       | $R_L = 1 \text{ M}\Omega; C_L = 10 \text{ pF}; A_V = +1$                                                 |       | 80  |     | V/ms    |

| Settling Time to 0.1%        | t <sub>s</sub>           | $V_{IN} = 1 \text{ V step; } R_{L} = 100 \text{ k}\Omega; C_{L} = 10 \text{ pF}$                         |       | 15  |     | μs      |

| Unity Gain Crossover         | UGC                      | $V_{IN} = 10 \text{ mV p-p; } R_L = 1 \text{ M}\Omega; C_L = 10 \text{ pF; } A_V = +1$                   |       | 240 |     | kHz     |

| Phase Margin                 | $\Phi_{M}$               | $V_{IN} = 10 \text{ mV p-p; } R_{L} = 1 \text{ M}\Omega; C_{L} = 10 \text{ pF; } A_{V} = +1$             |       | 60  |     | Degrees |

| Gain Bandwidth Product       | GBP                      | $V_{IN} = 10 \text{ mV p-p}$ ; $R_L = 1 \text{ M}\Omega$ ; $C_L = 10 \text{ pF}$ ; $A_V = +100$          |       | 240 |     | kHz     |

| –3 dB Closed-Loop Bandwidth  | $f_{-3 dB}$              | $V_{IN} = 10 \text{ mV p-p; } R_{L} = 1 \text{ M}\Omega; C_{L} = 10 \text{ pF; } A_{V} = +1$             |       | 310 |     | kHz     |

| Channel Separation           | CS                       | $f = 10 \text{ kHz}$ ; $R_L = 1 \text{ M}\Omega$                                                         |       | 105 |     | dB      |

| EMI Rejection Ratio of +IN x | EMIRR                    | V <sub>IN</sub> = 100 mV p-p; f = 400 MHz, 900 MHz, 1800 MHz, 2400 MHz                                   |       | 90  |     | dB      |

| NOISE PERFORMANCE            |                          |                                                                                                          |       |     |     |         |

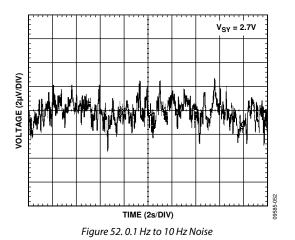

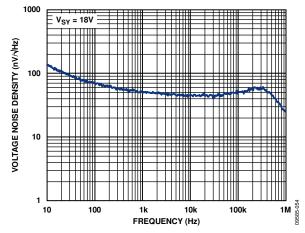

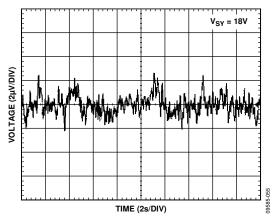

| Voltage Noise                | e <sub>n</sub> p-p       | f = 0.1 Hz to 10 Hz                                                                                      |       | 5   |     | μV p-p  |

| Voltage Noise Density        | e <sub>n</sub>           | f = 1 kHz                                                                                                |       | 50  |     | nV/√Hz  |

|                              |                          | f = 10 kHz                                                                                               |       | 45  |     | nV/√Hz  |

| Current Noise Density        | i <sub>n</sub>           | f = 1  kHz                                                                                               |       | 0.1 |     | pA/√Hz  |

## **ELECTRICAL CHARACTERISTICS—10 V OPERATION**

$\rm V_{SY}=10$  V,  $\rm V_{CM}=V_{SY}/2,\,T_{A}=25^{o}C,$  unless otherwise noted.

Table 3.

| Parameter                    | Symbol                   | Test Conditions/Comments                                                                             | Min  | Тур | Max | Unit    |

|------------------------------|--------------------------|------------------------------------------------------------------------------------------------------|------|-----|-----|---------|

| INPUT CHARACTERISTICS        |                          |                                                                                                      |      |     |     |         |

| Offset Voltage               | Vos                      | $V_{CM} = 0 \text{ V to } 10 \text{ V}$                                                              |      |     | 3   | mV      |

|                              |                          | $V_{CM} = 0.3 \text{ V to } 9.7 \text{ V}; -40^{\circ}\text{C} \le T_{A} \le +125^{\circ}\text{C}$   |      |     | 8   | mV      |

|                              |                          | $V_{CM} = 0 \text{ V to } 10 \text{ V}; -40^{\circ}\text{C} \le T_{A} \le +125^{\circ}\text{C}$      |      |     | 12  | mV      |

| Offset Voltage Drift         | $\Delta V_{OS}/\Delta T$ |                                                                                                      |      | 3   |     | μV/°C   |

| Input Bias Current           | I <sub>B</sub>           |                                                                                                      |      | 2   | 15  | рA      |

|                              |                          | $-40^{\circ}\text{C} \le \text{T}_{A} \le +125^{\circ}\text{C}$                                      |      |     | 2.6 | nA      |

| Input Offset Current         | I <sub>os</sub>          |                                                                                                      |      |     | 30  | pA      |

|                              |                          | $-40^{\circ}\text{C} \le \text{T}_{A} \le +125^{\circ}\text{C}$                                      |      |     | 5.2 | nA      |

| Input Voltage Range          | IVR                      |                                                                                                      | 0    |     | 10  | V       |

| Common-Mode Rejection Ratio  | CMRR                     | $V_{CM} = 0 V \text{ to } 10 V$                                                                      | 70   | 88  |     | dB      |

|                              |                          | $V_{CM} = 0.3 \text{ V to } 9.7 \text{ V}; -40^{\circ}\text{C} \le T_{A} \le +125^{\circ}\text{C}$   | 62   |     |     | dB      |

|                              |                          | $V_{CM} = 0 \text{ V to } 10 \text{ V}; -40^{\circ}\text{C} \le T_{A} \le +125^{\circ}\text{C}$      | 60   |     |     | dB      |

| Large Signal Voltage Gain    | $A_{VO}$                 | $R_L = 100 \text{ k}\Omega; V_O = 0.5 \text{ V to } 9.5 \text{ V}$                                   | 105  | 120 |     | dB      |

|                              |                          | $-40^{\circ}\text{C} \le \text{T}_{A} \le +125^{\circ}\text{C}$                                      | 100  |     |     | dB      |

| Input Resistance             | R <sub>IN</sub>          |                                                                                                      |      | 10  |     | GΩ      |

| Input Capacitance            |                          |                                                                                                      |      |     |     |         |

| Differential Mode            | C <sub>INDM</sub>        |                                                                                                      |      | 11  |     | pF      |

| Common Mode                  | C <sub>INCM</sub>        |                                                                                                      |      | 3.5 |     | pF      |

| OUTPUT CHARACTERISTICS       |                          |                                                                                                      |      |     |     |         |

| Output Voltage High          | $V_{OH}$                 | $R_L = 100 \text{ k}\Omega \text{ to } V_{CM}; -40^{\circ}\text{C} \le T_A \le +125^{\circ}\text{C}$ | 9.98 |     |     | V       |

| Output Voltage Low           | $V_{OL}$                 | $R_L = 100 \text{ k}\Omega \text{ to } V_{CM}; -40^{\circ}\text{C} \le T_A \le +125^{\circ}\text{C}$ |      |     | 20  | mV      |

| Short-Circuit Current        | I <sub>sc</sub>          |                                                                                                      |      | ±11 |     | mA      |

| Closed-Loop Output Impedance | Z <sub>out</sub>         | $f = 1 \text{ kHz; } A_V = +1$                                                                       |      | 15  |     | Ω       |

| POWER SUPPLY                 |                          |                                                                                                      |      |     |     |         |

| Power Supply Rejection Ratio | PSRR                     | $V_{SY} = 2.7 \text{ V to } 18 \text{ V}$                                                            | 95   | 115 |     | dB      |

|                              |                          | $-40^{\circ}\text{C} \le \text{T}_{A} \le +125^{\circ}\text{C}$                                      | 90   |     |     | dB      |

| Supply Current per Amplifier | I <sub>SY</sub>          | $I_0 = 0 \text{ mA}$                                                                                 |      | 18  | 22  | μΑ      |

|                              |                          | $-40$ °C $\leq$ T <sub>A</sub> $\leq$ $+125$ °C                                                      |      |     | 33  | μΑ      |

| DYNAMIC PERFORMANCE          |                          |                                                                                                      |      |     |     |         |

| Slew Rate                    | SR                       | $R_L = 1 \text{ M}\Omega; C_L = 10 \text{ pF}; A_V = +1$                                             |      | 75  |     | V/ms    |

| Settling Time to 0.1%        | $t_{S}$                  | $V_{IN} = 1 \text{ V step; } R_{L} = 100 \text{ k}\Omega; C_{L} = 10 \text{ pF}$                     |      | 15  |     | μs      |

| Unity-Gain Crossover         | UGC                      | $V_{IN} = 10 \text{ mV p-p; } R_{L} = 1 \text{ M}\Omega, C_{L} = 10 \text{ pF, } A_{V} = +1$         |      | 235 |     | kHz     |

| Phase Margin                 | $\Phi_{M}$               | $V_{IN} = 10 \text{ mV p-p}$ ; $R_L = 1 \text{ M}\Omega$ ; $C_L = 10 \text{ pF}$ ; $A_V = +1$        |      | 60  |     | Degrees |

| Gain Bandwidth Product       | GBP                      | $V_{IN} = 10 \text{ mV p-p; } R_{L} = 1 \text{ M}\Omega; C_{L} = 10 \text{ pF; } A_{V} = +100$       |      | 235 |     | kHz     |

| –3 dB Closed-Loop Bandwidth  | f <sub>-3 dB</sub>       | $V_{IN} = 10 \text{ mV p-p, } R_{L} = 1 \text{ M}\Omega, C_{L} = 10 \text{ pF, } A_{V} = +1$         |      | 300 |     | kHz     |

| Channel Separation           | CS                       | $f = 10 \text{ kHz; } R_L = 1 \text{ M}\Omega$                                                       |      | 105 |     | dB      |

| EMI Rejection Ratio of +IN x | EMIRR                    | V <sub>IN</sub> = 100 mV p-p; f = 400 MHz, 900 MHz, 1800 MHz, 2400 MHz                               |      | 90  |     | dB      |

| NOISE PERFORMANCE            |                          |                                                                                                      |      |     |     |         |

| Voltage Noise                | e <sub>n</sub> p-p       | f = 0.1 Hz to 10 Hz                                                                                  |      | 5   |     | μV р-р  |

| Voltage Noise Density        | e <sub>n</sub>           | f = 1 kHz                                                                                            |      | 50  |     | nV/√Hz  |

|                              |                          | f = 10 kHz                                                                                           |      | 45  |     | nV/√Hz  |

| Current Noise Density        | i <sub>n</sub>           | f = 1 kHz                                                                                            |      | 0.1 |     | pA/√Hz  |

## **ELECTRICAL CHARACTERISTICS—2.7 V OPERATION**

$V_{SY} = 2.7 \text{ V}$ ,  $V_{CM} = V_{SY}/2$ ,  $T_A = 25$ °C, unless otherwise noted.

Table 4.

| Parameter                    | Symbol                   | Test Conditions/Comments                                                                             | Min  | Тур | Max | Unit    |

|------------------------------|--------------------------|------------------------------------------------------------------------------------------------------|------|-----|-----|---------|

| INPUT CHARACTERISTICS        |                          |                                                                                                      |      |     |     |         |

| Offset Voltage               | V <sub>os</sub>          | $V_{CM} = 0 \text{ V to } 2.7 \text{ V}$                                                             |      |     | 3   | mV      |

|                              |                          | $V_{CM} = 0.3 \text{ V to } 2.4 \text{ V}; -40^{\circ}\text{C} \le T_{A} \le +125^{\circ}\text{C}$   |      |     | 4   | mV      |

|                              |                          | $V_{CM} = 0 \text{ V to } 2.7 \text{ V}; -40^{\circ}\text{C} \le T_{A} \le +125^{\circ}\text{C}$     |      |     | 12  | mV      |

| Offset Voltage Drift         | $\Delta V_{OS}/\Delta T$ |                                                                                                      |      | 3   |     | μV/°C   |

| Input Bias Current           | I <sub>B</sub>           |                                                                                                      |      | 1   | 10  | pА      |

|                              |                          | $-40^{\circ}\text{C} \le \text{T}_{A} \le +125^{\circ}\text{C}$                                      |      |     | 2.6 | nA      |

| Input Offset Current         | Ios                      |                                                                                                      |      |     | 20  | pА      |

|                              |                          | $-40$ °C $\leq T_A \leq +125$ °C                                                                     |      |     | 5.2 | nA      |

| Input Voltage Range          | IVR                      |                                                                                                      | 0    |     | 2.7 | V       |

| Common-Mode Rejection Ratio  | CMRR                     | $V_{CM} = 0 \text{ V to } 2.7 \text{ V}$                                                             | 60   | 75  |     | dB      |

|                              |                          | $V_{CM} = 0.3 \text{ V to } 2.4 \text{ V}; -40^{\circ}\text{C} \le T_{A} \le +125^{\circ}\text{C}$   | 58   |     |     | dB      |

|                              |                          | $V_{CM} = 0 \text{ V to } 2.7 \text{ V}; -40^{\circ}\text{C} \le T_{A} \le +125^{\circ}\text{C}$     | 49   |     |     | dB      |

| Large Signal Voltage Gain    | A <sub>vo</sub>          | $R_L = 100 \text{ k}\Omega; V_O = 0.5 \text{ V to } 2.2 \text{ V}$                                   | 97   | 115 |     | dB      |

|                              |                          | $-40^{\circ}\text{C} \le \text{T}_{\text{A}} \le +125^{\circ}\text{C}$                               | 90   |     |     | dB      |

| Input Resistance             | R <sub>IN</sub>          |                                                                                                      |      | 10  |     | GΩ      |

| Input Capacitance            |                          |                                                                                                      |      |     |     |         |

| Differential Mode            | C <sub>INDM</sub>        |                                                                                                      |      | 11  |     | рF      |

| Common Mode                  | C <sub>INCM</sub>        |                                                                                                      |      | 3.5 |     | рF      |

| OUTPUT CHARACTERISTICS       |                          |                                                                                                      |      |     |     |         |

| Output Voltage High          | $V_{OH}$                 | $R_L = 100 \text{ k}\Omega \text{ to } V_{CM}; -40^{\circ}\text{C} \le T_A \le +125^{\circ}\text{C}$ | 2.69 |     |     | V       |

| Output Voltage Low           | V <sub>OL</sub>          | $R_L = 100 \text{ k}\Omega \text{ to } V_{CM}; -40^{\circ}\text{C} \le T_A \le +125^{\circ}\text{C}$ |      |     | 10  | mV      |

| Short-Circuit Current        | I <sub>sc</sub>          |                                                                                                      |      | ±4  |     | mA      |

| Closed-Loop Output Impedance | Z <sub>out</sub>         | $f = 1 \text{ kHz; } A_V = +1$                                                                       |      | 20  |     | Ω       |

| POWER SUPPLY                 |                          |                                                                                                      |      |     |     |         |

| Power Supply Rejection Ratio | PSRR                     | $V_{SY} = 2.7 \text{ V to } 18 \text{ V}$                                                            | 95   | 115 |     | dB      |

|                              |                          | $-40$ °C $\leq T_A \leq +125$ °C                                                                     | 90   |     |     | dB      |

| Supply Current per Amplifier | I <sub>SY</sub>          | $I_0 = 0 \text{ mA}$                                                                                 |      | 18  | 22  | μΑ      |

|                              |                          | $-40$ °C $\leq$ T <sub>A</sub> $\leq$ $+125$ °C                                                      |      |     | 33  | μΑ      |

| DYNAMIC PERFORMANCE          |                          |                                                                                                      |      |     |     |         |

| Slew Rate                    | SR                       | $R_1 = 1 \text{ M}\Omega; C_1 = 10 \text{ pF}; A_V = +1$                                             |      | 50  |     | V/ms    |

| Settling Time to 0.1%        | t <sub>s</sub>           | $V_{IN} = 1 \text{ V step; } R_L = 100 \text{ k}\Omega; C_L = 10 \text{ pF}$                         |      | 20  |     | μs      |

| Unity Gain Crossover         | UGC                      | $V_{IN} = 10 \text{ mV p-p; } R_{L} = 1 \text{ M}\Omega; C_{L} = 10 \text{ pF; } A_{V} = +1$         |      | 190 |     | kHz     |

| Phase Margin                 | Фм                       | $V_{IN} = 10 \text{ mV p-p; } R_L = 1 \text{ M}\Omega; C_L = 10 \text{ pF; } A_V = +1$               |      | 60  |     | Degrees |

| Gain Bandwidth Product       | GBP                      | $V_{IN} = 10 \text{ mV p-p; } R_L = 1 \text{ M}\Omega; C_L = 10 \text{ pF; } A_V = +100$             |      | 200 |     | kHz     |

| -3 dB Closed-Loop Bandwidth  | $f_{-3 dB}$              | $V_{IN} = 10 \text{ mV p-p; } R_L = 1 \text{ M}\Omega; C_L = 10 \text{ pF; } A_V = +1$               |      | 250 |     | kHz     |

| Channel Separation           | CS                       | $f = 10 \text{ kHz; } R_L = 1 \text{ M}\Omega$                                                       |      | 105 |     | dB      |

| EMI Rejection Ratio of +IN x | EMIRR                    | V <sub>IN</sub> = 100 mV p-p; f = 400 MHz, 900 MHz, 1800 MHz, 2400 MHz                               |      | 90  |     | dB      |

| NOISE PERFORMANCE            |                          |                                                                                                      |      |     |     |         |

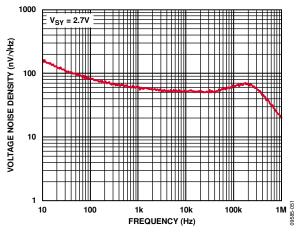

| Voltage Noise                | e <sub>n</sub> p-p       | f = 0.1 Hz to 10 Hz                                                                                  |      | 6   |     | μV p-p  |

| Voltage Noise Density        | e <sub>n</sub>           | f = 1 kHz                                                                                            |      | 60  |     | nV/√Hz  |

|                              |                          | f = 10 kHz                                                                                           |      | 56  |     | nV/√Hz  |

| Current Noise Density        | i <sub>n</sub>           | f = 1 kHz                                                                                            |      | 0.1 |     | pA/√Hz  |

## **ABSOLUTE MAXIMUM RATINGS**

Table 5.

| 1 1010 01                               |                                |

|-----------------------------------------|--------------------------------|

| Parameter                               | Rating                         |

| Supply Voltage                          | 20.5 V                         |

| Input Voltage                           | (V–) – 300 mV to (V+) + 300 mV |

| Input Current <sup>1</sup>              | ±10 mA                         |

| Differential Input Voltage              | $\pm V_{SY}$                   |

| Output Short-Circuit Duration to GND    | Indefinite                     |

| Storage Temperature Range               | −65°C to +150°C                |

| Operating Temperature Range             | -40°C to +125°C                |

| Junction Temperature Range              | −65°C to +150°C                |

| Lead Temperature<br>(Soldering, 60 sec) | 300°C                          |

<sup>&</sup>lt;sup>1</sup> The input pins have clamp diodes to the power supply pins. Limit the input current to 10 mA or less whenever input signals exceed the power supply rail by 0.3 V.

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## THERMAL RESISTANCE

$\theta_{JA}$  is specified for the worst-case conditions, that is, a device soldered in a circuit board for surface-mount packages using a standard 4-layer board.

**Table 6. Thermal Resistance**

| Package Type          | $\theta_{JA}$ | $\theta_{JC}$ | Unit |

|-----------------------|---------------|---------------|------|

| 8-Lead MSOP (RM-8)    | 142           | 45            | °C/W |

| 14-Lead SOIC_N (R-14) | 115           | 36            | °C/W |

## **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

## TYPICAL PERFORMANCE CHARACTERISTICS

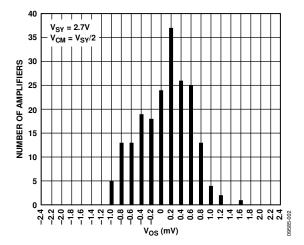

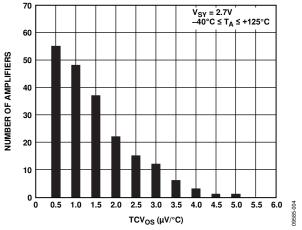

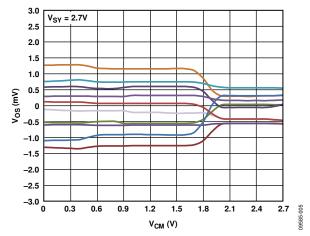

$T_A = 25$ °C, unless otherwise noted.

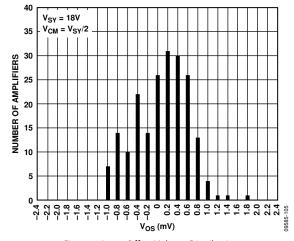

Figure 3. Input Offset Voltage Distribution

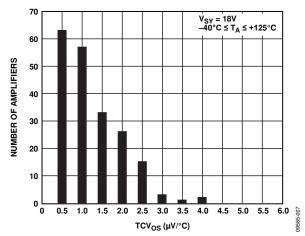

Figure 4. Input Offset Voltage Drift Distribution

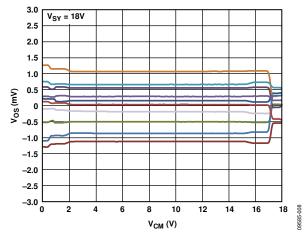

Figure 5. Input Offset Voltage vs. Common-Mode Voltage

Figure 6. Input Offset Voltage Distribution

Figure 7. Input Offset Voltage Drift Distribution

Figure 8. Input Offset Voltage vs. Common-Mode Voltage

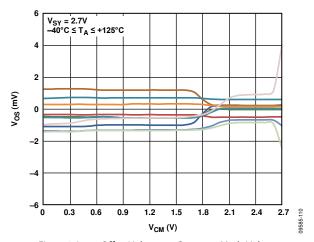

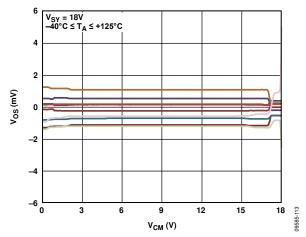

Figure 9. Input Offset Voltage vs. Common-Mode Voltage

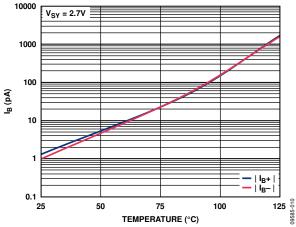

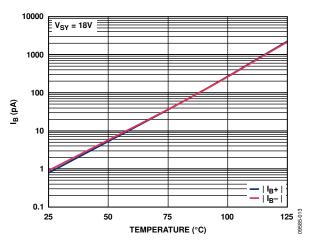

Figure 10. Input Bias Current vs. Temperature

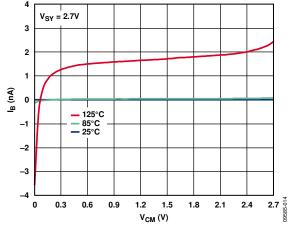

Figure 11. Input Bias Current vs. Common-Mode Voltage

Figure 12. Input Offset Voltage vs. Common-Mode Voltage

Figure 13. Input Bias Current vs. Temperature

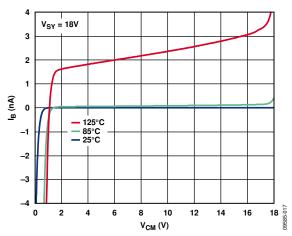

Figure 14. Input Bias Current vs. Common-Mode Voltage

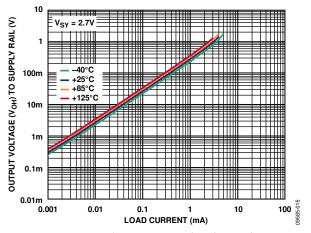

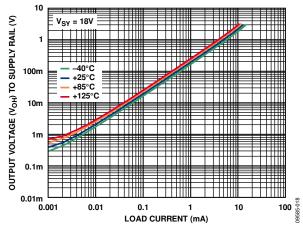

Figure 15. Output Voltage (V<sub>OH</sub>) to Supply Rail vs. Load Current

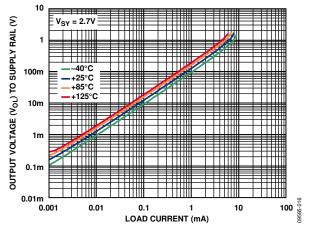

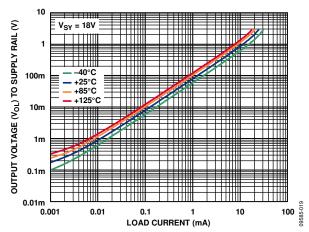

Figure 16. Output Voltage ( $V_{OL}$ ) to Supply Rail vs. Load Current

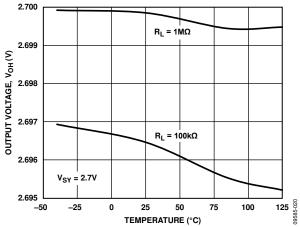

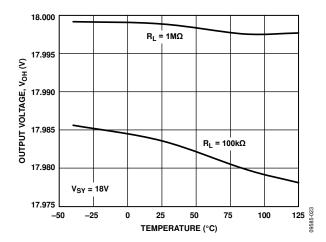

Figure 17. Output Voltage ( $V_{OH}$ ) vs. Temperature

Figure 18. Output Voltage (V<sub>OH</sub>) to Supply Rail vs. Load Current

Figure 19. Output Voltage ( $V_{\rm OL}$ ) to Supply Rail vs. Load Current

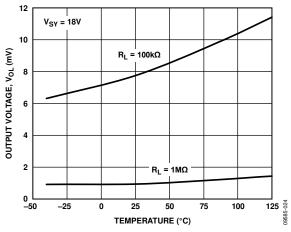

Figure 20. Output Voltage (V<sub>OH</sub>) vs. Temperature

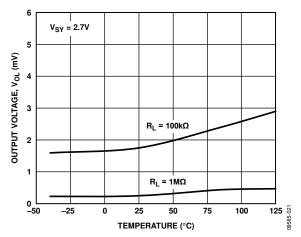

Figure 21. Output Voltage ( $V_{\rm OL}$ ) vs. Temperature

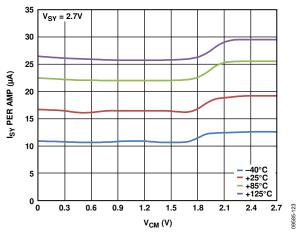

Figure 22. Supply Current per Amplifier vs. Common-Mode Voltage

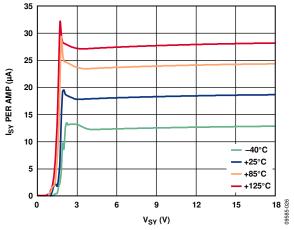

Figure 23. Supply Current per Amplifier vs. Supply Voltage

Figure 24. Output Voltage ( $V_{\rm OL}$ ) vs. Temperature

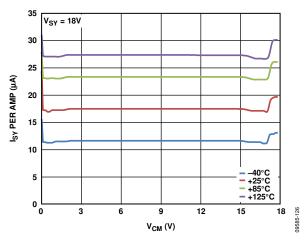

Figure 25. Supply Current per Amplifier vs. Common-Mode Voltage

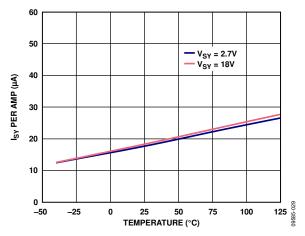

Figure 26. Supply Current per Amplifier vs. Temperature

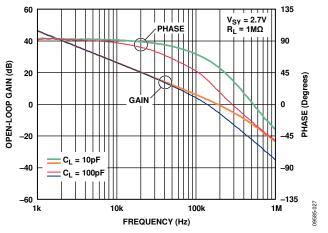

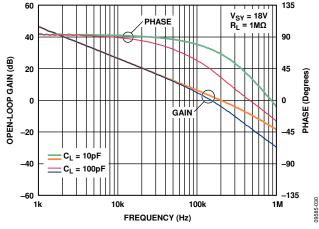

Figure 27. Open-Loop Gain and Phase vs. Frequency

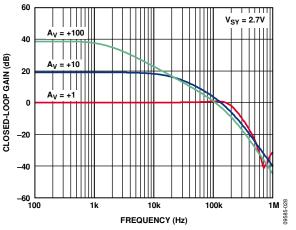

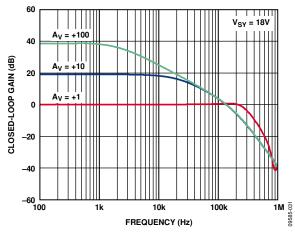

Figure 28. Closed-Loop Gain vs. Frequency

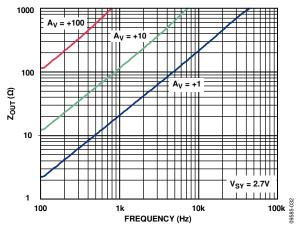

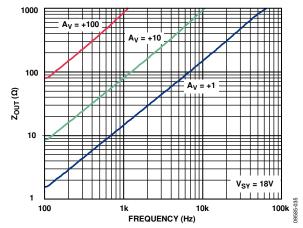

Figure 29. Output Impedance vs. Frequency

Figure 30. Open-Loop Gain and Phase vs. Frequency

Figure 31. Closed-Loop Gain vs. Frequency

Figure 32. Output Impedance vs. Frequency

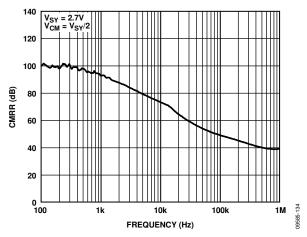

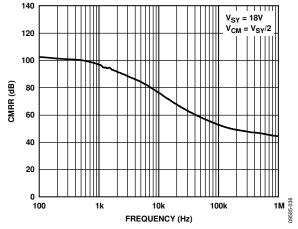

Figure 33. CMRR vs. Frequency

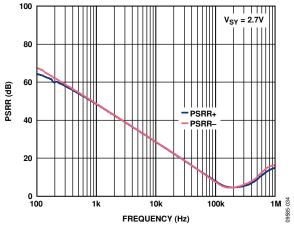

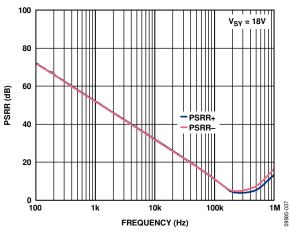

Figure 34. PSRR vs. Frequency

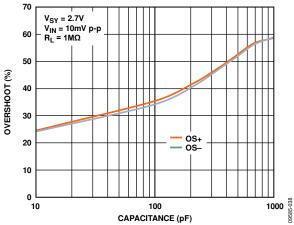

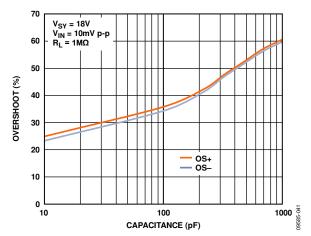

Figure 35. Small Signal Overshoot vs. Load Capacitance

Figure 36. CMRR vs. Frequency

Figure 37. PSRR vs. Frequency

Figure 38. Small Signal Overshoot vs. Load Capacitance

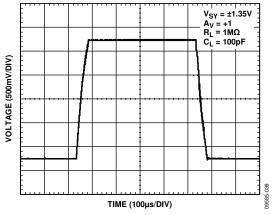

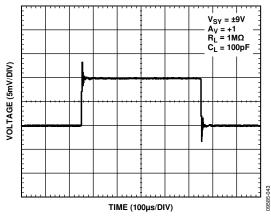

Figure 39. Large Signal Transient Response

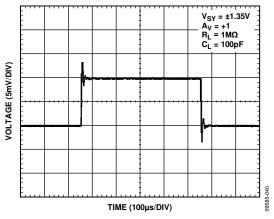

Figure 40. Small Signal Transient Response

V<sub>SY</sub> = ±9V A<sub>V</sub> = ±1 R<sub>L</sub> = 1MΩ C<sub>L</sub> = 100pF

Figure 42. Large Signal Transient Response

Figure 43. Small Signal Transient Response

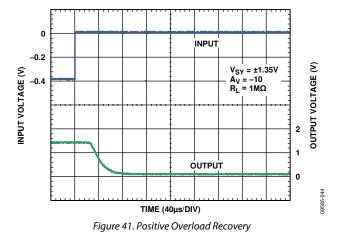

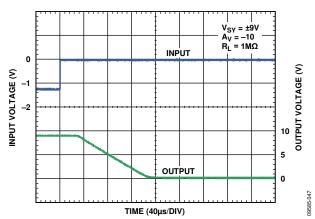

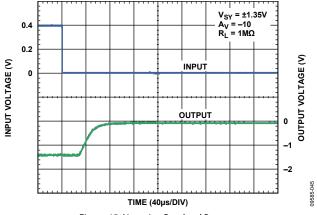

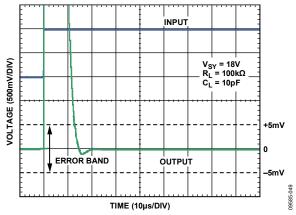

Figure 44. Positive Overload Recovery

Figure 45. Negative Overload Recovery

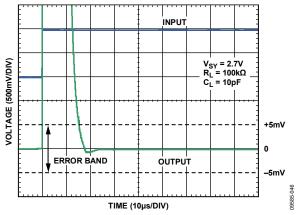

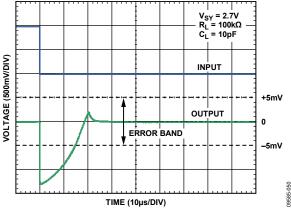

Figure 46. Positive Settling Time to 0.1%

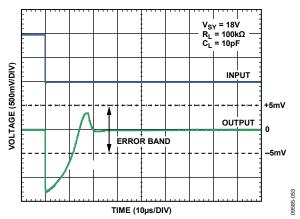

Figure 47. Negative Settling Time to 0.1%

Figure 48. Negative Overload Recovery

Figure 49. Positive Settling Time to 0.1%

Figure 50. Negative Settling Time to 0.1%

Figure 51. Voltage Noise Density vs. Frequency

3.0

2.5

2.5

2.0

9NMS 1.5

0 100 1k 10k 100k 1M

FREQUENCY (Hz)

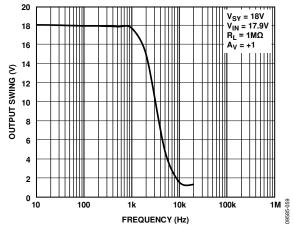

Figure 53. Output Swing vs. Frequency

Figure 54. Voltage Noise Density vs. Frequency

Figure 55. 0.1 Hz to 10 Hz Noise

Figure 56. Output Swing vs. Frequency

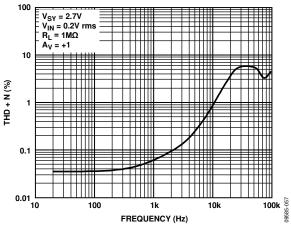

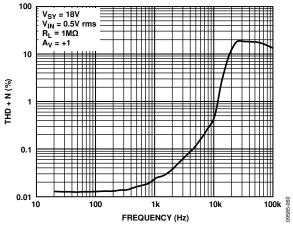

Figure 57. THD + N vs. Frequency

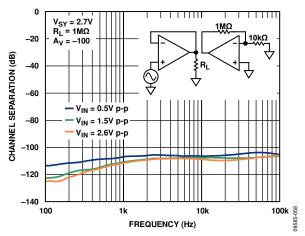

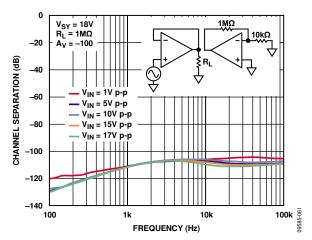

Figure 58. Channel Separation vs. Frequency

Figure 59. THD + N vs. Frequency

Figure 60. Channel Separation vs. Frequency

## APPLICATIONS INFORMATION

The AD8546/AD8548 are low input bias current, micropower CMOS amplifiers that operate over a wide supply voltage range of 2.7 V to 18 V. The AD8546/AD8548 also employ unique input and output stages to achieve rail-to-rail input and output ranges with very low supply current.

## **INPUT STAGE**

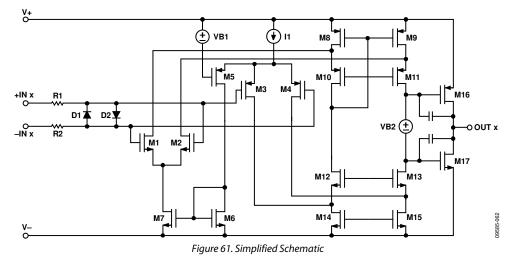

Figure 61 shows the simplified schematic of the AD8546/AD8548. The input stage comprises two differential transistor pairs: an NMOS pair (M1, M2) and a PMOS pair (M3, M4). The input common-mode voltage determines which differential pair turns on and is more active than the other.

The PMOS differential pair is active when the input voltage approaches and reaches the lower supply rail. The NMOS differential pair is needed for input voltages up to and including the upper supply rail. This topology allows the amplifier to maintain a wide dynamic input voltage range and maximize signal swing to both supply rails. For the greater part of the input common-mode voltage range, the PMOS differential pair is active.

Differential pairs commonly exhibit different offset voltages. The handoff from one pair to the other creates a step-like characteristic that is visible in the  $V_{\rm OS}$  vs.  $V_{\rm CM}$  graphs (see Figure 5 and Figure 8). This characteristic is inherent in all rail-to-rail amplifiers that use the dual differential pair topology. Therefore, always choose a common-mode voltage that does not include the region of handoff from one input differential pair to the other.

Additional steps in the  $V_{OS}$  vs.  $V_{CM}$  graphs are also visible as the input common-mode voltage approaches the power supply rails. These changes are a result of the load transistors (M8, M9, M14, and M15) running out of headroom. As the load transistors are forced into the triode region of operation, the mismatch of their

drain impedances contributes to the offset voltage of the amplifier. This problem is exacerbated at high temperatures due to the decrease in the threshold voltage of the input transistors. See Figure 9 and Figure 12 for typical performance data.

Current Source I1 drives the PMOS transistor pair. As the input common-mode voltage approaches the upper rail, I1 is steered away from the PMOS differential pair through the M5 transistor. The bias voltage, VB1, controls the point where this transfer occurs.

M5 diverts the tail current into a current mirror consisting of the M6 and M7 transistors. The output of the current mirror then drives the NMOS transistor pair. Note that the activation of this current mirror causes a slight increase in supply current at high common-mode voltages (see Figure 22 and Figure 25).

The AD8546/AD8548 achieve their high performance by using low voltage MOS devices for their differential inputs. These low voltage MOS devices offer excellent noise and bandwidth per unit of current. Each differential input pair is protected by proprietary regulation circuitry (not shown in Figure 61). The regulation circuitry consists of a combination of active devices, which maintain the proper voltages across the input pairs during normal operation, and passive clamping devices, which protect the amplifier during fast transients. However, these passive clamping devices begin to forward-bias as the common-mode voltage approaches either power supply rail. This causes an increase in the input bias current (see Figure 11 and Figure 14).

The input devices are also protected from large differential input voltages by clamp diodes (D1 and D2). These diodes are buffered from the inputs with two 10 k $\Omega$  resistors (R1 and R2). The differential diodes turn on when the differential input voltage exceeds approximately 600 mV; in this condition, the differential input resistance drops to 20 k $\Omega$ .

#### **OUTPUT STAGE**

The AD8546/AD8548 feature a complementary output stage consisting of the M16 and M17 transistors (see Figure 61). These transistors are configured in a Class AB topology and are biased by the voltage source, VB2. This topology allows the output voltage to go within millivolts of the supply rails, achieving a rail-to-rail output swing. The output voltage is limited by the output impedance of the transistors, which are low  $R_{\rm ON}$  MOS devices. The output voltage swing is a function of the load current and can be estimated using the output voltage to supply rail vs. load current graphs (see Figure 15, Figure 16, Figure 18, and Figure 19).

#### **RAIL-TO-RAIL INPUT AND OUTPUT**

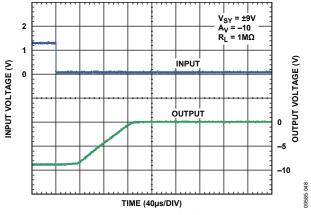

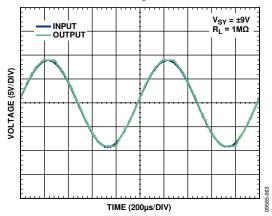

The AD8546/AD8548 feature rail-to-rail input and output with a supply voltage from 2.7 V to 18 V. Figure 62 shows the input and output waveforms of the AD8546/AD8548 configured as a unity-gain buffer with a supply voltage of  $\pm 9$  V and a resistive load of 1 M $\Omega$ . With an input voltage of  $\pm 9$  V, the AD8546/AD8548 allow the output to swing very close to both rails. Additionally, the AD8546/AD8548 do not exhibit phase reversal.

Figure 62. Rail-to-Rail Input and Output

#### **RESISTIVE LOAD**

The feedback resistor alters the load resistance that an amplifier sees. Therefore, it is important to carefully select the value of the feedback resistors used with the AD8546/AD8548. The amplifiers are capable of driving resistive loads down to  $100~k\Omega$ . The Inverting Op Amp Configuration section and the Noninverting Op Amp Configuration section show how the feedback resistor changes the actual load resistance seen at the output of the amplifier.

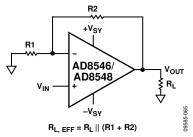

## **Inverting Op Amp Configuration**

Figure 63 shows the AD8546/AD8548 in an inverting configuration with a resistive load,  $R_{\rm L}$ , at the output. The actual load seen by the amplifier is the parallel combination of the feedback resistor, R2, and the load,  $R_{\rm L}$ . For example, the combination of a feedback resistor of 1 k $\Omega$  and a load of 1 M $\Omega$  results in an equivalent load resistance of 999  $\Omega$  at the output. Because the AD8546/AD8548 are incapable of driving such a heavy load, performance degrades greatly.

To avoid loading the output, use a larger feedback resistor, but consider the effect of resistor thermal noise on the overall circuit.

Figure 63. Inverting Op Amp Configuration

## **Noninverting Op Amp Configuration**

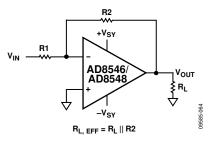

Figure 64 shows the AD8546/AD8548 in a noninverting configuration with a resistive load,  $R_{\rm L}$ , at the output. The actual load seen by the amplifier is the parallel combination of R1 + R2 and  $R_{\rm L}$ .

Figure 64. Noninverting Op Amp Configuration

#### **COMPARATOR OPERATION**

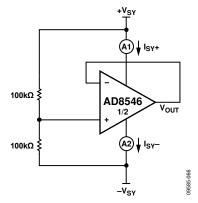

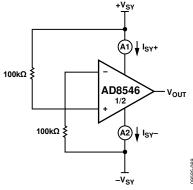

An op amp is designed to operate in a closed-loop configuration with feedback from its output to its inverting input. Figure 65 shows the AD8546 configured as a voltage follower with an input voltage that is always kept at the midpoint of the power supplies. The same configuration is applied to the unused channel. A1 and A2 indicate the placement of ammeters to measure supply current.  $I_{\text{SY}}+$  refers to the current flowing from the upper supply rail to the op amp, and  $I_{\text{SY}}-$  refers to the current flowing from the op amp to the lower supply rail.

Figure 65. Voltage Follower Configuration

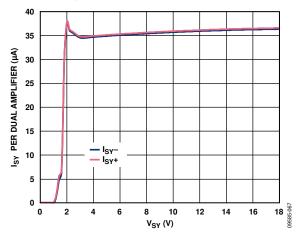

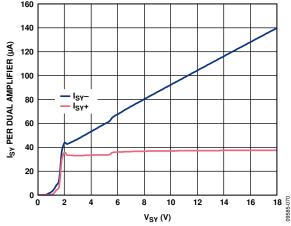

As expected, Figure 66 shows that in normal operating condition, the total current flowing into the op amp is equivalent to the total current flowing out of the op amp, where  $I_{\text{SY}}+=I_{\text{SY}}-=36~\mu\text{A}$  for the AD8546 at  $V_{\text{SY}}=18~\text{V}$ .

Figure 66. Supply Current vs. Supply Voltage (Voltage Follower)

In contrast to op amps, comparators are designed to work in an open-loop configuration and to drive logic circuits. Although op amps are different from comparators, occasionally an unused section of a dual or quad op amp is used as a comparator to save board space and cost; however, this is not recommended.

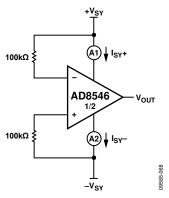

Figure 67 and Figure 68 show the AD8546 configured as a comparator, with 100 k $\Omega$  resistors in series with the input pins. The unused channel is configured as a buffer with the input voltage kept at the midpoint of the power supplies.

Figure 67. Comparator Configuration A

Figure 68. Comparator Configuration B

The AD8546/AD8548 have input devices that are protected from large differential input voltages by Diode D1 and Diode D2 (see Figure 61). These diodes consist of substrate PNP bipolar transistors and turn on when the differential input voltage exceeds approximately 600 mV; however, these diodes also allow a current path from the input to the lower supply rail, resulting in an increase in the total supply current of the system. As shown in Figure 69, both configurations yield the same result. At 18 V of power supply,  $I_{\rm SY}$ + remains at 36  $\mu$ A per dual amplifier, but  $I_{\rm SY}$ - increases to 140  $\mu$ A in magnitude per dual amplifier.

Figure 69. Supply Current vs. Supply Voltage (AD8546 as a Comparator)

Note that  $100 \text{ k}\Omega$  resistors are used in series with the input of the op amp. If smaller resistor values are used, the supply current of the system increases much more. For more information about using op amps as comparators, see the AN-849 Application Note, Using Op Amps as Comparators.

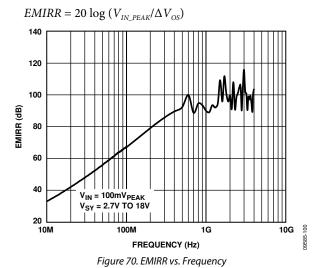

## **EMI REJECTION RATIO**

Circuit performance is often adversely affected by high frequency electromagnetic interference (EMI). In the event where signal strength is low and transmission lines are long, an op amp must accurately amplify the input signals. However, all op amp pins—the noninverting input, inverting input, positive supply, negative supply, and output pins—are susceptible to EMI signals. These high frequency signals are coupled into an op amp by various means such as conduction, near field radiation, or far field radiation. For instance, wires and PCB traces can act as antennas and pick up high frequency EMI signals.

Op amps, such as the AD8546 and AD8548, do not amplify EMI or RF signals because of their relatively low bandwidth. However, due to the nonlinearities of the input devices, op amps can rectify these out-of-band signals. When these high frequency signals are rectified, they appear as a dc offset at the output.

To describe the ability of the AD8546/AD8548 to perform as intended in the presence of an electromagnetic energy, the electromagnetic interference rejection ratio (EMIRR) of the noninverting pin is specified in Table 2, Table 3, and Table 4 of the Specifications section. A mathematical method of measuring EMIRR is defined as follows:

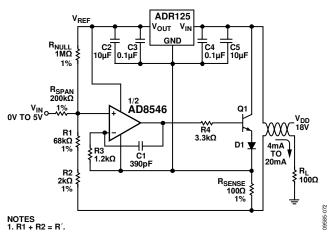

# 4 mA TO 20 mA PROCESS CONTROL CURRENT LOOP TRANSMITTER

A 2-wire current transmitter is often used in distributed control systems and process control applications to transmit analog signals between sensors and process controllers. Figure 71 shows a 4 mA to 20 mA current loop transmitter.

Figure 71. 4 mA to 20 mA Current Loop Transmitter

The transmitter is powered directly from the control loop power supply, and the current in the loop carries signal from 4 mA to 20 mA. Thus, 4 mA establishes the baseline current budget within which the circuit must operate.

The AD8546 is an excellent choice due to its low supply current of 33  $\mu A$  per amplifier over temperature and supply voltage. The current transmitter controls the current flowing in the loop, where a zero-scale input signal is represented by 4 mA of current and a full-scale input signal is represented by 20 mA. The transmitter also floats from the control loop power supply,  $V_{DD}$ , whereas signal ground is in the receiver. The loop current is measured at the load resistor,  $R_{I}$ , at the receiver side.

With a zero-scale input, a current of  $V_{\text{REF}}/R_{\text{NULL}}$  flows through R´. This creates a current,  $I_{\text{SENSE}}$ , that flows through the sense resistor, as determined by the following equation:

$$I_{SENSE, MIN} = (V_{REF} \times R')/(R_{NULL} \times R_{SENSE})$$

With a full-scale input voltage, current flowing through R  $\dot{}$  is increased by the full-scale change in  $V_{IN}/R_{SPAN}$ . This creates an increase in the current flowing through the sense resistor.

$I_{SENSE, DELTA} = (Full-Scale Change in V_{IN} \times R')/(R_{SPAN} \times R_{SENSE})$ Therefore,

$$I_{SENSE, MAX} = I_{SENSE, MIN} + I_{SENSE, DELTA}$$

When R' >>  $R_{SENSE}$ , the current through the load resistor at the receiver side is almost equivalent to  $I_{SENSE}$ .

Figure 71 shows a design for a full-scale input voltage of 5 V. At 0 V of input, the loop current is 3.5 mA, and at a full-scale input of 5 V, the loop current is 21 mA. This allows software calibration to fine-tune the current loop to the 4 mA to 20 mA range.

Together, the AD8546 and the ADR125 consume quiescent current of only 160  $\mu A,$  making 3.34 mA current available to power additional signal conditioning circuitry or to power a bridge circuit.

## **OUTLINE DIMENSIONS**

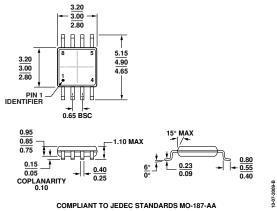

Figure 72. 8-Lead Mini Small Outline Package [MSOP] (RM-8) Dimensions shown in millimeters

COMPLIANT TO JEDEC STANDARDS MS-012-AB

CONTROLLING DIMENSIONS ARE IN MILLIMETERS; INCH DIMENSIONS

(IN PARENTHESES) ARE ROUNDED-OFF MILLIMETER EQUIVALENTS FOR

REFERENCE ONLY AND ARE NOT APPROPRIATE FOR USE IN DESIGN.

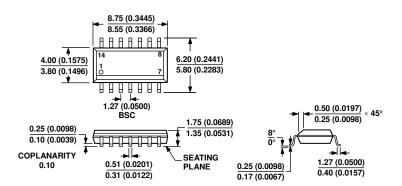

Figure 73. 14-Lead Standard Small Outline Package [SOIC\_N] Narrow Body (R-14) Dimensions shown in millimeters and (inches)

## **ORDERING GUIDE**

| Model <sup>1</sup> | Temperature Range | Package Description                             | Package Option | Branding |

|--------------------|-------------------|-------------------------------------------------|----------------|----------|

| AD8546ARMZ         | -40°C to +125°C   | 8-Lead Mini Small Outline Package [MSOP]        | RM-8           | A2V      |

| AD8546ARMZ-RL      | -40°C to +125°C   | 8-Lead Mini Small Outline Package [MSOP]        | RM-8           | A2V      |

| AD8546ARMZ-R7      | -40°C to +125°C   | 8-Lead Mini Small Outline Package [MSOP]        | RM-8           | A2V      |

| AD8548ARZ          | -40°C to +125°C   | 14-Lead Standard Small Outline Package [SOIC_N] | R-14           |          |

| AD8548ARZ-RL       | -40°C to +125°C   | 14-Lead Standard Small Outline Package [SOIC_N] | R-14           |          |

| AD8548ARZ-R7       | -40°C to +125°C   | 14-Lead Standard Small Outline Package [SOIC_N] | R-14           |          |

$<sup>^{1}</sup>$  Z = RoHS Compliant Part.

# **NOTES**

# **NOTES**

**NOTES**