Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# Dual, 16-Bit, 2.25 GSPS, TxDAC+ Digital-to-Analog Converter

Data Sheet AD9152

#### **FEATURES**

Supports input data rates up to 1.125 GSPS

Proprietary low spurious and distortion design

Single carrier LTE 20 MHz bandwidth (BW), ACLR = 77 dBc

at 180 MHz IF

SFDR = 72 dBc at 150 MHz IF, −6 dBFS

Flexible 4-lane JESD204B interface

Multiple chip synchronization

**Fixed latency**

**Data generator latency compensation**

Selectable  $1\times$ ,  $2\times$ ,  $4\times$ , and  $8\times$  interpolation filter

Low power architecture

Input signal power detection

Emergency stop for downstream analog circuitry protection

Transmit enable function allows extra power saving

High performance, low noise, phase-locked loop (PLL) clock multiplier

Digital inverse sinc filter and programmable finite impulse response (FIR) filter

Low power: 1223 mW at 1.5 GSPS, 1406 mW at 2.0 GSPS, full operating conditions

56-lead LFCSP with exposed pad

#### **APPLICATIONS**

Wireless communications

**Multicarrier LTE and GSM base stations**

Wideband repeaters

Software defined radios

Wideband communications

Point to point microwave radios

LMDS/MMDS

Transmit diversity, multiple input/multiple output (MIMO)

Instrumentation

**Automated test equipment**

#### **GENERAL DESCRIPTION**

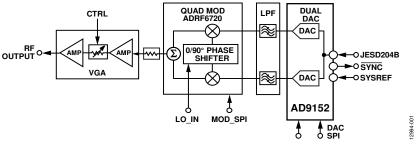

The AD9152 is a dual, 16-bit, high dynamic range digital-to-analog converter (DAC) that provides a maximum sample rate of 2.25 GSPS, permitting a multicarrier generation up to the Nyquist frequency. The DAC outputs are optimized to interface seamlessly with the ADRF6720 analog quadrature modulator (AQM) from Analog Devices, Inc. An optional 3-wire or 4-wire serial port interface (SPI) provides for programming/readback of many internal parameters. The full-scale output current can be programmed over a range of 4 mA to 20 mA. The AD9152 is available in a 56-lead LFCSP. The AD9152 is a member of the TxDAC+\* family.

#### **PRODUCT HIGHLIGHTS**

- 1. Ultrawide signal bandwidth enables emerging wideband and multiband wireless applications.

- 2. Advanced low spurious and distortion design techniques provide high quality synthesis of wideband signals from baseband to high intermediate frequencies.

- JESD204B Subclass 1 support simplifies multichip synchronization in software and hardware design.

- 4. Fewer pins for data interface width with the serializer/ descrializer (SERDES) JESD204B four-lane interface.

- 5. Programmable transmit enable function allows easy design balance between power consumption and wake-up time.

- 6. Small package size with an  $8 \text{ mm} \times 8 \text{ mm}$  footprint.

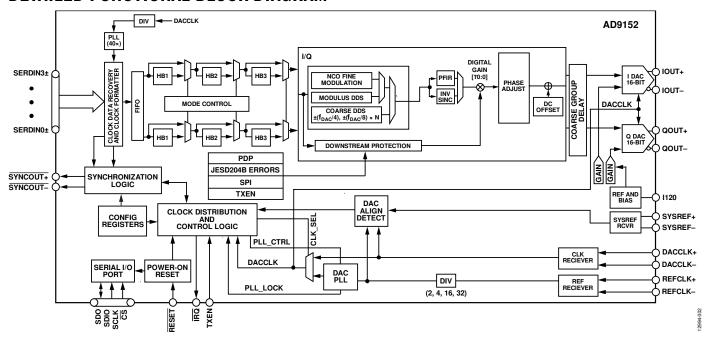

## **FUNCTIONAL BLOCK DIAGRAM**

Figure 1.

# **AD9152\* PRODUCT PAGE QUICK LINKS**

Last Content Update: 02/23/2017

## COMPARABLE PARTS -

View a parametric search of comparable parts.

## **EVALUATION KITS**

· AD9152 Evaluation Board

## **DOCUMENTATION**

## **Data Sheet**

AD9152: Dual, 16-Bit, 2.25 GSPS, TxDAC+ Digital-to-Analog Converter Data Sheet

## TOOLS AND SIMULATIONS $\Box$

- AD9144/AD9152/AD9154/AD9135/AD9136 AMI Model Download

- AD9152 IBIS Model

## **DESIGN RESOURCES**

- · AD9152 Material Declaration

- PCN-PDN Information

- · Quality And Reliability

- · Symbols and Footprints

## **DISCUSSIONS**

View all AD9152 EngineerZone Discussions.

## SAMPLE AND BUY 🖵

Visit the product page to see pricing options.

## **TECHNICAL SUPPORT**

Submit a technical question or find your regional support number.

## DOCUMENT FEEDBACK 🖳

Submit feedback for this data sheet.

# **TABLE OF CONTENTS**

| Features                                                | JESD204B Setup                                      | 27   |

|---------------------------------------------------------|-----------------------------------------------------|------|

| Applications1                                           | SERDES Clocks Setup                                 | 28   |

| General Description1                                    | Equalization Mode Setup                             | 28   |

| Product Highlights1                                     | Link Latency Setup                                  | 28   |

| Functional Block Diagram1                               | Crossbar Setup                                      | 30   |

| Revision History                                        | JESD204B Serial Data Interface                      | 31   |

| Detailed Functional Block Diagram4                      | JESD204B Overview                                   | 31   |

| Specifications5                                         | Physical Layer                                      | 32   |

| DC Specifications                                       | Data Link Layer                                     | 35   |

| Digital Specifications6                                 | Transport Layer                                     | 43   |

| Maximum DAC Update Rate Speed Specifications by Supply7 | JESD204B Test Modes                                 | 51   |

| JESD204B Serial Interface Speed Specifications          | JESD204B Error Monitoring                           | 52   |

| SYSREF± to DAC Clock Timing Specifications8             | Digital Datapath                                    | 54   |

| Digital Input Data Timing Specifications 8              | Data Format                                         | 54   |

| Latency Variation Specifications9                       | Interpolation Filters                               | 54   |

| JESD204B Interface Electrical Specifications9           | Digital Modulation                                  | 55   |

| AC Specifications                                       | NCO Alignment                                       | 56   |

| Absolute Maximum Ratings11                              | Inverse Sinc                                        | 57   |

| Thermal Resistance                                      | Programmable FIR Filter (PFIR)                      | 57   |

| ESD Caution                                             | Digital Gain, Phase Adjust, DC Offset, and Coarse G | roup |

| Pin Configuration and Function Descriptions12           | Delay                                               | 57   |

| Terminology14                                           | Downstream Protection                               |      |

| Typical Performance Characteristics                     | Datapath PRBS                                       |      |

| Theory of Operation20                                   | DC Test Mode                                        | 62   |

| Serial Port Operation21                                 | Interrupt Request Operation                         | 63   |

| Data Format21                                           | Interrupt Service Routine                           |      |

| Serial Port Pin Descriptions21                          | DAC Input Clock Configurations                      | 64   |

| Serial Port Options                                     | Driving the DACCLK± AND REFCLK± Inputs              |      |

| Chip Information23                                      | Condition Specific Register Writes                  |      |

| Device Setup Guide24                                    | Starting the PLL                                    | 65   |

| Overview24                                              | Analog Outputs                                      |      |

| Step 1: Start Up the DAC24                              | Transmit DAC Operation                              | 67   |

| Step 2: Digital Datapath                                | Temperature Sensor                                  |      |

| Step 3: Transport Layer                                 | Example Start-Up Sequence                           | 69   |

| Step 4: Physical Layer                                  | Step 1: Start Up the DAC                            | 69   |

| Step 5: Data Link Layer                                 | Step 2: Digital Datapath                            | 70   |

| Step 6: Optional Error Monitoring                       | Step 3: Transport Layer                             |      |

| Step 7: Optional Features                               | Step 4: Physical Layer                              |      |

| DAC PLL Setup                                           | Step 5: Data Link Layer                             |      |

| Interpolation27                                         | Step 6: Optional Error Monitoring                   | 70   |

| Board Level Hardware Considerations71                         |

|---------------------------------------------------------------|

| Power Supply Recommendations71                                |

| JESD204B Serial Interface Inputs (SERDIN0± to SERDIN3±) .71   |

| Register Map and Descriptions74                               |

| Device Configuration Register Map74                           |

| REVISION HISTORY                                              |

| 2/2017—Rev. 0 to Rev. A                                       |

| Changes to Figure 24                                          |

| Change to Device Revision Parameter, Table 1423               |

| Changes to Step 1: Start Up the DAC Section and Table 1624    |

| Changes to Digital Datapath Section, Address 0x14, Table 17,  |

| and Table 1826                                                |

| Change to JESD204B Setup Section27                            |

| Changes to SERDES PLL Fixed Register Writes Section33         |

| Added Table 36; Renumbered Sequentially33                     |

| Change to Register Block 0x47, Bit 4, Table 6963              |

| Deleted DAC PLL Fixed Register Writes Section, Figure 70, and |

| Figure 71; Renumbered Sequentially64                          |

| Changes to Temperature Tracking Section, Starting the PLL     |

| Section, and Table 7365                                       |

| Changes to Table 76 and Table 7769                            |

| Changes to Table 7870                                         |

| Changes to Table 8574                                         |

| Changes to Table 8680                                         |

4/2015—Revision 0: Initial Version

| Device Configuration Register Descriptions | 79  |

|--------------------------------------------|-----|

| Outline Dimensions                         | 103 |

| Ordering Guide                             | 103 |

# **DETAILED FUNCTIONAL BLOCK DIAGRAM**

Figure 2. Detailed Functional Block Diagram

# **SPECIFICATIONS** DC SPECIFICATIONS

Table 1.

| Parameter                                            | Test Conditions/Comments                                                                                                                                                                   | Min   | Тур        | Max   | Unit   |

|------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------------|-------|--------|

| RESOLUTION                                           |                                                                                                                                                                                            |       | 16         |       | Bits   |

| ACCURACY                                             |                                                                                                                                                                                            |       |            |       |        |

| Differential Nonlinearity (DNL)                      |                                                                                                                                                                                            |       | ±5.0       |       | LSB    |

| Integral Nonlinearity (INL)                          |                                                                                                                                                                                            |       | ±10.0      |       | LSB    |

| MAIN DAC OUTPUTS                                     |                                                                                                                                                                                            |       |            |       |        |

| Gain Error                                           | With internal reference                                                                                                                                                                    | -5.5  | -1.3       | +5.5  | % FSR  |

| I/Q Gain Mismatch                                    |                                                                                                                                                                                            | -4.5  |            | +4.5  | % FSR  |

| Full-Scale Output Current (Ioutes)                   | Based on a $4 \text{ k}\Omega$ external resistor between I120 and ground                                                                                                                   |       |            |       |        |

| Maximum Setting                                      |                                                                                                                                                                                            | 19.1  | 20.22      | 21.4  | mA     |

| Minimum Setting                                      |                                                                                                                                                                                            | 3.8   | 4.04       | 4.3   | mA     |

| Output Compliance Range                              |                                                                                                                                                                                            | 2.3   |            | 3.47  | mV     |

| Output Resistance                                    |                                                                                                                                                                                            |       | 15         |       | ΜΩ     |

| Output Capacitance                                   |                                                                                                                                                                                            |       | 3.0        |       | pF     |

| Gain DAC Monotonicity                                |                                                                                                                                                                                            |       | Guaranteed |       |        |

| MAIN DAC TEMPERATURE DRIFT                           |                                                                                                                                                                                            |       |            |       |        |

| Offset                                               |                                                                                                                                                                                            |       | 0.1        |       | ppm/°C |

| Gain                                                 |                                                                                                                                                                                            |       | 35         |       | ppm/°C |

| Reference Voltage                                    |                                                                                                                                                                                            |       | 25         |       | ppm/°C |

| REFERENCE                                            |                                                                                                                                                                                            |       |            |       |        |

| Internal Reference Voltage                           |                                                                                                                                                                                            |       | 0.5        |       | V      |

| ANALOG SUPPLY VOLTAGES                               |                                                                                                                                                                                            |       |            |       |        |

| AVDD33                                               | ±5%                                                                                                                                                                                        | 3.13  | 3.3        | 3.47  | V      |

| PVDD12, CVDD12                                       | ±5%                                                                                                                                                                                        | 1.14  | 1.2        | 1.26  | V      |

|                                                      | ±2%                                                                                                                                                                                        | 1.274 | 1.3        | 1.326 | V      |

| SVDD12, PLLVDD12, V <sub>TT</sub>                    | ±5%                                                                                                                                                                                        | 1.14  | 1.2        | 1.26  | V      |

|                                                      | ±2%                                                                                                                                                                                        | 1.274 | 1.3        | 1.326 | V      |

| DIGITAL SUPPLY VOLTAGES                              |                                                                                                                                                                                            |       |            |       |        |

| DVDD12, SDVDD12                                      | ±5%                                                                                                                                                                                        | 1.14  | 1.2        | 1.26  | V      |

|                                                      | ±2%                                                                                                                                                                                        | 1.274 | 1.3        | 1.326 | V      |

| SIOVDD33                                             | ±5%                                                                                                                                                                                        | 3.13  | 3.3        | 3.47  | V      |

| IOVDD                                                | ±5%                                                                                                                                                                                        | 1.71  | 1.8        | 3.47  | V      |

| POWER CONSUMPTION                                    |                                                                                                                                                                                            |       |            |       |        |

| Total Power                                          | $2\times$ interpolation mode, $f_{DAC}=1.5$ GSPS, IF = 70 MHz, PLL off, INVSINC on, digital gain on, NCO on, JESD204B Mode 4, four SERDES lanes with 7.5 Gbps lane rate, $I_{OUTFS}=20$ mA |       | 1223       |       | mW     |

| AVDD33                                               |                                                                                                                                                                                            | 1     | 87         |       | mA     |

| PVDD12                                               |                                                                                                                                                                                            |       | 11         |       | mA     |

| CVDD12                                               |                                                                                                                                                                                            | 1     | 179        |       | mA     |

| SDVDD12 and SVDD12 (Includes PLLVDD12 and $V_{TT}$ ) |                                                                                                                                                                                            |       | 328        |       | mA     |

| DVDD12                                               |                                                                                                                                                                                            | 1     | 246        |       | mA     |

| SIOVDD33 and IOVDD                                   |                                                                                                                                                                                            | 1     | 5.7        |       | mA     |

| OPERATING TEMPERATURE RANGE                          |                                                                                                                                                                                            | -40   | +25        | +85   | °C     |

## **DIGITAL SPECIFICATIONS**

$AVDD33 = 3.3 \text{ V}, SIOVDD33 = 3.3 \text{ V}, IOVDD = 1.8 \text{ V}, DVDD12 = 1.2 \text{ V}, CVDD12 = 1.2 \text{ V}, PVDD12 = 1.2 \text{ V}, PLLVDD12 = 1.2 \text{ V}, SVDD12 = 1.2 \text{ V}, SDVDD12 = 1.2 \text{ V}, V_{TT} = 1.2 \text{ V}, T_A = -40^{\circ}\text{C} \text{ to} +85^{\circ}\text{C}, I_{OUTFS} = 20 \text{ mA}, unless otherwise noted.}$

Table 2.

| Parameter                                | Symbol           | Test Conditions/Comments                   | Min         | Тур  | Max                     | Unit  |

|------------------------------------------|------------------|--------------------------------------------|-------------|------|-------------------------|-------|

| CMOS INPUT LOGIC LEVEL                   |                  |                                            |             |      |                         |       |

| Input Voltage Logic                      | V <sub>IN</sub>  |                                            |             |      |                         |       |

| High                                     |                  | 1.8 V ≤ IOVDD ≤ 3.3 V                      | 0.7 × IOVDD |      |                         | V     |

| Low                                      |                  | 1.8 V ≤ IOVDD ≤ 3.3 V                      |             |      | $0.3 \times IOVDD$      | V     |

| CMOS OUTPUT LOGIC LEVEL                  |                  |                                            |             |      |                         |       |

| Output Voltage Logic                     | V <sub>OUT</sub> |                                            |             |      |                         |       |

| High                                     |                  | 1.8 V ≤ IOVDD ≤ 3.3 V                      | 0.7 × IOVDD |      |                         | V     |

| Low                                      |                  | 1.8 V ≤ IOVDD ≤ 3.3 V                      |             |      | 0.3 × IOVDD             | V     |

| MAXIMUM DAC UPDATE RATE <sup>1</sup>     |                  | DVDD12 = CVDD12 = PVDD12 =                 |             |      |                         | -     |

|                                          |                  | $1.3 \text{ V} \pm 2\%$                    |             |      |                         |       |

|                                          |                  | 1× interpolation <sup>2</sup>              | 1238        |      |                         | MSPS  |

|                                          |                  | 2× interpolation                           | 2250        |      |                         | MSPS  |

|                                          |                  | 4× interpolation                           | 2250        |      |                         | MSPS  |

|                                          |                  | 8× interpolation                           | 2250        |      |                         | MSPS  |

| ADJUSTED DAC UPDATE RATE                 |                  | DVDD12 = CVDD12 = PVDD12 = 1.3 V ± 2%      |             |      |                         |       |

|                                          |                  | 1× interpolation                           | 1238        |      |                         | MSPS  |

|                                          |                  | 2× interpolation                           | 1125        |      |                         | MSPS  |

|                                          |                  | 4× interpolation                           | 562.5       |      |                         | MSPS  |

|                                          |                  | 8× interpolation                           | 281.25      |      |                         | MSPS  |

| INTERFACE <sup>3</sup>                   |                  |                                            |             |      |                         |       |

| Number of JESD204B Lanes                 |                  |                                            |             | 4    |                         | Lanes |

| JESD204B Serial Interface Speed          |                  | SVDD12 = SDVDD12 = PLLVDD12 =              |             |      |                         |       |

|                                          |                  | 1.3 V ± 2%                                 |             |      |                         |       |

| Minimum                                  |                  | Per lane                                   |             |      | 1.44                    | Gbps  |

| Maximum                                  |                  | Per lane                                   | 12.38       |      |                         | Gbps  |

| DAC CLOCK INPUT (DACCLK±)                |                  |                                            |             |      |                         |       |

| Differential Peak-to-Peak Voltage        |                  |                                            | 400         | 1000 | 2000                    | mV    |

| Common-Mode Voltage                      |                  | Self biased input, ac-coupled              |             | 600  |                         | mV    |

| Maximum Clock Rate                       |                  | DVDD12 = CVDD12 = PVDD12 = 1.3 V ± 2%      | 2250        |      |                         | MHz   |

| REFERENCE CLOCK INPUT (REFCLK±)          |                  |                                            |             |      |                         |       |

| Differential Peak-to-Peak Voltage        |                  |                                            | 400         | 1000 | 2000                    | mV    |

| Common-Mode Voltage                      |                  | Self biased input, ac-coupled              |             | 600  |                         | mV    |

| Input Clock Frequency (PLL               |                  | 6 GHz ≤ f <sub>VCO</sub> ≤ 12 GHz          | 70          |      | 1000                    | MHz   |

| Mode)                                    |                  |                                            |             |      |                         |       |

| SYSTEM REFERENCE INPUT<br>(SYSREF±)      |                  |                                            |             |      |                         |       |

| Differential Peak-to-Peak                |                  |                                            | 400         | 1000 | 2000                    | mV    |

| Voltage                                  |                  |                                            | 0           |      | 2000                    | mV    |

| Common-Mode Voltage                      |                  |                                            | 0           |      |                         |       |

| SYSREF± Frequency⁴ SYSREF± TO DAC CLOCK⁵ |                  | SYSREF± differential swing = 1.2 V,        |             |      | $f_{DATA}/(K \times S)$ | Hz    |

| STAREFE TO DAC CLOCK                     |                  | slew rate = 6.3 V/ns, hysteresis off (ac-  |             |      |                         |       |

|                                          |                  | coupled, and 0 V, 0.6 V, 1.25 V, 2.0 V dc- |             |      |                         |       |

|                                          |                  | coupled common-mode voltages)              |             |      |                         |       |

| Setup Time                               | t <sub>SSD</sub> |                                            | -6          |      |                         | ps    |

| Hold Time                                | t <sub>HSD</sub> |                                            | 224         |      |                         | ps    |

| Keep Out Window                          | KOW              |                                            |             | 218  |                         | ps    |

| Parameter                | Symbol            | Test Conditions/Comments | Min | Тур Мах | Unit |

|--------------------------|-------------------|--------------------------|-----|---------|------|

| SPI                      |                   |                          |     |         |      |

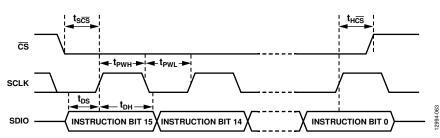

| Maximum Clock Rate       | SCLK              | IOVDD = 1.8 V            | 10  |         | MHz  |

| Minimum SCLK Pulse Width |                   |                          |     |         |      |

| High                     | t <sub>PWH</sub>  |                          |     | 8       | ns   |

| Low                      | t <sub>PWL</sub>  |                          |     | 12      | ns   |

| SDIO to SCLK             |                   |                          |     |         |      |

| Setup Time               | t <sub>DS</sub>   |                          | 5   |         | ns   |

| Hold Time                | t <sub>DH</sub>   |                          | 2   |         | ns   |

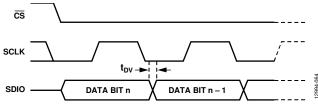

| SDO to SCLK              |                   |                          |     |         |      |

| Data Valid Window        | t <sub>DV</sub>   |                          | 26  |         | ns   |

| CS to SCLK               |                   |                          |     |         |      |

| Setup Time               | tscs              |                          | 5   |         | ns   |

| Hold Time                | t <sub>H</sub> CS |                          | 2   |         | ns   |

<sup>&</sup>lt;sup>1</sup> See Table 3 and Table 4 for detailed specifications for the DAC update rate conditions.

## MAXIMUM DAC UPDATE RATE SPEED SPECIFICATIONS BY SUPPLY

AVDD33 = 3.3 V, SIOVDD33 = 3.3 V, IOVDD = 1.8 V, DVDD12 = 1.2 V, CVDD12 = 1.2 V, PVDD12 = 1.2 V

Table 3.

| Parameter               | Test Conditions/Comments    | Min  | Тур | Max | Unit |

|-------------------------|-----------------------------|------|-----|-----|------|

| MAXIMUM DAC UPDATE RATE | DVDD12, CVDD12 = 1.2 V ± 5% | 1.85 |     |     | GSPS |

|                         | DVDD12, CVDD12 = 1.3 V ± 2% | 2.25 |     |     | GSPS |

#### JESD204B SERIAL INTERFACE SPEED SPECIFICATIONS

Table 4.

| Parameter    | Test Conditions/Comments                            | Min  | Тур | Max   | Unit |

|--------------|-----------------------------------------------------|------|-----|-------|------|

| HALF RATE    | SVDD12, SDVDD12, PLLVDD12 = $1.2 \text{ V} \pm 5\%$ | 5.75 |     | 11.00 | Gbps |

|              | SVDD12, SDVDD12, PLLVDD12 = $1.3 \text{ V} \pm 2\%$ | 5.75 |     | 12.38 | Gbps |

| FULL RATE    | SVDD12, SDVDD12, PLLVDD12 = 1.2 V ± 5%              | 2.88 |     | 5.53  | Gbps |

|              | SVDD12, SDVDD12, PLLVDD12 = $1.3 \text{ V} \pm 2\%$ | 2.88 |     | 6.19  | Gbps |

| OVERSAMPLING | SVDD12, SDVDD12, PLLVDD12 = 1.2 V ± 5%              | 1.44 |     | 2.69  | Gbps |

|              | SVDD12, SDVDD12, PLLVDD12 = $1.3 \text{ V} \pm 2\%$ | 1.44 |     | 3.09  | Gbps |

$<sup>^2</sup>$  The maximum speed for 1× interpolation is limited by the JESD2040B interface. See Table 4 for details.

<sup>&</sup>lt;sup>3</sup> See Table 4 for detailed specifications for JESD2040B speed conditions.

$<sup>^{\</sup>rm 4}\,\rm K$  and S are JESD204B transport layer parameters. See Table 41 for the full definitions.

<sup>&</sup>lt;sup>5</sup> See Table 5 for detailed specifications for SYSREF± to DAC clock timing conditions.

## **SYSREF± TO DAC CLOCK TIMING SPECIFICATIONS**

$AVDD33 = 3.3 \text{ V}, SIOVDD33 = 3.3 \text{ V}, IOVDD = 1.8 \text{ V}, DVDD12 = 1.2 \text{ V}, CVDD12 = 1.2 \text{ V}, PVDD12 = 1.2 \text{ V}, PLLVDD12 = 1.2 \text{ V}, SVDD12 = 1.2 \text{ V}, SDVDD12 = 1.2 \text{ V}, T_A = -40^{\circ}\text{C} \text{ to } +85^{\circ}\text{C}, I_{OUTFS} = 20 \text{ mA}, SYSREF \pm common-mode voltages = 0.0 \text{ V}, 0.6 \text{ V}, 1.25 \text{ V}, and 2.0 \text{ V}, unless otherwise noted.}$

Table 5.

| Parameter                         | Test Conditions/Comments                         | Min | Тур | Max | Unit |

|-----------------------------------|--------------------------------------------------|-----|-----|-----|------|

| SYSREF                            | Differential swing = 1.2 V, slew rate = 6.3 V/ns |     |     |     |      |

| Hysteresis Off                    |                                                  |     |     |     |      |

| Setup Time                        | AC-coupled                                       | -9  |     |     | ps   |

|                                   | DC-coupled                                       | -6  |     |     | ps   |

| Hold Time                         | AC-coupled                                       | 199 |     |     | ps   |

|                                   | DC-coupled                                       | 224 |     |     | ps   |

| Hysteresis On (HYS_CNTRL = 0x3FF) |                                                  |     |     |     |      |

| Setup Time                        | AC-coupled                                       | 143 |     |     | ps   |

|                                   | DC-coupled                                       | 145 |     |     | ps   |

| Hold Time                         | AC-coupled                                       | 97  |     |     | ps   |

|                                   | DC-coupled                                       | 123 |     |     | ps   |

## **DIGITAL INPUT DATA TIMING SPECIFICATIONS**

Table 6.

| Parameter            | Test Conditions/Comments         | Min | Тур | Max | Unit                       |

|----------------------|----------------------------------|-----|-----|-----|----------------------------|

| LATENCY              |                                  |     |     |     |                            |

| Interface            |                                  |     | 17  |     | PClock <sup>1</sup> cycles |

| Interpolation        |                                  |     |     |     |                            |

| 1×                   |                                  |     | 143 |     | DAC clock cycles           |

| 2×                   |                                  |     | 163 |     | DAC clock cycles           |

| 4×                   |                                  |     | 287 |     | DAC clock cycles           |

| 8×                   |                                  |     | 557 |     | DAC clock cycles           |

| Inverse Sinc         |                                  |     | 17  |     | DAC clock cycles           |

| Fine Modulation      |                                  |     | 20  |     | DAC clock cycles           |

| Coarse Modulation    |                                  |     |     |     |                            |

| $f_S/8$              |                                  |     | 8   |     | DAC clock cycles           |

| fs/4                 |                                  |     | 4   |     | DAC clock cycles           |

| Digital Phase Adjust |                                  |     | 12  |     | DAC clock cycles           |

| Digital Gain Adjust  |                                  |     | 12  |     | DAC clock cycles           |

| Power-Up Time        | Register 0x011 from 0x60 to 0x00 |     | 60  |     | μs                         |

$<sup>^{1}\,</sup>PClock$  is the AD9152 internal processing clock and equals the lane rate  $\div$  40.

## **LATENCY VARIATION SPECIFICATIONS**

AVDD33 = 3.3 V, SIOVDD33 = 3.3 V, IOVDD = 1.8 V, DVDD12 = 1.2 V, CVDD12 = 1.2 V, PVDD12 = 1.2 V

Table 7.

| Parameter             | Test Conditions/Comments                                            | Min | Тур | Max | Unit             |

|-----------------------|---------------------------------------------------------------------|-----|-----|-----|------------------|

| DAC LATENCY VARIATION | Given proper calibration of the local multiframe clock (LMFC) delay |     |     |     |                  |

| Subclass 1            |                                                                     |     |     |     | DAC clock cycles |

| PLL Off               |                                                                     | -3  | 0   | +3  | DAC clock cycles |

| PLL On                |                                                                     | -4  |     | +4  | DAC clock cycles |

## **JESD204B INTERFACE ELECTRICAL SPECIFICATIONS**

Table 8.

| Parameter                                    | Symbol              | Test Conditions/Comments                                                           | Min   | Тур | Max   | Unit                       |

|----------------------------------------------|---------------------|------------------------------------------------------------------------------------|-------|-----|-------|----------------------------|

| JESD204B DATA INPUTS                         |                     |                                                                                    |       |     |       |                            |

| Input Leakage Current                        |                     | $T_A = 25$ °C                                                                      |       |     |       |                            |

| Logic High                                   |                     | Input level = $1.2 \text{ V} \pm 0.25 \text{ V}$ , $\text{V}_{TT} = 1.2 \text{ V}$ |       | 10  |       | μΑ                         |

| Logic Low                                    |                     | Input level = 0 V                                                                  |       | -4  |       | μΑ                         |

| Unit Interval                                | UI                  |                                                                                    | 81    |     | 694   | ps                         |

| Common-Mode Voltage                          | $V_{RCM}$           | AC-coupled                                                                         | -0.05 |     | +1.85 | V                          |

|                                              |                     | $V_{TT} = SVDD12^1$                                                                |       |     |       |                            |

| Differential Voltage                         | R_V <sub>DIFF</sub> |                                                                                    | 110   |     | 1050  | mV                         |

| V <sub>™</sub> Source Impedance              | Z <sub>TT</sub>     | At dc                                                                              |       |     | 30    | Ω                          |

| Differential Impedance                       | Z <sub>RDIFF</sub>  | At dc                                                                              | 80    | 100 | 120   | Ω                          |

| Differential Return Loss                     | RL <sub>RDIF</sub>  |                                                                                    |       | 8   |       | dB                         |

| Common-Mode Return Loss                      | RL <sub>RCM</sub>   |                                                                                    |       | 6   |       | dB                         |

| DIFFERENTIAL OUTPUTS (SYNCOUT±) <sup>2</sup> |                     |                                                                                    |       |     |       |                            |

| Output Offset Voltage                        | Vos                 |                                                                                    | 1.15  |     | 1.25  | V                          |

| Output Differential Voltage                  | V <sub>OD</sub>     | High swing mode: Register 0x230,                                                   | 350   |     | 410   | mV                         |

|                                              |                     | Bit 0 = 1                                                                          |       |     |       |                            |

| DETERMINISTIC LATENCY                        |                     |                                                                                    |       |     |       |                            |

| Fixed                                        |                     |                                                                                    |       |     | 17    | PClock <sup>3</sup> cycles |

| Variable                                     |                     |                                                                                    |       |     | 2     | PClock <sup>3</sup> cycles |

| SYSREF± TO LMFC DELAY                        |                     |                                                                                    |       | 4   |       | DAC clock cycles           |

<sup>&</sup>lt;sup>1</sup> As measured on the input side of the ac coupling capacitor.

<sup>&</sup>lt;sup>2</sup> IEEE Standard 1596.3 LVDS compatible.

$<sup>^3</sup>$  PClock is the AD9152 internal processing clock and equals the lane rate  $\div$  40.

## **AC SPECIFICATIONS**

$AVDD33 = 3.3 \text{ V}, SIOVDD33 = 3.3 \text{ V}, IOVDD = 1.8 \text{ V}, DVDD12 = 1.2 \text{ V}, CVDD12 = 1.2 \text{ V}, PVDD12 = 1.2 \text{ V}, PLLVDD12 = 1.2 \text{ V}, SVDD12 = 1.2 \text{ V}, SDVDD12 = 1.2 \text{ V}, V_{TT} = 1.2 \text{ V}, T_A = -40^{\circ}\text{C} \text{ to} +85^{\circ}\text{C}, I_{OUTFS} = 20 \text{ mA}, unless otherwise noted.}$

Table 9.

| Parameter                                                                   | Test Conditions/Comments   | Min | Тур    | Max | Unit   |

|-----------------------------------------------------------------------------|----------------------------|-----|--------|-----|--------|

| SPURIOUS-FREE DYNAMIC RANGE (SFDR)                                          | −6 dBFS single tone        |     |        |     |        |

| $f_{DAC} = 1966.08 \text{ MSPS}$                                            | $f_{OUT} = 20 \text{ MHz}$ |     | 76     |     | dBc    |

|                                                                             | f <sub>OUT</sub> = 150 MHz |     | 72     |     | dBc    |

|                                                                             | f <sub>OUT</sub> = 180 MHz |     | 68     |     | dBc    |

| TWO-TONE THIRD INTERMODULATION DISTORTION (IMD)                             | −6 dBFS                    |     |        |     |        |

| $f_{DAC} = 983.04 \text{ MSPS}$                                             | f <sub>OUT</sub> = 30 MHz  |     | 86     |     | dBc    |

|                                                                             | f <sub>OUT</sub> = 150 MHz |     | 79     |     | dBc    |

| $f_{DAC} = 1966.08 \text{ MSPS}$                                            | f <sub>OUT</sub> = 30 MHz  |     | 86     |     | dBc    |

|                                                                             | f <sub>OUT</sub> = 180 MHz |     | 78     |     | dBc    |

| NOISE SPECTRAL DENSITY (NSD), SINGLE TONE                                   | 0 dBFS                     |     |        |     |        |

| $f_{DAC} = 983.04 \text{ MSPS}$                                             | f <sub>OUT</sub> = 150 MHz |     | -162.5 |     | dBm/Hz |

| $f_{DAC} = 1966.08 \text{ MSPS}$                                            | f <sub>OUT</sub> = 180 MHz |     | -163   |     | dBm/Hz |

| 5 MHz BW LTE FIRST ADJACENT CHANNEL LEAKAGE<br>RATIO (ACLR), SINGLE CARRIER | 0 dBFS, PLL off            |     |        |     |        |

| $f_{DAC} = 1966.08 \text{ MSPS}$                                            | f <sub>OUT</sub> = 50 MHz  |     | 79     |     | dBc    |

|                                                                             | f <sub>OUT</sub> = 150 MHz |     | 77     |     | dBc    |

|                                                                             | f <sub>OUT</sub> = 180 MHz |     | 77     |     | dBc    |

| 5 MHz BW LTE SECOND ACLR, SINGLE CARRIER                                    | 0 dBFS, PLL off            |     |        |     |        |

| $f_{DAC} = 1966.08 \text{ MSPS}$                                            | f <sub>OUT</sub> = 50 MHz  |     | 82     |     | dBc    |

|                                                                             | f <sub>оит</sub> = 150 MHz |     | 81     |     | dBc    |

|                                                                             | f <sub>оит</sub> = 180 MHz |     | 81     |     | dBc    |

## **ABSOLUTE MAXIMUM RATINGS**

Table 10.

| 14010 101                                       |                            |

|-------------------------------------------------|----------------------------|

| Parameter                                       | Rating                     |

| I120 to Ground                                  | -0.3 V to AVDD33 + 0.3 V   |

| SERDINx±, V <sub>TT</sub> , SYNCOUT±, TXEN      | -0.3 V to SIOVDD33 + 0.3 V |

| IOUT±, QOUT±                                    | -0.3 V to AVDD33 + 0.3 V   |

| SYSREF±                                         | GND – 0.5 V to +2.5 V      |

| DACCLK± and REFCLK± to Ground                   | -0.3 V to PVDD12 + 0.3 V   |

| RESET, IRQ, CS, SCLK, SDIO, SDO,                | -0.3 V to IOVDD + 0.3 V    |

| PROTECT_OUT to Ground                           |                            |

| LDO_BYP1                                        | −0.3 V to SVDD12 + 0.3 V   |

| LDO_BYP2                                        | −0.3 V to PVDD12 + 0.3 V   |

| Ambient Operating Temperature (T <sub>A</sub> ) | −40°C to +85°C             |

| Junction Temperature                            | 125°C                      |

| Storage Temperature Range                       | −65°C to +150°C            |

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

## THERMAL RESISTANCE

The exposed pad (EPAD) must be soldered to the ground plane for the 56-lead LFCSP. The EPAD provides an electrical, thermal, and mechanical connection to the board.

Typical  $\theta_{JA}$ ,  $\theta_{JB}$ , and  $\theta_{JC}$  values are specified for a 4-layer JESD51-7 high effective thermal conductivity test board for leaded surface-mount packages.  $\theta_{JA}$  is obtained in still air conditions (JESD51-2). Airflow increases heat dissipation, effectively reducing  $\theta_{JA}$ .  $\theta_{JB}$  is obtained following double-ring cold plate test conditions (JESD51-8).  $\theta_{JC}$  is obtained with the test case temperature monitored at the bottom of the exposed pad.

$\Psi_{JT}$  and  $\Psi_{JB}$  are thermal characteristic parameters obtained with  $\theta_{JA}$  in still air test conditions.

Junction temperature (T<sub>J</sub>) can be estimated using the following equations:

$$T_{J} = T_{T} + (\Psi_{JT} \times P)$$

or

$T_{I} = T_{B} + (\Psi_{IB} \times P)$

where:

$T_T$  is the temperature measured at the top of the package. P is the total device power dissipation.

$T_B$  is the temperature measured at the board.

**Table 11. Thermal Resistance**

| Package                    | $\theta_{JA}$ | θЈВ | θις | Ψл  | $\Psi_{JB}$ | Unit |

|----------------------------|---------------|-----|-----|-----|-------------|------|

| 56-Lead LFCSP <sup>1</sup> | 25.5          | 4.8 | 1.7 | 0.1 | 4.8         | °C/W |

<sup>&</sup>lt;sup>1</sup> The exposed pad must be securely connected to the ground plane.

#### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

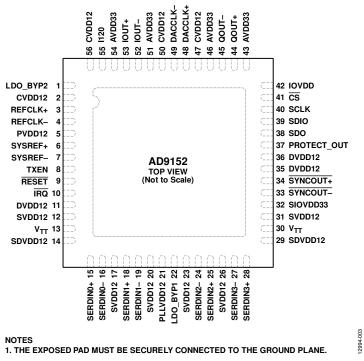

## PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Figure 3. Pin Configuration

**Table 12. Pin Function Descriptions**

| Pin No. | Mnemonic        | Description                                                                                                                                                                 |

|---------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | LDO_BYP2        | LDO Clock Bypass for the DAC PLL. This pin requires a 1 $\Omega$ resistor in series with a 1 $\mu$ F capacitor to ground.                                                   |

| 2       | CVDD12          | 1.2 V Clock Supply.                                                                                                                                                         |

| 3       | REFCLK+         | PLL Reference Clock Input, Positive.                                                                                                                                        |

| 4       | REFCLK-         | PLL Reference Clock Input, Negative.                                                                                                                                        |

| 5       | PVDD12          | 1.2 V Supply. This pin supplies the DAC PLL and clock receiver circuitry.                                                                                                   |

| 6       | SYSREF+         | Positive Reference Clock for Deterministic Latency. This pin is self biased for ac coupling. This pin may be accoupled or dc-coupled.                                       |

| 7       | SYSREF—         | Negative Reference Clock for Deterministic Latency. This pin is self biased for ac coupling. This pin may be ac-coupled or dc-coupled.                                      |

| 8       | TXEN            | Transmitter (Tx) Enable for I DAC and Q DAC. CMOS levels are determined with respect to IOVDD.                                                                              |

| 9       | RESET           | Reset (Active Low). CMOS levels are determined with respect to IOVDD.                                                                                                       |

| 10      | ĪRQ             | Interrupt Request (Active Low, Open Drain).                                                                                                                                 |

| 11      | DVDD12          | 1.2 V Digital Supply.                                                                                                                                                       |

| 12      | SVDD12          | 1.2 V JESD204B Receiver (Rx) Analog Supply.                                                                                                                                 |

| 13      | V <sub>TT</sub> | 1.2 V Termination Voltage. Connect this pin to the SVDD12 pin externally.                                                                                                   |

| 14      | SDVDD12         | 1.2 V JESD204B Rx Digital Supply.                                                                                                                                           |

| 15      | SERDIN0+        | Serial Channel Input 0, Positive. CML compliant. SERDIN0+ is 50 $\Omega$ terminated to the V <sub>TT</sub> pin voltage. This pin is ac-coupled only. Resistance calibrated. |

| 16      | SERDINO-        | Serial Channel Input 0, Negative. CML compliant. SERDIN0– is $50 \Omega$ terminated to the $V_{TT}$ pin voltage. This pin is ac-coupled only. Resistance calibrated.        |

| 17      | SVDD12          | 1.2 V JESD204B Rx Analog Supply.                                                                                                                                            |

| 18      | SERDIN1+        | Serial Channel Input 1, Positive. CML compliant. SERDIN1+ is $50 \Omega$ terminated to the $V_{TT}$ pin voltage. This pin is ac-coupled only. Resistance calibrated.        |

| 19      | SERDIN1-        | Serial Channel Input 1, Negative. CML compliant. SERDIN1– is $50 \Omega$ terminated to the $V_{TT}$ pin voltage. This pin is ac-coupled only. Resistance calibrated.        |

| 20      | SVDD12          | 1.2 V JESD204B Rx Analog Supply.                                                                                                                                            |

| 21      | PLLVDD12        | 1.2 V SERDES PLL Supply.                                                                                                                                                    |

| 22      | LDO_BYP1        | LDO SERDES Bypass. This pin requires a 1 $\Omega$ resistor in series with a 1 $\mu$ F capacitor to ground.                                                                  |

| Pin No. | Mnemonic        | Description                                                                                                                                                                 |

|---------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 23      | SVDD12          | 1.2 V JESD204B Rx Analog Supply.                                                                                                                                            |

| 24      | SERDIN2-        | Serial Channel Input 2, Negative. CML compliant. SERDIN2— is 50 $\Omega$ terminated to the V <sub>TT</sub> pin voltage. This pin is ac-coupled only. Resistance calibrated  |

| 25      | SERDIN2+        | Serial Channel Input 2, Positive. CML compliant. SERDIN2+ is $50 \Omega$ terminated to the $V_{TT}$ pin voltage. This pin is ac-coupled only. Resistance calibrated.        |

| 26      | SVDD12          | 1.2 V JESD204B Rx Analog Supply.                                                                                                                                            |

| 27      | SERDIN3-        | Serial Channel Input 3, Negative. CML compliant. SERDIN3— is 50 $\Omega$ terminated to the V <sub>TT</sub> pin voltage. This pin is ac-coupled only. Resistance calibrated. |

| 28      | SERDIN3+        | Serial Channel Input 3, Positive. CML compliant. SERDIN3+ is 50 $\Omega$ terminated to the V <sub>TT</sub> pin voltage. This pin is ac-coupled only. Resistance calibrated. |

| 29      | SDVDD12         | 1.2 V JESD204B Rx Digital Supply.                                                                                                                                           |

| 30      | V <sub>TT</sub> | $1.2V$ Termination Voltage. Connect $V_{TT}$ to the SVDD12 pin externally.                                                                                                  |

| 31      | SVDD12          | 1.2 V JESD204B Rx Analog Supply.                                                                                                                                            |

| 32      | SIOVDD33        | 3.3 V Supply for Equalizers.                                                                                                                                                |

| 33      | SYNCOUT_        | Negative LVDS Sync Output Signal.                                                                                                                                           |

| 34      | SYNCOUT+        | Positive LVDS Sync Output Signal.                                                                                                                                           |

| 35      | DVDD12          | 1.2 V Digital Supply.                                                                                                                                                       |

| 36      | DVDD12          | 1.2 V Digital Supply.                                                                                                                                                       |

| 37      | PROTECT_OUT     | Protection Indicator for I DAC and Q DAC. CMOS levels are determined with respect to IOVDD.                                                                                 |

| 38      | SDO             | Serial Port Data Output. CMOS levels are determined with respect to IOVDD.                                                                                                  |

| 39      | SDIO            | Serial Port Data Input/Output. CMOS levels are determined with respect to IOVDD.                                                                                            |

| 40      | SCLK            | Serial Port Clock Input. CMOS levels are determined with respect to IOVDD.                                                                                                  |

| 41      | <del>CS</del>   | Serial Port Chip Select, Active Low. CMOS levels are determined with respect to IOVDD.                                                                                      |

| 42      | IOVDD           | 1.8 V IOVDD Supply for CMOS Input/Output and SPI.                                                                                                                           |

| 43      | AVDD33          | 3.3 V Analog Supply for the DAC Cores.                                                                                                                                      |

| 44      | QOUT+           | Q DAC Positive Current Output.                                                                                                                                              |

| 45      | QOUT-           | Q DAC Negative Current Output.                                                                                                                                              |

| 46      | AVDD33          | 3.3 V Analog Supply for the DAC Cores.                                                                                                                                      |

| 47      | CVDD12          | 1.2 V Clock Supply.                                                                                                                                                         |

| 48      | DACCLK+         | Positive Device Clock When PLL Is Not Used.                                                                                                                                 |

| 49      | DACCLK-         | Negative Device Clock When PLL Is Not Used.                                                                                                                                 |

| 50      | CVDD12          | 1.2 V Clock Supply.                                                                                                                                                         |

| 51      | AVDD33          | 3.3 V Analog Supply for the DAC Cores.                                                                                                                                      |

| 52      | IOUT-           | I DAC Negative Current Output.                                                                                                                                              |

| 53      | IOUT+           | I DAC Positive Current Output.                                                                                                                                              |

| 54      | AVDD33          | 3.3 V Analog Supply for the DAC Cores.                                                                                                                                      |

| 55      | l120            | Output Current Generation Pin for the DAC Full-Scale Current. Tie a $4 \text{ k}\Omega$ resistor from this pin to the ground plane.                                         |

| 56      | CVDD12          | 1.2 V Clock Supply.                                                                                                                                                         |

|         | EPAD            | Exposed Pad. The exposed pad must be securely connected to the ground plane.                                                                                                |

## **TERMINOLOGY**

## **Integral Nonlinearity (INL)**

INL is the maximum deviation of the actual analog output from the ideal output, determined by a straight line drawn from zero scale to full scale.

#### Differential Nonlinearity (DNL)

DNL is the measure of the variation in analog value, normalized to full scale, associated with a 1 LSB change in digital input code.

#### **Offset Error**

Offset error is the deviation of the output current from the ideal of 0 mA. For IOUT+/QOUT+, 0 mA output is expected when all inputs are set to 0. For IOUT-/QOUT-, 0 mA output is expected when all inputs are set to 1.

#### **Gain Error**

Gain error is the difference between the actual and ideal output span. The actual span is determined by the difference between the output when the input is at its minimum code and the output when the input is at its maximum code.

## **Output Compliance Range**

The output compliance range is the range of allowable voltages at the output of a current output DAC. Operation beyond the maximum compliance limits can cause either output stage saturation or breakdown, resulting in nonlinear performance.

## **Temperature Drift**

Temperature drift is specified as the maximum change from the ambient (25°C) value to the value at either  $T_{\text{MIN}}$  or  $T_{\text{MAX}}$ . For offset and gain drift, the drift is reported in ppm of full-scale range (FSR) per degree Celsius. For reference drift, the drift is reported in ppm per degree Celsius.

### Power Supply Rejection (PSR)

PSR is the maximum change in the full-scale output as the supplies are varied from minimum to maximum specified voltages.

## Spurious-Free Dynamic Range (SFDR)

SFDR is the difference, in decibels, between the peak amplitude of the output signal and the peak spurious signal within the dc to Nyquist frequency of the DAC. Typically, energy in this band is rejected by the interpolation filters. This specification, therefore, defines how well the interpolation filters work and the effect of other parasitic coupling paths on the DAC output.

## Signal-to-Noise Ratio (SNR)

SNR is the ratio of the rms value of the measured output signal to the rms sum of all other spectral components below the Nyquist frequency, excluding the first six harmonics and dc. The value for SNR is expressed in decibels.

## **Interpolation Filter**

If the digital inputs to the DAC are sampled at a multiple rate of  $f_{DATA}$  (interpolation rate), a digital filter can be constructed that has a sharp transition band near  $f_{DATA}/2$ . Images that typically appear around  $f_{DAC}$  (output data rate) can be greatly suppressed.

#### Adjacent Channel Leakage Ratio (ACLR)

ACLR is the ratio in decibels relative to the carrier (dBc) between the measured power within a channel relative to its adjacent channel.

## **Complex Image Rejection**

In a traditional two-part upconversion, two images are created around the second IF frequency. These images have the effect of wasting transmitter power and system bandwidth. By placing the real part of a second complex modulator in series with the first complex modulator, either the upper or lower frequency image near the second IF can be rejected.

### Adjusted DAC Update Rate

The adjusted DAC update rate is defined as the DAC update rate divided by the smallest interpolating factor. For clarity on DACs with multiple interpolating factors, the adjusted DAC update rate for each interpolating factor may be given.

## **Physical Lane**

Physical Lane x refers to SERDINx±.

### **Logical Lane**

Logical Lane x refers to physical lanes after optionally being remapped by the crossbar block (Register 0x308 and Register 0x309).

## TYPICAL PERFORMANCE CHARACTERISTICS

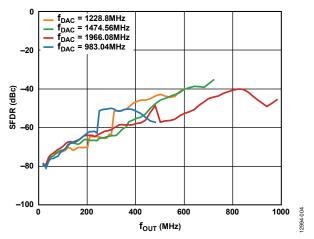

Figure 4. Single Tone (0 dBFS) SFDR vs.  $f_{OUT}$  in the First Nyquist Zone over  $f_{DAC}$

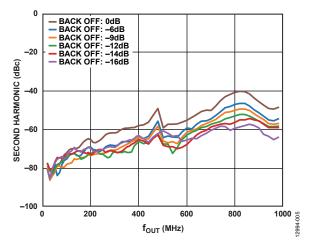

Figure 5. Single Tone Second Harmonic vs.  $f_{OUT}$  in the First Nyquist Zone over Digital Back Off,  $f_{DAC}$  = 1966.08 MHz

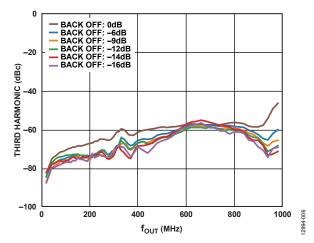

Figure 6. Single Tone Third Harmonic vs.  $f_{OUT}$  in the First Nyquist Zone over Digital Back Off,  $f_{DAC} = 1966.08 \, \text{MHz}$

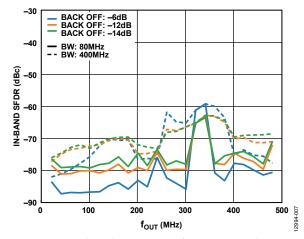

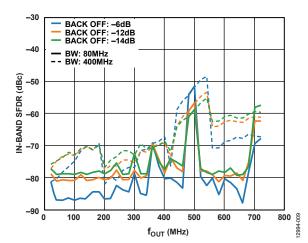

Figure 7. In-Band, Single Tone SFDR vs.  $f_{OUT}$  in 80 MHz and 400 MHz Bandwidths,  $f_{DAC}$  = 983.04 MHz

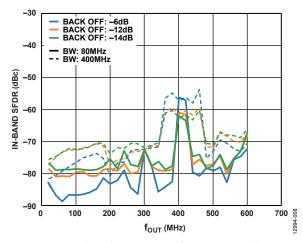

Figure 8. In-Band, Single Tone SFDR vs.  $f_{OUT}$  in 80 MHz and 400 MHz Bandwidths,  $f_{DAC}$  = 1228.8 MHz

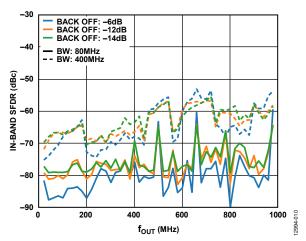

Figure 9. In-Band, Single Tone SFDR vs.  $f_{OUT}$  in 80 MHz and 400 MHz Bandwidths,  $f_{DAC} = 1474.56$  MHz

Figure 10. In-Band, Single Tone SFDR vs.  $f_{OUT}$  in 80 MHz and 400 MHz Bandwidths,  $f_{DAC} = 1966.08$  MHz

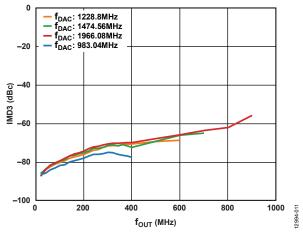

Figure 11. Two-Tone, Third-Order IMD (IMD3) vs. f<sub>OUT</sub> over f<sub>DAC</sub>

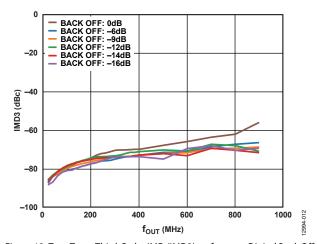

Figure 12. Two-Tone, Third-Order IMD (IMD3) vs.  $f_{OUT}$  over Digital Back Off,  $f_{DAC} = 1966.08$  MHz

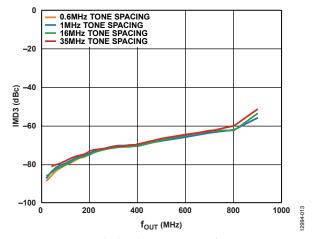

Figure 13. Two-Tone, Third-Order IMD (IMD3) vs.  $f_{OUT}$  over Tone Spacing,  $f_{DAC} = 1966.08 \, \mathrm{MHz}$

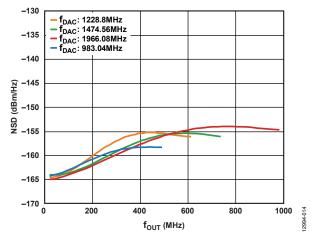

Figure 14. Single Tone (0 dBFS) NSD vs. fout over fDAC

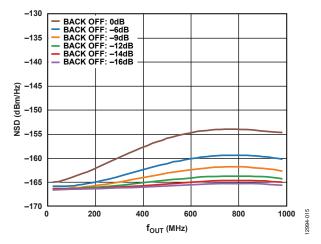

Figure 15. Single Tone NSD vs.  $f_{OUT}$  over Digital Back Off,  $f_{DAC} = 1966.08$  MHz

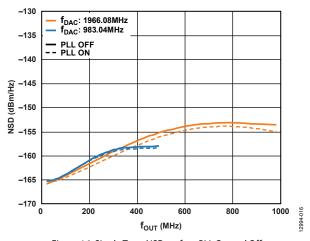

Figure 16. Single Tone NSD vs.  $f_{\text{OUT}}$ , PLL On and Off

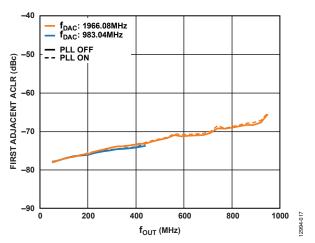

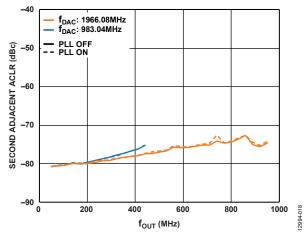

Figure 17. One-Carrier (1C) 5 MHz Bandwidth LTE, First Adjacent ACLR vs.  $f_{\rm OUT}$ , PLL On and Off

Figure 18. 1C 5 MHz Bandwidth LTE, Second Adjacent ACLR vs.  $f_{\rm OUT}$ , PLL On and Off

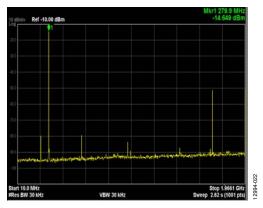

Figure 19. Two-Tone, Third-Order IMD Performance, IF = 180 MHz,  $f_{DAC}$  = 1966.08 MHz

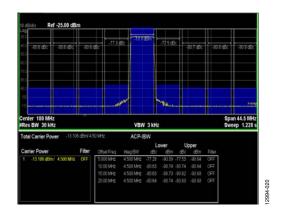

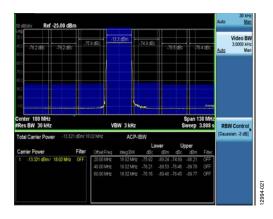

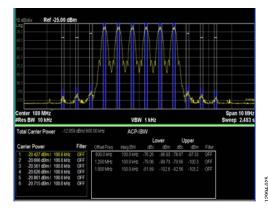

Figure 20. 1C 5 MHz Bandwidth LTE ACLR Performance, IF = 180 MHz,  $f_{\rm DAC} = 1966.08\,{\rm MHz}$

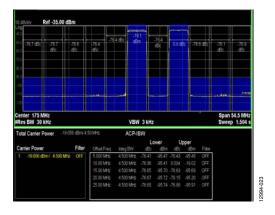

Figure 21. 1C 20 MHz Bandwidth LTE ACLR Performance, IF = 180 MHz,  $f_{\rm DAC}$  = 1966.08 MHz

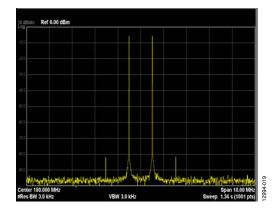

Figure 22. Single Tone,  $f_{DAC} = 1966.08 \text{ MHz}$ ,  $f_{OUT} = 280 \text{ MHz}$ , -14 dBFS

Figure 23. Two-Carrier (2C)  $2 \times 5$  MHz Bandwidth with 5 MHz Gap LTE ACLR Performance, IF = 180 MHz,  $f_{DAC} = 1966.08$  MHz

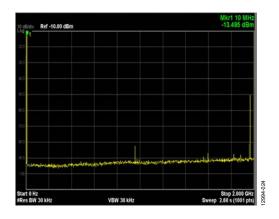

Figure 24. Single Tone SFDR,  $f_{DAC}$  =1966.08 MHz, 4× Interpolation,  $f_{OUT}$  = 10 MHz, -14 dBFS

Figure 25. Six-Carrier (6C) Spaced by 600 kHz GSM Edge ACP Performance, IF = 180 MHz,  $f_{DAC} = 1966.08$  MHz

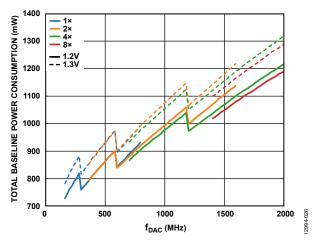

Figure 26. Total Baseline Power Consumption vs.  $f_{DAC}$  over Interpolation

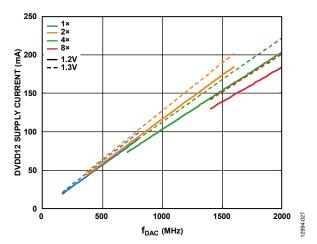

Figure 27. DVDD12 Supply Current vs.  $f_{DAC}$  over Interpolation

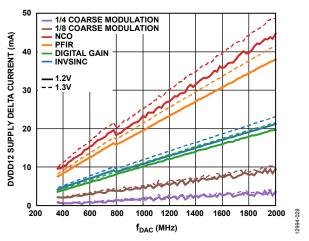

Figure 28. DVDD12 Supply Delta Current vs. f<sub>DAC</sub> over Digital Functions

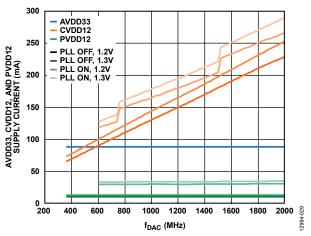

Figure 29. AVDD33, CVDD12, PVDD12 Supply Current vs. f<sub>DAC</sub>

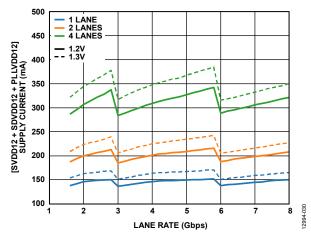

Figure 30. Total SERDES Supply Current (SVDD12, SDVDD12, PLLVDD12) vs. Lane Rate; One, Two, and Four Lanes

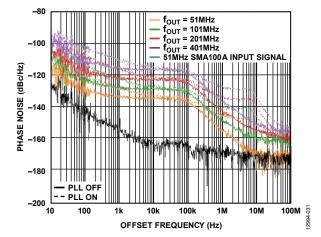

Figure 31. Single Tone Phase Noise vs. Offset Frequency at Four  $f_{OUT}$  Values and with an SMA100A Signal Generator,  $f_{DAC} = 1.96608$  GHz, PLL On and Off

## THEORY OF OPERATION

The AD9152 is a 16-bit, dual DAC with a SERDES interface. Figure 2 shows a detailed functional block diagram of the AD9152. Four high speed serial lanes carry data at a maximum speed of 12.38 Gbps, and a 1.238 GSPS input data rate to the DACs. Compared to either LVDS or CMOS interfaces, the SERDES interface simplifies pin count, board layout, and input clock requirements to the device.

The clock for the input data is derived from the device clock (required by the JESD204B specification). This device clock can be sourced with a PLL reference clock used by the on-chip PLL to generate a DAC clock, a high fidelity direct external DAC sampling clock, or a 2× DAC frequency RF clock. The device can be configured to operate in one-, two-, or four-lane modes, depending on the required input data rate.

The digital datapath of the AD9152 offers four interpolation modes  $(1\times, 2\times, 4\times, \text{ and } 8\times)$  through three half-band filters with a maximum DAC sample rate of 2.25 GSPS. An inverse sinc filter compensates for sinc related roll-off. The PFIR filter compensates the gain over frequency in a more flexible way.

The AD9152 DAC cores provide a fully differential current output with a nominal full-scale current of 20 mA. The full-scale

current, I<sub>OUTES</sub>, is user adjustable to between 4.04 mA and 20.22 mA, typically. The differential current outputs are complementary and are optimized for easy integration with the Analog Devices ADRF6720 AQM. The AD9152 is capable of multichip synchronization that can both synchronize multiple DACs and establish a constant and deterministic latency (latency locking) path for the DACs. The latency for each of the DACs remains constant from link establishment to link establishment. An external alignment (SYSREF±) signal makes the AD9152 Subclass 1 compliant. Several modes of SYSREF± signal handling are available for use in the system.

An SPI configures the various functional blocks and monitors their statuses. The various functional blocks and the data interface must be set up in a specific sequence for proper operation (see the Device Setup Guide section). Simple SPI initialization routines set up the JESD204B link and are included in the evaluation board package. The following sections describe the various blocks of the AD9152 in greater detail. Descriptions of the JESD204B interface, control parameters, and various registers to set up and monitor the device are provided. The recommended start-up routine reliably sets up the data link.

## SERIAL PORT OPERATION

The serial port is a flexible, synchronous serial communications port that allows easy interfacing with many industry-standard microcontrollers and microprocessors. The serial input/output is compatible with most synchronous transfer formats, including both the Motorola SPI and Intel® SSR protocols. The interface allows read/write access to all registers that configure the AD9152. MSB first or LSB first transfer formats are supported. The serial port interface is a 4-wire or a 3-wire (by default) interface in which the input and output share a single-pin input/output (SDIO).

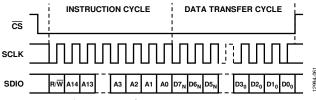

Figure 32. Serial Port Interface Pins

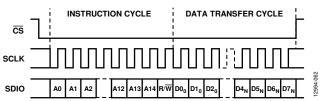

There are two phases to a communication cycle with the AD9152. Phase 1 is the instruction cycle (the writing of an instruction byte into the device), coincident with the first 16 SCLK rising edges. The instruction word provides the serial port controller with information regarding the data transfer cycle, Phase 2 of the communication cycle. The Phase 1 instruction word defines whether the upcoming data transfer is a read or write, along with the starting register address for the following data transfer.

A logic high on the  $\overline{CS}$  pin followed by a logic low resets the serial port timing to the initial state of the instruction cycle. From this state, the next 16 rising SCLK edges represent the instruction bits of the current input/output operation.

The remaining SCLK edges are for Phase 2 of the communication cycle. Phase 2 is the actual data transfer between the device and the system controller. Phase 2 of the communication cycle is a transfer of one or more data bytes. Eight  $\times$  N SCLK cycles are needed to transfer N bytes during the transfer cycle. Registers change immediately upon writing to the last bit of each transfer byte, except for the frequency tuning word (FTW) and the numerically controlled oscillator (NCO) phase offsets, which change only when the frequency tuning word (FTW) FTW\_UPDATE\_REQ bit (Register 0x113, Bit 0) is set.

## **DATA FORMAT**

The instruction byte contains the information shown in Table 13.

**Table 13. Serial Port Instruction Word**

| I15 (MSB) | I[14:0] |

|-----------|---------|

| R/W       | A[14:0] |

$R/\overline{W}$ , Bit 15 of the instruction word, determines whether a read or a write data transfer occurs after the instruction word write. Logic 1 indicates a read operation, and Logic 0 indicates a write operation.

A14 to A0, Bit 14 to Bit 0 of the instruction word, determine the register that is accessed during the data transfer portion of the communication cycle. For multibyte transfers, [A14:0] is the starting address. The remaining register addresses are generated by the device based on the address increment bits (Register 0x000, Bit 5 and Bit 2). If the address increment bits are set high, multibyte SPI writes start on A[14:0] and increment by 1 every 8 bits sent/received. If the address increment bits are set to 0, the address decrements by 1 every 8 bits.

# SERIAL PORT PIN DESCRIPTIONS Serial Clock (SCLK)