Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# Dual, 16-Bit, 6.2 GSPS RF DAC with Single Channelizer

Data Sheet AD9171

#### **FEATURES**

Supports single-band wireless applications

1 complex data input channel per RF DAC

516 MSPS maximum complex input data rate per input channel

1 independent NCO per input channel

Proprietary, low spurious and distortion design

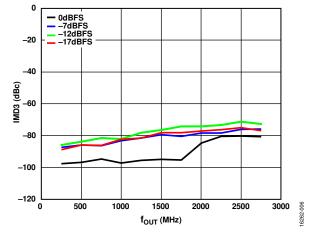

2-tone IMD = -83 dBc at 1.8 GHz, -7 dBFS/tone RF output

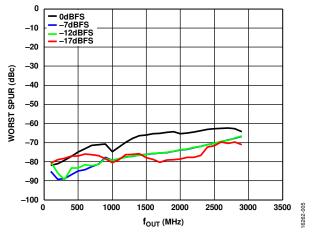

SFDR < -80 dBc at 1.8 GHz, -7 dBFS RF output

Flexible 8-lane, 15.4 Gbps JESD204B interface

Supports single-band use cases

Supports 12-bit high density mode for increased data throughput

Multiple chip synchronization

**Supports JESD204B Subclass 1**

Selectable interpolation filter for a complete set of input data rates

$2\times$ ,  $3\times$ ,  $4\times$ , and  $6\times$  configurable data channel interpolation  $6\times$  and  $8\times$  configurable final interpolation

Final 48-bit NCO that operates at the DAC rate to support frequency synthesis up to 3.1 GHz

Transmit enable function allows extra power saving and downstream circuitry protection

High performance, low noise PLL clock multiplier

Supports 6.2 GSPS DAC update rate

Observation ADC clock driver with selectable divide ratios

1.45 W at 6 GSPS, single-channel mode

10 mm × 10 mm, 144-ball BGA\_ED with metal enhanced thermal lid, 0.80 mm pitch

#### **APPLICATIONS**

Wireless communications infrastructure

Single-band base station radios

Instrumentation, automatic test equipment (ATE)

#### **GENERAL DESCRIPTION**

The AD9171 is a high performance, dual, 16-bit digital-to-analog converter (DAC) that supports DAC sample rates to 6.2 GSPS. The device features an 8-lane, 15.4 Gbps JESD204B data input port, a high performance, on-chip DAC clock multiplier, and digital signal processing capabilities targeted at single-band direct to radio frequency (RF) wireless applications.

The AD9171 features one complex data input channels per RF DAC. Each data input channel includes a configurable gain stage, an interpolation filter, and a channel numerically controlled oscillator (NCO) for flexible, frequency planning. The device supports up to a 516 MSPS complex data rate per input channel.

The AD9171 is available in a 144-ball BGA\_ED package.

#### **PRODUCT HIGHLIGHTS**

- Supports one complex data input channel per RF DAC at a maximum complex input data rate of 513 MSPS with 12-bit resolution and 516 MSPS with 16-bit resolution options. There is one independent NCO per input channel.

- Low power dual converter decreases the amount of power consumption needed in high bandwidth and multichannel applications.

## **TABLE OF CONTENTS**

| Features                                               | ]  |

|--------------------------------------------------------|----|

| Applications                                           | 1  |

| General Description                                    | 1  |

| Product Highlights                                     | 1  |

| Revision History                                       | 2  |

| Functional Block Diagram                               | 3  |

| Specifications                                         | 4  |

| DC Specifications                                      | 4  |

| Digital Specifications                                 | 5  |

| Power Supply DC Specifications                         | 5  |

| Serial Port and CMOS Pin Specifications                | 6  |

| Digital Input Data Timing Specifications               | 7  |

| JESD204B Interface Electrical and Speed Specifications | 8  |

| Input Data Rates and Signal Bandwidth Specifications   | 8  |

| AC Specifications                                      | 9  |

| Absolute Maximum Ratings1                              | 1  |

| Reflow Profile1                                        | 1  |

| Thermal Characteristics 1                              | 1  |

| ESD Caution                                            | 1  |

| Pin Configuration and Function Descriptions1           | 2  |

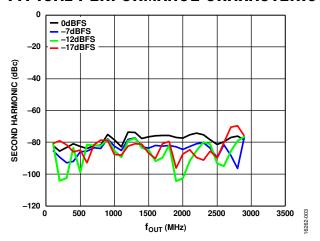

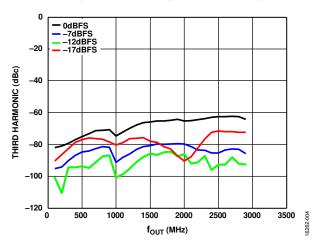

| Typical Performance Characteristics 1                  | 5  |

| Terminology 1                                          | 8  |

| Theory of Operation1                                   | 9  |

| Serial Port Operation2                                 | 20 |

| Data Format2                                           | 20 |

| Serial Port Pin Descriptions2                          | 20 |

| Serial Port Options2                                   | 20 |

| JESD204B Serial Data Interface  |

|---------------------------------|

| JESD204B Overview               |

| Physical Layer                  |

| Data Link Layer26               |

| Syncing LMFC Signals            |

| Transport Layer                 |

| JESD204B Test Modes             |

| JESD204B Error Monitoring       |

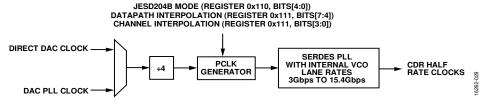

| Digital Datapath                |

| Total Datapath Interpolation    |

| Channel Digital Datapath41      |

| Main Digital Datapath44         |

| Interrupt Request Operation     |

| Interrupt Service Routine       |

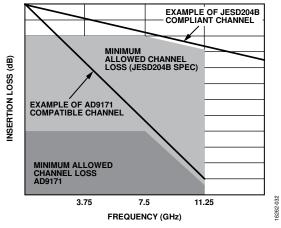

| Applications Information        |

| Hardware Considerations51       |

| Analog Interface Considerations |

| DAC Input Clock Configurations  |

| Clock Output Driver56           |

| Analog Outputs56                |

| Start-Up Sequence               |

| Register Summary                |

| Register Details                |

| Outline Dimensions              |

| Ordering Guide                  |

#### **REVISION HISTORY**

1/2018—Revision 0: Initial Version

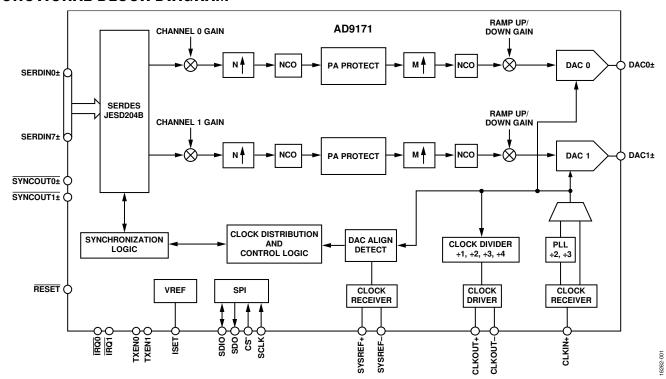

## **FUNCTIONAL BLOCK DIAGRAM**

Figure 1. Functional Block Diagram

## **SPECIFICATIONS**

#### **DC SPECIFICATIONS**

AVDD1.0 = 1.0 V, AVDD1.8 = 1.8 V, DVDD1.0 = 1.0 V, DVDD1.8 = 1.8 V, SVDD1.0 = 1.0 V, and DAC output full-scale current ( $I_{OUTFS}$ ) = 20 mA, unless otherwise noted. For the minimum and maximum values,  $T_J = -40$ °C to +118°C. For the typical values,  $T_A = 25$ °C, which corresponds to  $T_J = 51$ °C.

Table 1.

| Parameter                                   | <b>Test Conditions/Comments</b>              | Min   | Тур   | Max  | Unit   |

|---------------------------------------------|----------------------------------------------|-------|-------|------|--------|

| RESOLUTION                                  |                                              | 16    |       |      | Bit    |

| ACCURACY                                    |                                              |       |       |      |        |

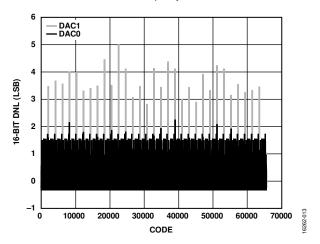

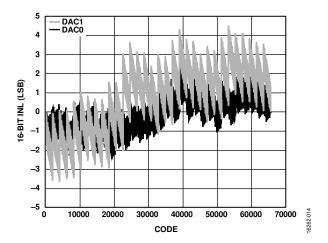

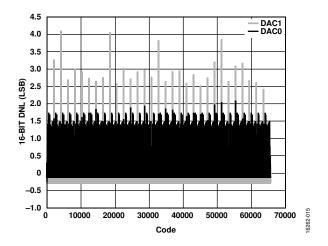

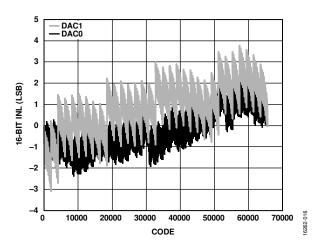

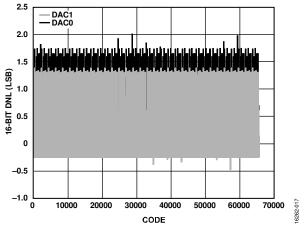

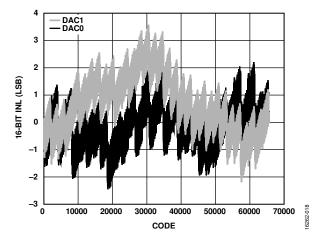

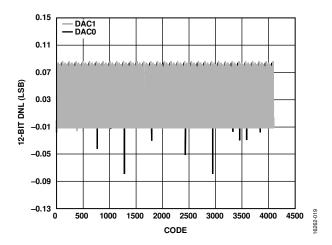

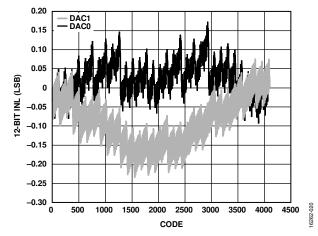

| Integral Nonlinearity (INL)                 |                                              |       | ±7    |      | LSB    |

| Differential Nonlinearity (DNL)             |                                              |       | ±7    |      | LSB    |

| ANALOG OUTPUTS (DAC0+, DAC0-, DAC1+, DAC1-) |                                              |       |       |      |        |

| Gain Error (with Internal ISET Reference)   |                                              |       | ±15   |      | %      |

| Full-Scale Output Current                   |                                              |       |       |      |        |

| Minimum                                     | $R_{SET} = 5 k\Omega$                        | 14.2  | 16    | 17.8 | mA     |

| Maximum                                     | $R_{SET} = 5 k\Omega$                        | 23.6  | 26    | 28.8 | mA     |

| Common-Mode Voltage                         |                                              |       | 0     |      | V      |

| Differential Impedance                      |                                              |       | 100   |      | Ω      |

| DAC DEVICE CLOCK INPUT (CLKIN+, CLKIN-)     |                                              |       |       |      |        |

| Differential Input Power                    | $R_{LOAD} = 100 \Omega$ differential on-chip |       |       |      |        |

| Minimum                                     |                                              |       | 0     |      | dBm    |

| Maximum                                     |                                              |       | 6     |      | dBm    |

| Differential Input Impedance <sup>1</sup>   |                                              |       | 100   |      | Ω      |

| Common-Mode Voltage                         | AC-coupled                                   |       | 0.5   |      | V      |

| CLOCK OUTPUT DRIVER (CLKOUT+, CLKOUT-)      |                                              |       |       |      |        |

| Differential Output Power                   |                                              |       |       |      |        |

| Minimum                                     |                                              |       | -9    |      | dBm    |

| Maximum                                     |                                              |       | 0     |      | dBm    |

| Differential Output Impedance               |                                              |       | 100   |      | Ω      |

| Common-Mode Voltage                         | AC-coupled                                   |       | 0.5   |      | V      |

| Output Frequency                            |                                              | 727.5 |       | 3000 | MHz    |

| TEMPERATURE DRIFT                           |                                              |       |       |      |        |

| Gain                                        |                                              |       | 10    |      | ppm/°C |

| REFERENCE                                   |                                              |       |       |      |        |

| Internal Reference Voltage                  |                                              |       | 0.495 |      | V      |

| ANALOG SUPPLY VOLTAGES                      |                                              |       |       |      |        |

| AVDD1.0                                     |                                              | 0.95  | 1.0   | 1.05 | V      |

| AVDD1.8                                     |                                              | 1.71  | 1.8   | 1.89 | V      |

| DIGITAL SUPPLY VOLTAGES                     |                                              |       |       |      |        |

| DVDD1.0                                     |                                              | 0.95  | 1.0   | 1.05 | V      |

| DAVDD1.0                                    |                                              | 0.95  | 1.0   | 1.05 | V      |

| DVDD1.8                                     |                                              | 1.71  | 1.8   | 1.89 | V      |

| SERDES SUPPLY VOLTAGES                      |                                              |       |       |      |        |

| SVDD1.0                                     |                                              | 0.95  | 1.0   | 1.05 | V      |

<sup>&</sup>lt;sup>1</sup> See the DAC Input Clock Configurations section for more details.

#### **DIGITAL SPECIFICATIONS**

AVDD1.0 = 1.0 V, AVDD1.8 = 1.8 V, DVDD1.0 = 1.0 V, DVDD1.8 = 1.8 V, SVDD1.0 = 1.0 V, and DAC  $I_{OUTFS}$  = 20 mA, unless otherwise noted. For the minimum and maximum values,  $T_J = -40^{\circ}$ C to +118°C. For the typical values,  $T_A = +25^{\circ}$ C, which corresponds to  $T_J = 51^{\circ}$ C.

Table 2.

| Parameter                                                                        | Test Conditions/Comments     | Min  | Тур | Max  | Unit |

|----------------------------------------------------------------------------------|------------------------------|------|-----|------|------|

| DAC UPDATE RATE                                                                  |                              |      |     |      |      |

| Minimum                                                                          |                              |      |     | 2.91 | GSPS |

| Maximum <sup>1</sup>                                                             |                              | 6.2  |     |      | GSPS |

| Adjusted <sup>2</sup>                                                            |                              | 516  |     |      | MSPS |

| DAC PHASE-LOCKED LOOP (PLL) VOLTAGE CONTROLLED OSCILLATOR (VCO) FREQUENCY RANGES |                              |      |     |      |      |

| VCO Output Divide by 2                                                           |                              | 4.37 |     | 6.2  | GSPS |

| VCO Output Divide by 3                                                           |                              | 2.91 |     | 4.14 | GSPS |

| PHASE FREQUENCY DETECT INPUT FREQUENCY RANGES                                    |                              |      |     |      |      |

| 9.96 GHz ≤ VCO Frequency ≤ 10.87 GHz                                             |                              | 25   |     | 225  | MHz  |

| VCO Frequency < 9.96 GHz or VCO Frequency > 10.87 GHz                            |                              | 25   |     | 770  | MHz  |

| DAC DEVICE CLOCK INPUT (CLKIN+, CLKIN-) FREQUENCY RANGES                         |                              |      |     |      |      |

| PLL Off                                                                          |                              | 2.91 |     | 6.2  | GHz  |

| PLL On                                                                           | M divider set to divide by 1 | 25   |     | 770  | MHz  |

|                                                                                  | M divider set to divide by 2 | 50   |     | 1540 | MHz  |

|                                                                                  | M divider set to divide by 3 | 75   |     | 2310 | MHz  |

|                                                                                  | M divider set to divide by 4 | 100  |     | 3080 | MHz  |

<sup>&</sup>lt;sup>1</sup> The maximum DAC update rate varies depending on the selected JESD204B mode and the lane rate for the given configuration used. The maximum DAC rate according to lane rate and voltage supply levels is listed in Table 3.

#### **POWER SUPPLY DC SPECIFICATIONS**

AVDD1.0 = 1.0 V, AVDD1.8 = 1.8 V, DVDD1.0 = 1.0 V, DVDD1.8 = 1.8 V, SVDD1.0 = 1.0 V, and DAC  $I_{OUTFS}$  = 20 mA, unless otherwise noted. For the minimum and maximum values,  $T_{J}$  = -40°C to +118°C. For the typical values,  $T_{A}$  = 25°C, which corresponds to  $T_{J}$  = 51°C.

Table 3.

| Parameter                                                 | Test Conditions/Comments                                                                                                                                                             | Min | Тур  | Max  | Unit |

|-----------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|------|------|

| DUAL-LINK MODE, Mode 0 (L = 1,<br>M = 2, NP = 16, N = 16) | 5.89824 GSPS DAC rate, 184.32 MHz PLL reference clock, 16× total interpolation (2×, 8×), 40 MHz tone at –3 dBFS, channel NCO disabled, main NCO = 1.8425 GHz, SYNCOUTx± in LVDS mode |     |      |      |      |

| AVDD1.0                                                   | All supply levels set to nominal values                                                                                                                                              |     | 400  | 670  | mA   |

|                                                           | All supplies at 5% tolerance                                                                                                                                                         |     | 425  | 745  | mA   |

| AVDD1.8                                                   |                                                                                                                                                                                      |     | 110  | 130  | mA   |

| DVDD1.0                                                   | Combined current consumption with the DAVDD1.0 supply                                                                                                                                |     |      |      |      |

|                                                           | All supply levels set to nominal values                                                                                                                                              |     | 625  | 960  | mA   |

|                                                           | All supplies at 5% tolerance                                                                                                                                                         |     | 670  | 1070 | mA   |

| DVDD1.8                                                   |                                                                                                                                                                                      |     | 35   | 50   | mA   |

| SVDD1.0                                                   |                                                                                                                                                                                      |     | 175  | 340  | mA   |

| <b>Total Power Dissipation</b>                            |                                                                                                                                                                                      |     | 1.45 | 2.15 | W    |

<sup>&</sup>lt;sup>2</sup> The adjusted DAC update rate is calculated as f<sub>DAC</sub>, divided by the minimum required interpolation factor for a given mode or the maximum channel data rate for a given mode. Different modes have different maximum DAC update rates, minimum interpolation factors, and maximum channel data rates, as shown in Table 13.

| Parameter                                                          | Test Conditions/Comments                                                                                                                                               | Min | Тур | Max   | Unit |

|--------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-------|------|

| DUAL-LINK, MODE 3 (NCO ONLY,<br>SINGLE-CHANNEL MODE,<br>NO SERDES) | 6 GSPS DAC rate, 300 MHz PLL reference clock, 8× total interpolation (1×, 8×), no input tone (dc internal level = 0x50FF), channel NCO = 40 MHz, main NCO = 1.8425 GHz |     |     |       |      |

| AVDD1.0                                                            |                                                                                                                                                                        |     |     |       |      |

|                                                                    | All supply levels set to nominal values                                                                                                                                |     | 410 | 660   | mA   |

|                                                                    | All supplies at 5% tolerance                                                                                                                                           |     | 435 | 750   | mA   |

| AVDD1.8                                                            |                                                                                                                                                                        |     | 110 | 130   | mA   |

| DVDD1.0                                                            | Combined current consumption with the DAVDD1.0 supply                                                                                                                  |     |     |       |      |

|                                                                    | All supply levels set to nominal values                                                                                                                                |     | 500 | 780   | mA   |

|                                                                    | All supplies at 5% tolerance                                                                                                                                           |     | 515 | 950   | mA   |

| DVDD1.8                                                            |                                                                                                                                                                        |     | 0.3 | 1     | mA   |

| SVDD1.0                                                            | All supply levels set to nominal values                                                                                                                                |     | 5   | 100   | mA   |

|                                                                    | All supplies at 5% tolerance                                                                                                                                           |     | 3   | 120   | mA   |

| <b>Total Power Dissipation</b>                                     |                                                                                                                                                                        |     | 1.1 | 1.671 | W    |

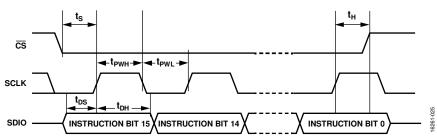

#### **SERIAL PORT AND CMOS PIN SPECIFICATIONS**

AVDD1.0 = 1.0 V, AVDD1.8 = 1.8 V, DVDD1.0 = 1.0 V, DVDD1.8 = 1.8 V, SVDD1.0 = 1.0 V, and  $DAC\ I_{OUTES} = 20\ mA$ , unless otherwise noted. For the minimum and maximum values,  $T_J = -40^{\circ}\text{C}$  to  $+118^{\circ}\text{C}$ . For the typical values,  $T_A = 25^{\circ}\text{C}$ , which corresponds to  $T_J = 51^{\circ}\text{C}$ .

Table 4.

| Parameter                                        | Symbol                                  | Test Comments/Conditions            | Min   | Тур | Max   | Unit |

|--------------------------------------------------|-----------------------------------------|-------------------------------------|-------|-----|-------|------|

| WRITE OPERATION                                  |                                         | See Figure 48                       |       |     |       |      |

| Maximum SCLK Clock Rate                          | f <sub>SCLK</sub> , 1/t <sub>SCLK</sub> |                                     | 80    |     |       | MHz  |

| SCLK Clock High                                  | t <sub>PWH</sub>                        | SCLK = 20 MHz                       | 5.03  |     |       | ns   |

| SCLK Clock Low                                   | t <sub>PWL</sub>                        | SCLK = 20 MHz                       | 1.6   |     |       | ns   |

| SDIO to SCLK Setup Time                          | t <sub>DS</sub>                         |                                     | 1.154 |     |       | ns   |

| SCLK to SDIO Hold Time                           | t <sub>DH</sub>                         |                                     | 0.577 |     |       | ns   |

| CS to SCLK Setup Time                            | ts                                      |                                     | 1.036 |     |       | ns   |

| SCLK to CS Hold Time                             | t <sub>H</sub>                          |                                     | -5.3  |     |       | ps   |

| READ OPERATION                                   |                                         | See Figure 47                       |       |     |       |      |

| SCLK Clock Rate                                  | f <sub>SCLK</sub> , 1/t <sub>SCLK</sub> |                                     |       |     | 48.58 | MHz  |

| SCLK Clock High                                  | t <sub>PWH</sub>                        |                                     | 5.03  |     |       | ns   |

| SCLK Clock Low                                   | t <sub>PWL</sub>                        |                                     | 1.6   |     |       | ns   |

| SDIO to SCLK Setup Time                          | t <sub>DS</sub>                         |                                     | 1.158 |     |       | ns   |

| SCLK to SDIO Hold Time                           | t <sub>DH</sub>                         |                                     | 0.537 |     |       | ns   |

| CS to SCLK Setup Time                            | ts                                      |                                     | 1.036 |     |       | ns   |

| SCLK to SDIO Data Valid Time                     | t <sub>DV</sub>                         |                                     | 9.6   |     |       | ns   |

| SCLK to SDO Data Valid Time                      | t <sub>DV</sub>                         |                                     | 13.7  |     |       | ns   |

| CS to SDIO Output Valid to High-Z                |                                         | Not shown in Figure 47 or Figure 48 | 5.4   |     |       | ns   |

| CS to SDO Output Valid to High-Z                 |                                         | Not shown in Figure 47 or Figure 48 | 9.59  |     |       | ns   |

| INPUTS (SDIO, SCLK, CS, RESET, TXENO, and TXEN1) |                                         |                                     |       |     |       |      |

| Voltage Input                                    |                                         |                                     |       |     |       |      |

| High                                             | V <sub>IH</sub>                         |                                     | 1.48  |     |       | ٧    |

| Low                                              | V <sub>IL</sub>                         |                                     |       |     | 0.425 | ٧    |

| Current Input                                    |                                         |                                     |       |     |       |      |

| High                                             | Іін                                     |                                     |       |     | ±100  | nA   |

| Low                                              | I <sub>IL</sub>                         |                                     | ±100  |     |       | nA   |

| Parameter                      | Symbol          | Test Comments/Conditions | Min  | Тур | Max   | Unit |

|--------------------------------|-----------------|--------------------------|------|-----|-------|------|

| OUTPUTS (SDIO, SDO)            |                 |                          |      |     |       |      |

| Voltage Output                 |                 |                          |      |     |       |      |

| High                           | V <sub>OH</sub> |                          |      |     |       |      |

| 0 mA load                      |                 |                          | 1.69 |     |       | V    |

| 4 mA load                      |                 |                          | 1.52 |     |       | V    |

| Low                            | V <sub>OL</sub> |                          |      |     |       |      |

| 0 mA load                      |                 |                          |      |     | 0.045 | V    |

| 4 mA load                      |                 |                          |      |     | 0.175 | V    |

| Current Output                 |                 |                          |      |     |       |      |

| High                           | Іон             |                          |      | 4   |       | mA   |

| Low                            | loL             |                          |      | 4   |       | mA   |

| INTERRUPT OUTPUTS (IRQ0, IRQ1) |                 |                          |      |     |       |      |

| Voltage Output                 |                 |                          |      |     |       |      |

| High                           | V <sub>OH</sub> |                          | 1.71 |     |       | V    |

| Low                            | V <sub>OL</sub> |                          |      |     | 0.075 | V    |

#### **DIGITAL INPUT DATA TIMING SPECIFICATIONS**

AVDD1.0 = 1.0 V, AVDD1.8 = 1.8 V, DVDD1.0 = 1.0 V, DVDD1.8 = 1.8 V, SVDD1.0 = 1.0 V, and DAC I<sub>OUTES</sub> = 20 mA, unless otherwise noted. For the minimum and maximum values,  $T_J = -40$ °C to +118°C. For the typical values,  $T_A = 25$ °C, which corresponds to  $T_J = 51$ °C.

Table 5

| Parameter                                                           | Test Conditions/Comments                                                               | Min | Тур  | Max | Unit              |

|---------------------------------------------------------------------|----------------------------------------------------------------------------------------|-----|------|-----|-------------------|

| LATENCY <sup>1</sup>                                                |                                                                                        |     |      |     |                   |

| Channel Interpolation Factor, Main Datapath<br>Interpolation Factor | LMFC_VAR_x = 12, LMFC_DELAY_x = 12, unless otherwise noted                             |     |      |     |                   |

| 2×, 6×                                                              | JESD204B Mode 3                                                                        |     | 1970 |     | DAC clock cycle   |

|                                                                     | JESD204B Mode 5                                                                        |     | 1770 |     | DAC clock cycle   |

| 2×, 8×                                                              | JESD204B Mode 0                                                                        |     | 2020 |     | DAC clock cycle   |

|                                                                     | JESD204B Mode 3                                                                        |     | 2500 |     | DAC clock cycle   |

| 3×, 6×                                                              | JESD204B Mode 3                                                                        |     | 2880 |     | DAC clock cycle   |

|                                                                     | JESD204B Mode 5                                                                        |     | 2630 |     | DAC clock cycle   |

| 3×, 8×                                                              | JESD204B Mode 3                                                                        |     | 3310 |     | DAC clock cycle   |

|                                                                     | JESD204B Mode 5                                                                        |     | 2980 |     | DAC clock cycle   |

| 4×, 6×                                                              | JESD204B Mode 0                                                                        |     | 2410 |     | DAC clock cycle   |

| 4×, 8×                                                              | JESD204B Mode 0                                                                        |     | 3090 |     | DAC clock cycle   |

| 6×, 6×                                                              | JESD204B Mode 0                                                                        |     | 3190 |     | DAC clock cycle   |

| 6×, 8×                                                              | JESD204B Mode 0                                                                        |     | 4130 |     | DAC clock cycle   |

| DETERMINISTIC LATENCY                                               |                                                                                        |     |      |     |                   |

| Fixed                                                               |                                                                                        |     |      | 13  | PCLK <sup>2</sup> |

| Variable                                                            |                                                                                        |     |      | 2   | PCLK cycles       |

| SYSREF± TO LOCAL MULTIFRAME CLOCK (LMFC) DELAY                      | Indicates the relationship between the<br>SYSREF± signal and the LMFC Clock<br>Phase 0 |     | 0    |     | DAC clock cycles  |

$<sup>^{1}</sup>$  Total latency (or pipeline delay) through the device is calculated as follows: total latency = interface latency + fixed latency + variable latency + pipeline delay.  $^{2}$  PCLK is the internal processing clock for the AD9171 and equals the lane rate  $\div$  40.

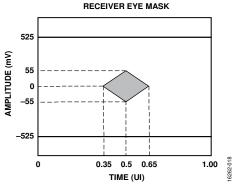

#### **JESD204B INTERFACE ELECTRICAL AND SPEED SPECIFICATIONS**

AVDD1.0 = 1.0 V, AVDD1.8 = 1.8 V, DVDD1.0 = 1.0 V, DVDD1.8 = 1.8 V, SVDD1.0 = 1.0 V, and DAC  $I_{OUTFS}$  = 20 mA, unless otherwise noted. For the minimum and maximum values,  $T_J = -40^{\circ}\text{C}$  to +118°C. For the typical values,  $T_A = 25^{\circ}\text{C}$ , which corresponds to  $T_J = 51^{\circ}\text{C}$ .

Table 6.

| Parameter                                         | Symbol              | Test Conditions/Comments                         | Min   | Тур  | Max   | Unit |

|---------------------------------------------------|---------------------|--------------------------------------------------|-------|------|-------|------|

| JESD204B SERIAL INTERFACE RATE (SERIAL LANE RATE) |                     |                                                  | 3     |      | 15.4  | Gbps |

| JESD204B DATA INPUTS                              |                     |                                                  |       |      |       |      |

| Input Leakage Current                             |                     | $T_A = 25$ °C                                    |       |      |       |      |

| Logic High                                        |                     | Input level = $1.0 \text{ V} \pm 0.25 \text{ V}$ |       | 10   |       | μΑ   |

| Logic Low                                         |                     | Input level = 0 V                                |       | -4   |       | μΑ   |

| Unit Interval                                     | UI                  |                                                  | 333   |      | 66.7  | ps   |

| Common-Mode Voltage                               | $V_{RCM}$           | AC-coupled                                       | -0.05 |      | +1.1  | V    |

| Differential Voltage                              | R_V <sub>DIFF</sub> |                                                  | 110   |      | 1050  | mV   |

| Differential Impedance                            | Z <sub>RDIFF</sub>  | At dc                                            | 80    | 100  | 120   | Ω    |

| SYSREF± INPUT                                     |                     |                                                  |       |      |       |      |

| Differential Impedance                            |                     |                                                  |       | 100  |       | Ω    |

| DIFFERENTIAL OUTPUTS (SYNCOUT0±, SYNCOUT1±)1      |                     | Driving 100 Ω differential load                  |       |      |       |      |

| Output Differential Voltage                       | V <sub>OD</sub>     |                                                  | 320   | 390  | 460   | mV   |

| Output Offset Voltage                             | Vos                 |                                                  | 1.08  | 1.12 | 1.15  | V    |

| SINGLE-ENDED OUTPUTS (SYNCOUT0±, SYNCOUT1±)       |                     | Driving 100 Ω differential load                  |       |      |       |      |

| Output Voltage                                    |                     |                                                  |       |      |       |      |

| High                                              | V <sub>OH</sub>     |                                                  | 1.69  |      |       | V    |

| Low                                               | V <sub>OL</sub>     |                                                  |       |      | 0.045 | V    |

| Current Output                                    |                     |                                                  |       |      |       |      |

| High                                              | Іон                 |                                                  |       | 0    |       | mA   |

| Low                                               | loL                 |                                                  |       | 0    |       | mA   |

<sup>&</sup>lt;sup>1</sup> IEEE Standard 1596.3 LVDS compatible.

#### INPUT DATA RATES AND SIGNAL BANDWIDTH SPECIFICATIONS

AVDD1.0 = 1.0 V, AVDD1.8 = 1.8 V, DVDD1.0 = 1.0 V, DVDD1.8 = 1.8 V, SVDD1.0 = 1.0 V, and DAC output full-scale current ( $I_{OUTFS}$ ) = 20 mA, unless otherwise noted. For the minimum and maximum values,  $T_J = -40$ °C to +118°C. For the typical values,  $T_A = 25$ °C, which corresponds to  $T_J = 51$ °C.

Table 7.

| Parameter <sup>1</sup>                          | Test Conditions/Comments                             | Min     | Тур Мах | Unit     |

|-------------------------------------------------|------------------------------------------------------|---------|---------|----------|

| INPUT DATA RATE PER INPUT<br>CHANNEL            | 1 complex channel enabled                            |         | 516     | MSPS     |

| COMPLEX SIGNAL BANDWIDTH PER INPUT CHANNEL      | 1 complex channel enabled (0.8 × f <sub>DATA</sub> ) |         | 413.    | 34 MHz   |

| MAXIMUM NCO CLOCK RATE                          |                                                      |         |         |          |

| Channel NCO                                     |                                                      | -258    | +25     | B MHz    |

| Main NCO                                        |                                                      |         | 6.2     | GHz      |

| MAXIMUM NCO SHIFT FREQUENCY RANGE               |                                                      |         |         |          |

| Channel NCO                                     |                                                      | -258.34 | +25     | 8.34 MHz |

| Main NCO                                        |                                                      | -3.1    | +3.1    | GHz      |

| MAXIMUM FREQUENCY SPACING ACROSS INPUT CHANNELS | Maximum NCO output frequency × 0.8                   |         | 412.    | 8 MHz    |

<sup>&</sup>lt;sup>1</sup> Values listed for these parameters are the maximum possible when considering all JESD204B modes of operation. Some modes are more limiting, based on other parameters.

#### **AC SPECIFICATIONS**

$AVDD1.0 = 1.0 \text{ V}, AVDD1.8 = 1.8 \text{ V}, DVDD1.0 = 1.0 \text{ V}, DVDD1.8 = 1.8 \text{ V}, SVDD1.0 = 1.0 \text{ V}, and DAC I_{OUTFS} = 20 \text{ mA}, unless otherwise noted.}$  For the minimum and maximum,  $T_J = -40^{\circ}\text{C}$  to  $+118^{\circ}\text{C}$ . For the typical values,  $T_A = 25^{\circ}\text{C}$ , which corresponds to  $T_J = 51^{\circ}\text{C}$ .

Table 8.

| Parameter                                                             | Test Conditions/Comments                                                                                                                                                      | Min | Тур         | Max | Unit       |

|-----------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------------|-----|------------|

| SPURIOUS-FREE DYNAMIC RANGE (SFDR)                                    |                                                                                                                                                                               |     |             |     |            |

| Single Tone, $f_{DAC} = 6000$ MSPS, Mode 0 (L = 1, M = 2)             | -7 dBFS, shuffle enabled                                                                                                                                                      |     |             |     |            |

| $f_{OUT} = 100 MHz$                                                   |                                                                                                                                                                               |     | -85         |     | dBc        |

| $f_{OUT} = 500 \text{ MHz}$                                           |                                                                                                                                                                               |     | -85         |     | dBc        |

| $f_{OUT} = 950 \text{ MHz}$                                           |                                                                                                                                                                               |     | -78         |     | dBc        |

| f <sub>OUT</sub> = 1840 MHz                                           |                                                                                                                                                                               |     | -75         |     | dBc        |

| $f_{OUT} = 2650 \text{ MHz}$                                          |                                                                                                                                                                               |     | -69         |     | dBc        |

| Single-Band Application—Band 3 (1805 MHz to 1880 MHz)                 | Mode 0, $2 \times$ to $8 \times$ , $f_{DAC} = 6000$ MSPS, 368.64 MHz reference clock                                                                                          |     |             |     |            |

| SFDR Harmonics                                                        | -7 dBFS, shuffle enabled                                                                                                                                                      |     |             |     |            |

| In-Band                                                               |                                                                                                                                                                               |     | -82         |     | dBc        |

| Digital Predistortion (DPD) Band                                      | DPD bandwidth = data rate $\times$ 0.8                                                                                                                                        |     | -80         |     | dBc        |

| Second Harmonic                                                       |                                                                                                                                                                               |     | -82         |     | dBc        |

| Third Harmonic                                                        |                                                                                                                                                                               |     | -80         |     | dBc        |

| Fourth and Fifth Harmonic                                             |                                                                                                                                                                               |     | -95         |     | dBc        |

| SFDR Nonharmonics                                                     | −7 dBFS, shuffle enabled                                                                                                                                                      |     |             |     |            |

| In-Band                                                               |                                                                                                                                                                               |     | -74         |     | dBc        |

| DPD Band                                                              |                                                                                                                                                                               |     | -74         |     | dBc        |

| ADJACENT CHANNEL LEAKAGE RATIO                                        |                                                                                                                                                                               |     |             |     |            |

| 4C-WCDMA                                                              | −1 dBFS digital backoff                                                                                                                                                       |     |             |     |            |

| $f_{DAC} = 6000 \text{ MSPS}, \text{ Mode 0 (L = 1, M = 2)}$          | $f_{OUT} = 1840 \text{ MHz}$                                                                                                                                                  |     | -71         |     | dBc        |

|                                                                       | $f_{OUT} = 2650 \text{ MHz}$                                                                                                                                                  |     | -66         |     | dBc        |

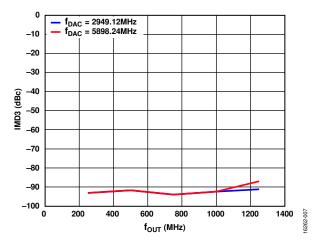

| THIRD-ORDER INTERMODULATION DISTORTION (IMD)                          | Two-tone test, –7 dBFS/tone, 1 MHz spacing                                                                                                                                    |     |             |     |            |

| $f_{DAC} = 6000 \text{ MSPS}, \text{ Mode } 0 \text{ (L} = 1, M = 2)$ | $f_{OUT} = 1840 \text{ MHz}$                                                                                                                                                  |     | -74         |     | dBc        |

|                                                                       | $f_{OUT} = 2650 \text{ MHz}$                                                                                                                                                  |     | -72         |     | dBc        |

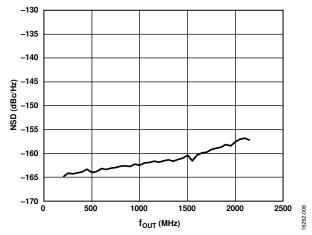

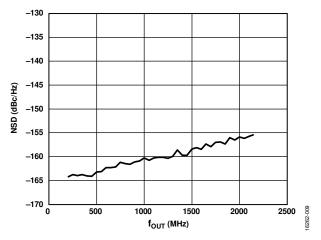

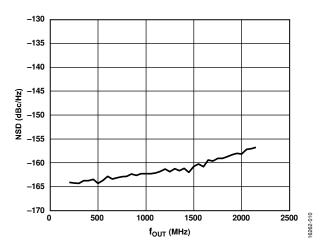

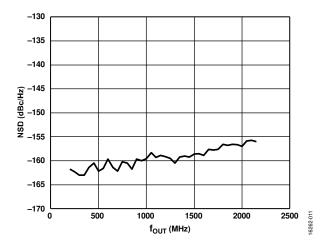

| NOISE SPECTRAL DENSITY (NSD)                                          | 0 dBFS, NSD measurement taken at 10% away from $f_{\text{OUT}}$ , shuffle off                                                                                                 |     |             |     |            |

| Single Tone, $f_{DAC} = 6000 \text{ MSPS}$ , Mode 3 (L = 2, M = 2)    |                                                                                                                                                                               |     |             |     |            |

| $f_{OUT} = 100 \text{ MHz}$                                           |                                                                                                                                                                               |     | -169        |     | dBm/Hz     |

| $f_{OUT} = 500 \text{ MHz}$                                           |                                                                                                                                                                               |     | -167        |     | dBm/Hz     |

| $f_{OUT} = 950 \text{ MHz}$                                           |                                                                                                                                                                               |     | -166        |     | dBm/Hz     |

| $f_{OUT} = 1840 \text{ MHz}$                                          |                                                                                                                                                                               |     | -163        |     | dBm/Hz     |

| f <sub>OUT</sub> = 2150 MHz                                           |                                                                                                                                                                               |     | -162        |     | dBm/Hz     |

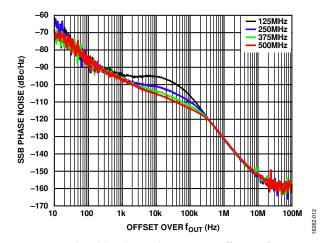

| SINGLE-SIDEBAND PHASE NOISE OFFSET                                    | Loop filter component values according to Figure 89 are as follows: $C1 = 22 \text{ nF}$ , $R1 = 232 \Omega$ , $C2 = 2.4 \text{ nF}$ , $C3 = 33 \text{ nF}$ ; PFD frequency = |     |             |     |            |

| 1 1.11-                                                               | 500 MHz, $f_{OUT} = 1.8 \text{ GHz}$ , $f_{DAC} = 6 \text{ GHz}$                                                                                                              |     | 07          |     | 4D = // 1- |

| 1 kHz                                                                 |                                                                                                                                                                               |     | -97         |     | dBc/Hz     |

| 10 kHz                                                                |                                                                                                                                                                               |     | -105        |     | dBc/Hz     |

| 100 kHz                                                               |                                                                                                                                                                               |     | -114<br>126 |     | dBc/Hz     |

| 600 kHz                                                               |                                                                                                                                                                               |     | -126        |     | dBc/Hz     |

| 1.2 MHz                                                               |                                                                                                                                                                               |     | -133        |     | dBc/Hz     |

| 1.8 MHz                                                               |                                                                                                                                                                               |     | -137        |     | dBc/Hz     |

| 6 MHz                                                                 |                                                                                                                                                                               |     | -148        |     | dBc/Hz     |

| Parameter                                                 | Test Conditions/Comments                        | Min | Тур | Max | Unit |

|-----------------------------------------------------------|-------------------------------------------------|-----|-----|-----|------|

| DAC TO DAC OUTPUT ISOLATION                               | Taken using the AD9171-FMC-EBZ evaluation board |     |     |     |      |

| Single-Band— $f_{DAC} = 6000$ MSPS, Mode 0 (L = 1, M = 2) |                                                 |     |     |     |      |

|                                                           | f <sub>OUT</sub> = 1840 MHz                     |     | -81 |     | dBc  |

|                                                           | f <sub>OUT</sub> = 2100 MHz                     |     | -78 |     | dBc  |

|                                                           | f <sub>OUT</sub> = 2650 MHz                     |     | -73 |     | dBc  |

## **ABSOLUTE MAXIMUM RATINGS**

Table 9.

| Rating                                 |

|----------------------------------------|

| -0.3 V to AVDD1.8 + 0.3 V              |

| $-0.2\mathrm{V}$ to SVDD1.0 + 0.2 V    |

| -0.3  V to DVDD1.8 + 0.3 V             |

|                                        |

|                                        |

| $-0.2\mathrm{V}$ to AVDD1.0 + 0.2 V    |

|                                        |

| $-0.2\mathrm{V}$ to DVDD1.0 + 0.2 V    |

| $-0.2 \mathrm{V}$ to $+1.2 \mathrm{V}$ |

| -0.3 V to 2.2 V                        |

| 118°C                                  |

| −65°C to +150°C                        |

| 260°C                                  |

|                                        |

Some operating modes of the device may cause the device to approach or exceed the maximum junction temperature during operation at supported ambient temperatures. Removal of heat from the device may require additional measures such as active airflow, heat sinks, or other measures.

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

#### **REFLOW PROFILE**

The AD9171 reflow profile is in accordance with the JEDEC JESD20 criteria for Pb-free devices. The maximum reflow temperature is 260°C.

#### THERMAL CHARACTERISTICS

Thermal performance is directly linked to printed circuit board (PCB) design and operating environment. Careful attention to PCB thermal design is required.

$\theta_{JA}$  is the natural convection junction to ambient thermal resistance measured in a one cubic foot sealed enclosure.  $\theta_{JC}$  is the junction to case thermal resistance.

Thermal resistances and thermal characterization parameters are specified vs. the number of PCB layers in different airflow velocities (in m/sec). The use of appropriate thermal management techniques is recommended to ensure that the maximum junction temperature does not exceed the limits shown in Table 10.

Use the values in Table 11 in compliance with JEDEC 51-12.

Table 10. Simulated Thermal Resistance vs. PCB Layers<sup>1</sup>

| PCB Type                  | Airflow<br>Velocity<br>(m/sec) | θ <sub>JA</sub> | $\theta_{	exttt{JC\_TOP}}$ | Ө <sub>ЈС_ВОТ</sub> | Unit |

|---------------------------|--------------------------------|-----------------|----------------------------|---------------------|------|

| JEDEC 2s2p Board          | 0.0                            | 25.3            | 2.43                       | 3.04                | °C/W |

|                           | 1.0                            | 22.6            | N/A                        | N/A                 | °C/W |

|                           | 2.5                            | 21.0            | N/A                        | N/A                 | °C/W |

| 12-Layer PCB <sup>2</sup> | 0.0                            | 15.4            | 2.4                        | 2.6                 | °C/W |

|                           | 1.0                            | 13.1            | N/A                        | N/A                 | °C/W |

|                           | 2.5                            | 11.6            | N/A                        | N/A                 | °C/W |

<sup>&</sup>lt;sup>1</sup> N/A means not applicable.

#### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

<sup>&</sup>lt;sup>2</sup> Non JEDEC thermal resistance.

<sup>&</sup>lt;sup>3</sup> 1SOP PCB with no vias in PCB.

<sup>&</sup>lt;sup>4</sup> 1SOP PCB with 7 × 7 standard JEDEC vias.

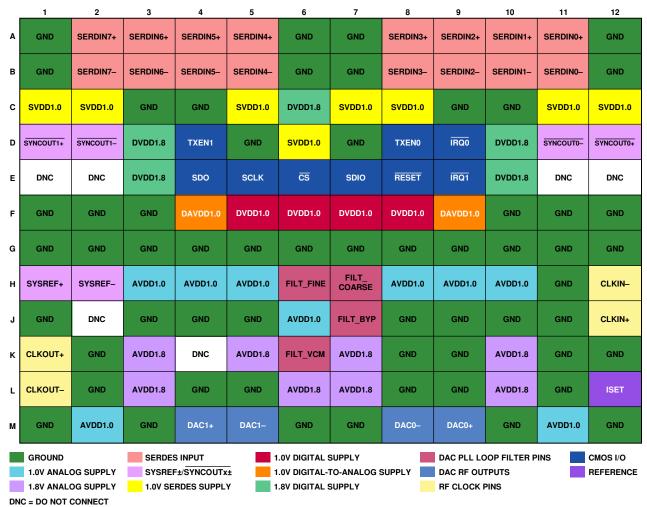

## PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Figure 2. Pin Configuration

**Table 11. Pin Function Descriptions**

| Pin No.                          | Mnemonic | Description                                                                                                                                                                                                                                                                                                 |

|----------------------------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.0 V Supply                     |          |                                                                                                                                                                                                                                                                                                             |

| H3 to H5, H8 to H10, J6, M2, M11 | AVDD1.0  | 1.0 V Clock and Analog Supplies. These pins supply the clock receivers, clock distribution, the on-chip DAC clock multiplier, and the DAC analog core. Clean power supply rail sources are required on these pins.                                                                                          |

| F5 to F8                         | DVDD1.0  | 1.0 V Digital Supplies. These pins supply power to the DAC digital circuitry. Clean power supply rail sources are required on these pins.                                                                                                                                                                   |

| F4, F9                           | DAVDD1.0 | 1.0 V Digital to Analog Supplies. These pins can share a supply rail with the DVDD1.0 supply (electrically connected) but must have separate supply plane and decoupling capacitors for the PCB layout to improve isolation for these two pins. Clean power supply rail sources are required on these pins. |

| C1, C2, C5, C7, C8, C11, C12, D6 | SVDD1.0  | 1.0 V SERDES Supplies to the JESD204B Data Interface. Clean power supply rail sources are required on these pins.                                                                                                                                                                                           |

| 1.8 V Supply                     |          |                                                                                                                                                                                                                                                                                                             |

| K3, K5, K7, K10, L3, L6, L7, L10 | AVDD1.8  | 1.8 V Analog Supplies to the On-Chip DAC Clock Multiplier and the DAC Analog Core. Clean power supply rail sources are required on these pins.                                                                                                                                                              |

| C6, D3, D10, E3, E10             | DVDD1.8  | 1.8 V Digital Supplies to the JESD204B Data Interface and the Other Input/Output Circuitry, Such as the Serial Port Interface (SPI). Clean power supply rail sources are required on these pins.                                                                                                            |

| Pin No.                                                                                                                                                                                           | Mnemonic    | Description                                                                                                                                                                                                                                                                                                                              |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Ground                                                                                                                                                                                            |             |                                                                                                                                                                                                                                                                                                                                          |

| A1, A6, A7, A12, B1, B6, B7, B12, C3, C4, C9, C10, D5, D7, F1 to F3, F10 to F12, G1 to G12, H11, J1, J3 to J5, J8 to J11, K2, K8, K9, K11, K12, L2, L4, L5, L8, L9, L11, M1, M3, M6, M7, M10, M12 | GND         | Device Common Ground.                                                                                                                                                                                                                                                                                                                    |

| RF Clock                                                                                                                                                                                          |             |                                                                                                                                                                                                                                                                                                                                          |

| J12                                                                                                                                                                                               | CLKIN+      | Positive Device Clock Input. This pin is the clock input for the on-chip DAC clock multiplier, REFCLK, when the DAC PLL is on. This pin is also the clock input for the DAC sample clock or device clock (DACCLK) when the DAC PLL is off. AC couple this input. There is an internal $100~\Omega$ resistor between this pin and CLKIN—. |

| H12                                                                                                                                                                                               | CLKIN-      | Negative Device Clock Input.                                                                                                                                                                                                                                                                                                             |

| K1                                                                                                                                                                                                | CLKOUT+     | Positive Device Clock Output. This pin is the clock output of a divided down DACCLK and is available with the DAC PLL on and off. The divide down ratios are by 1, 2, or 4.                                                                                                                                                              |

| L1                                                                                                                                                                                                | CLKOUT-     | Negative Device Clock Output.                                                                                                                                                                                                                                                                                                            |

| System Reference                                                                                                                                                                                  |             |                                                                                                                                                                                                                                                                                                                                          |

| H1                                                                                                                                                                                                | SYSREF+     | Positive System Reference Input. It is recommended to ac couple this pin, but dc coupling is also acceptable. See Table 7 for the dc common-mode voltage.                                                                                                                                                                                |

| H2                                                                                                                                                                                                | SYSREF—     | Negative System Reference Input. It is recommended to ac couple this pin, but dc coupling is also acceptable. See Table 7 for the dc common-mode voltage.                                                                                                                                                                                |

| On-Chip DAC PLL Loop Filter                                                                                                                                                                       |             |                                                                                                                                                                                                                                                                                                                                          |

| H6                                                                                                                                                                                                | FILT_FINE   | On-Chip DAC Clock Multiplier and PLL Fine Loop Filter Input.                                                                                                                                                                                                                                                                             |

| H7                                                                                                                                                                                                | FILT_COARSE | On-Chip DAC Clock Multiplier and PLL Coarse Loop Filter Input.                                                                                                                                                                                                                                                                           |

| J7                                                                                                                                                                                                | FILT_BYP    | On-Chip DAC Clock Multiplier and LDO Bypass.                                                                                                                                                                                                                                                                                             |

| K6                                                                                                                                                                                                | FILT_VCM    | On-Chip DAC Clock Multiplier and VCO Common-Mode Input.                                                                                                                                                                                                                                                                                  |

| SERDES Data Bits                                                                                                                                                                                  |             |                                                                                                                                                                                                                                                                                                                                          |

| A2                                                                                                                                                                                                | SERDIN7+    | SERDES Data Bit 7, Positive.                                                                                                                                                                                                                                                                                                             |

| B2                                                                                                                                                                                                | SERDIN7-    | SERDES Data Bit 7, Negative.                                                                                                                                                                                                                                                                                                             |

| A3                                                                                                                                                                                                | SERDIN6+    | SERDES Data Bit 6, Positive.                                                                                                                                                                                                                                                                                                             |

| B3                                                                                                                                                                                                | SERDIN6-    | SERDES Data Bit 6, Negative.                                                                                                                                                                                                                                                                                                             |

| A4                                                                                                                                                                                                | SERDIN5+    | SERDES Data Bit 5, Positive.                                                                                                                                                                                                                                                                                                             |

| B4                                                                                                                                                                                                | SERDIN5-    | SERDES Data Bit 5, Negative.                                                                                                                                                                                                                                                                                                             |

| A5                                                                                                                                                                                                | SERDIN4+    | SERDES Data Bit 4, Positive.                                                                                                                                                                                                                                                                                                             |

| B5                                                                                                                                                                                                | SERDIN4-    | SERDES Data Bit 4, Negative.                                                                                                                                                                                                                                                                                                             |

| A8                                                                                                                                                                                                | SERDIN3+    | SERDES Data Bit 3, Positive.                                                                                                                                                                                                                                                                                                             |

| B8                                                                                                                                                                                                | SERDIN3-    | SERDES Data Bit 3, Negative.                                                                                                                                                                                                                                                                                                             |

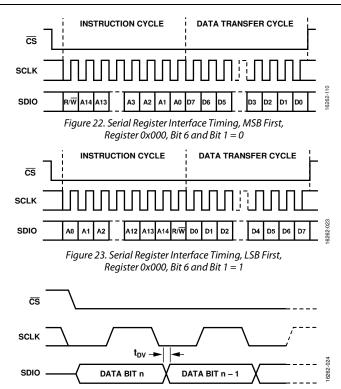

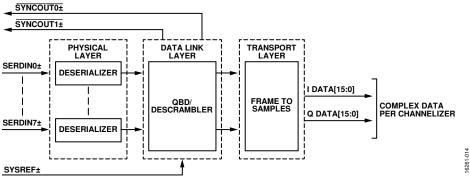

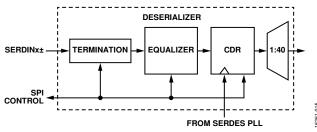

| A9                                                                                                                                                                                                | SERDIN2+    | SERDES Data Bit 2, Positive.                                                                                                                                                                                                                                                                                                             |