Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# Octal LNA/VGA/AAF/12-Bit ADC and CW I/Q Demodulator

AD9276

#### **FEATURES**

8 channels of LNA, VGA, AAF, ADC, and I/Q demodulator Low noise preamplifier (LNA)

Input-referred noise: 0.75 nV/√Hz typical at 5 MHz (gain = 21.3 dB)

SPI-programmable gain: 15.6 dB/17.9 dB/21.3 dB Single-ended input: V<sub>IN</sub> maximum = 733 mV p-p/

550 mV p-p/367 mV p-p

**Dual-mode active input impedance matching**

Bandwidth (BW) > 100 MHz

Full-scale (FS) output: 4.4 V p-p differential

Variable gain amplifier (VGA)

Attenuator range: -42 dB to 0 dB

Postamp gain: 21 dB/24 dB/27 dB/30 dB

Linear-in-dB gain control

Antialiasing filter (AAF)

Programmable second-order LPF from 8 MHz to 18 MHz

**Programmable HPF**

Analog-to-digital converter (ADC)

12 bits at 10 MSPS to 80 MSPS

SNR: 70 dB SFDR: 75 dB

Serial LVDS (ANSI-644, IEEE 1596.3 reduced range link)

Data and frame clock outputs

CW mode I/Q demodulator

Individual programmable phase rotation

Output dynamic range per channel >160 dBFS/√Hz

Low power: 195 mW per channel at 12 bits/40 MSPS (TGC),

94 mW per channel for CW Doppler

Flexible power-down modes

Overload recovery in <10 ns

Fast recovery from low power standby mode: <2 µs

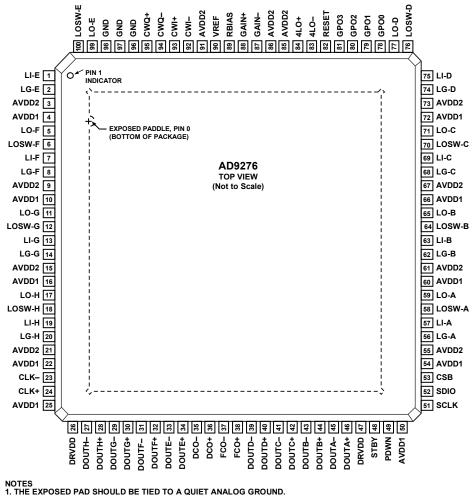

100-lead TQFP\_EP

#### **APPLICATIONS**

Medical imaging/ultrasound Automotive radar

#### **PRODUCT HIGHLIGHTS**

1. Small Footprint.

Eight channels are contained in a small, space-saving package. Full TGC path, ADC, and I/Q demodulator contained within a 100-lead,  $16 \text{ mm} \times 16 \text{ mm}$  TQFP.

2. Low Power.

In TGC mode, low power of 195 mW per channel at 40 MSPS. In CW mode, ultralow power of 94 mW per channel.

- Integrated High Dynamic Range I/Q Demodulator with Phase Rotation.

- 4. Ease of Use.

A data clock output (DCO±) operates up to 480 MHz and supports double data rate (DDR) operation.

5. User Flexibility.

Serial port interface (SPI) control offers a wide range of flexible features to meet specific system requirements.

Integrated Second-Order Antialiasing Filter.

This filter is placed before the ADC and is programmable from 8 MHz to 18 MHz.

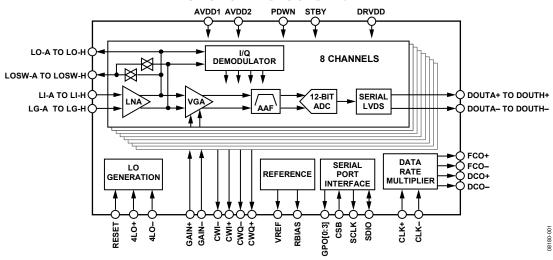

#### **FUNCTIONAL BLOCK DIAGRAM**

Figure 1.

# **AD9276\* PRODUCT PAGE QUICK LINKS**

Last Content Update: 02/23/2017

# COMPARABLE PARTS 🖳

View a parametric search of comparable parts.

### **EVALUATION KITS**

· AD9276 Evaluation Board

### **DOCUMENTATION**

#### **Data Sheet**

AD9276: Octal LNA/VGA/AAF/12-Bit ADC and CW I/Q Demodulator Data Sheet

#### **User Guides**

· UG-016: Evaluation Board User Guide

### TOOLS AND SIMULATIONS !-

- Visual Analog

- AD9276 IBIS Models

### REFERENCE MATERIALS 🖵

#### **Press**

Industry's First Octal Ultrasound Receiver with Digital I/Q Demodulator and Decimation Filter Reduces Processor Overhead in Ultrasound Systems

#### **Technical Articles**

• MS-2210: Designing Power Supplies for High Speed ADC

# DESIGN RESOURCES 🖵

- · AD9276 Material Declaration

- PCN-PDN Information

- · Quality And Reliability

- · Symbols and Footprints

### **DISCUSSIONS**

View all AD9276 EngineerZone Discussions.

### SAMPLE AND BUY 🖳

Visit the product page to see pricing options.

### **TECHNICAL SUPPORT**

Submit a technical question or find your regional support number.

### DOCUMENT FEEDBACK 🖳

Submit feedback for this data sheet.

# **TABLE OF CONTENTS**

| Features                                      |

|-----------------------------------------------|

| Applications                                  |

| Product Highlights                            |

| Functional Block Diagram 1                    |

| Revision History                              |

| General Description                           |

| Specifications                                |

| AC Specifications4                            |

| Digital Specifications                        |

| Switching Specifications                      |

| ADC Timing Diagrams9                          |

| Absolute Maximum Ratings                      |

| Thermal Impedance                             |

| ESD Caution 10                                |

| Pin Configuration and Function Descriptions11 |

| Typical Performance Characteristics           |

| TGC Mode14                                    |

| CW Doppler Mode17                             |

| Equivalent Circuits                           |

| Theory of Operation                           |

| Ultrasound                                          |

|-----------------------------------------------------|

| Channel Overview                                    |

| Input Overdrive                                     |

| CW Doppler Operation                                |

| TGC Operation                                       |

| ADC                                                 |

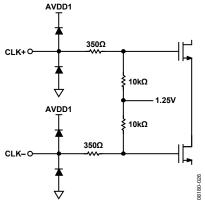

| Clock Input Considerations                          |

| Digital Outputs and Timing                          |

| Serial Port Interface (SPI)                         |

| Hardware Interface                                  |

| Memory Map 41                                       |

| Reading the Memory Map Table                        |

| Reserved Locations                                  |

| Default Values                                      |

| Logic Levels41                                      |

| Applications Information                            |

| Power and Ground Recommendations45                  |

| Exposed Paddle Thermal Heat Slug Recommendations 45 |

| Outline Dimensions                                  |

| Ordering Guide                                      |

### **REVISION HISTORY**

7/09—Revision 0: Initial Version

### **GENERAL DESCRIPTION**

The AD9276 is designed for low cost, low power, small size, and ease of use. It contains eight channels of a variable gain amplifier (VGA) with a low noise preamplifier (LNA); an antialiasing filter (AAF); a 12-bit, 10 MSPS to 80 MSPS analog-to-digital converter (ADC); and an I/Q demodulator with programmable phase rotation.

Each channel features a variable gain range of 42 dB, a fully differential signal path, an active input preamplifier termination, a maximum gain of up to 52 dB, and an ADC with a conversion rate of up to 80 MSPS. The channel is optimized for dynamic performance and low power in applications where a small package size is critical.

The LNA has a single-ended-to-differential gain that is selectable through the SPI. The LNA input noise is typically  $0.75~\text{nV}/\sqrt{\text{Hz}}$  at a gain of 21.3 dB, and the combined input-referred noise of the entire channel is  $0.85~\text{nV}/\sqrt{\text{Hz}}$  at maximum gain. Assuming a 15 MHz noise bandwidth (NBW) and a 21.3 dB LNA gain, the input SNR is roughly 92 dB. In CW Doppler mode, each LNA output drives an I/Q demodulator. Each demodulator has independently programmable phase rotation through the SPI with 16 phase settings.

The AD9276 requires a LVPECL-/CMOS-/LVDS-compatible sample rate clock for full performance operation. No external reference or driver components are required for many applications.

The ADC automatically multiplies the sample rate clock for the appropriate LVDS serial data rate. A data clock (DCO±) for capturing data on the output and a frame clock (FCO±) trigger for signaling a new output byte are provided.

Powering down individual channels is supported to increase battery life for portable applications. A standby mode option allows quick power-up for power cycling. In CW Doppler operation, the VGA, AAF, and ADC are powered down. The power of the TGC path scales with selectable ADC speed power modes.

The ADC contains several features designed to maximize flexibility and minimize system cost, such as a programmable clock, data alignment, and programmable digital test pattern generation. The digital test patterns include built-in fixed patterns, built-in pseudorandom patterns, and custom user-defined test patterns entered via the serial port interface.

Fabricated in an advanced CMOS process, the AD9276 is available in a 16 mm  $\times$  16 mm, RoHS compliant, 100-lead TQFP. It is specified over the industrial temperature range of  $-40^{\circ}$ C to  $+85^{\circ}$ C.

# **SPECIFICATIONS**

### **AC SPECIFICATIONS**

AVDD1 = 1.8 V, AVDD2 = 3.0 V, DRVDD = 1.8 V, 1.0 V internal ADC reference,  $f_{\rm IN}$  = 5 MHz,  $R_{\rm S}$  = 50  $\Omega$ , LNA gain = 21.3 dB, LNA bias = high, PGA gain = 27 dB, GAIN- = 0.8 V, AAF LPF cutoff =  $f_{\rm SAMPLE}$ /3 (Mode I/Mode II),  $f_{\rm SAMPLE}$ /4.5 (Mode III), HPF cutoff = LPF cutoff/20.7 (default), Mode I =  $f_{\rm SAMPLE}$  = 40 MSPS, Mode II =  $f_{\rm SAMPLE}$  = 65 MSPS, Mode III =  $f_{\rm SAMPLE}$  = 80 MSPS, full temperature, ANSI-644 LVDS mode, unless otherwise noted.

Table 1.

| Parameter <sup>1</sup> Test Conditions/Comments |                                                  | Min Typ | Max       | Unit   |  |

|-------------------------------------------------|--------------------------------------------------|---------|-----------|--------|--|

| LNA CHARACTERISTICS                             |                                                  |         |           |        |  |

| Gain                                            | Single-ended input to differential output        | 15.6/   | 17.9/21.3 | dB     |  |

|                                                 | Single-ended input to single-ended output        | 9.6/1   | 1.9/15.3  | dB     |  |

| Input Voltage Range                             | LNA output limited to 4.4 V p-p differential     |         |           |        |  |

| (Single-Ended)                                  | output                                           |         |           |        |  |

|                                                 | LNA gain = 15.6 dB                               | 733     |           | mV p-p |  |

|                                                 | LNA gain = 17.9 dB                               | 550     |           | mV p-p |  |

|                                                 | LNA gain = 21.3 dB                               | 367     |           | mV p-p |  |

| Input Common Mode (LI-x, LG-x)                  |                                                  | 1.0     |           | V      |  |

| Output Common Mode (LO-x)                       |                                                  | 1.5     |           | V      |  |

| Output Common Mode (LOSW-x)                     | Switch off                                       | High    | -Z        | Ω      |  |

|                                                 | Switch on                                        | 1.5     |           | V      |  |

| Input Resistance (LI-x)                         | $R_{FB} = 250 \Omega$                            | 50      |           | Ω      |  |

|                                                 | $R_{FB} = 500 \Omega$                            | 100     |           | Ω      |  |

|                                                 | R <sub>FB</sub> = ∞                              | 15      |           | kΩ     |  |

| Input Capacitance (LI-x)                        |                                                  | 22      |           | рF     |  |

| –3 dB Bandwidth                                 |                                                  | 100     |           | MHz    |  |

| Input Noise Voltage                             | $R_S = 0 \Omega$ , $R_{FB} = \infty$             |         |           |        |  |

| ,                                               | LNA gain = 15.6 dB                               | 0.98    |           | nV/√Hz |  |

|                                                 | LNA gain = 17.9 dB                               | 0.86    |           | nV/√Hz |  |

|                                                 | LNA gain = 21.3 dB                               | 0.75    |           | nV/√Hz |  |

| Input Noise Current                             | R <sub>FB</sub> = ∞                              | 1       |           | pA/√Hz |  |

| 1 dB Input Compression Point                    | GAIN+ = 0 V                                      |         |           |        |  |

| p                                               | LNA gain = 15.6 dB                               | 1.0     |           | V p-p  |  |

|                                                 | LNA gain = 17.9 dB                               | 0.8     |           | V p-p  |  |

|                                                 | LNA gain = 21.3 dB                               | 0.5     |           | V p-p  |  |

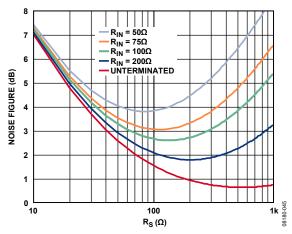

| Noise Figure                                    | $R_S = 50 \Omega$                                |         |           | . 6 6  |  |

| Active Termination Matched                      | LNA gain = 15.6 dB, $R_{FB} = 200 \Omega$        | 4.8     |           | dB     |  |

|                                                 | LNA gain = 17.9 dB, $R_{FB}$ = 250 $\Omega$      | 4.1     |           | dB     |  |

|                                                 | LNA gain = 21.3 dB, $R_{FB}$ = 350 $\Omega$      | 3.2     |           | dB     |  |

| Unterminated                                    | LNA gain = 15.6 dB, $R_{FB} = \infty$            | 3.4     |           | dB     |  |

| oc.                                             | LNA gain = 17.9 dB, $R_{FB} = \infty$            | 2.8     |           | dB     |  |

|                                                 | LNA gain = 21.3 dB, $R_{FB} = \infty$            | 2.3     |           | dB     |  |

| FULL-CHANNEL (TGC)                              | 2.0.134 2.00 4.0,141                             |         |           |        |  |

| CHARACTERISTICS                                 |                                                  |         |           |        |  |

| AAF Low-Pass Cutoff                             |                                                  |         |           |        |  |

| In Range                                        | −3 dB, programmable                              | 8       | 18        | MHz    |  |

| In Range AAF Bandwidth<br>Tolerance             |                                                  | ±10     |           | %      |  |

| Group Delay Variation                           | f = 1  MHz to  18  MHz, GAIN + = 0  V to  1.6  V | ±0.5    |           | ns     |  |

| Input-Referred Noise Voltage                    | $GAIN+=1.6 \text{ V}, R_{FB}=\infty$             |         |           |        |  |

| -                                               | LNA gain = 15.6 dB                               | 1.26    |           | nV/√Hz |  |

|                                                 | LNA gain = 17.9 dB                               | 1.04    |           | nV/√Hz |  |

|                                                 | LNA gain = 21.3 dB                               | 0.85    |           | nV/√Hz |  |

| Parameter <sup>1</sup>                                 | Test Conditions/Comments                                                                                                                                             | Min                | Тур         | Max                | Unit    |

|--------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-------------|--------------------|---------|

| Noise Figure                                           | GAIN+ = 1.6 V, $R_S$ = 50 Ω                                                                                                                                          |                    |             |                    |         |

| Active Termination Matched<br>Mode I/Mode II/Mode III  | LNA gain = 15.6 dB, $R_{FB} = 200 \Omega$                                                                                                                            |                    | 8.0/7.7/7.6 |                    | dB      |

|                                                        | LNA gain = 17.9 dB, $R_{FB} = 250 \Omega$                                                                                                                            |                    | 6.6/6.2/6.1 |                    | dB      |

|                                                        | LNA gain = 21.3 dB, $R_{FB}$ = 350 $\Omega$                                                                                                                          |                    | 4.7/4.5/4.4 |                    | dB      |

| Unterminated                                           | LNA gain = 15.6 dB, R <sub>FB</sub> = ∞                                                                                                                              |                    | 4.7         |                    | dB      |

|                                                        | LNA gain = 17.9 dB, R <sub>FB</sub> = ∞                                                                                                                              |                    | 3.7         |                    | dB      |

|                                                        | LNA gain = 21.3 dB, R <sub>FB</sub> = ∞                                                                                                                              |                    | 2.8         |                    | dB      |

| Correlated Noise Ratio                                 | No signal, correlated/uncorrelated                                                                                                                                   |                    | -30         |                    | dB      |

| Output Offset                                          |                                                                                                                                                                      | -35                |             | +35                | LSB     |

| Signal-to-Noise Ratio (SNR)<br>Mode I/Mode II/Mode III | $f_{IN} = 5 \text{ MHz at} - 10 \text{ dBFS, GAIN} + = 0 \text{ V}$                                                                                                  |                    | 65/64/63    |                    | dBFS    |

|                                                        | $f_{IN} = 5 \text{ MHz at } -1 \text{ dBFS, GAIN} + = 1.6 \text{ V}$                                                                                                 |                    | 57/56/54.5  |                    | dBFS    |

| Harmonic Distortion<br>Mode I/Mode II/Mode III         |                                                                                                                                                                      |                    |             |                    |         |

| Second Harmonic                                        | $f_{IN} = 5 \text{ MHz at } -10 \text{ dBFS, GAIN} + = 0 \text{ V}$                                                                                                  |                    | -62/-58/-55 |                    | dBc     |

|                                                        | $f_{IN} = 5 \text{ MHz at} - 1 \text{ dBFS, GAIN} + = 1.6 \text{ V}$                                                                                                 |                    | -60/-61/-58 |                    | dBc     |

| Third Harmonic                                         | $f_{IN} = 5 \text{ MHz at } -10 \text{ dBFS, GAIN} + = 0 \text{ V}$                                                                                                  |                    | -71/-60/-60 |                    | dBc     |

|                                                        | $f_{IN} = 5 \text{ MHz at } -1 \text{ dBFS, GAIN} + = 1.6 \text{ V}$                                                                                                 |                    | -57/-55/-56 |                    | dBc     |

| Two-Tone Intermodulation (IMD3)                        | $\begin{cases} f_{RF1} = 5.015 \text{ MHz, } f_{RF2} = 5.020 \text{ MHz,} \\ A_{RF1} = 0 \text{ dB, } A_{RF2} = -20 \text{ dB, } GAIN+ = 1.6 \text{ V,} \end{cases}$ |                    | <b>-55</b>  |                    | dBc     |

|                                                        | IMD3 relative to A <sub>RF2</sub>                                                                                                                                    |                    | 70          |                    | ID      |

| Channel-to-Channel Crosstalk                           | $f_{IN} = 5 \text{ MHz at} - 1 \text{ dBFS}$                                                                                                                         |                    | -70         |                    | dB      |

|                                                        | Overrange condition <sup>2</sup>                                                                                                                                     |                    | <b>–65</b>  |                    | dB      |

| Channel-to-Channel Delay<br>Variation                  | Full TGC path, $f_{IN} = 5$ MHz, GAIN+ = 0 V to 1.6 V                                                                                                                |                    | 0.3         |                    | Degrees |

| PGA Gain                                               | Differential input to differential output                                                                                                                            |                    | 21/24/27/30 |                    | dB      |

| GAIN ACCURACY                                          | 25°C                                                                                                                                                                 |                    |             |                    |         |

| Gain Law Conformance Error<br>Mode I/Mode II/Mode III  | 0 < GAIN+ < 0.16 V                                                                                                                                                   |                    | 1.5         |                    | dB      |

|                                                        | 0.16 V < GAIN+ < 1.44 V                                                                                                                                              | -1.5/-1.5/<br>-1.6 |             | +1.5/+1.5/<br>+1.6 | dB      |

|                                                        | 1.44 V < GAIN+ < 1.6 V                                                                                                                                               | -1.5/-1.5/<br>-1.6 | -2.5        | +1.5/+1.5/<br>+1.6 | dB      |

| Linear Gain Error                                      | GAIN+ = 0.8 V, normalized for ideal AAF loss                                                                                                                         | -1.5               |             | +1.5               | dB      |

| Channel-to-Channel Matching                            | 0.16 V < GAIN+ < 1.44 V                                                                                                                                              |                    | 0.1         |                    | dB      |

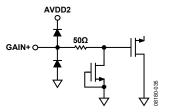

| GAIN CONTROL INTERFACE                                 |                                                                                                                                                                      |                    |             |                    |         |

| Normal Operating Range                                 |                                                                                                                                                                      | 0                  |             | 1.6                | V       |

| Gain Range                                             | GAIN+ = 0 V to 1.6 V                                                                                                                                                 | -42                |             | 0                  | dB      |

| Scale Factor                                           |                                                                                                                                                                      |                    | 28.5        |                    | dB/V    |

| Response Time                                          | 42 dB change                                                                                                                                                         |                    | 750         |                    | ns      |

| GAIN+ Impedance                                        | Single-ended                                                                                                                                                         |                    | 10          |                    | ΜΩ      |

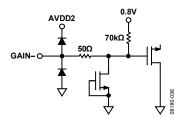

| GAIN – Impedance                                       | Single-ended                                                                                                                                                         |                    | 70          |                    | kΩ      |

| CW DOPPLER MODE                                        |                                                                                                                                                                      |                    |             |                    |         |

| LO Frequency                                           | $f_{LO} = f_{4LO}/4$                                                                                                                                                 | 1                  |             | 10                 | MHz     |

| Phase Increment                                        | Per channel                                                                                                                                                          |                    | 22.5        |                    | Degrees |

| Output DC Bias (Single-Ended)                          | CWI+, CWI–, CWQ+, CWQ–                                                                                                                                               |                    | 1.5         |                    | V       |

| Maximum Output Swing                                   | Per CWI+, CWI-, CWQ+, CWQ-, per channel enabled                                                                                                                      |                    |             | ±1.25              | mA      |

| Transconductance (Differential)                        | Demodulated I <sub>OUT</sub> /V <sub>IN</sub> , each I or Q output                                                                                                   |                    |             |                    |         |

|                                                        | LNA gain = 15.6 dB                                                                                                                                                   |                    | 1.8         |                    | mA/V    |

|                                                        | LNA gain = 17.9 dB                                                                                                                                                   |                    | 2.4         |                    | mA/V    |

|                                                        | LNA gain = 21.3 dB                                                                                                                                                   |                    | 3.5         |                    | mA/V    |

| Parameter <sup>1</sup>                                | Test Conditions/Comments                                                                                                                                                                                           | Min | Тур                | Max                | Unit     |

|-------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--------------------|--------------------|----------|

| Input-Referred Noise Voltage                          | $R_S = 0 \Omega$ , $R_{FB} = \infty$                                                                                                                                                                               |     |                    |                    |          |

|                                                       | LNA gain = 15.6 dB                                                                                                                                                                                                 |     | 1.5                |                    | nV/√Hz   |

|                                                       | LNA gain = 17.9 dB                                                                                                                                                                                                 |     | 1.4                |                    | nV/√Hz   |

|                                                       | LNA gain = 21.3 dB                                                                                                                                                                                                 |     | 1.3                |                    | nV/√Hz   |

| Noise Figure                                          | $R_S = 50 \Omega$ , $R_{FB} = \infty$                                                                                                                                                                              |     |                    |                    |          |

|                                                       | LNA gain = 15.6 dB                                                                                                                                                                                                 |     | 5.7                |                    | dB       |

|                                                       | LNA gain = 17.9 dB                                                                                                                                                                                                 |     | 5.3                |                    | dB       |

|                                                       | LNA gain = 21.3 dB                                                                                                                                                                                                 |     | 4.8                |                    | dB       |

| Input-Referred Dynamic Range                          | $R_S = 0 \Omega$ , $R_{FB} = \infty$                                                                                                                                                                               |     |                    |                    |          |

|                                                       | LNA gain = 15.6 dB                                                                                                                                                                                                 |     | 164                |                    | dBFS/√Hz |

|                                                       | LNA gain = 17.9 dB                                                                                                                                                                                                 |     | 162                |                    | dBFS/√Hz |

|                                                       | LNA gain = 21.3 dB                                                                                                                                                                                                 |     | 160                |                    | dBFS/√Hz |

| Output-Referred SNR                                   | $-3$ dBFS input, $f_{RF} = 2.5$ MHz, $f_{4LO} = 10$ MHz, 1 kHz offset                                                                                                                                              |     | 155                |                    | dBc/√Hz  |

| Two-Tone Intermodulation (IMD3)                       | $\begin{aligned} f_{RF1} &= 5.015 \text{ MHz, } f_{RF2} = 5.020 \text{ MHz,} \\ f_{4LO} &= 20 \text{ MHz, } A_{RF1} = 0 \text{ dB, } A_{RF2} = -20 \text{ dB,} \\ IMD3 \text{ relative to } A_{RF2} \end{aligned}$ |     | <b>–</b> 58        |                    | dB       |

| Quadrature Phase Error                                | I to Q, all phases, 1 σ                                                                                                                                                                                            |     | 0.15               |                    | Degrees  |

| I/Q Amplitude Imbalance                               | I to Q, all phases, 1 σ                                                                                                                                                                                            |     | 0.015              |                    | dB       |

| Channel-to-Channel Matching                           | Phase I to I, Q to Q, 1 σ                                                                                                                                                                                          |     | 0.5                |                    | Degrees  |

|                                                       | Amplitude I to I, Q to Q, 1 $\sigma$                                                                                                                                                                               |     | 0.25               |                    | dB       |

| POWER SUPPLY                                          |                                                                                                                                                                                                                    |     |                    |                    |          |

| Mode I/Mode III                                       |                                                                                                                                                                                                                    |     |                    |                    |          |

| AVDD1                                                 |                                                                                                                                                                                                                    | 1.7 | 1.8                | 1.9                | V        |

| AVDD2                                                 |                                                                                                                                                                                                                    | 2.7 | 3.0                | 3.6                | V        |

| DRVDD                                                 |                                                                                                                                                                                                                    | 1.7 | 1.8                | 1.9                | V        |

| l <sub>AVDD1</sub>                                    | TGC mode                                                                                                                                                                                                           |     | 190/263/317        |                    | mA       |

|                                                       | CW Doppler mode                                                                                                                                                                                                    |     | 15                 |                    | mA       |

| l <sub>AVDD2</sub>                                    | TGC mode, no signal                                                                                                                                                                                                |     | 365                |                    | mA       |

|                                                       | CW Doppler mode per channel enabled, no signal                                                                                                                                                                     |     | 30                 |                    | mA       |

| I <sub>DRVDD</sub>                                    |                                                                                                                                                                                                                    |     | 49/51/52           |                    | mA       |

| Total Power Dissipation<br>(Including Output Drivers) | TGC mode, no signal                                                                                                                                                                                                |     | 1560/1690/<br>1780 | 1800/1940/<br>2050 | mW       |

|                                                       | CW Doppler mode with eight channels enabled, no signal                                                                                                                                                             |     | 750                |                    | mW       |

| Power-Down Dissipation                                |                                                                                                                                                                                                                    |     |                    | 5                  | mW       |

| Standby Power Dissipation                             |                                                                                                                                                                                                                    |     |                    | 175/200/210        | mW       |

| Power Supply Rejection Ratio (PSRR)                   |                                                                                                                                                                                                                    |     | 1.6                |                    | mV/V     |

| ADC RESOLUTION                                        |                                                                                                                                                                                                                    |     | 12                 |                    | Bits     |

| ADC REFERENCE                                         |                                                                                                                                                                                                                    |     |                    |                    |          |

| Output Voltage Error                                  | VREF = 1 V                                                                                                                                                                                                         |     |                    | ±20                | mV       |

| Load Regulation at 1.0 mA                             | VREF = 1 V                                                                                                                                                                                                         |     | 2                  |                    | mV       |

| Input Resistance                                      |                                                                                                                                                                                                                    | 1   | 6                  |                    | kΩ       |

<sup>&</sup>lt;sup>1</sup> See the AN-835 Application Note, *Understanding High Speed ADC Testing and Evaluation*, for a complete set of definitions and information about how these tests were completed. <sup>2</sup> The overrange condition is specified as being 6 dB more than the full-scale input range.

### **DIGITAL SPECIFICATIONS**

AVDD1 = 1.8 V, AVDD2 = 3.0 V, DRVDD = 1.8 V, 1.0 V internal ADC reference,  $f_{IN} = 5 \text{ MHz}$ , full temperature, unless otherwise noted.

Table 2.

| Parameter <sup>1</sup>                                    | Temperature | Min           | Тур         | Max         | Unit   |

|-----------------------------------------------------------|-------------|---------------|-------------|-------------|--------|

| CLOCK INPUTS (CLK+, CLK-)                                 |             |               |             |             |        |

| Logic Compliance                                          |             |               | CMOS/LVDS/L | VPECL       |        |

| Differential Input Voltage <sup>2</sup>                   | Full        | 250           |             |             | mV p-p |

| Input Common-Mode Voltage                                 | Full        |               | 1.2         |             | V      |

| Input Resistance (Differential)                           | 25°C        |               | 20          |             | kΩ     |

| Input Capacitance                                         | 25°C        |               | 1.5         |             | pF     |

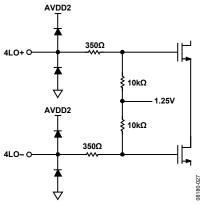

| CW 4LO INPUTS (4LO+, 4LO-)                                |             |               |             |             |        |

| Logic Compliance                                          |             |               | CMOS/LVDS/L | VPECL       |        |

| Differential Input Voltage <sup>2</sup>                   | Full        | 250           |             |             | mV p-p |

| Input Common-Mode Voltage                                 | Full        |               | 1.2         |             | V      |

| Input Resistance (Differential)                           | 25°C        |               | 20          |             | kΩ     |

| Input Capacitance                                         | 25°C        |               | 1.5         |             | pF     |

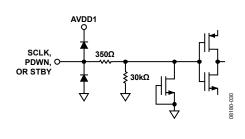

| LOGIC INPUTS (PDWN, STBY, SCLK, RESET)                    |             |               |             |             |        |

| Logic 1 Voltage                                           | Full        | 1.2           |             | 3.6         | V      |

| Logic 0 Voltage                                           | Full        |               |             | 0.3         | V      |

| Input Resistance                                          | 25°C        |               | 30          |             | kΩ     |

| Input Capacitance                                         | 25°C        |               | 0.5         |             | pF     |

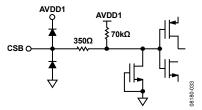

| LOGIC INPUT (CSB)                                         |             |               |             |             |        |

| Logic 1 Voltage                                           | Full        | 1.2           |             | 3.6         | V      |

| Logic 0 Voltage                                           | Full        |               |             | 0.3         | V      |

| Input Resistance                                          | 25°C        |               | 70          |             | kΩ     |

| Input Capacitance                                         | 25°C        |               | 0.5         |             | pF     |

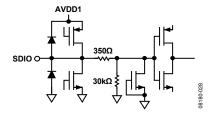

| LOGIC INPUT (SDIO)                                        |             |               |             |             | •      |

| Logic 1 Voltage                                           | Full        | 1.2           |             | DRVDD + 0.3 | V      |

| Logic 0 Voltage                                           | Full        | 0             |             | 0.3         | V      |

| Input Resistance                                          | 25°C        |               | 30          |             | kΩ     |

| Input Capacitance                                         | 25°C        |               | 2           |             | pF     |

| LOGIC OUTPUT (SDIO) <sup>3</sup>                          |             |               |             |             |        |

| Logic 1 Voltage ( $I_{OH} = 800 \mu A$ )                  | Full        |               | 1.79        |             | V      |

| Logic 0 Voltage ( $I_{OL} = 50 \mu A$ )                   | Full        |               |             | 0.05        | V      |

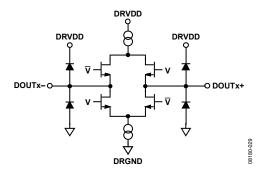

| DIGITAL OUTPUTS (DOUTx+, DOUTx-), (ANSI-644) <sup>1</sup> |             |               |             |             |        |

| Logic Compliance                                          |             |               | LVDS        |             |        |

| Differential Output Voltage (VoD)                         | Full        | 247           |             | 454         | mV     |

| Output Offset Voltage (Vos)                               | Full        | 1.125         |             | 1.375       | V      |

| Output Coding (Default)                                   |             | Offset binary |             |             |        |

| DIGITAL OUTPUTS (DOUTx+, DOUTx-),                         |             |               |             | •           |        |

| (LOW POWER, REDUCED SIGNAL OPTION) <sup>1</sup>           |             |               |             |             |        |

| Logic Compliance                                          |             |               | LVDS        |             |        |

| Differential Output Voltage (VoD)                         | Full        | 150 250       |             | 250         | mV     |

| Output Offset Voltage (Vos)                               | Full        |               |             | 1.30        | V      |

| Output Coding (Default)                                   |             |               | Offset bina |             |        |

| LOGIC OUTPUTS (GPO0, GPO1, GPO2, GPO3)                    |             |               |             |             |        |

| Logic 0 Voltage (I <sub>OL</sub> = 50 μA)                 | Full        |               |             | 0.05        | V      |

<sup>&</sup>lt;sup>1</sup> See the AN-835 Application Note, *Understanding High Speed ADC Testing and Evaluation*, for a complete set of definitions and information about how these tests were completed.

<sup>&</sup>lt;sup>2</sup> Specified for LVDS and LVPECL only.

<sup>3</sup> Specified for 13 SDIO pins sharing the same connection.

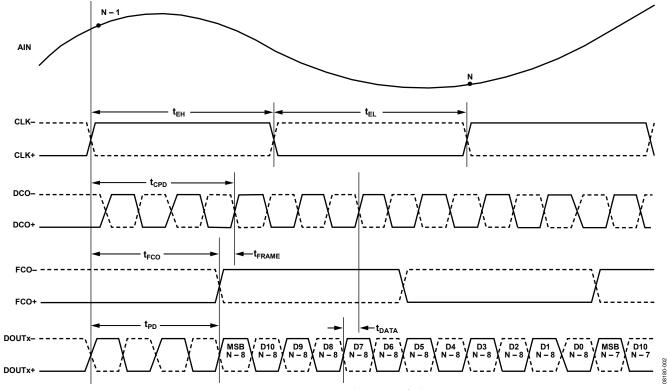

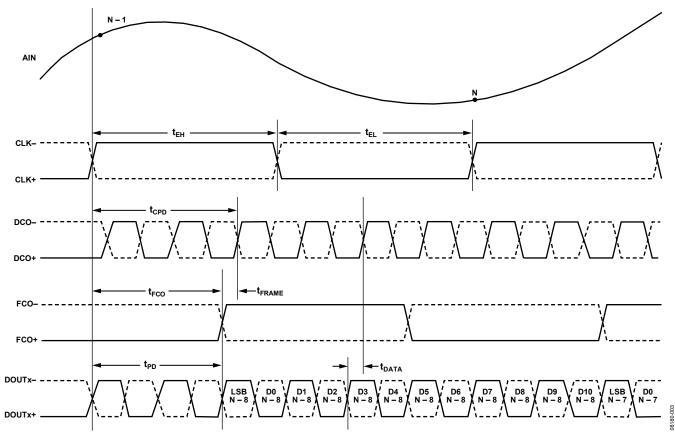

### **SWITCHING SPECIFICATIONS**

AVDD1 = 1.8 V, AVDD2 = 3.0 V, DRVDD = 1.8 V, 1.0 V internal ADC reference,  $f_{IN} = 5 \text{ MHz}$ , full temperature, unless otherwise noted.

Table 3.

| Parameter <sup>1</sup>                              | Temperature | Min                     | Тур                         | Max                     | Unit   |

|-----------------------------------------------------|-------------|-------------------------|-----------------------------|-------------------------|--------|

| CLOCK <sup>2</sup>                                  |             |                         |                             |                         |        |

| Clock Rate                                          |             |                         |                             |                         |        |

| 40 MSPS (Mode I)                                    | Full        | 10                      |                             | 40                      | MHz    |

| 65 MSPS (Mode II)                                   | Full        | 10                      |                             | 65                      | MHz    |

| 80 MSPS (Mode III)                                  | Full        | 10                      |                             | 80                      | MHz    |

| Clock Pulse Width High (teh)                        | Full        |                         | 6.25                        |                         | ns     |

| Clock Pulse Width Low (tel)                         | Full        |                         | 6.25                        |                         | ns     |

| OUTPUT PARAMETERS <sup>2, 3</sup>                   |             |                         |                             |                         |        |

| Propagation Delay (tpd)                             | Full        | $(t_{SAMPLE}/2) + 1.5$  | $(t_{SAMPLE}/2) + 2.3$      | $(t_{SAMPLE}/2) + 3.1$  | ns     |

| Rise Time (t <sub>R</sub> ) (20% to 80%)            | Full        |                         | 300                         |                         | ps     |

| Fall Time (t <sub>F</sub> ) (20% to 80%)            | Full        |                         | 300                         |                         | ps     |

| FCO Propagation Delay (t <sub>FCO</sub> )           | Full        | $(t_{SAMPLE}/2) + 1.5$  | $(t_{SAMPLE}/2) + 2.3$      | $(t_{SAMPLE}/2) + 3.1$  | ns     |

| DCO Propagation Delay (tcpd)4                       | Full        |                         | $t_{FCO} + (t_{SAMPLE}/24)$ |                         | ns     |

| DCO to Data Delay (t <sub>DATA</sub> ) <sup>4</sup> | Full        | $(t_{SAMPLE}/24) - 300$ | $(t_{SAMPLE}/24)$           | $(t_{SAMPLE}/24) + 300$ | ps     |

| DCO to FCO Delay (t <sub>FRAME</sub> ) <sup>4</sup> | Full        | $(t_{SAMPLE}/24) - 300$ | $(t_{SAMPLE}/24)$           | $(t_{SAMPLE}/24) + 300$ | ps     |

| Data-to-Data Skew ( $t_{DATA-MAX} - t_{DATA-MIN}$ ) | Full        |                         | ±100                        | ±350                    | ps     |

| Wake-Up Time (Standby), $GAIN+ = 0.5 V$             | 25°C        |                         | 2                           |                         | μs     |

| Wake-Up Time (Power-Down)                           | 25°C        |                         | 1                           |                         | ms     |

| Pipeline Latency                                    | Full        |                         | 8                           |                         | Clock  |

|                                                     |             |                         |                             |                         | cycles |

| APERTURE                                            |             |                         |                             |                         |        |

| Aperture Uncertainty (Jitter)                       | 25°C        |                         | <1                          |                         | ps rms |

| LO GENERATION                                       |             |                         |                             |                         |        |

| 4LO Frequency                                       | Full        | 4                       |                             | 40                      | MHz    |

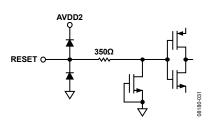

| LO Divider RESET Setup Time⁵                        | Full        | 5                       |                             |                         | ns     |

| LO Divider RESET Hold Time⁵                         | Full        | 5                       |                             |                         | ns     |

| LO Divider RESET High Pulse Width                   | Full        | 20                      |                             |                         | ns     |

See the AN-835 Application Note, Understanding High Speed ADC Testing and Evaluation, for a complete set of definitions and information about how these tests were completed.

<sup>&</sup>lt;sup>2</sup> Can be adjusted via the SPI. <sup>3</sup> Measurements were made using a part soldered to FR-4 material.

$<sup>^4</sup>$  t<sub>SAMPLE</sub>/24 is based on the number of bits divided by 2 because the delays are based on half duty cycles.

$<sup>^{\</sup>rm 5}$  RESET edge to rising 4LO edge.

### **ADC TIMING DIAGRAMS**

Figure 2. 12-Bit Data Serial Stream (Default)

Figure 3. 12-Bit Data Serial Stream, LSB First

### **ABSOLUTE MAXIMUM RATINGS**

Table 4.

| Parameter                                                         | Rating           |

|-------------------------------------------------------------------|------------------|

| AVDD1 to GND                                                      | -0.3 V to +2.0 V |

| AVDD2 to GND                                                      | −0.3 V to +3.9 V |

| DRVDD to GND                                                      | -0.3 V to +2.0 V |

| GND to GND                                                        | −0.3 V to +0.3 V |

| AVDD2 to AVDD1                                                    | −2.0 V to +3.9 V |

| AVDD1 to DRVDD                                                    | -2.0 V to +2.0 V |

| AVDD2 to DRVDD                                                    | −2.0 V to +3.9 V |

| Digital Outputs (DOUTx+, DOUTx-, DCO+, DCO-, FCO+, FCO-) to GND   | -0.3 V to +2.0 V |

| CLK+, CLK-, SDIO to GND                                           | -0.3 V to +2.0 V |

| LI-x, LO-x, LOSW-x to GND                                         | −0.3 V to +3.9 V |

| CWI-, CWI+, CWQ-, CWQ+ to GND                                     | −0.3 V to +3.9 V |

| PDWN, STBY, SCLK, CSB to GND                                      | −0.3 V to +2.0 V |

| GAIN+, GAIN–, RESET, 4LO+, 4LO–,<br>GPO0, GPO1, GPO2, GPO3 to GND | -0.3 V to +3.9 V |

| RBIAS, VREF to GND                                                | -0.3 V to +2.0 V |

| Operating Temperature Range (Ambient)                             | −40°C to +85°C   |

| Storage Temperature Range (Ambient)                               | −65°C to +150°C  |

| Maximum Junction Temperature                                      | 150°C            |

| Lead Temperature (Soldering, 10 sec)                              | 300°C            |

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### THERMAL IMPEDANCE

Table 5.

| Airflow Velocity (m/s) | $\theta_{JA}^1$ | <b>Ө</b> ЈВ | θ <sub>JC</sub> | Unit |

|------------------------|-----------------|-------------|-----------------|------|

| 0.0                    | 20.3            |             |                 | °C/W |

| 1.0                    | 14.4            | 7.6         | 4.7             | °C/W |

| 2.5                    | 12.9            |             |                 | °C/W |

$<sup>^1</sup>$   $\theta_{\text{JA}}$  for a 4-layer PCB with solid ground plane (simulated). Exposed pad soldered to PCB.

### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

## PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Figure 4. Pin Configuration

**Table 6. Pin Function Descriptions**

| Pin No.                                     | Name   | Description                                                     |

|---------------------------------------------|--------|-----------------------------------------------------------------|

| 0, 96, 97, 98                               | GND    | Ground. Exposed paddle should be tied to a quiet analog ground. |

| 1                                           | LI-E   | LNA Analog Input for Channel E.                                 |

| 2                                           | LG-E   | LNA Ground for Channel E.                                       |

| 3, 9, 15, 21, 55, 61,<br>67, 73, 85, 86, 91 | AVDD2  | 3.0 V Analog Supply.                                            |

| 4, 10, 16, 22, 25, 50, 54, 60, 66, 72       | AVDD1  | 1.8 V Analog Supply.                                            |

| 5                                           | LO-F   | LNA Analog Inverted Output for Channel F.                       |

| 6                                           | LOSW-F | LNA Analog Switched Output for Channel F.                       |

| 7                                           | LI-F   | LNA Analog Input for Channel F.                                 |

| 8                                           | LG-F   | LNA Ground for Channel F.                                       |

| 11                                          | LO-G   | LNA Analog Inverted Output for Channel G.                       |

| 12                                          | LOSW-G | LNA Analog Switched Output for Channel G.                       |

| 13                                          | LI-G   | LNA Analog Input for Channel G.                                 |

| 14                                          | LG-G   | LNA Ground for Channel G.                                       |

| 17                                          | LO-H   | LNA Analog Inverted Output for Channel H.                       |

| 18                                          | LOSW-H | LNA Analog Switched Output for Channel H.                       |

| 19                                          | LI-H   | LNA Analog Input for Channel H.                                 |

| 20                                          | LG-H   | LNA Ground for Channel H.                                       |

Rev. 0 | Page 11 of 48

| Pin No.              | Name   | Description                                                                |

|----------------------|--------|----------------------------------------------------------------------------|

| 23                   | CLK-   | Clock Input Complement.                                                    |

| 24                   | CLK+   | Clock Input True.                                                          |

| 26, 47               | DRVDD  | 1.8 V Digital Output Driver Supply.                                        |

| 20, 47               | DOUTH- | ADC H Digital Output Complement.                                           |

| 28                   | DOUTH+ | ADC H Digital Output Complement.  ADC H Digital Output True.               |

| 29                   | DOUTG- | ADC G Digital Output Complement.                                           |

| 30                   | DOUTG+ | ADC G Digital Output Complement.  ADC G Digital Output True.               |

| 31                   | DOUTF- | ADC F Digital Output Complement.                                           |

| 32                   | DOUTF+ | ADC F Digital Output Complement.  ADC F Digital Output True.               |

| 33                   | DOUTE- | ADC E Digital Output True.  ADC E Digital Output Complement.               |

| 34                   | DOUTE+ | ADC E Digital Output Complement.  ADC E Digital Output True.               |

| 35                   | DCO-   | Digital Clock Output Complement.                                           |

| 36                   | DCO=   | Digital Clock Output True.                                                 |

| 37                   | FCO-   | Digital Frame Clock Output Complement.                                     |

| 38                   | FCO+   | Digital Frame Clock Output Complement.  Digital Frame Clock Output True.   |

| 39                   | DOUTD- | ADC D Digital Output Complement.                                           |

| 40                   | DOUTD+ | ADC D Digital Output Complement.  ADC D Digital Output True.               |

|                      | DOUTC- | ADC C Digital Output True.  ADC C Digital Output Complement.               |

| 41<br>42             | DOUTC+ | ADC C Digital Output Complement.  ADC C Digital Output True.               |

|                      | DOUTE- | ADC B Digital Output True.  ADC B Digital Output Complement.               |

| 43                   | DOUTB+ | ADC B Digital Output Complement.  ADC B Digital Output True.               |

| 44                   | DOUTA- | ADC A Digital Output True.  ADC A Digital Output Complement.               |

| 45                   | DOUTA+ |                                                                            |

| 46                   | STBY   | ADC A Digital Output True. Standby Power-Down.                             |

| 48<br>49             | PDWN   | Full Power-Down.                                                           |

| 51                   | SCLK   | Serial Clock.                                                              |

| 52                   | SDIO   | Serial Data Input/Output.                                                  |

| 53                   | CSB    | Chip Select Bar.                                                           |

| 56                   | LG-A   | LNA Ground for Channel A.                                                  |

| 57                   | LI-A   | LNA Analog Input for Channel A.                                            |

| 58                   | LOSW-A | LNA Analog Switched Output for Channel A.                                  |

| 59                   | LO-A   | LNA Analog Inverted Output for Channel A.                                  |

| 62                   | LG-B   | LNA Ground for Channel B.                                                  |

| 63                   | LI-B   | LNA Analog Input for Channel B.                                            |

| 64                   | LOSW-B | LNA Analog Switched Output for Channel B.                                  |

| 65                   | LO-B   | LNA Analog Inverted Output for Channel B.                                  |

| 68                   | LG-C   | LNA Ground for Channel C.                                                  |

| 69                   | LI-C   | LNA Analog Input for Channel C.                                            |

| 70                   | LOSW-C | LNA Analog Switched Output for Channel C.                                  |

| 70<br>71             | LO-C   | LNA Analog Inverted Output for Channel C.                                  |

| 74                   | LG-D   | LNA Ground for Channel D.                                                  |

| 7 <del>4</del><br>75 | LI-D   | LNA Analog Input for Channel D.                                            |

| 76<br>76             | LOSW-D | LNA Analog Switched Output for Channel D.                                  |

| 76<br>77             | LO-D   | LNA Analog Inverted Output for Channel D.                                  |

| 77<br>78             | GPO0   | General-Purpose Open-Drain Output 0.                                       |

| 78<br>79             | GPO1   | General-Purpose Open-Drain Output 0.  General-Purpose Open-Drain Output 1. |

| 80                   | GPO2   | General-Purpose Open-Drain Output 1.  General-Purpose Open-Drain Output 2. |

| 81                   | GPO3   | General-Purpose Open-Drain Output 2.  General-Purpose Open-Drain Output 3. |

| 82                   | RESET  | Reset for Synchronizing 4LO Divide-by-4 Counter.                           |

| 83                   | 4LO-   | CW Doppler 4LO Input Complement.                                           |

| 84                   | 4LO+   | CW Doppler 4LO Input True.                                                 |

| 87                   | GAIN-  | Gain Control Voltage Input Complement.                                     |

| 88                   | GAIN+  | Gain Control Voltage Input Complement.  Gain Control Voltage Input True.   |

|                      | JAINT  | Gain Control voltage input riue.                                           |

| Pin No. | Name   | Description                                                  |

|---------|--------|--------------------------------------------------------------|

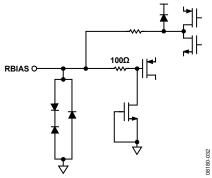

| 89      | RBIAS  | External Resistor to Set the Internal ADC Core Bias Current. |

| 90      | VREF   | Voltage Reference Input/Output.                              |

| 92      | CWI-   | CW Doppler I Output Complement.                              |

| 93      | CWI+   | CW Doppler I Output True.                                    |

| 94      | CWQ-   | CW Doppler Q Output Complement.                              |

| 95      | CWQ+   | CW Doppler Q Output True.                                    |

| 99      | LO-E   | LNA Analog Inverted Output for Channel E.                    |

| 100     | LOSW-E | LNA Analog Switched Output for Channel E.                    |

### TYPICAL PERFORMANCE CHARACTERISTICS

### **TGC MODE**

$f_{SAMPLE} = 40$  MSPS,  $f_{IN} = 5$  MHz,  $R_S = 50$   $\Omega$ , LNA gain = 21.3 dB, LNA bias = high, PGA gain = 27 dB, AAF LPF cutoff =  $f_{SAMPLE}/3$ , HPF cutoff = LPF cutoff/20.7 (default).

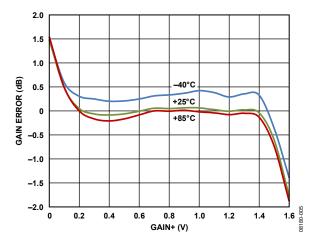

Figure 5. Gain Error vs. GAIN+ at Three Temperatures

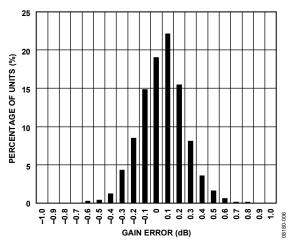

Figure 6. Gain Error Histogram, GAIN+ = 0.16 V

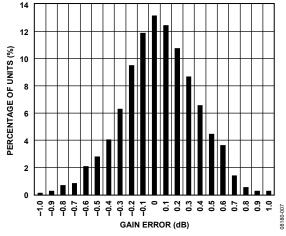

Figure 7. Gain Error Histogram, GAIN+ = 0.8 V

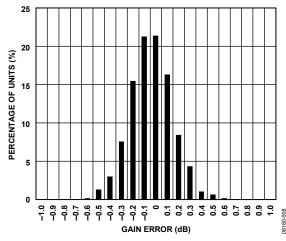

Figure 8. Gain Error Histogram, GAIN+ = 1.44 V

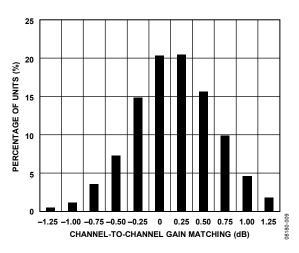

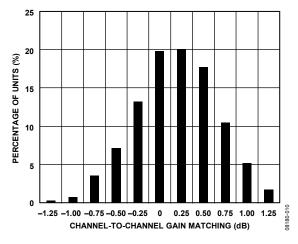

Figure 9. Gain Match Histogram, GAIN+ = 0.3 V

Figure 10. Gain Match Histogram, GAIN+ = 1.3 V

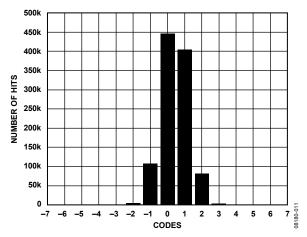

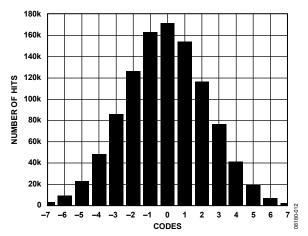

Figure 11. Output-Referred Noise Histogram, GAIN+ = 0.0 V

Figure 12. Output-Referred Noise Histogram, GAIN+ = 1.6 V

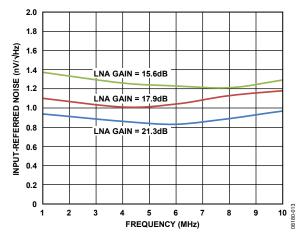

Figure 13. Short-Circuit, Input-Referred Noise vs. Frequency, PGA Gain = 30 dB, GAIN+ = 1.6 V

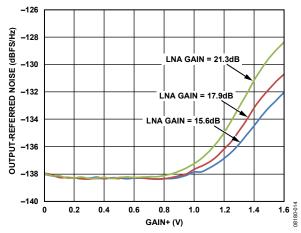

Figure 14. Short-Circuit, Output-Referred Noise vs. GAIN+

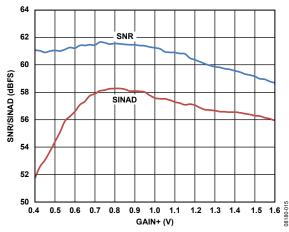

Figure 15. SNR/SINAD vs. GAIN+, AIN = -1.0 dBFS

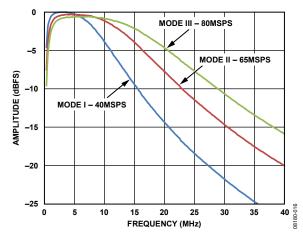

Figure 16. Antialiasing Filter (AAF) Pass-Band Response, LPF Cutoff = f<sub>SAMPLE</sub>/3 (Mode I and Mode II), f<sub>SAMPLE</sub>/4.5 (Mode III)

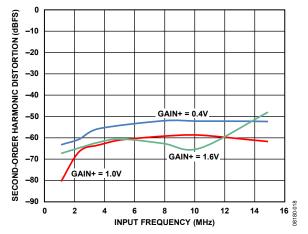

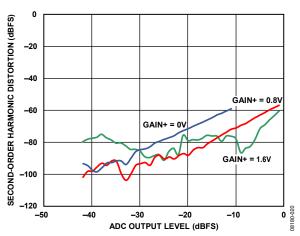

Figure 17. Second-Order Harmonic Distortion vs. Frequency, AIN = -1.0 dBFS

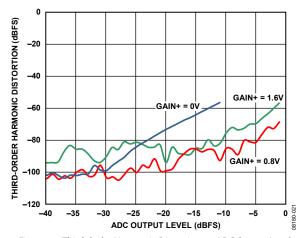

Figure 18. Third-Order Harmonic Distortion vs. Frequency, AIN = -1.0 dBFS

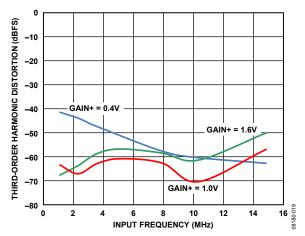

Figure 19. Second-Order Harmonic Distortion vs. ADC Output Level

Figure 20. Third-Order Harmonic Distortion vs. ADC Output Level

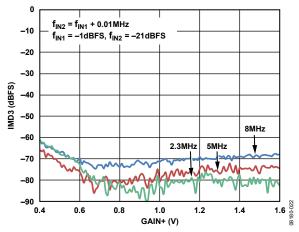

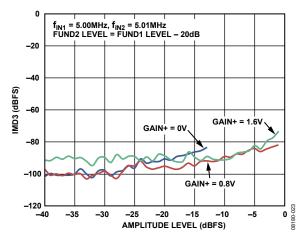

Figure 21. IMD3 vs. GAIN+

Figure 22. IMD3 vs. Amplitude Level

#### **CW DOPPLER MODE**

$f_{RF} = 2.5$  MHz at -3 dBFS,  $f_{4LO} = 10$  MHz,  $R_S = 50$   $\Omega$ , LNA gain = 21.3 dB, LNA bias = high, all CW channels enabled, phase rotation  $0^{\circ}$ .

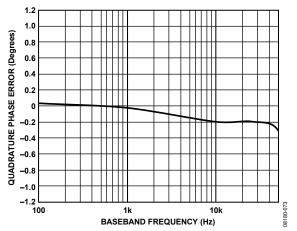

Figure 23. Quadrature Phase Error vs. Baseband Frequency

Figure 24. Quadrature Amplitude Imbalance vs. Baseband Frequency

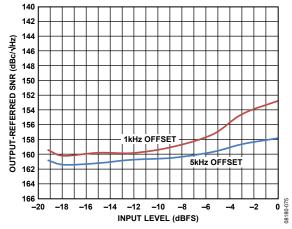

Figure 25. Output-Referred SNR vs. Input Level

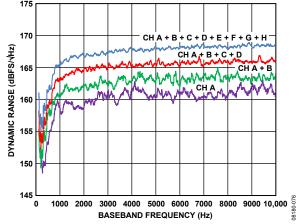

Figure 26. Small-Signal Dynamic Range

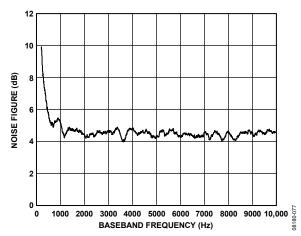

Figure 27. Noise Figure vs. Baseband Frequency

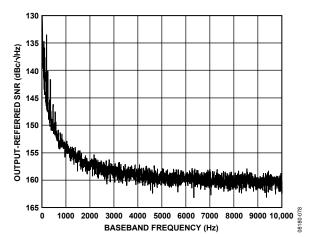

Figure 28. Output-Referred SNR vs. Baseband Frequency

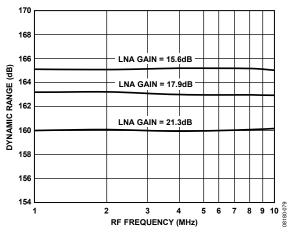

Figure 29. Small-Signal Dynamic Range vs. RF Frequency

# **EQUIVALENT CIRCUITS**

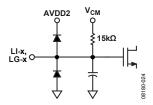

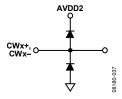

Figure 30. Equivalent LNA Input Circuit

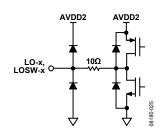

Figure 31. Equivalent LNA Output Circuit

Figure 32. Equivalent Clock Input Circuit

Figure 33. Equivalent 4LO Input Circuit

Figure 34. Equivalent SDIO Input Circuit

Figure 35. Equivalent Digital Output Circuit

Figure 36. Equivalent SCLK, PDWN, or STBY Input Circuit

Figure 37. Equivalent RESET Input Circuit

Figure 38. Equivalent CSB Input Circuit

Figure 39. Equivalent VREF Circuit

Figure 40. Equivalent RBIAS Circuit

Figure 41. Equivalent GAIN+ Input Circuit

Figure 42. Equivalent GAIN— Input Circuit

Figure 43. Equivalent CWI±, CWQ± Output Circuit

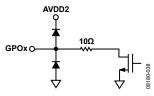

Figure 44. Equivalent GPOx Output Circuit

### THEORY OF OPERATION

#### **ULTRASOUND**

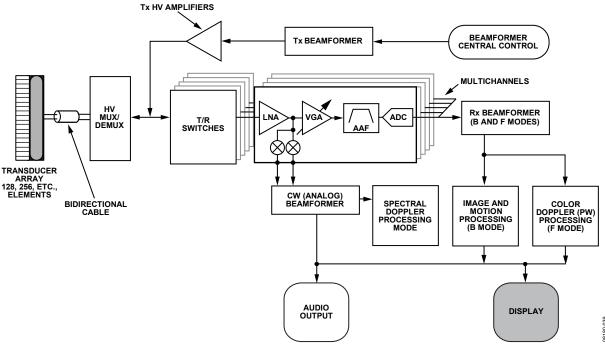

The primary application for the AD9276 is medical ultrasound. Figure 45 shows a simplified block diagram of an ultrasound system. A critical function of an ultrasound system is the time gain control (TGC) compensation for physiological signal attenuation. Because the attenuation of ultrasound signals is exponential with respect to distance (time), a linear-in-dB VGA is the optimal solution.

Key requirements in an ultrasound signal chain are very low noise, active input termination, fast overload recovery, low power, and differential drive to an ADC. Because ultrasound machines use beamforming techniques requiring large binary-weighted numbers of channels (for example, 32 to 512), using the lowest power at the lowest possible noise is of chief importance.

Most modern ultrasound machines use digital beamforming. In this technique, the signal is converted to digital format immediately following the TGC amplifier, and then beamforming is accomplished digitally.

The ADC resolution of 12 bits with up to 80 MSPS sampling satisfies the requirements of both general-purpose and high end systems.

Power conservation and low cost are two of the most important factors in low end and portable ultrasound machines, and the AD9276 is designed to meet these criteria.

For additional information regarding ultrasound systems, refer to "How Ultrasound System Considerations Influence Front-End Component Choice," *Analog Dialogue*, Volume 36, Number 3, May–July 2002, and "The AD9271—A Revolutionary Solution for Portable Ultrasound," *Analog Dialogue*, Volume 41, Number 7, July 2007.

Figure 45. Simplified Ultrasound System Block Diagram

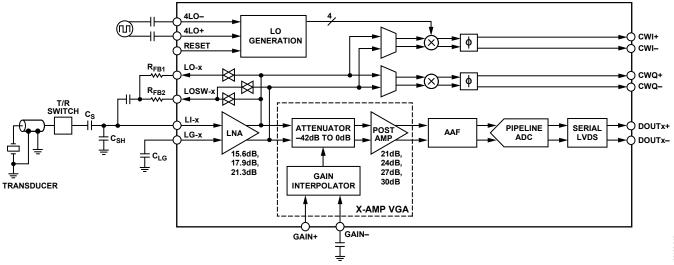

Figure 46. Simplified Block Diagram of a Single Channel

### **CHANNEL OVERVIEW**

Each channel contains both a TGC signal path and a CW Doppler signal path. Common to both signal paths, the LNA provides user-adjustable input impedance termination. The CW Doppler path includes an I/Q demodulator. The TGC path includes a differential X-AMP\* VGA, an antialiasing filter, and an ADC. Figure 46 shows a simplified block diagram with external components.

The signal path is fully differential throughout to maximize signal swing and reduce even-order distortion; however, the LNA is designed to be driven from a single-ended signal source.

### Low Noise Amplifier (LNA)

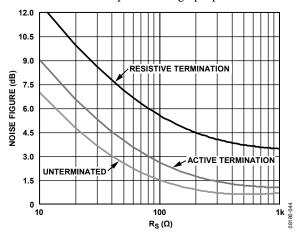

Good noise performance relies on a proprietary ultralow noise LNA at the beginning of the signal chain, which minimizes the noise contribution in the following VGA. Active impedance control optimizes noise performance for applications that benefit from input impedance matching.

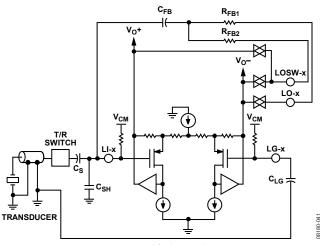

A simplified schematic of the LNA is shown in Figure 47. LI-x is capacitively coupled to the source. An on-chip bias generator establishes dc input bias voltages of around 0.9 V and centers the output common-mode levels at 1.5 V (AVDD2 divided by 2). A capacitor,  $C_{\rm LG}$ , of the same value as the input coupling capacitor,  $C_{\rm S}$ , is connected from the LG-x pin to ground.

It is highly recommended that the LG-x pins form a Kelvin type connection to the input or probe connection ground. Simply connecting the LG-x pin to ground near the device can allow differences in potential to be amplified through the LNA. This generally shows up as a dc offset voltage that can vary from channel to channel and part to part, depending on the application and the layout of the PCB.

Figure 47. Simplified LNA Schematic

The LNA supports differential output voltages as high as 4.4 V p-p with positive and negative excursions of  $\pm 1.1$  V from a common-mode voltage of 1.5 V. The LNA differential gain sets the maximum input signal before saturation. One of three gains is set through the SPI. The corresponding full-scale input for the gain settings of 15.6 dB, 17.9 dB, and 21.3 dB is 733 mV p-p, 550 mV p-p, and 367 mV p-p, respectively. Overload protection ensures quick recovery time from large input voltages. Because the inputs are capacitively coupled to a bias voltage near midsupply, very large inputs can be handled without interacting with the ESD protection.

Low value feedback resistors and the current-driving capability of the output stage allow the LNA to achieve a low input-referred noise voltage of 0.75 nV/ $\sqrt{\rm Hz}$  (at a gain of 21.3 dB). This is achieved with a current consumption of only 27 mA per channel (80 mW). On-chip resistor matching results in precise single-ended gains, which are critical for accurate impedance control. The use of a fully differential topology and negative feedback minimizes distortion. Low second-order harmonic distortion is particularly important in second harmonic ultrasound imaging applications. Differential signaling enables smaller swings at each output, further reducing third-order harmonic distortion.

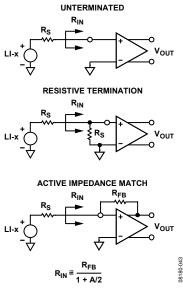

#### **Active Impedance Matching**

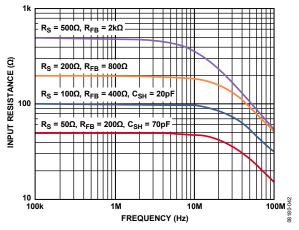

The LNA consists of a single-ended voltage gain amplifier with differential outputs and the negative output externally available. For example, with a fixed gain of 8× (17.9 dB), an active input termination is synthesized by connecting a feedback resistor between the negative output pin, LO-x, and the positive input pin, LI-x. This well-known technique is used for interfacing multiple probe impedances to a single system. The input resistance is shown in Equation 1.

$$R_{IN} = \frac{R_{FB}}{(1 + \frac{A}{2})} \tag{1}$$

where:

A/2 is the single-ended gain or the gain from the LI-x inputs to the LO-x outputs.

$R_{FB}$  is the resulting impedance of the  $R_{FB1}$  and  $R_{FB2}$  combination (see Figure 47).

Because the amplifier has a gain of 8× from its input to its differential output, it is important to note that the gain A/2 is the gain from Pin LI-x to Pin LO-x and that it is 6 dB less than the gain of the amplifier, or 11.9 dB (4×). The input resistance is reduced by an internal bias resistor of 15 k $\Omega$  in parallel with the source resistance connected to Pin LI-x, with Pin LG-x ac grounded. Equation 2 can be used to calculate the required  $R_{\rm FB}$  for a desired  $R_{\rm IN}$ , even for higher values of  $R_{\rm IN}$ .

$$R_{IN} = \frac{R_{FB}}{(1+3)} || 15 \text{ k}\Omega$$

(2)

For example, to set  $R_{\rm IN}$  to 200  $\Omega,$  the value of  $R_{\rm FB}$  must be 1000  $\Omega.$  If the simplified equation (Equation 2) is used to calculate  $R_{\rm IN},$  the value is 188  $\Omega,$  resulting in a gain error of less than 0.6 dB. Some factors, such as the presence of a dynamic source resistance, may influence the absolute gain accuracy more significantly. At higher frequencies, the input capacitance of the LNA must be considered. The user must determine the level of matching accuracy and adjust  $R_{\rm FB}$  accordingly.