# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# 8-Bit, 40/80/100 MSPS Dual A/D Converter

# AD9288

### FEATURES

Dual 8-bit, 40 MSPS, 80 MSPS, and 100 MSPS ADC Low power: 90 mW at 100 MSPS per channel On-chip reference and track-and-hold 475 MHz analog bandwidth each channel SNR = 47 dB @ 41 MHz 1 V p-p analog input range each channel Single 3.0 V supply operation (2.7 V to 3.6 V) Standby mode for single-channel operation Twos complement or offset binary output mode Output data alignment mode Pin-compatible 10-bit upgrade available

### APPLICATIONS

Battery-powered instruments Hand-held scopemeters Low cost digital oscilloscopes I and Q communications

### **GENERAL DESCRIPTION**

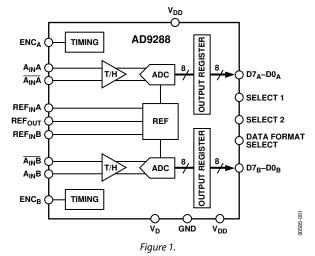

The AD9288 is a dual 8-bit monolithic sampling analog-todigital converter with on-chip track-and-hold circuits. It is optimized for low cost, low power, small size, and ease of use. The product operates at a 100 MSPS conversion rate with outstanding dynamic performance over its full operating range. Each channel can be operated independently.

The ADC requires only a single 3.0 V (2.7 V to 3.6 V) power supply and an Encode clock for full-performance operation. No external reference or driver components are required for many applications. The digital outputs are TTL/CMOS-compatible, and a separate output power supply pin supports interfacing with 3.3 V or 2.5 V logic.

### FUNCTIONAL BLOCK DIAGRAM

The Encode input is TTL/CMOS-compatible, and the 8-bit digital outputs can be operated from 3.0 V (2.5 V to 3.6 V) supplies. User-selectable options offer a combination of standby modes, digital data formats, and digital data timing schemes. In standby mode, the digital outputs are driven to a high impedance state.

Fabricated on an advanced CMOS process, the AD9288 is available in a 48-lead surface-mount plastic package (7 mm  $\times$ 7 mm, 1.4 mm LQFP) specified over the industrial temperature range (-40°C to +85°C). The AD9288 is pin-compatible with the 10-bit AD9218, facilitating future system migrations.

Rev. C

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700

www.analog.com

Fax: 781.326.8703

© 2004 Analog Devices, Inc. All rights reserved.

# **AD9288\* PRODUCT PAGE QUICK LINKS**

Last Content Update: 02/23/2017

### COMPARABLE PARTS

View a parametric search of comparable parts.

### DOCUMENTATION

### **Application Notes**

- AN-302: Exploit Digital Advantages in an SSB Receiver

- AN-835: Understanding High Speed ADC Testing and Evaluation

### Data Sheet

AD9288: 8-Bit, 40/80/100 MSPS Dual A/D Converter Data Sheet

### TOOLS AND SIMULATIONS $\square$

AD9288 IBIS Models

### REFERENCE MATERIALS

### **Technical Articles**

- Correlating High-Speed ADC Performance to Multicarrier 3G Requirements

- DNL and Some of its Effects on Converter Performance

- Single Chip Realizes Direct-Conversion Rx

### DESIGN RESOURCES

- AD9288 Material Declaration

- PCN-PDN Information

- Quality And Reliability

- Symbols and Footprints

### DISCUSSIONS

View all AD9288 EngineerZone Discussions.

### SAMPLE AND BUY

Visit the product page to see pricing options.

### TECHNICAL SUPPORT

Submit a technical question or find your regional support number.

### DOCUMENT FEEDBACK

Submit feedback for this data sheet.

# **TABLE OF CONTENTS**

| Specifications                              |

|---------------------------------------------|

| Explanation of Test Levels 4                |

| Timing Diagrams5                            |

| Absolute Maximum Ratings7                   |

| ESD Caution7                                |

| Pin Configuration and Function Descriptions |

| Typical Performance Characteristics         |

| Test Circuits                               |

| Terminology                                 |

| Theory of Operation14                       |

| Using the AD928814                          |

| Encode Input14                              |

| Digital Outputs14                           |

| Analog Input14                              |

| Voltage Reference                           |

# Timing14User-Selectable Options14AD9218/AD9288 Customer PCB BOM15Evaluation Board16Power Connector16Analog Inputs16Voltage Reference16Clocking16Data Outputs16Data Format/Gain16Timing16Troubleshooting20Outline Dimensions21Ordering Guide21

### **REVISION HISTORY**

### 12/04—Rev. B to Rev. C

| Change to Absolute Maximum Ratings | 7 |

|------------------------------------|---|

| Replaced Evaluation Board Section  |   |

| Updated Outline Dimensions         |   |

| Changes to Ordering Guide          |   |

|                                    |   |

### 2/02—Rev. A to Rev. B

| Edits to ABSOLUTE MAXIMUM RATINGS | RATINGS 3 |

|-----------------------------------|-----------|

|-----------------------------------|-----------|

1/01—Rev. 0 to Rev. A

2/99—Revision 0: Initial Version

# **SPECIFICATIONS**

$V_{\rm DD}$  = 3.0 V;  $V_{\rm D}$  = 3.0 V, differential input; external reference, unless otherwise noted.

### Table 1.

| <b>-</b> .                                                         | _    | Test  |       | AD9288BST-1 |       |       | AD9288BST-80    |       |       | AD9288BST-40    |       |        |

|--------------------------------------------------------------------|------|-------|-------|-------------|-------|-------|-----------------|-------|-------|-----------------|-------|--------|

| Parameter                                                          | Temp | Level | Min   | Тур         | Max   | Min   | Тур             | Max   | Min   | Тур             | Max   | Unit   |

| RESOLUTION                                                         |      |       |       | 8           |       |       | 8               |       |       | 8               |       | Bits   |

| DC ACCURACY                                                        |      |       |       |             |       |       |                 |       |       |                 |       |        |

| Differential Nonlinearity                                          | 25°C | I     |       | ± 0.5       | +1.25 |       | ± 0.5           | +1.25 |       | ± 0.5           | +1.25 | LSB    |

|                                                                    | Full | VI    |       |             | 1.50  |       |                 | 1.50  |       |                 | 1.50  | LSB    |

| Integral Nonlinearity                                              | 25°C | 1     |       | ± 0.50      | +1.25 |       | ± 0.50          | +1.25 |       | ± 0.50          | +1.25 | LSB    |

|                                                                    | Full | VI    |       |             | 1.50  |       |                 | 1.50  |       |                 | 1.50  | LSB    |

| No Missing Codes                                                   | Full | VI    |       | Guaranteed  |       |       | Guaranteed      |       |       | Guaranteed      |       |        |

| Gain Error <sup>1</sup>                                            | 25°C | 1     | -6    | ± 2.5       | +6    | -6    | ± 2.5           | +6    | -6    | ± 2.5           | +6    | % FS   |

|                                                                    | Full | VI    | -8    |             | +8    | -8    |                 | +8    | -8    |                 | +8    | % FS   |

| Gain Tempco <sup>1</sup>                                           | Full | VI    |       | 80          |       |       | 80              |       |       | 80              |       | ppm/   |

| Gain Matching                                                      | 25°C | V     |       | ±1.5        |       |       | ±1.5            |       |       | ±1.5            |       | % FS   |

| Voltage Matching                                                   | 25°C | V     |       | ±15         |       |       | ±15             |       |       | ±15             |       | mV     |

| ANALOG INPUT                                                       |      |       |       |             |       |       |                 |       |       |                 |       |        |

| Input Voltage Ra <u>ng</u> e (with<br>Respect to A <sub>IN</sub> ) | Full | v     |       | ±512        |       |       | ±512            |       |       | ±512            |       | mV p-  |

| Common-Mode Voltage                                                | Full | v     | 0.3 × | 0.3 × VD    | 0.3 × | 0.3 × | $0.3 \times VD$ | 0.3 × | 0.3 × | $0.3 \times VD$ | 0.3 × | v      |

|                                                                    |      |       | VD    |             | VD    | VD    |                 | VD    | VD    |                 | VD    |        |

|                                                                    |      |       | -0.2  |             | +0.2  | -0.2  |                 | +0.2  | -0.2  |                 | +0.2  |        |

| Input Offset Voltage                                               | 25°C | 1     | -35   | ±10         | +35   | -35   | ± 10            | +35   | -35   | ± 10            | +35   | mV     |

| . 5                                                                | Full | VI    | -40   |             | +40   | -40   |                 | +40   | -40   |                 | +40   | mV     |

| Reference Voltage                                                  | Full | VI    | 1.2   | 1.25        | 1.3   | 1.2   | 1.25            | 1.3   | 1.2   | 1.25            | 1.3   | v      |

| Reference Tempco                                                   | Full | VI    |       | ±130        |       |       | ±130            |       |       | ± 130           |       | ppm/   |

| Input Resistance                                                   | 25°C | 1     | 7     | 10          | 13    | 7     | 10              | 13    | 7     | 10              | 13    | kΩ     |

| mparmentance                                                       | Full | VI    | 5     | 10          | 16    | 5     |                 | 16    | 5     |                 | 16    |        |

| Input Capacitance                                                  | 25°C | v     | 5     | 2           | 10    | 5     | 2               | 10    | 5     | 2               | 10    | pF     |

| Analog Bandwidth, Full                                             | 25°C | v     |       | 475         |       |       | 475             |       |       | 475             |       | MHz    |

| Power                                                              | 25 0 | ľ     |       | 475         |       |       | -17 <b>5</b>    |       |       | 475             |       | 111112 |

| SWITCHING PERFORMANCE                                              |      |       |       |             |       |       |                 |       |       |                 |       |        |

| Maximum Conversion Rate                                            | Full | VI    | 100   |             |       | 80    |                 |       | 40    |                 |       | MSPS   |

| Minimum Conversion Rate                                            | 25°C | IV    |       |             | 1     |       |                 | 1     |       |                 | 1     | MSPS   |

| Encode Pulse Width High (t <sub>EH</sub> )                         | 25°C | IV    | 4.3   |             | 1000  | 5.0   |                 | 1000  | 8.0   |                 | 1000  | ns     |

| Encode Pulse Width Low $(t_{EL})$                                  | 25°C | IV    | 4.3   |             | 1000  | 5.0   |                 | 1000  | 8.0   |                 | 1000  | ns     |

| Aperture Delay $(t_A)$                                             | 25°C | V     | ч.5   | 300         | 1000  | 5.0   | 300             | 1000  | 0.0   | 300             | 1000  | ps     |

| Aperture Uncertainty (Jitter)                                      | 25°C | v     |       | 5           |       |       | 5               |       |       | 5               |       |        |

| Output Valid Time (t <sub>v</sub> ) <sup>2</sup>                   | Full | VI    | 2     | 3.0         |       | 2     | 3.0             |       | 2     | 3.0             |       | ps rm  |

| Output Valid Time (tv) <sup>-</sup><br>Output Propagation Delay    |      | VI    | 2     |             | 6.0   | 2     |                 | 6.0   | 2     |                 | 6.0   | ns     |

| (t <sub>PD</sub> ) <sup>2</sup>                                    | Full | VI    |       | 4.5         | 6.0   |       | 4.5             | 6.0   |       | 4.5             | 6.0   | ns     |

|                                                                    |      |       |       |             |       |       |                 |       |       |                 |       |        |

| Logic 1 Voltage                                                    | Full | VI    | 2.0   |             |       | 2.0   |                 |       | 2.0   |                 |       | v      |

| Logic 1 Voltage                                                    | Full | VI    | 2.0   |             | 0.8   | 2.0   |                 | 0.8   | 2.0   |                 | 0.8   | v      |

| 5 5                                                                | Full | VI    |       |             |       |       |                 |       |       |                 |       |        |

| Logic 1 Current                                                    |      | VI    |       |             | ±1    |       |                 | ±1    |       |                 | ±1    | μA     |

| Logic 0 Current                                                    | Full |       |       | 2.0         | ±1    |       | 2.0             | ± 1   |       | 2.0             | ± 1   | μA     |

| Input Capacitance                                                  | 25°C | V     |       | 2.0         |       |       | 2.0             |       |       | 2.0             |       | pF     |

| DIGITAL OUTPUTS <sup>3</sup>                                       |      |       |       |             |       |       |                 |       |       |                 |       |        |

| Logic 1 Voltage                                                    | Full | VI    | 2.45  |             |       | 2.45  |                 |       | 2.45  |                 |       | V      |

| Logic 0 Voltage                                                    | Full | VI    |       |             | 0.05  | L     |                 | 0.05  | ļ     |                 | 0.05  | V      |

| POWER SUPPLY                                                       |      |       |       |             |       |       |                 |       |       |                 |       |        |

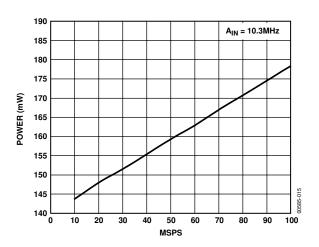

| Power Dissipation <sup>4</sup>                                     | Full | VI    |       | 180         | 218   |       | 171             | 207   |       | 156             | 189   | mW     |

| Standby Dissipation <sup>4, 5</sup>                                | Full | VI    |       | 6           | 11    |       | 6               | 11    |       | 6               | 11    | mW     |

| Power Supply Rejection<br>Ratio (PSRR)                             | 25°C | I     |       | 8           | 20    |       | 8               | 20    |       | 8               | 20    | mV/V   |

|                                                    |      | Test  |     | AD9288BST | -100 |     | AD9288BS | T-80 |     | AD9288BS | Г-40 |      |

|----------------------------------------------------|------|-------|-----|-----------|------|-----|----------|------|-----|----------|------|------|

| Parameter                                          | Temp | Level | Min | Тур       | Max  | Min | Тур      | Max  | Min | Тур      | Max  | Unit |

| DYNAMIC PERFORMANCE <sup>6</sup>                   |      |       |     |           |      |     |          |      |     |          |      |      |

| Transient Response                                 | 25°C | V     |     | 2         |      |     | 2        |      |     | 2        |      | ns   |

| Overvoltage Recovery Time                          | 25°C | V     |     | 2         |      |     | 2        |      |     | 2        |      | ns   |

| Signal-to-Noise Ratio (SNR)<br>(without Harmonics) |      |       |     |           |      |     |          |      |     |          |      |      |

| $f_{IN} = 10.3 \text{ MHz}$                        | 25°C | 1     |     | 47.5      |      |     | 47.5     |      | 44  | 47.5     | dB   |      |

| $fI_N = 26 MHz$                                    | 25°C | 1     |     | 47.5      |      | 44  | 47       |      |     |          | dB   |      |

| $f_{IN} = 41 \text{ MHz}$                          | 25°C | 1     | 44  | 47.0      |      |     |          |      |     |          | dB   |      |

| Signal-to-Noise Ratio<br>(SINAD) (with Harmonics)  |      |       |     |           |      |     |          |      |     |          |      |      |

| $f_{IN} = 10.3 \text{ MHz}$                        | 25°C | 1     |     | 47        |      |     | 47       |      | 44  | 47       |      | dB   |

| $f_{IN} = 26 \text{ MHz}$                          | 25°C | 1     |     | 47        |      | 44  | 47       |      |     |          |      | dB   |

| $f_{IN} = 41 \text{ MHz}$                          | 25°C | 1     | 44  | 47        |      |     | 47       |      |     |          |      | dB   |

| Effective Number of Bits                           |      |       |     |           |      |     |          |      |     |          |      |      |

| $f_{IN} = 10.3 \text{ MHz}$                        | 25°C | 1     |     | 7.5       |      |     | 7.5      |      | 7.0 | 7.5      |      | Bits |

| $f_{IN} = 26 \text{ MHz}$                          | 25°C | 1     |     | 7.5       |      | 7.0 | 7.5      |      |     |          |      | Bits |

| $f_{IN} = 41 \text{ MHz}$                          | 25°C | 1     | 7.0 | 7.5       |      |     | 7.5      |      |     |          |      | Bits |

| Second Harmonic Distortion                         |      |       |     |           |      |     |          |      |     |          |      |      |

| $f_{IN} = 10.3 \text{ MHz}$                        | 25°C | 1     |     | 70        |      |     | 70       |      | 55  | 70       |      | dBc  |

| $f_{IN} = 26 \text{ MHz}$                          | 25°C | 1     |     | 70        |      | 55  | 70       |      |     |          |      | dBc  |

| $f_{IN} = 41 \text{ MHz}$                          | 25°C | 1     | 55  | 70        |      |     | 70       |      |     |          |      | dBc  |

| Third Harmonic Distortion                          |      |       |     |           |      |     |          |      |     |          |      |      |

| $f_{IN} = 10.3 \text{ MHz}$                        | 25°C | 1     |     | 60        |      |     | 60       |      | 55  | 60       |      | dBc  |

| $f_{IN} = 26 \text{ MHz}$                          | 25°C | 1     |     | 60        |      | 55  | 60       |      |     |          |      | dBc  |

| $f_{IN} = 41 \text{ MHz}$                          | 25°C | 1     | 52  | 60        |      | 1   | 60       |      |     |          |      | dBc  |

| Two-Tone Intermod<br>Distortion (IMD)              |      |       |     |           |      |     |          |      |     |          |      |      |

| $f_{IN} = 10.3 \text{ MHz}$                        | 25°C | v     | 1   | 60        |      | 1   | 60       |      | 60  |          |      | dBc  |

<sup>1</sup> Gain error and gain temperature coefficient are based on the ADC only (with a fixed 1.25 V external reference). <sup>2</sup> t<sub>v</sub> and t<sub>PD</sub> are measured from the 1.5 V level of the Encode input to the 10%/90% levels of the digital outputs swing. The digital output load during test is not to exceed an ac load of 10 pF or a dc current of  $\pm 40~\mu A.$

<sup>3</sup> Digital supply current based on  $V_{DD}$  = 3.0 V output drive with < 10 pF loading under dynamic test conditions. <sup>4</sup> Power dissipation measured under the following conditions:  $f_s$  = 100 MSPS, analog input is -0.7 dBFS, both channels in operation.

<sup>5</sup> Standby dissipation calculated with Encode clock in operation.

### **EXPLANATION OF TEST LEVELS**

| Level | Description                                                                                                                                                                              |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| I     | 100% production tested.                                                                                                                                                                  |

| II    | 100% production tested at 25°C and sample tested at specified temperatures.                                                                                                              |

| III   | Sample tested only.                                                                                                                                                                      |

| IV    | Parameter is guaranteed by design and characterization testing.                                                                                                                          |

| V     | Parameter is a typical value only.                                                                                                                                                       |

| VI    | 100% production tested at 25°C; guaranteed by design and characterization testing for industrial temperature range; 100% production tested at temperature extremes for military devices. |

<sup>&</sup>lt;sup>6</sup> SNR/harmonics based on an analog input voltage of -0.7 dBFS referenced to a 1.024 V full-scale input range.

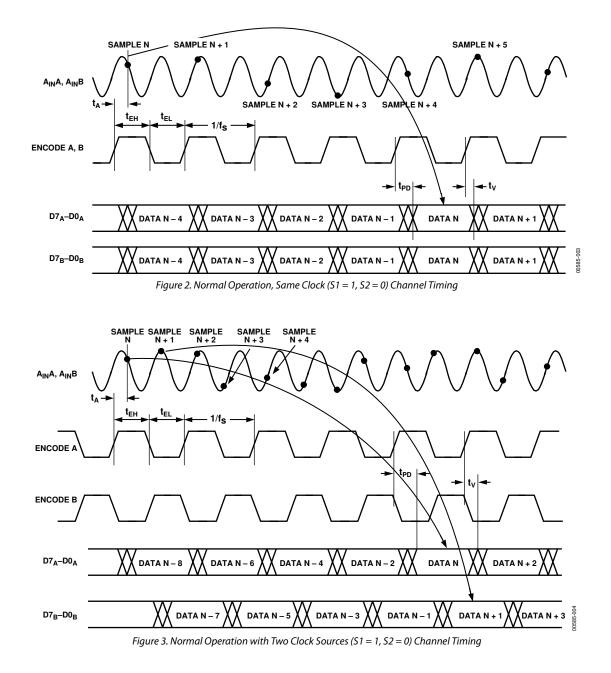

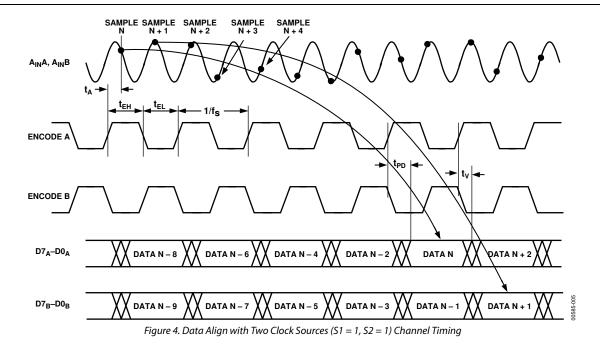

### **TIMING DIAGRAMS**

# **ABSOLUTE MAXIMUM RATINGS**

### Table 2.

| Parameter                        | Rating                            |

|----------------------------------|-----------------------------------|

| V <sub>D</sub> , V <sub>DD</sub> | 4 V                               |

| Analog Inputs                    | -0.5 V to V <sub>D</sub> + 0.5 V  |

| Digital Inputs                   | -0.5 V to V <sub>DD</sub> + 0.5 V |

| VREF IN                          | -0.5 V to V <sub>D</sub> + 0.5 V  |

| Digital Output Current           | 20 mA                             |

| Operating Temperature            | –55°C to +125°C                   |

| Storage Temperature              | –65°C to +150°C                   |

| Maximum Junction Temperature     | 150°C                             |

| Maximum Case Temperature         | 150°C                             |

| Thermal Impedance $\theta_{ja}$  | 57°C/W                            |

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions outside of those indicated in the operation sections of this specification is not implied. Exposure to absolute maximum ratings for extended periods may affect device reliability.

### **ESD CAUTION**

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although this product features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

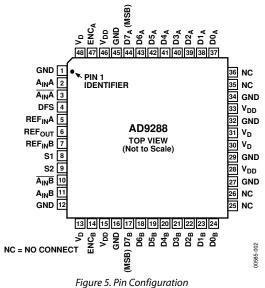

# **PIN CONFIGURATION AND FUNCTION DESCRIPTIONS**

Table 3.

| Pin No.            | Name                             | Description                                                                                                  |

|--------------------|----------------------------------|--------------------------------------------------------------------------------------------------------------|

| 1, 12, 16, 27, 29, | GND                              | Ground                                                                                                       |

| 32, 34, 45         |                                  |                                                                                                              |

| 2                  | AinA                             | Analog Input for Channel A.                                                                                  |

| 3                  | AINA                             | Analog Input for Channel A (Complementary).                                                                  |

| 4                  | DFS                              | Data Format Select. Offset binary output available if set low. Twos complement output available if set high. |

| 5                  | REFINA                           | Reference Voltage Input for Channel A.                                                                       |

| 6                  | REFOUT                           | Internal Reference Voltage.                                                                                  |

| 7                  | REFINB                           | Reference Voltage Input for Channel B.                                                                       |

| 8                  | S1                               | User Select 1. Refer to Table 4. Tied with respect to $V_D$ .                                                |

| 9                  | S2                               | User Select 2. Refer to Table 4. Tied with respect to $V_D$ .                                                |

| 10                 | AINB                             | Analog Input for Channel B (Complementary).                                                                  |

| 11                 | AINB                             | Analog Input for Channel B.                                                                                  |

| 13, 30, 31, 48     | VD                               | Analog Supply (3 V).                                                                                         |

| 14                 | ENCB                             | Clock Input for Channel B.                                                                                   |

| 15, 28, 33, 46     | V <sub>DD</sub>                  | Digital Supply (3 V).                                                                                        |

| 17–24              | D7 <sub>B</sub> -D0 <sub>B</sub> | Digital Output for Channel B.                                                                                |

| 25, 26, 35, 36     | NC                               | Do Not Connect.                                                                                              |

| 37–44              | D0 <sub>A</sub> -D7 <sub>A</sub> | Digital Output for Channel A.                                                                                |

| 47                 | ENC A                            | Clock Input for Channel A.                                                                                   |

# **TYPICAL PERFORMANCE CHARACTERISTICS**

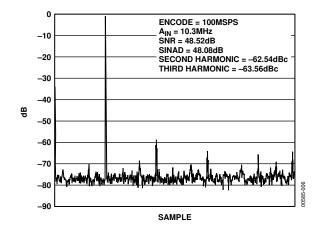

Figure 6. Spectrum:  $f_s = 100 \text{ MSPS}$ ,  $f_{IN} = 10 \text{ MHz}$ , Single-Ended Input

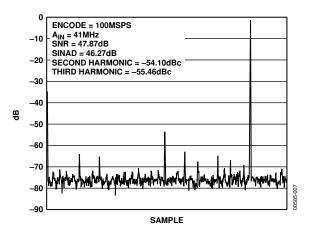

Figure 7. Spectrum:  $f_S = 100$  MSPS,  $f_{IN} = 41$  MHz, Single-Ended Input

Figure 8. Spectrum:  $f_s = 100$  MSPS,  $f_{IN} = 76$  MHz, Single-Ended Input

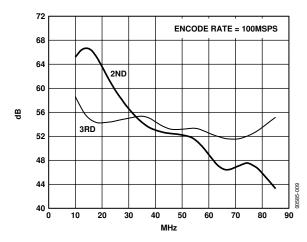

Figure 9. Harmonic Distortion vs. A<sub>IN</sub> Frequency

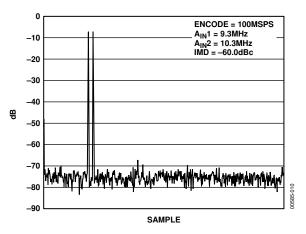

*Figure 10. Two-Tone Intermodulation Distortion*

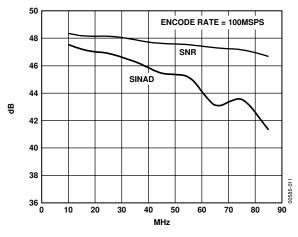

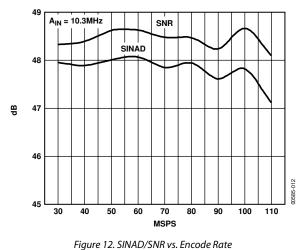

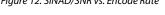

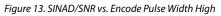

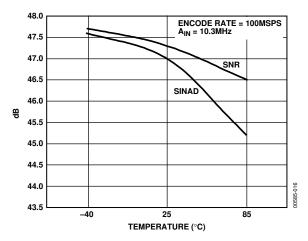

Figure 11. SINAD/SNR vs. AIN Frequency

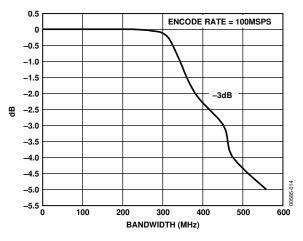

Figure 14. ADC Frequency Response:  $f_s = 100 \text{ MSPS}$

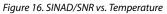

Figure 17. ADC Gain vs. Temperature (with External 1.25 V Reference)

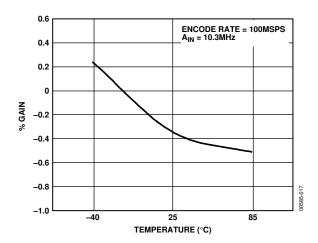

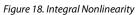

Figure 19. Differential Nonlinearity

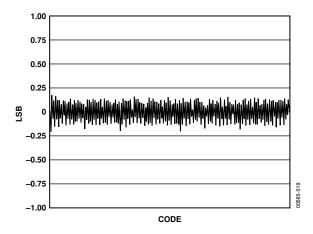

Figure 20. Voltage Reference Out vs. Current Load

# **TEST CIRCUITS**

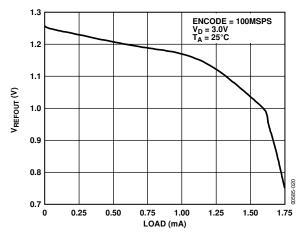

Figure 21. Equivalent Analog Input Circuit

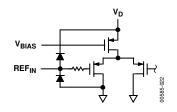

Figure 22. Equivalent Reference Input Circuit

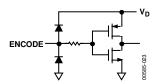

Figure 23. Equivalent Encode Input Circuit

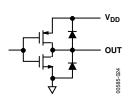

Figure 24. Equivalent Digital Output Circuit

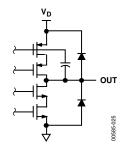

Figure 25. Equivalent Reference Output Circuit

## TERMINOLOGY

### Analog Bandwidth (Small Signal)

The analog input frequency at which the spectral power of the fundamental frequency (as determined by the FFT analysis) is reduced by 3 dB.

### Aperture Delay

The delay between a 50% crossing of Encode and the instant at which the analog input is sampled.

### Aperture Uncertainty (Jitter)

The sample-to-sample variation in aperture delay.

### **Differential Nonlinearity**

The deviation of any code from an ideal 1 LSB step.

### Encode Pulse Width/Duty Cycle

Pulse width high is the minimum amount of time that the Encode pulse should be left in Logic 1 state to achieve rated performance; pulse width low is the minimum time Encode pulse should be left in low state. At a given clock rate, these specs define an acceptable Encode duty cycle.

### **Integral Nonlinearity**

The deviation of the transfer function from a reference line measured in fractions of 1 LSB using a "best straight line" determined by a least square curve fit.

### **Minimum Conversion Rate**

The Encode rate at which the SNR of the lowest analog signal frequency drops by no more than 3 dB below the guaranteed limit.

### **Maximum Conversion Rate**

The Encode rate at which parametric testing is performed.

### **Output Propagation Delay**

The delay between a 50% crossing of Encode and the time when all output data bits are within valid logic levels.

### **Power Supply Rejection Ratio**

The ratio of a change in input offset voltage to a change in power supply voltage.

### Signal-to-Noise-and-Distortion (SINAD)

The ratio of the rms signal amplitude (set at 1 dB below full scale) to the rms value of the sum of all other spectral components, including harmonics but excluding dc.

### Signal-to-Noise Ratio (SNR)

The ratio of the rms signal amplitude (set at 1 dB below full scale) to the rms value of the sum of all other spectral components, excluding the first five harmonics and dc.

### Spurious-Free Dynamic Range (SFDR)

The ratio of the rms signal amplitude to the rms value of the peak spurious spectral component. The peak spurious component may or may not be a harmonic. May be reported in dBc (i.e., degrades as signal level is lowered), or in dBFS (always related back to converter full scale).

# Two-Tone Intermodulation Distortion Rejection Two-Tone SFDR

The ratio of the rms value of either input tone to the rms value of the peak spurious component. The peak spurious component may or may not be an IMD product. May be reported in dBc (i.e., degrades as signal level is lowered), or in dBFS (always related back to converter full scale).

### Worst Harmonic

The ratio of the rms value of either input tone to the rms value of the worst third order intermodulation product; reported in dBc.

# THEORY OF OPERATION

The AD9288 ADC architecture is a bit-per-stage pipeline-type converter utilizing switch capacitor techniques. These stages determine the 5 MSBs and drive a 3-bit flash. Each stage provides sufficient overlap and error correction, allowing optimization of comparator accuracy. The input buffers are differential, and both sets of inputs are internally biased. This allows the most flexible use of ac or dc and differential or single-ended input modes. The output staging block aligns the data, carries out the error correction, and feeds the data to output buffers. The set of output buffers are powered from a separate supply, allowing adjustment of the output voltage swing. There is no discernible difference in performance between the two channels.

### **USING THE AD9288**

Good high speed design practices must be followed when using the AD9288. To obtain maximum benefit, decoupling capacitors should be physically as close as possible to the chip, minimizing trace and via inductance between chip pins and capacitor (0603 surface-mount capacitors are used on the AD9288/PCB evaluation board). It is recommended to place a 0.1  $\mu$ F capacitor at each power-ground pin pair for high frequency decoupling, and to include one 10  $\mu$ F capacitor for local low frequency decoupling. The VREF IN pin should also be decoupled by a 0.1  $\mu$ F capacitor. It is also recommended to use a split power plane and a contiguous ground plane (see the Evaluation Board section). Data output traces should be short (< 1 inch), minimizing on-chip noise at switching.

### **ENCODE INPUT**

Any high speed A/D converter is extremely sensitive to the quality of the sampling clock provided by the user. A track-andhold circuit is essentially a mixer. Any noise, distortion, or timing jitter on the clock is combined with the desired signal at the A/D output. For that reason, considerable care has been taken in the design of the Encode (Clock) input of the AD9288, and the user is advised to give commensurate thought to the clock source. The Encode input is fully TTL/CMOS-compatible.

### **DIGITAL OUTPUTS**

The digital outputs are TTL/CMOS-compatible for lower power consumption. During standby, the output buffers transition to a high impedance state. A data format selection option supports either twos complement (set high) or offset binary output (set low) formats.

### **ANALOG INPUT**

The analog input to the AD9288 is a differential buffer. For best dynamic performance, impedance at  $A_{IN}$  and  $\overline{A_{IN}}$  should match. Special care was taken in the design of the analog input stage of the AD9288 to prevent damage and corruption of data when

the input is overdriven. The nominal input range is 1.024 V p-p centered at  $V_{\rm D} \times 0.3.$

### **VOLTAGE REFERENCE**

A stable and accurate 1.25 V voltage reference is built into the AD9288 (REF<sub>OUT</sub>). In normal operation, the internal reference is used by strapping Pins 5 (REF<sub>IN</sub>A) and 7 (REF<sub>IN</sub>B) to Pin 6 (REFOUT). The input range can be adjusted by varying the reference voltage applied to the AD9288. No appreciable degradation in performance occurs when the reference is adjusted  $\pm$ 5%. The full-scale range of the ADC tracks reference voltage, which changes linearly.

### TIMING

The AD9288 provides latched data outputs, with four pipeline delays. Data outputs are available one propagation delay ( $t_{PD}$ ) after the rising edge of the Encode command (see Figure 2, Figure 3, and Figure 4). The length of the output data lines and loads placed on them must be minimized to reduce transients within the AD9288. These transients can detract from the converter's dynamic performance.

The minimum guaranteed conversion rate of the AD9288 is 1 MSPS. At clock rates below 1 MSPS, dynamic performance degrades. Typical power-up recovery time after standby mode is 15 clock cycles.

### **USER-SELECTABLE OPTIONS**

Two pins are available for a combination of operational modes. These options allow the user to place both channels, excluding the reference, into standby mode, or just the B channel. Both modes place the output buffers and clock inputs into high impedance states.

The other option allows the user to skew the B channel output data by 1/2 of a clock cycle. In other words, if two clocks are fed to the AD9288 and are 180° out of phase, enabling the data align allows Channel B output data to be available at the rising edge of Clock A. If the same Encode clock is provided to both channels and the data align pin is enabled, then output data from Channel B is 180° out of phase with respect to Channel A. If the same Encode clock is provided to both channels and the data align pin is disabled, both outputs are delivered on the same rising edge of the clock.

Table 4. User-Selectable Options

| <b>S</b> 1 | <b>S</b> 2 | Option                                                                                                                                 |

|------------|------------|----------------------------------------------------------------------------------------------------------------------------------------|

| 0          | 0          | Standby Both Channels A and B.                                                                                                         |

| 0          | 1          | Standby Channel B Only.                                                                                                                |

| 1          | 0          | Normal Operation (Data Align Disabled).                                                                                                |

| 1          | 1          | Data Align Enabled (data from both channels avail-<br>able on rising edge of Clock A. Channel B data is<br>delayed a 1/2 clock cycle). |

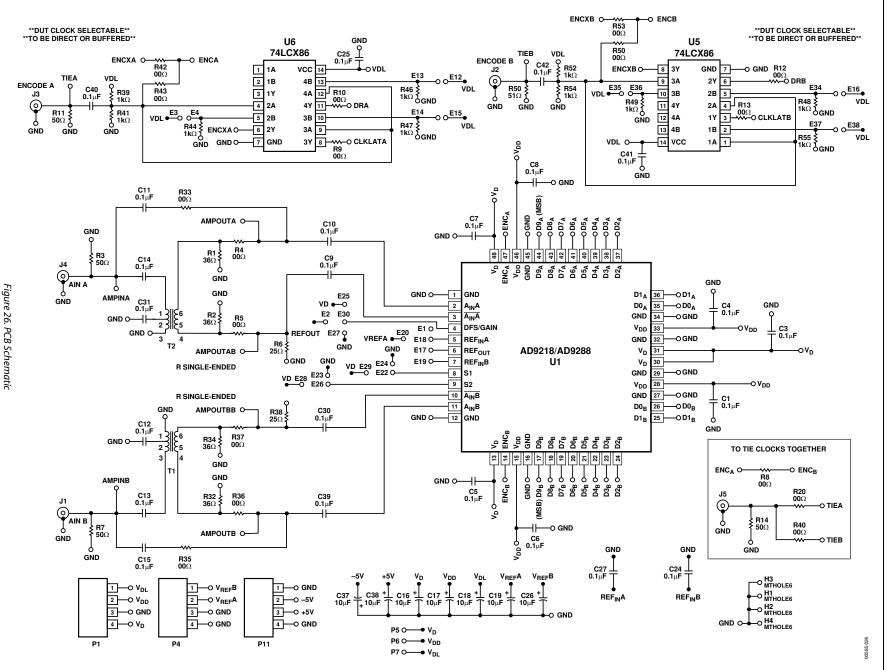

# AD9218/AD9288 CUSTOMER PCB BOM

### Table 5. Bill of Materials

| No. | Qty. | Reference Designator                                                                  | Device                     | Package                 | Value                 | Comments                                      |

|-----|------|---------------------------------------------------------------------------------------|----------------------------|-------------------------|-----------------------|-----------------------------------------------|

| 1   | 29   | C1, C3-C15, C20, C21, C24,<br>C25, C27, C30–C35, C39–C42                              | Capacitor                  | 0603                    | 0.1 μF                |                                               |

| 2   | 2    | C2, C36                                                                               | Capacitor                  | 0603                    | 15 pF                 | 8138 out                                      |

| 3   | 7    | C16–C19, C26, C37, C38                                                                | Capacitor                  | TAJD                    | 10 µF                 |                                               |

| 4   | 28   | E1, E2, E3, E4, E12–E30,<br>E34–E38                                                   | W-HOLE                     | W-HOLE                  |                       |                                               |

| 5   | 4    | H1, H2, H3, H4                                                                        | MTHOLE                     | MTHOLE                  |                       |                                               |

| 6   | 5    | J1, J2, J3, J4, J5                                                                    | SMA                        | SMA                     |                       | J2, J3, not placed                            |

| 7   | 3    | P1, P4, P11                                                                           | 4-pin power connector      | Post                    | Z5.531.3425.0         | Wieland                                       |

| 8   | 3    | P1, P4, P11                                                                           | 4-pin power connector      | Detachable<br>Connector | 25.602.5453.0         | Wieland                                       |

| 9   | 1    | P2, P3 <sup>1</sup>                                                                   | 80-pin rt. angle male      |                         | TSW-140-08-<br>L-D-RA | Samtec                                        |

| 10  | 4    | R1, R2, R32, R34                                                                      | Resistor                   | 0603                    | 36 Ω                  | R1, R2, R32, R34,<br>not placed               |

| 11  | 9    | R3, R7, R11, R14, R22, R23,<br>R24, R30, R51                                          | Resistor                   | 0603                    | 50 Ω                  | R11, R22, R23,<br>R24, R30, R51<br>not placed |

| 12  | 17   | R4, R5, R8, R9, R10, R12, R13,<br>R20, R33, R35, R36, R37, R40,<br>R42, R43, R50, R53 | Resistor                   | 0603                    | Zero Ω                | R43, R50<br>not placed                        |

| 13  | 2    | R6, R38                                                                               | Resistor                   | 0603                    | 25 Ω                  | R6, R38<br>not placed                         |

| 14  | 6    | R15, R16, R18, R26, R29, R31                                                          | Resistor                   | 0603                    | 500 Ω                 | R16, R29<br>not placed                        |

| 15  | 2    | R17, R25                                                                              | Resistor                   | 0603                    | 525 Ω                 |                                               |

| 16  | 2    | R19, R27                                                                              | Resistor                   | 0603                    | 4 kΩ                  |                                               |

| 17  | 12   | R21, R28, R39, R41, R44,<br>R46–R49, R52, R54, R55                                    | Resistor                   | 0603                    | 1 kΩ                  |                                               |

| 18  | 2    | T1, T2                                                                                | Transformer                | ADT1-1WT                |                       | Minicircuits                                  |

| 19  | 1    | U1                                                                                    | AD9288 <sup>2</sup>        | LQFP48                  |                       |                                               |

| 20  | 2    | U2, U3                                                                                | 74LCX821                   |                         |                       |                                               |

| 21  | 2    | U5, U6                                                                                | SN74VCX86                  |                         |                       |                                               |

| 22  | 4    | U7, U8, U9, U10                                                                       | Resistor array             | СТЅ                     | 47 Ω                  | 768203470G                                    |

| 23  | 2    | U11, U12                                                                              | AD8138 op amp <sup>3</sup> |                         |                       |                                               |

P2, P3 are implemented as one physical 80-pin connector SAMTEC TSW-140-08-L-D-RA.

AD9288/PCB populated with AD9288-100.

To use optional amp: place R22, R23, R30, R24, R16, R29, remove R4, R36.

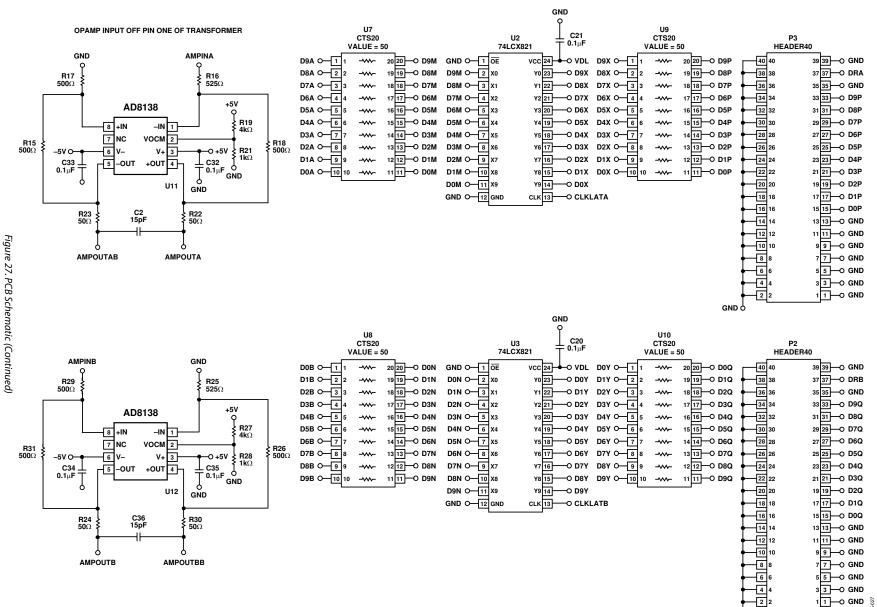

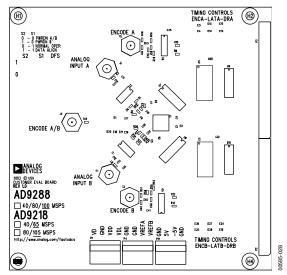

# **EVALUATION BOARD**

The AD9218/AD9288 customer evaluation board offers an easy way to test the AD9218 or the AD9288. The compatible pinout of the two parts facilitates the use of one PCB for testing either part. The PCB requires power supplies, a clock source, and a filtered analog source for most ADC testing required.

### **POWER CONNECTOR**

Power is supplied to the board via a detachable 12-lead power strip. The minimum 3 V supplies required to run the board are  $V_{DD}$ ,  $V_{DL}$ , and  $V_{DD}$ . To allow the use of the optional amplifier path,  $\pm 5$  V supplies are required.

### **ANALOG INPUTS**

Each channel has an independent analog path that uses a wideband transformer to drive the ADC differentially from a single-ended sine source at the input SMAs. The transformer paths can be bypassed to allow the use of a dc-coupled path by using two AD8138 op amps with a simple board modification. The analog input should be band-pass filtered to remove any harmonics in the input signal and to minimize aliasing.

### **VOLTAGE REFERENCE**

The AD9288 has an internal 1.25 V voltage reference; an external reference for each channel can be used instead by connecting two external voltage references at the power connector and setting jumpers at E18 and E19. The evaluation board is shipped configured for internal reference mode.

### CLOCKING

Each channel can be clocked by a common clock input at SMA input ENCODE A/B. The channels can also be clocked independently by a simple board modification. The clock input should be a low jitter sine source for maximum performance.

### DATA OUTPUTS

The data outputs are latched on-board by two 10-bit latches and drive an 8-pin connector which is compatible with the dualchannel FIFO board available from Analog Devices. This board, together with ADC analyzer software, can greatly simplify ADC testing.

### DATA FORMAT/GAIN

The DFS/Gain pin can be biased for desired operation at the DFS jumper located at the S1, S2 jumpers.

### TIMING

Timing on each channel can be controlled if needed on the PCB. Clock signals at the latches or the data ready signals that go to the output 80-pin connector can be inverted if required. Jumpers also allow for biasing of Pins S1 and S2 for power-down and timing alignment control.

Rev. C | Page 17 of 24

# AD9288

Rev. C | Page 18 of 24

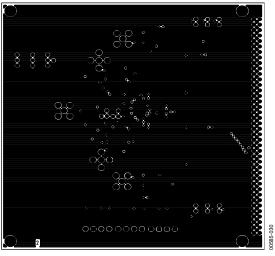

Figure 28. Top Silkscreen

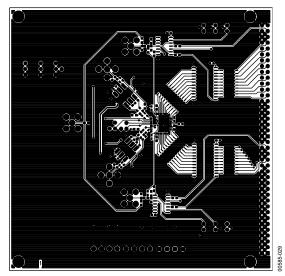

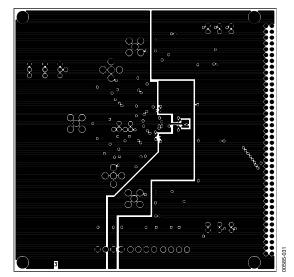

Figure 29. Top Routing

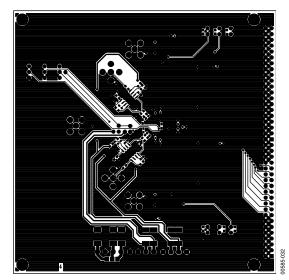

Figure 30. Ground Plane

Figure 31. Split Power Plane

Figure 32. Bottom Routing

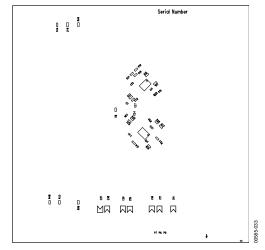

Figure 33. Bottom Silkscreen

### TROUBLESHOOTING

If the board does not seem to be working correctly, try the following:

- Verify power at the IC pins.

- Check that all jumpers are in the correct position for the desired mode of operation.

- Verify that V<sub>REF</sub> is at 1.23 V.

- Try running Encode clock and analog inputs at low speeds (20 MSPS/1 MHz) and monitor LCX821 outputs, DAC outputs, and ADC outputs for toggling.

The AD9218/AD9288 evaluation board is provided as a design example for customers of Analog Devices, Inc. ADI makes no warranties, express, statutory, or implied, regarding merchantability or fitness for a particular purpose.

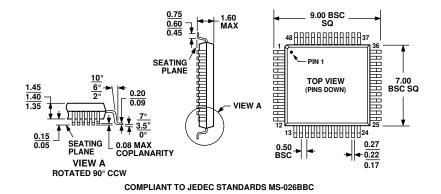

# **OUTLINE DIMENSIONS**

Figure 34. 48-Lead Low Profile Quad Flat Package [LQFP] (ST-48) Dimensions shown in millimeters

### **ORDERING GUIDE**

| Model                        | Temperature Range | Package Description                   | Package Options |

|------------------------------|-------------------|---------------------------------------|-----------------|

| AD9288BST-40                 | -40°C to +85°C    | 48-Lead Low Profile Quad Flat Package | ST-48           |

| AD9288BSTZ-401               | -40°C to +85°C    | 48-Lead Low Profile Quad Flat Package | ST-48           |

| AD9288BSTZRL-40 <sup>1</sup> | –40°C to +85°C    | 48-Lead Low Profile Quad Flat Package | ST-48           |

| AD9288BST-80                 | -40°C to +85°C    | 48-Lead Low Profile Quad Flat Package | ST-48           |

| AD9288BSTZ-801               | –40°C to +85°C    | 48-Lead Low Profile Quad Flat Package | ST-48           |

| AD9288BST-100                | –40°C to +85°C    | 48-Lead Low Profile Quad Flat Package | ST-48           |

| AD9288BSTZ-1001              | -40°C to +85°C    | 48-Lead Low Profile Quad Flat Package | ST-48           |

| AD9288/PCB                   |                   | Evaluation Board                      |                 |

$^{1}$  Z = Pb-free part.

# NOTES

# NOTES

# NOTES

www.analog.com

© 2004 Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective owners. C00585–0–12/04(C)

Rev. C | Page 24 of 24