Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# Mixed-Signal Front End Set-Top Box, Cable Modem

AD9879

### **FEATURES**

Low cost 3.3 V MxFE™ for DOCSIS-, EURO-DOCSIS-, DVB-, DAVIC-compliant set-top box and cable modem applications 232 MHz quadrature digital upconverter 12-bit direct IF DAC (TxDAC+™) Up to 65 MHz carrier frequency DDS **Programmable sampling clock rates** 16× upsampling interpolation LPF Single-tone frequency synthesis Analog Tx output level adjust Direct cable amp interface 12-bit, 33 MSPS direct IF ADC with optional video clamping input 10-bit, 33 MSPS direct IF ADC Dual 7-bit, 16.5 MSPS sampling I/Q ADC 12-bit Σ-Δ auxiliary DAC

### **APPLICATIONS**

Cable modem and satellite systems

Set-top boxes

Power line modem

PC multimedia

Digital communications

Data and video modems

QAM, OFDM, FSK modulation

### **GENERAL DESCRIPTION**

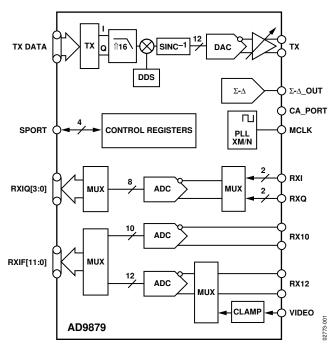

The AD9879 is a single-supply set-top box and cable modem mixed-signal front end. The device contains a transmit path interpolation filter, complete quadrature digital upconverter, and transmit DAC. The receive path contains a 12-bit ADC, a 10-bit ADC, and dual 7-bit ADCs. All internally required clocks and an output system clock are generated by the phase-locked loop (PLL) from a single crystal or clock input.

The transmit path interpolation filter provides an upsampling factor of 16× with an output signal bandwidth as high as 8.3 MHz. Carrier frequencies up to 65 MHz with 26 bits of frequency tuning resolution can be generated by the direct digital synthesizer (DDS). The transmit DAC resolution is 12 bits and can run at sampling rates as high as 232 MSPS. Analog output scaling from 0.0 dB to 7.5 dB in 0.5 dB steps is available to preserve SNR when reduced output levels are required.

### Rev. A

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

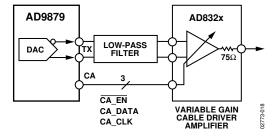

#### **FUNCTIONAL BLOCK DIAGRAM**

Figure 1.

The 12-bit and 10-bit IF ADCs can convert direct IF inputs up to 70 MHz and run at sample rates up to 33 MSPS. A video input with an adjustable signal clamping level, along with the 10-bit ADC, allow the AD9879 to process an NTSC and a QAM channel simultaneously.

The programmable  $\Sigma$ - $\Delta$  DAC can be used to control external components, such as variable gain amplifiers (VGAs) or voltage controlled tuners. The CA port provides an interface to the AD8321/AD8323 or AD8322/AD8327 programmable gain amplifier (PGA) cable drivers, enabling host processor control via the MxFE SPORT.

The AD9879 is available in a 100-lead MQFP. It offers enhanced receive path undersampling performance and lower cost when compared with the pin-compatible AD9873. The AD9879 is specified over the commercial ( $-40^{\circ}$ C to  $+85^{\circ}$ C) temperature range.

## **AD9879\* PRODUCT PAGE QUICK LINKS**

Last Content Update: 02/23/2017

## COMPARABLE PARTS 🖳

View a parametric search of comparable parts.

## **EVALUATION KITS**

· AD9879 Evaluation Board

## **DOCUMENTATION**

### **Application Notes**

• AN-237: Choosing DACs for Direct Digital Synthesis

### **Data Sheet**

AD9879: Mixed Signal Front End Set Top Box, Cable Modem Data Sheet

### REFERENCE MATERIALS -

### Informational

Advantiv<sup>™</sup> Advanced TV Solutions

### **Technical Articles**

- High Integration Simplifies Signal Processing For CCDs

- MS-2210: Designing Power Supplies for High Speed ADC

### **DESIGN RESOURCES**

- · AD9879 Material Declaration

- PCN-PDN Information

- · Quality And Reliability

- Symbols and Footprints

### **DISCUSSIONS**

View all AD9879 EngineerZone Discussions.

## SAMPLE AND BUY 🖵

Visit the product page to see pricing options.

## **TECHNICAL SUPPORT**

Submit a technical question or find your regional support number.

### DOCUMENT FEEDBACK 🖳

Submit feedback for this data sheet.

## **TABLE OF CONTENTS**

| Specifications                                                   |

|------------------------------------------------------------------|

| Absolute Maximum Ratings                                         |

| Explanation of Test Levels                                       |

| Thermal Characteristics                                          |

| ESD Caution                                                      |

| Pin Configuration and Function Descriptions8                     |

| Terminology10                                                    |

| Theory of Operation11                                            |

| Transmit Path11                                                  |

| Data Assembler11                                                 |

| Interpolation Filter                                             |

| Digital Upconverter12                                            |

| DPLL-A Clock Distribution12                                      |

| Clock and Oscillator Circuitry                                   |

| Programmable Clock Output REFCLK13                               |

| Reset and Transmit Power-Down                                    |

| $\Sigma$ - $\Delta$ Outputs                                      |

| Register Map and Bit Definitions16                               |

| Register 0x00—Initialization                                     |

| Register 0x01—Clock Configuration                                |

| Register 0x02—Power-Down17                                       |

| Registers $0x03$ – $0x04$ — $\Sigma$ - $\Delta$ and Flag Control |

| Register 0x07—Video Input Configuration                          |

| Register 0x08—ADC Clock Configuration                            |

| Register 0x0C—Die Revision                                       |

| Register 0x0D—Tx Frequency Tuning Words LSBs 18                  |

| Register 0x0E—DAC Gain Control                                   |

| Register 0x0F—Tx Path Configuration18                            |

| Registers 0x10-0x17—Carrier Frequency Tuning 19                  |

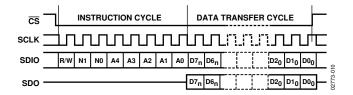

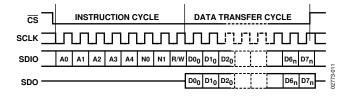

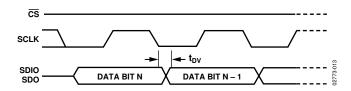

| Serial Interface for Register Control20                                            |

|------------------------------------------------------------------------------------|

| General Operation of the Serial Interface                                          |

| Instruction Byte                                                                   |

| Serial Interface Port Pin Description                                              |

| MSB/LSB Transfers                                                                  |

| Notes on Serial Port Operation                                                     |

| Transmit Path (Tx)                                                                 |

| Transmit Timing                                                                    |

| Data Assembler                                                                     |

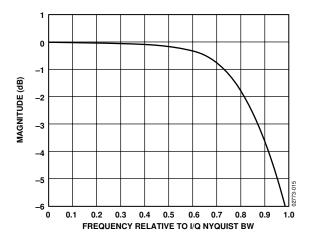

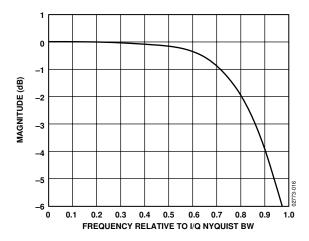

| Half-Band Filters (HBFs)                                                           |

| Cascaded Integrator-Comb (CIC) Filter                                              |

| Combined Filter Response                                                           |

| Tx Signal Level Considerations                                                     |

| Tx Throughput and Latency24                                                        |

| Digital-to-Analog Converter                                                        |

| Programming the AD8321/AD8323 or AD8322/AD8327 Cable Driver Amplifier Gain Control |

| Receive Path (Rx)                                                                  |

| IF10 and IF12 ADC Operation27                                                      |

| Input Signal Range and Digital Output Codes27                                      |

| Driving the Inputs                                                                 |

| PCB Design Considerations                                                          |

| Component Placement                                                                |

| Power Planes and Decoupling28                                                      |

| Ground Planes                                                                      |

| Signal Routing                                                                     |

| Outline Dimensions                                                                 |

| Ordering Guide                                                                     |

### **REVISION HISTORY**

### 6/05—Rev. 0 to Rev. A

| Updated Format                    | Universal |

|-----------------------------------|-----------|

| Changed OSCOUT to REFCLK          | Universal |

| Changed REF CLK to REFCLK         | Universal |

| Changes to Specifications Section | 4         |

| Changes to Figure 13              | 21        |

| Changes to Equation 18            | 24        |

| Changes to Equation 21            | 24        |

| Changes to Outline Dimensions     | 30        |

| Changes to Ordering Guide         | 30        |

### 8/02—Revision 0: Initial Version

## **SPECIFICATIONS**

$V_{AS} = 3.3~V~\pm~5\%, V_{DS} = 3.3~V~\pm~10\%, f_{OSCIN} = 27~MHz, f_{SYSCLK} = 216~MHz, f_{MCLK} = 54~MHz~(M=8), ADC~clock~from~OSCIN, R_{SET} = 4.02~k\Omega, 75~\Omega~DAC~load, unless otherwise noted.$

Table 1.

| Parameter                                                                 | Temp | Test Level | Min  | Тур    | Max   | Unit       |

|---------------------------------------------------------------------------|------|------------|------|--------|-------|------------|

| OSCIN AND XTAL CHARACTERISTICS                                            |      |            |      |        |       |            |

| Frequency Range                                                           | Full | II         | 3    |        | 29    | MHz        |

| Duty Cycle                                                                | Full | II         | 35   | 50     | 65    | %          |

| Input Impedance                                                           | 25°C | III        |      | 100  3 |       | MΩ  pF     |

| MCLK Cycle to Cycle Jitter                                                | 25°C | III        |      | 6      |       | ps rms     |

| Tx DAC CHARACTERISTICS                                                    |      |            |      |        |       |            |

| Resolution                                                                | N/A  | N/A        |      | 12     |       | Bits       |

| Maximum Sample Rate                                                       | Full | II         | 232  |        |       | MHz        |

| Full-Scale Output Current                                                 | Full | II         | 4    | 10     | 20    | mA         |

| Gain Error (Using Internal Reference)                                     | 25°C | 1          | -2.0 | -1.0   | +2.0  | % FS       |

| Offset Error                                                              | 25°C | 1          |      | ±1.0   |       | % FS       |

| Reference Voltage (REFIO Level)                                           | 25°C | 1          | 1.18 | 1.23   | 1.28  | V          |

| Differential Nonlinearity (DNL)                                           | 25°C | III        |      | ±2.5   |       | LSB        |

| Integral Nonlinearity (INL)                                               | 25°C | III        |      | ±8     |       | LSB        |

| Output Capacitance                                                        | 25°C | III        |      | 5      |       | pF         |

| Phase Noise @ 1 kHz Offset, 42 MHz                                        |      |            |      |        |       |            |

| Crystal and OSCIN Multiplier Enabled at 16×                               | 25°C | III        |      | -110   |       | dBc/Hz     |

| Output Voltage Compliance Range                                           | Full | II         | -0.5 |        | +1.5  | V          |

| Wideband SFDR                                                             |      |            |      |        |       |            |

| 5 MHz Analog Out, I <sub>OUT</sub> = 10 mA                                | Full | III        | 60.8 | 66.9   |       | dBc        |

| 65 MHz Analog Out, I <sub>OUT</sub> = 10 mA                               | Full | III        | 44.0 | 46.2   |       | dBc        |

| Narrow-band SFDR (±1 MHz Window)                                          |      |            |      |        |       |            |

| 5 MHz Analog Out, I <sub>OUT</sub> = 10 mA                                | Full | III        | 65.4 | 72.3   |       | dBc        |

| Tx MODULATOR CHARACTERISTICS                                              |      |            |      |        |       |            |

| I/Q Offset                                                                | Full | II         | 50   | 55     |       | dB         |

| Pass-Band Amplitude Ripple (f < fiQCLK/8)                                 | Full | II         |      |        | ±0.1  | dB         |

| Pass-Band Amplitude Ripple (f < f <sub>IQCLK</sub> /4)                    | Full | II         |      |        | ±0.5  | dB         |

| Stop-Band Response (f > $f_{IQCLK} \times 3/4$ )                          | Full | II         |      |        | -63   | dB         |

| Tx GAIN CONTROL                                                           |      |            |      |        |       |            |

| Gain Step Size                                                            | 25°C | III        |      | 0.5    |       | dB         |

| Gain Step Error                                                           | 25°C | III        |      | < 0.05 |       | dB         |

| Settling Time to 1% (Full-Scale Step)                                     | 25°C | III        |      | 1.8    |       | μs         |

| IQ ADC CHARACTERISTICS                                                    |      |            |      |        |       |            |

| Resolution <sup>1</sup>                                                   | N/A  | N/A        |      | 6      |       | Bits       |

| Maximum Conversion Rate                                                   | Full | II         | 14.5 |        |       | MHz        |

| Pipeline Delay                                                            | N/A  | N/A        |      | 3.5    |       | ADC cycles |

| Offset Matching Between I and Q ADCs                                      | Full | III        |      | ±4.0   |       | LSBs       |

| Gain Matching Between I and Q ADCs                                        | Full | III        |      | ±2.0   |       | LSBs       |

| Analog Input                                                              |      |            |      |        |       |            |

| Input Voltage Range <sup>1</sup>                                          | Full | III        |      | 1      |       | Vppd       |

| Input Capacitance                                                         | 25°C | III        |      | 2.0    |       | pF         |

| Differential Input Resistance                                             | 25°C | III        |      | 4      |       | kΩ         |

| AC Performance ( $A_{IN} = 0.5 \text{ dBFS}$ , $f_{IN} = 5 \text{ MHz}$ ) | 1    |            |      |        |       |            |

| Effective Number of Bits (ENOB)                                           | 25°C | 1          | 5.00 | 5.8    |       | Bits       |

| Signal-to-Noise Ratio (SNR)                                               | 25°C | 1          | 34.7 | 36.5   |       | dB         |

| Total Harmonic Distortion (THD)                                           | 25°C | 1          |      | -50    | -36.2 | dB         |

| Spurious-Free Dynamic Range (SFDR)                                        | 25°C | 1          | 41.3 | 51     |       | dB         |

| Parameter                                                                   | Temp  | Test Level | Min   | Тур         | Max   | Unit       |

|-----------------------------------------------------------------------------|-------|------------|-------|-------------|-------|------------|

| 10-BIT ADC CHARACTERISTICS                                                  |       |            |       | • •         |       |            |

| Resolution                                                                  | N/A   | N/A        |       | 10          |       | Bits       |

| Maximum Conversion Rate                                                     | Full  | II         | 29    |             |       | MHz        |

| Pipeline Delay                                                              | N/A   | N/A        |       | 4.5         |       | ADC cycles |

| Analog Input                                                                |       |            |       |             |       |            |

| Input Voltage Range                                                         | Full  | III        |       | 2.0         |       | Vppd       |

| Input Capacitance                                                           | 25°C  | III        |       | 2           |       | pF         |

| Differential Input Resistance                                               | 25°C  | II         |       | 4           |       | kΩ         |

| Reference Voltage Error                                                     |       |            |       |             |       |            |

| (REFT10-REFB10) -1 V                                                        | Full  | 1          |       | ±4          | ±200  | mV         |

| AC Performance ( $A_{IN} = -0.5 \text{ dBFS}$ , $f_{IN} = 5 \text{ MHz}$ )  |       |            |       |             |       |            |

| ADC Sample Clock Source = OSCIN                                             |       |            |       |             |       |            |

| Signal-to-Noise and Distortion (SINAD)                                      | Full  | II         | 58.3  | 59.9        |       | dB         |

| Effective Number of Bits (ENOB)                                             | Full  | II         | 9.4   | 9.65        |       | Bits       |

| Signal-to-Noise Ratio (SNR)                                                 | Full  | II         | 58.6  | 60          |       | dB         |

| Total Harmonic Distortion (THD)                                             | Full  | II         |       | <b>-73</b>  | -62   | dB         |

| Spurious-Free Dynamic Range (SFDR)                                          | Full  | II         | 65.7  | 76          |       | dB         |

| AC Performance ( $A_{IN} = -0.5 \text{ dBFS}$ , $f_{IN} = 50 \text{ MHz}$ ) |       |            |       |             |       |            |

| ADC Sample Clock Source = OSCIN                                             |       |            |       |             |       |            |

| Signal-to-Noise and Distortion (SINAD)                                      | Full  | П          | 57.7  | 59.0        |       | dB         |

| Effective Number of Bits (ENOB)                                             | Full  | l II       | 9.29  | 9.51        |       | Bits       |

| Signal-to-Noise Ratio (SNR)                                                 | Full  | П          | 57.8  | 59.1        |       | dB         |

| Total Harmonic Distortion (THD)                                             | Full  | II         | -61.4 | <b>–75</b>  |       | dB         |

| Spurious-Free Dynamic Range (SFDR)                                          | Full  | II         | 64    | 78          |       | dB         |

| 12-BIT ADC CHARACTERISTICS                                                  |       |            | -     | -           |       |            |

| Resolution                                                                  | N/A   | N/A        |       | 12          |       | Bits       |

| Maximum Conversion Rate                                                     | Full  | II         | 29    |             |       | MHz        |

| Pipeline Delay                                                              | N/A   | N/A        |       | 5.5         |       | ADC cycles |

| Analog Input                                                                |       |            |       |             |       |            |

| Input Voltage Range                                                         | Full  | III        |       | 2           |       | Vppd       |

| Input Capacitance                                                           | 25°C  | III        |       | 2           |       | pF         |

| Differential Input Resistance                                               | 25°C  | l III      |       | 4           |       | kΩ         |

| Reference Voltage Error                                                     |       |            |       | ·           |       | 1          |

| (REFT12–REFB12) –1 V                                                        | Full  | l i        |       | ±16         | ±200  | mV         |

| AC Performance ( $A_{IN} = -0.5 \text{ dBFS}$ , $f_{IN} = 5 \text{ MHz}$ )  |       |            |       |             |       |            |

| ADC Sample Clock Source = OSCIN                                             |       |            |       |             |       |            |

| Signal-to-Noise and Distortion (SINAD)                                      | Full  | II         | 60.0  | 65.2        |       | dB         |

| Effective Number of Bits (ENOB)                                             | Full  | II         | 9.67  | 10.53       |       | Bits       |

| Signal-to-Noise Ratio (SNR)                                                 | Full  | II         | 60.3  | 65.6        |       | dB         |

| Total Harmonic Distortion (THD)                                             | Full  |            |       | -76.6       | -58.7 | dB         |

| Spurious-Free Dynamic Range (SFDR)                                          | Full  |            | 64.7  | 79          | 30.7  | dB         |

| AC Performance ( $A_{IN} = -0.5 \text{ dBFS}$ , $f_{IN} = 50 \text{ MHz}$ ) | I dii | "          | 0 1.7 | ,,          |       | ab         |

| ADC Sample Clock Source = OSCIN                                             |       |            |       |             |       |            |

| Signal-to-Noise and Distortion (SINAD)                                      | Full  | II         | 59.5  | 62.7        |       | dB         |

| Effective Number of Bits (ENOB)                                             | Full  | ii         | 9.59  | 10.1        |       | Bits       |

| Signal-to-Noise Ratio (SNR)                                                 | Full  |            | 59.7  | 63.0        |       | dB         |

| Total Harmonic Distortion (THD)                                             | Full  | "          | 33.7  | -75.5       | -60.5 | dB         |

| Spurious-Free Dynamic Range (SFDR)                                          | Full  | "          | 63.8  | -73.3<br>79 | 00.5  | dB         |

| VIDEO CLAMP PERFORMANCE                                                     | 1 411 |            | 33.0  | .,,         |       | 45         |

| $(A_{IN} = -0.5 \text{ dBFS}, f = 5 \text{ MHz})$                           |       |            |       |             |       |            |

| ADC Sample Clock = OSCIN                                                    |       |            |       |             |       |            |

| Signal-to-Noise and Distortion (SINAD)                                      | Full  | II         | 43.9  | 50.6        |       | dB         |

| Effective Number of Bits (ENOB)                                             | Full  | II         | 7.0   | 8.1         |       | Bits       |

| Parameter                                                                | Temp  | Test Level | Min                       | Тур   | Max               | Unit                     |

|--------------------------------------------------------------------------|-------|------------|---------------------------|-------|-------------------|--------------------------|

| Signal-to-Noise Ratio (SNR)                                              | Full  | II         | 46.2                      | 57.2  |                   | Bits                     |

| Total Harmonic Distortion (THD)                                          | Full  | II         |                           | -50.1 | -44.5             | dB                       |

| Spurious-Free Dynamic Range (SFDR)                                       | Full  | II         | 44.9                      | 53.4  |                   | dB                       |

| CHANNEL-TO-CHANNEL ISOLATION                                             |       |            |                           |       |                   |                          |

| Tx DAC-to-ADC Isolation $(A_{OUT} = 5 \text{ MHz})$                      |       |            |                           |       |                   |                          |

| Isolation Between Tx and IQ ADCs                                         | 25°C  | III        |                           | >60   |                   | dB                       |

| Isolation Between Tx and 10-Bit ADC                                      | 25°C  | III        |                           | >80   |                   | dB                       |

| Isolation Between Tx and 12-Bit ADC                                      | 25°C  | III        |                           | >80   |                   | dB                       |

| ADC-to-ADC ( $A_{IN} = -0.5 \text{ dBFS}, f = 5 \text{ MHz}$ )           |       |            |                           |       |                   |                          |

| Isolation Between IF10 and IF12 ADCs                                     | 25°C  | Ш          |                           | >85   |                   | dB                       |

| Isolation Between Q and I Inputs                                         | 25°C  | Ш          |                           | >50   |                   | dB                       |

| TIMING CHARACTERISTICS (10 pF Load)                                      |       |            |                           |       |                   |                          |

| Minimum RESET Pulse Width Low (t <sub>RL</sub> )                         | N/A   | N/A        | 5                         |       |                   | t <sub>MCLK</sub> cycles |

| Digital Output Rise/Fall Time                                            | Full  | II         | 2.8                       |       | 4                 | ns                       |

| Tx/Rx Interface                                                          |       |            |                           |       |                   |                          |

| MCLK Frequency (f <sub>MCLK</sub> )                                      | Full  | II         |                           |       | 66                | MHz                      |

| TxSYNC/TxIQ Setup Time (tsu)                                             | Full  | "          | 3                         |       |                   | ns                       |

| TxSYNC/TxIQ Hold Time (t <sub>HD</sub> )                                 | Full  | II         | 3                         |       |                   | ns                       |

| MCLK Rising Edge to                                                      | T dil | "          |                           |       |                   | 113                      |

| RxSYNC/RxIQ/IF Valid Delay (t <sub>MD</sub> )                            | Full  | l II       | 0                         |       | 1.0               | ns                       |

| REFCLK Rising or Falling Edge to                                         | T dil | "          |                           |       | 1.0               | 113                      |

| RxSYNC/RxIQ/IF Valid Delay (t <sub>op</sub> )                            | Full  | II         | T <sub>OSC</sub> /4 – 2.0 |       | $T_{OSC}/4 + 3.0$ | ns                       |

| REFCLK Edge to MCLK Falling Edge (tee)                                   | Full  | "          | -1.0                      |       | +1.0              | ns                       |

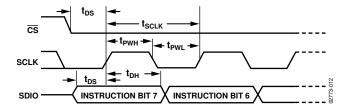

| Serial Control Bus                                                       | Tuil  | "          | -1.0                      |       | 71.0              | 113                      |

| Maximum SCLK Frequency (fsclk)                                           | Full  | l II       |                           |       | 15                | MHz                      |

| Minimum Clock Pulse Width High (t <sub>PWH</sub> )                       | Full  | "          | 30                        |       | 13                | ns                       |

| Minimum Clock Pulse Width Low (t <sub>PWL</sub> )                        | Full  | "          | 30                        |       |                   | ns                       |

| Maximum Clock Rise/Fall Time                                             | Full  | "          | 30                        |       | 1                 | ms                       |

| Minimum Data/Chip-Select Setup Time (t <sub>DS</sub> )                   | Full  |            | 25                        |       | ı                 | ns                       |

| Minimum Data/Citip-Select Setup Time (LDS)  Minimum Data Hold Time (tDH) | Full  | "          | 0                         |       |                   | ns                       |

| Maximum Data Hold Time (tp4)                                             | Full  | "          | 0                         |       | 30                |                          |

| CMOS LOGIC INPUTS                                                        | Full  | "          |                           |       | 30                | ns                       |

|                                                                          | 2500  |            | V 0.7                     |       |                   | V                        |

| Logic 1 Voltage                                                          | 25°C  | l II       | $V_{DRVDD} - 0.7$         |       | 0.4               | V                        |

| Logic 0 Voltage                                                          | 25°C  | l II       |                           |       | 0.4               | -                        |

| Logic 1 Current                                                          | 25°C  | l II       |                           |       | 12                | μΑ                       |

| Logic 0 Current                                                          | 25°C  | l II       |                           | 2     | 12                | μA                       |

| Input Capacitance                                                        | 25°C  | II         |                           | 3     |                   | pF                       |

| CMOS LOGIC OUTPUTS (1 mA Load)                                           | 2506  |            | .,                        |       |                   | .,                       |

| Logic 1 Voltage                                                          | 25°C  | II<br>     | V <sub>DRVDD</sub> – 0.6  |       |                   | V                        |

| Logic 0 Voltage                                                          | 25°C  | II         |                           |       | 0.4               | V                        |

| POWER SUPPLY                                                             |       |            |                           |       |                   |                          |

| Supply Current, Is (Full Operation)                                      | 25°C  | II         |                           | 163   | 184               | mA                       |

| Analog Supply Current, I <sub>AS</sub>                                   | 25°C  | III        |                           | 95    |                   | mA                       |

| Digital Supply Current, I <sub>DS</sub>                                  | 25°C  | III        |                           | 68    |                   | mA                       |

| Supply Current, Is                                                       |       |            |                           |       |                   |                          |

| Standby (PWRDN Pin Active)                                               | 25°C  | II         |                           | 119   | 126               | mA                       |

| Full Power-Down (Register $0x02 = 0xF9$ )                                | 25℃   | III        |                           | 16    |                   | mA                       |

| Power-Down Tx Path (Register $0x02 = 0x60$ )                             | 25°C  | III        |                           | 113   |                   | mA                       |

| Power-Down Rx Path (Register $0x02 = 0x19$ )                             | 25°C  | III        |                           | 110   |                   | mA                       |

<sup>&</sup>lt;sup>1</sup> IQ ADC in default mode. ADC Clock Select Register 8, Bit 3 set to 0.

### **ABSOLUTE MAXIMUM RATINGS**

### Table 2.

| Parameter                                                                | Rating                                        |

|--------------------------------------------------------------------------|-----------------------------------------------|

| Power Supply (V <sub>AVDD</sub> ,V <sub>DVDD</sub> ,V <sub>DRVDD</sub> ) | 3.9 V                                         |

| Digital Output Current                                                   | 5 mA                                          |

| Digital Inputs                                                           | $-0.3 \text{ V to V}_{DRVDD} + 0.3 \text{ V}$ |

| Analog Inputs                                                            | $-0.3 \text{ V to V}_{AVDD} + 0.3 \text{ V}$  |

| Operating Temperature                                                    | -40°C to +85°C                                |

| Maximum Junction Temperature                                             | 150°C                                         |

| Storage Temperature                                                      | −65°C to +150°C                               |

| Lead Temperature (Soldering, 10 sec)                                     | 300°C                                         |

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **EXPLANATION OF TEST LEVELS**

- I Devices are 100% production tested at +25°C and guaranteed by design and characterization testing for commercial operating temperature range (-40°C to +85°C).

- II Parameter is guaranteed by design and/or characterization testing.

- III Parameter is a typical value only.

- N/A Test level definition is not applicable.

### THERMAL CHARACTERISTICS

Thermal Resistance 100-Lead MOFP

$\theta_{IA} = 40.5$ °C/W

### **ESD CAUTION**

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although this product features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

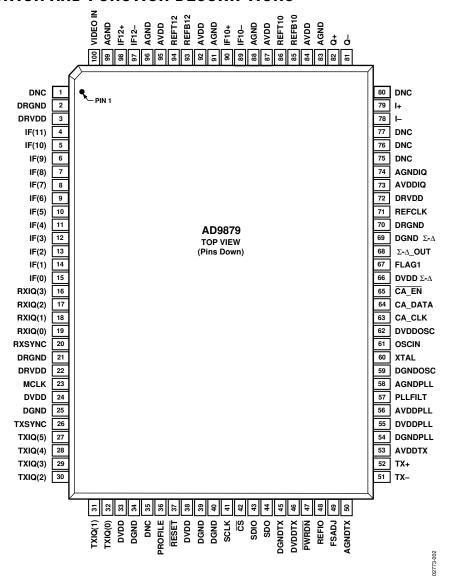

## PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Figure 2. Pin Configuration

**Table 3. Pin Function Descriptions**

| Pin No.             | Mnemonic  | Description                                 |  |

|---------------------|-----------|---------------------------------------------|--|

| 1, 35, 75 to 77, 80 | DNC       | Do Not Connect. Pins are not bonded to die. |  |

| 2, 21, 70           | DRGND     | Pin Driver Digital Ground.                  |  |

| 3, 22, 72           | DRVDD     | Pin Driver Digital 3.3 V Supply.            |  |

| 4 to 15             | IF[11:0]  | 12-Bit ADC Digital Output.                  |  |

| 16 to 19            | RXIQ[3:0] | Muxed I and Q ADCs Output.                  |  |

| 20                  | RXSYNC    | Sync Output, IF, I and Q ADCs.              |  |

| 23                  | MCLK      | Master Clock Output.                        |  |

| 24, 33, 38          | DVDD      | Digital 3.3 V Supply.                       |  |

| 25, 34, 39, 40      | DGND      | Digital Ground.                             |  |

| 26                  | TXSYNC    | Sync Input for Transmit Port.               |  |

| 27 to 32            | TXIQ[5:0] | Digital Input for Transmit Port.            |  |

| 36                  | PROFILE   | Profile Selection Inputs.                   |  |

| 37                  | RESET     | Chip Reset Input (Active Low).              |  |

| Pin No.            | Mnemonic     | Description                            |

|--------------------|--------------|----------------------------------------|

| 41                 | SCLK         | SPORT Clock.                           |

| 42                 | CS           | SPORT Chip Select.                     |

| 43                 | SDIO         | SPORT Data I/O.                        |

| 44                 | SDO          | SPORT Data Output.                     |

| 45                 | DGNDTX       | Tx Path Digital Ground.                |

| 46                 | DVDDTX       | Tx Path Digital 3.3 V Supply.          |

| 47                 | PWRDN        | Power-Down Transmit Path.              |

| 48                 | REFIO        | TxDAC Decoupling (to AGND).            |

| 49                 | FSADJ        | DAC Output Adjust (External Resistor). |

| 50                 | AGNDTX       | Tx Path Analog Ground.                 |

| 51, 52             | TX-, TX+     | Tx Path Complementary Outputs.         |

| 53                 | AVDDTX       | Tx Path Analog 3.3 V Supply.           |

| 54                 | DGNDPLL      | PLL Digital Ground.                    |

| 55                 | DVDDPLL      | PLL Digital 3.3 V Supply.              |

| 56                 | AVDDPLL      | PLL Analog 3.3 V Supply.               |

| 57                 | PLLFILT      | PLL Loop Filter Connection.            |

| 58                 | AGNDPLL      | PLL Analog Ground.                     |

| 59                 | DGNDOSC      | Oscillator Digital Ground.             |

| 60                 | XTAL         | Crystal Oscillator Inverted Output.    |

| 61                 | OSCIN        | Oscillator Clock Input.                |

| 62                 | DVDDOSC      | Oscillator Digital 3.3 V Supply.       |

| 63                 | CA_CLK       | Serial Clock to Cable Driver.          |

| 64                 | CA_DATA      | Serial Data to Cable Driver.           |

| 65                 | CA_EN        | Serial Enable to Cable Drive.          |

| 66                 | DVDD Σ-Δ     | Σ-Δ Digital 3.3 V Supply.              |

| 67                 | FLAG1        | Digital Output Flag 1.                 |

| 68                 | Σ-Δ_ΟUΤ      | Σ-Δ DAC Output.                        |

| 69                 | DGND Σ-Δ     | Σ-Δ Digital Ground.                    |

| 71                 | REFCLK       | Programmable Reference Clock Output.   |

| 73                 | AVDDIQ       | 7-Bit ADCs Analog 3.3 V Supply.        |

| 74                 | AGNDIQ       | 7-Bit ADCs Analog Ground.              |

| 78, 79             | I–, I+       | Differential Input to I ADC.           |

| 81, 82             | Q-, Q+       | Differential Input to Q ADC.           |

| 83, 88, 91, 96, 99 | AGND         | 12-Bit ADC Analog Ground.              |

| 84, 87, 92, 95     | AVDD         | 12-Bit ADC Analog 3.3 V Supply.        |

| 85                 | REFB10       | 10-Bit ADC Decoupling Node.            |

| 86                 | REFT10       | 10-Bit ADC Decoupling Node.            |

| 89, 90             | IF10-, IF10+ | Differential Input to 10-Bit ADC.      |

| 93                 | REFB12       | 12-Bit ADC Decoupling Node.            |

| 94                 | REFT12       | 12-Bit ADC Decoupling Node.            |

| 97, 98             | IF12-, IF12+ | Differential Input to IF ADC.          |

| 100                | VIDEO IN     | Video Clamp Input, 12-Bit ADC.         |

### **TERMINOLOGY**

### **Aperture Delay**

The aperture delay is a measure of the sample-and-hold amplifier (SHA) performance. It specifies the time delay between the rising edge of the sampling clock input and when the input signal is held for conversion.

### Aperture Uncertainty (Jitter)

Aperture jitter is the variation in aperture delay for successive samples. It is manifested as noise on the input to the ADC.

### Channel-to-Channel Isolation (Crosstalk)

In an ideal multichannel system, the signal in one channel does not influence the signal level of another channel. The channelto-channel isolation specification is a measure of the change that occurs to a grounded channel as a full-scale signal is applied to another channel.

### Differential Nonlinearity Error (DNL, No Missing Codes)

An ideal converter exhibits code transitions that are exactly 1 LSB apart. DNL is the deviation from this ideal value. Guaranteed no missing codes to 10-bit resolution indicates that all 1,024 codes, respectively, must be present over all operating ranges.

### **Effective Number of Bits (ENOB)**

For a sine wave, *SINAD* can be expressed in terms of the number of bits. Using the formula

$$N = (SINAD - 1.76 \text{ dB/6.02})$$

it is possible to determine a measure of performance expressed as *N*, the effective number of bits. Thus, the effective number of bits for a device's sine wave inputs at a given input frequency can be calculated directly from its measured *SINAD*.

#### **Gain Error**

The first code transition should occur at an analog value 1/2 LSB above full scale. The last transition should occur for an analog value 1 1/2 LSB below the nominal full scale. Gain error is the deviation of the actual difference between the first and last code transitions and the ideal difference between the first and last code transitions.

### **Input Referred Noise**

The rms output noise is measured using histogram techniques. The standard deviation of the ADC output code is calculated in LSB and converted to an equivalent voltage. This results in a noise figure that can be directly referred to the input of the MxFE.

### **Integral Nonlinearity Error (INL)**

Linearity error refers to the deviation of each individual code from a line drawn from negative full scale through the positive full scale. The point used as the negative full scale occurs 1/2 LSB before the first code transition. Positive full scale is defined as a level 1 1/2 LSB beyond the last code transition. The deviation is measured from the middle of each code to the true straight line.

#### Offset Error

First transition should occur for an analog value 1/2 LSB above –FS. Offset error is defined as the deviation of the actual transition from that point.

### **Output Compliance Range**

The range of allowable voltage at the output of a current-output DAC. Operation beyond the maximum compliance limits can cause either output stage saturation or break down, resulting in nonlinear performance.

#### **Phase Noise**

Single-sideband phase noise power is specified relative to the carrier (dBc/Hz) at a given frequency offset (1 kHz) from the carrier. Phase noise can be measured directly in single-tone transmit mode with a spectrum analyzer that supports noise marker measurements. It detects the relative power between the carrier and the offset (1 kHz) sideband noise and takes the resolution bandwidth (RBW) into account by subtracting 10 log(RBW). It also adds a correction factor that compensates for the implementation of the resolution bandwidth, log display, and detector characteristic.

### Pipeline Delay (Latency)

Pipeline delay is the number of clock cycles between conversion initiation and the availability of the associated output data.

### **Power Supply Rejection**

Power supply rejection specifies the converter's maximum full-scale change when the supplies are varied from nominal to minimum and maximum specified voltages.

### Signal-to-Noise and Distortion (SINAD) Ratio

SINAD is the ratio of the rms value of the measured input signal to the rms sum of all other spectral components below the Nyquist frequency, including harmonics but excluding dc. The value for SINAD is expressed in decibels.

### Signal-to-Noise Ratio (SNR)

SNR is the ratio of the rms value of the measured input signal to the rms sum of all other spectral components below the Nyquist frequency, excluding harmonics and dc. The value for SNR is expressed in decibels.

### Spurious-Free Dynamic Range (SFDR)

SFDR is the difference, in dB, between the rms amplitude of the DAC output signal (or the ADC input signal) and the peak spurious signal over the specified bandwidth (Nyquist bandwidth, unless otherwise noted).

### **Total Harmonic Distortion (THD)**

THD is the ratio of the rms sum of the first six harmonic components to the rms value of the measured input signal, and is expressed as a percentage or in decibels.

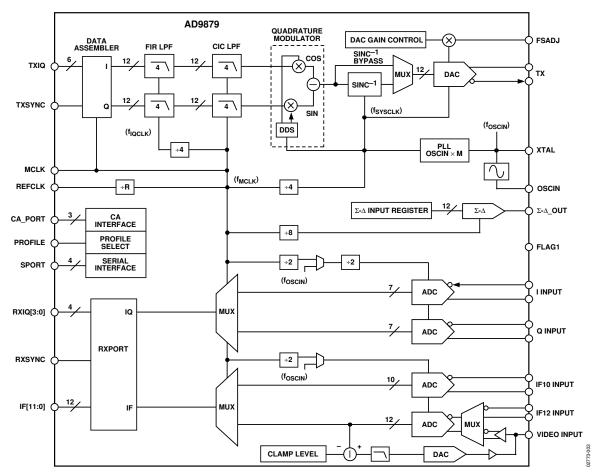

### THEORY OF OPERATION

To gain a general understanding of the AD9879, refer to the block diagram of the device architecture in Figure 3. The device consists of a transmit path, receive path, and auxiliary functions, such as a DPLL, a  $\Sigma$ - $\Delta$  DAC, a serial control port, and a cable amplifier interface.

### **TRANSMIT PATH**

The transmit path contains an interpolation filter, a complete quadrature digital upconverter, an inverse sinc filter, and a 12-bit current output DAC. The maximum output current of the DAC is set by an external resistor. The Tx output PGA provides additional transmit signal level control.

The transmit path interpolation filter provides an upsampling factor of 16 with an output signal bandwidth as high as 5.8 MHz. Carrier frequencies up to 65 MHz with 26 bits of frequency tuning resolution can be generated by the direct digital synthesizer (DDS).

The transmit DAC resolution is 12 bits and can run at sampling rates as high as 232 MSPS. Analog output scaling from 0.0 dB to 7.5 dB in 0.5 dB steps is available to preserve SNR when reduced output levels are required.

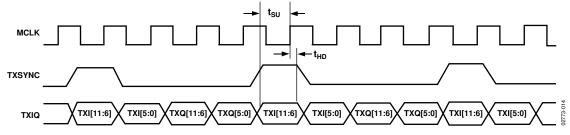

### **DATA ASSEMBLER**

The AD9879 data path operates on two 12-bit words, the I and Q components, which compose a complex symbol. The data assembler builds the 24-bit complex symbols from four consecutive 6-bit nibbles read over the TxIQ[5:0] bus. The nibbles are strobed synchronous to the master clock, MCLK, into the data assembler. A high level on TxSYNC signals the start of a transmit symbol. The first two nibbles of the symbol form the I component, and the second two nibbles form the Q component. Symbol components are assumed to be in twos complement format. The timing of the interface is fully described in the Transmit Timing section of this data sheet.

Figure 3. Block Diagram

### INTERPOLATION FILTER

Once through the data assembler, the IQ data streams are fed through a 4× FIR low-pass filter and a 4× cascaded integrator-comb (CIC) low-pass filter. The combination of these two filters results in the sample rate increasing by a factor of 16. In addition to the sample rate increase, the half-band filters provide the low-pass filtering characteristic necessary to suppress the spectral images between the original sampling frequency and the new (16× higher) sampling frequency.

### **DIGITAL UPCONVERTER**

The digital quadrature modulator stage following the CIC filters is used to frequency shift (upconvert) the baseband spectrum of the incoming data stream up to the desired carrier frequency. The carrier frequency is controlled numerically by a direct digital synthesizer (DDS). The DDS uses the internal system clock (f<sub>SYSCLK</sub>) to generate the desired carrier frequency with a high degree of precision. The carrier is applied to the I and Q multipliers in quadrature fashion (90° phase offset) and summed to yield a data stream that is the modulated carrier. The modulated carrier becomes the 12-bit sample sent to the DAC.

The receive path contains a 12-bit ADC, a 10-bit ADC, and a dual 7-bit ADC. All internally required clocks and an output system clock are generated by the PLL from a single crystal or clock input.

The 12-bit and 10-bit IF ADCs can convert direct IF inputs up to 70 MHz and run at sample rates up to 33 MSPS. A video input with an adjustable signal clamping level along with the 10-bit ADC allow the AD9879 to process an NTSC and a QAM channel simultaneously.

The programmable  $\Sigma$ - $\Delta$  DAC can be used to control external components, such as variable gain amplifiers (VGAs) or voltage controlled tuners. The CA\_PORT provides an interface to the AD8321/AD8323 or AD8322/AD8327 programmable gain amplifier (PGA) cable drivers, enabling host processor control via the MxFE SPORT.

### **OSCIN Clock Multiplier**

The AD9879 can accept either an input clock into the OSCIN pin or a fundamental mode XTAL across the OSCIN pin and XTAL pins as the device's main clock source. The internal PLL then generates the  $f_{\text{SYSCLK}}$  signal from which all other internal signals are derived.

The DAC uses f<sub>SYSCLK</sub> as its sampling clock. For DDS applications, the carrier is typically limited to about 30% of f<sub>SYSCLK</sub>. For a 65 MHz carrier, the system clock required is above 216 MHz.

The OSCIN multiplier function maintains clock integrity, as evidenced by the excellent phase noise characteristics and low clock-related spur in the output spectrum of the AD9879's systems.

External loop filter components consisting of a series resistor (1.3 k $\Omega$ ) and capacitor (0.01  $\mu F$ ) provide the compensation zero for the OSCIN multiplier PLL loop. The overall loop performance has been optimized for these component values.

### **DPLL-A CLOCK DISTRIBUTION**

Figure 3 shows the clock signals used in the transmit path. The DAC sampling clock,  $f_{DAC}$ , is generated by DPLL-A.  $F_{DAC}$  has a frequency equal to  $L \times f_{OSCIN}$ , where  $f_{OSCIN}$  is the internal signal generated by either the crystal oscillator when a crystal is connected between the OSCIN and XTAL pins or the clock that is fed into the OSCIN pin, and L is the multiplier programmed through the serial port. L can have the values of 1, 2, 3, or 8.

The transmit path expects a new half word of data at the rate of  $f_{\text{CLK-A}}$ . When the Tx multiplexer is enabled, the frequency of Tx Port is

$$f_{CLK-A} = 2 \times f_{DA}/K = 2 \times L \times f_{OSCIN}/K$$

(1)

where K is the interpolation factor.

The interpolation factor can be programmed to be 1, 2, or 4. When the Tx multiplexer is disabled, the frequency of the Tx Port is

$$f_{CLK-A} = f_{DAC}/K = L \times f_{OSCIN}/K$$

(2)

#### **Receive Section**

The AD9879 includes two high speed, high performance ADCs. The 10-bit and 12-bit direct IF ADCs deliver excellent undersampling performance with input frequencies as high as 70 MHz. The sampling rate can be as high as 33 MSPS.

The ADC sampling frequency can be derived directly from the OSCIN signal or from the on-chip OSCIN multiplier. For highest dynamic performance, it is advisable to choose an OSCIN frequency that can be directly used as the ADC sampling clock. Digital IQ ADC outputs are multiplexed to one 4-bit bus, clocked by a frequency ( $f_{MCLK}$ ) of four times the sampling rate. The IF ADCs use a multiplexed 12-bit interface with an output word rate of  $f_{MCLK}$ .

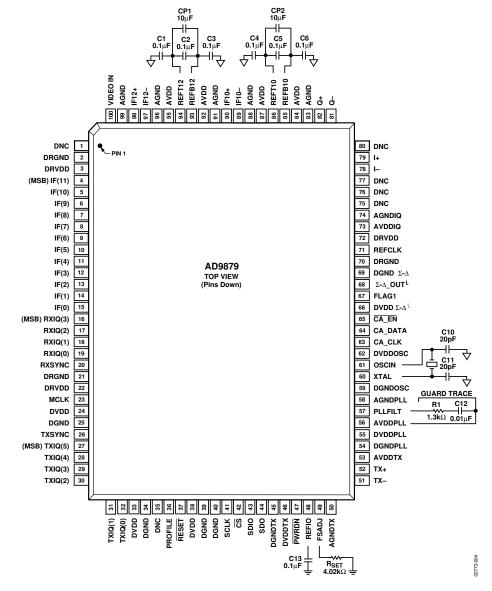

### **CLOCK AND OSCILLATOR CIRCUITRY**

The internal oscillator of the AD9879 generates all sampling clocks from a simple, low cost, parallel resonance, fundamental frequency quartz crystal. Figure 4 shows how the quartz crystal is connected between OSCIN (Pin 61) and XTAL (Pin 60) with parallel resonant load capacitors as specified by the crystal manufacturer. The internal oscillator circuitry can also be overdriven by a TTL-level clock applied to OSCIN with XTAL left unconnected.

$$f_{OSCIN} = f_{MCLK} \times M \tag{3}$$

An internal PLL generates the DAC sampling frequency,  $f_{SYSCLK}$ , by multiplying OSCIN frequency M times. The MCLK signal (Pin 23),  $f_{MCLK}$ , is derived by dividing  $f_{SYSCLK}$  by 4.

$$f_{\text{SYSCLK}} = f_{\text{OSCIN}} \times M \tag{4}$$

$$f_{MCLK} = f_{OSCIN} \times M/4 \tag{5}$$

An external PLL loop filter (Pin 57) consisting of a series resistor and ceramic capacitor (Figure 18, R1 = 1.3 k $\Omega$ , C12 = 0.01  $\mu$ F) is required for stability of the PLL. Also, a shield surrounding these components is recommended to minimize external noise coupling into the PLL's voltage controlled oscillator input (guard trace connected to AVDDPLL).

Figure 3 shows that ADCs are either sampled directly by a low jitter clock at OSCIN or by a clock that is derived from the PLL output. Operating modes can be selected in Register 0x08. Sampling the ADCs directly with the OSCIN clock requires MCLK to be programmed to be twice the OSCIN frequency.

### PROGRAMMABLE CLOCK OUTPUT REFCLK

The AD9879 provides an auxiliary output clock on Pin 71, REFCLK. The value of the MCLK divider bit field, *R*, determines its output frequency as shown:

$$f_{REFCLK} = f_{MCLK}/R$$

, for  $R = 2 - 3$  (6)

$$f_{REFCLK} = f_{OSCIN}/R$$

, for  $R = 0$  (7)

In its default setting (0x00 in Register 0x01), the REFCLK pin provides a buffered output of  $f_{\rm OSCIN}$ .

Figure 4. Basic Connection Diagram

### **RESET AND TRANSMIT POWER-DOWN**

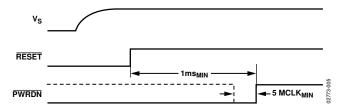

### **Power-Up Sequence**

On initial power-up, the RESET pin should be held low until the power supply is stable.

Once RESET is deasserted, the AD9879 can be programmed over the serial port. The on-chip PLL requires a maximum of 1 millisecond after the rising edge of RESET or a change of the multiplier factor (M) to completely settle. It is recommended that the PWRDN pin be held low during the reset and PLL settling time. Changes to ADC Clock Select (Register 0x08) or SYS Clock Divider N (Register 0x01) should be programmed before the rising edge of PWRDN.

Once the PLL is frequency locked and after the PWRDN pin is brought high, transmit data can be sent reliably.

If the PWRDN pin cannot be held low throughout the reset and PLL settling time period, the power-down digital Tx bit or the PWRDN pin should be pulsed after the PLL has settled. This will ensure correct transmit filter initialization.

### RESET

To initiate a hardware reset, the RESET pin should be held low for at least 100 nanoseconds. All internally generated clocks stop during reset. The rising edge of RESET resets the PLL clock multiplier and reinitializes the programmable registers to their default values. The same sequence as described in the Power-Up Sequence section should be followed after a reset or change in M.

A software reset (writing a 1 into Bit 5 of Register 0x00) is functionally equivalent to the hardware reset but does not force Register 0x00 to its default value.

Figure 5. Power-Up Sequence for Tx Data Path

### **Transmit Power-Down**

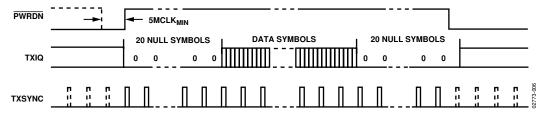

A low level on the PWRDN pin stops all clocks linked to the digital transmit data path and resets the CIC filter. Deasserting PWRDN reactivates all clocks. The CIC filter is held in a reset state for 80 MCLK cycles after the rising edge of PWRDN to allow for flushing of the half-band filters with new input data.

Transmit data bursts should be <u>padded</u> with at least 20 symbols of null data directly before the <u>PWRDN</u> pin is deasserted. Immediately after the <u>PWRDN</u> pin is deasserted, the transmit burst should start with a minimum of 20 null data symbols. This avoids unintended DAC output samples caused by the transmit path latency and filter settling time.

Software Power-Down Digital Tx (Bit 5 in Register 02x00) is functionally equivalent to the hardware  $\overline{PWRDN}$  pin and takes effect immediately after the last register bit has been written over the serial port.

Figure 6. Timing Sequence to Flush Tx Data Path

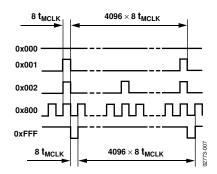

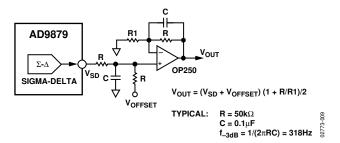

### Σ-Δ OUTPUTS

The AD9879 contains an on-chip  $\Sigma$ - $\Delta$  output that provides a digital logic bit stream with an average duty cycle that varies between 0% and (4095/4096)%, depending on the programmed code, as shown in Figure 7.

This bit stream can be low-pass filtered to generate a programmable dc voltage of

$$V_{DC} = (\Sigma - \Delta Code/4096)(V_{\rm H}) + V_L \tag{8}$$

where:

$V_H = V_{DRVDD} - 0.6 \text{ V}$

$V_L = 0.4 \text{ V}$

Figure 7. Σ-Δ Output Signals

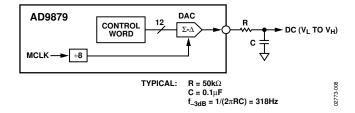

In set-top box and cable modem applications, the output can be used to control external variable gain amplifiers or RF tuners. A simple single-pole RC low-pass filter provides sufficient filtering (see Figure 8).

In more demanding applications where additional gain, level shift, or drive capability is required, a first or second order active filter might be considered for each  $\Sigma$ - $\Delta$  output (see Figure 9).

Figure 8. Σ-Δ RC Filter

Figure 9.  $\Sigma$ - $\Delta$  Active Filter with Gain and Offset

## **REGISTER MAP AND BIT DEFINITIONS**

Table 4. Register Map<sup>1</sup>

| Address<br>(hex) | Bit 7                                   | Bit 6                    | Bit 5                           | Bit 4                                               | Bit 3                                    | Bit 2                                             | Bit 1                                             | Bit 0                                 | Default<br>(hex) | Туре       |

|------------------|-----------------------------------------|--------------------------|---------------------------------|-----------------------------------------------------|------------------------------------------|---------------------------------------------------|---------------------------------------------------|---------------------------------------|------------------|------------|

| 0x00             | SDIO<br>Bidirectional                   | SPI Bytes<br>LSB First   | RESET                           |                                                     | OSCIN Multiplier M[4:0]                  |                                                   |                                                   |                                       |                  | Read/Write |

| 0x01             | PLL Lock<br>Detect                      |                          |                                 |                                                     | MCLK/REFCLK I                            | Ratio R[5:0]                                      |                                                   |                                       | 0x00             | Read/Write |

| 0x02             | Power-<br>Down PLL                      | Power-<br>Down<br>DAC Tx | Power-<br>Down<br>Digital<br>Tx | Power-<br>Down<br>IF12<br>ADC                       | Power-Down<br>Reference<br>IF12 ADC      | Power-<br>Down<br>IF10 ADC                        | Power-<br>Down<br>Reference<br>IQ and<br>IF10 ADC | Power-<br>Down IQ<br>ADC              | 0x00             | Read/Write |

| 0x03             | Σ-Δ Output C                            | ontrol Word              | [3:0]                           |                                                     |                                          |                                                   | Flag 1                                            | Flag 0<br>Enable                      | 0x00             | Read/Write |

| 0x04             | Flag 0                                  |                          |                                 |                                                     | Σ-Δ Output Cor                           | ntrol Word [11                                    | 1:4]                                              | •                                     | 0x00             | Read/Write |

| 0x05             | 0                                       | 0                        | 0                               | 0                                                   | 0                                        | 0                                                 | 0                                                 | 0                                     | 0x00             | Read/Write |

| 0x06             | 0                                       | 0                        | 0                               | 0                                                   | 0                                        | 0                                                 | 0                                                 | 0                                     | 0x00             | Read Only  |

| 0x07             | Video Input<br>Enable                   |                          |                                 |                                                     | Clamp Level for                          | r Video Input                                     | [6:0]                                             |                                       | 0x00             | Read/Write |

| 0x08             | ADCs<br>Clocked<br>Direct from<br>OSCIN | 0                        | Rx Port<br>Fast<br>Edge<br>Rate | Power-<br>Down<br>RxSYNC<br>and IQ<br>ADC<br>Clocks | Enable 7-Bits<br>IQ ADC                  | 0                                                 | Send<br>12-Bit<br>ADC Data<br>Only                | Send<br>10-Bit<br>ADC<br>Data<br>Only | 0x80             | Read/Write |

| 0x09             | 0                                       | 0                        | 0                               | 0                                                   | 0                                        | 0                                                 | 0                                                 | 0                                     | 0x00             | Read/Write |

| 0x0A             | 0                                       | 0                        | 0                               | 0                                                   | 0                                        | 0                                                 | 0                                                 | 0                                     | 0x00             | Read/Write |

| 0x0B             | 0                                       | 0                        | 0                               | 0                                                   | 0                                        | 0                                                 | 0                                                 | 0                                     | 0x00             | Read/Write |

| 0x0C             | 0                                       | 0                        | 0                               | 0                                                   |                                          | Version [3:0                                      | ]                                                 |                                       | 0x05             | Read/Write |

| 0x0D             | 0                                       | 0                        | 0                               | 0                                                   | Tx Frequency T<br>Profile 1 LSBs [1      | 1:0]                                              | Tx Frequen<br>Word Profil<br>[1:0]                | le 0 LSBs                             | 0x00             | Read/Write |

| 0x0E             | 0                                       | 0                        | 0                               | 0                                                   |                                          | DAC Fine G                                        | ain Control [3                                    | 3:0]                                  | 0x00             | Read/Write |

| 0x0F             | 0                                       | 0                        | Tx Path<br>Select<br>Profile 1  | 0                                                   | Tx Path AD8322/ AD8327 Gain Control Mode | Tx Path<br>Bypass<br>Sinc <sup>-1</sup><br>Filter | Tx Path<br>Spectral<br>Inversion                  | Tx Path<br>Transmit<br>Single<br>Tone | 0x00             | Read/Write |

| 0x10             |                                         |                          | Tx Path F                       | requency T                                          | uning Word Profi                         | le 0 [9:2]                                        |                                                   |                                       | 0x00             | Read/Write |

| 0x11             |                                         |                          | Tx Path F                       | requency T                                          | uning Word Profi                         | le 0 [17:10]                                      |                                                   |                                       | 0x00             | Read/Write |

| 0x12             |                                         |                          | Tx Path F                       | requency T                                          | uning Word Profi                         | le 0 [25:18]                                      |                                                   |                                       | 0x00             | Read/Write |

| 0x13             | Cable Driver A                          | Amplifier Coa            | rse Gain Co                     | ntrol Profile                                       | e 0 [7:4]                                | Fine Gain C                                       | ontrol Profile                                    | 0 [3:0]                               | 0x00             | Read/Write |

| 0x14             |                                         |                          | Tx Path F                       | requency T                                          | uning Word Profi                         | le 1 [9:2]                                        |                                                   |                                       | 0x00             | Read/Write |

| 0x15             |                                         |                          | Tx Path F                       | requency T                                          | uning Word Profi                         | le 1 [17:10]                                      |                                                   |                                       | 0x00             | Read/Write |

| 0x16             |                                         |                          | Tx Path F                       | requency T                                          | uning Word Profi                         | le 1 [25:18]                                      |                                                   |                                       | 0x00             | Read/Write |

| 0x17             | Cable Driver A                          | Amplifier Coa            | rse Gain Co                     | ntrol Profile                                       | e 1 [7:4]                                | Fine Gain C                                       | ontrol Profile                                    | 1 [3:0]                               | 0x00             | Read/Write |

$<sup>^{\</sup>rm 1}$  Register bits denoted with 0 must be programmed with a 0 each time that register is written.

### **REGISTER 0x00—INITIALIZATION**

### Bits 0-4: OSCIN Multiplier

This register field is used to program the on-chip multiplier (PLL) that generates the chip's high frequency system clock f<sub>SYSCLK</sub>. The value of M depends on the ADC clocking mode selected, as shown in Table 5.

Table 5.

| ADC Clock Select                   | М  |

|------------------------------------|----|

| 1, foscin                          | 8  |

| 0, f <sub>MCLK</sub> (PLL Derived) | 16 |

When using the AD9879 in systems where the Tx path and Rx path do not operate simultaneously, the value of M can be programmed from 1 to 31. The maximum f<sub>SYSCLK</sub> rate of 236 MHz must be observed, whatever value is chosen for M. When M is set to 1, the internal PLL is disabled and all internal clocks are derived directly from OSCIN.

### Bit 5: RESET

Writing a 1 to this bit resets the registers to their default values and restarts the chip. The  $\overline{RESET}$  bit always reads back 0. The bits in Register 0x00 are not affected by this software reset. A low level at the  $\overline{RESET}$  pin, however, would force all registers, including all bits in Register 0x00, to their default state.

### Bit 6: SPI Bytes LSB First

Active high indicates SPI serial port access of instruction byte and data registers are least significant bit (LSB) first. Default low indicates most significant bit (MSB) first format.

### Bit 7: SDIO Bidirectional

Active high configures the serial port as a three-signal port with the SDIO pin used as a bidirectional input/output pin. Default low indicates the serial port uses four signals with SDIO configured as an input and SDO configured as an output.

# REGISTER 0x01—CLOCK CONFIGURATION Bits 0-5: MCLK/REFCLK Ratio

This bit field defines R, the ratio between the auxiliary clock output, REFCLK and MCLK. R can be any integer number between 2 and 63. At default zero (R=0), REFCLK provides a buffered version of the OSCIN clock signal.

### Bit 7: PLL Lock Detect

When this bit is set low, the REFCLK pin functions in its default mode and provides an output clock with frequency  $f_{\text{MCLK}}/R$ , as described above.

If this bit is set to 1, the REFCLK pin is configured to indicate whether the PLL is locked to  $f_{OSCIN}.$  In this mode, the REFCLK pin should be low-pass filtered with an RC filter of 1.0 k $\Omega$  and 0.1  $\mu F$ . A low output on REFCLK indicates the PLL has achieved lock with  $f_{OSCIN}$ .

### **REGISTER 0x02—POWER-DOWN**

Sections of the chip that are not used can be powered down when the corresponding bits are set high. This register has a default value of 0x00, with all sections active.

### Bit 0: Power-Down IQ ADC

Active high powers down the IQ ADC.

### Bit 1: Power-Down IQ and IF10 ADC Reference

Active high powers down the IQ and IF10 ADC reference.

### Bit 2: Power-Down IF10 ADC

Active high powers down the IF10 ADC.

#### Bit 3: Power-Down IF12 ADC Reference

Active high powers down the 12-bit ADC reference.

#### Bit 4: Power-Down IF12 ADC

Active high powers down the IF12 ADC.

### Bit 5: Power-Down Digital TX

Active high powers down the digital transmit section of the chip, similar to the function of the  $\overline{PWRDN}$  pin.

### **Bit 6: Power-Down DAC TX**

Active high powers down the DAC.

### Bit 7: Power-Down PLL

Active high powers down the OSCIN multiplier.

### REGISTERS 0x03-0x04—Σ-Δ AND FLAG CONTROL

The  $\Sigma$ - $\Delta$  control word is 12 bits wide and split into MSB bits [11:4] and LSB bits [3:0]. Changes to the  $\Sigma$ - $\Delta$  control words take effect immediately for every MSB or LSB register write.  $\Sigma$ - $\Delta$  output control words have a default value of 0. The control words are in straight binary format with 0x000 corresponding to the bottom of the scale and 0xFFF corresponding to the top of the scale. See Figure 8 for details.

If the flag enable (Register 0x03, Bit 0) is set high, the  $\Sigma$ - $\Delta$ \_OUT pin maintains a fixed logic level determined directly by the MSB of the  $\Sigma$ - $\Delta$  control word.

The FLAG1 pin assumes the logic level programmed into the FLAG1 bit (Register 0x03, Bit 1).

## REGISTER 0x07—VIDEO INPUT CONFIGURATION

### Bits 0-6: Clamp Level Control Value

The 7-bit clamp level control value is used to set an offset to the automatic clamp level control loop. The actual ADC output has a clamp level offset equal to 16 times the clamp level control value as shown:

Clamp Level Offset = Clamp Level Control Value  $\times$  16 (9)

The default value for the clamp level control value is 0x20. This results in an ADC output clamp level offset of 512 LSBs. The valid programming range for the clamp level control value is from 0x16 to 0x127.

# REGISTER 0x08—ADC CLOCK CONFIGURATION Bit 0: Send 10-Bit ADC Data Only

When this bit is set high, the device enters a nonmultiplexed mode and only the data from the 10-bit ADC is sent to the IF [11:0] digital output port.

### Bit 1: Send 12-Bit ADC Data Only

When this bit is set high, the device enters a nonmultiplexed mode and only data from the 12-bit ADC is sent to the IF [11:0] digital output port.

### Bit 3: Enable 7-Bits, IQ ADC

When this bit is active, the IQ ADC is put into 7-bit mode. In this mode, the full-scale input range is 2 Vppd. When this bit is set inactive, the IQ ADC is put into 6-bit mode and the full-scale input voltage range is 1 Vppd.

### Bit 4: Power-Down RXSYNC and IQ ADC Clocks

Setting this bit to 1 powers down the IQ ADC's sampling clock and stops the RXSYNC output pin. It can be used for additional power saving on top of the power-down selections in Register 0x02.

### Bit 5: Rx Port Fast Edge Rate

Setting this bit to 1 increases the output drive strength of all digital output pins, except MCLK, REFCLK,  $\Sigma$ - $\Delta$ \_OUT, and FLAG1. These pins always have high output drive capability.

### Bit 7: ADC Clocked Direct from OSCIN

When set high, the input clock at OSCIN is used directly as the ADC sampling clock. When set low, the internally generated master clock, MCLK, is divided by two and used as the ADC sampling clock. Best ADC performance is achieved when the ADCs are sampled directly from foscin using an external crystal or low jitter crystal oscillator.

### **REGISTER 0x0C—DIE REVISION**

### Bits 0-3: Version

The die version of the chip can be read from this register.

# REGISTER 0x0D—Tx FREQUENCY TUNING WORDS LSBs

This register accommodates two LSBs for both frequency tuning words. For more information, see the description in the Registers 0X10–0X17—Carrier Frequency Tuning section.

### REGISTER 0x0E—DAC GAIN CONTROL

### Bits 0-3: DAC Fine Gain Control

This bit field sets the DAC gain if the Tx Path AD8321/AD8323 gain control select bit (Register F, Bit 3) is set to 0. The DAC gain can be set from 0.0 dB to 7.5 dB in increments of 0.5 dB. Table 6 details the programming.

Table 6. DAC Gain Control

| Bits [3:0] | DAC Gain         |  |

|------------|------------------|--|

| 0000       | 0.0 dB (default) |  |

| 0001       | 0.5 dB           |  |

| 0010       | 1.0 dB           |  |

| 0011       | 1.5 dB           |  |

| ••••       |                  |  |