Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# High Voltage, Differential 18-Bit ADC Driver

Data Sheet ADA4922-1

#### **FEATURES**

Single-ended-to-differential conversion Low distortion ( $V_{O,\,dm}$  = 40 V p-p) -99 dBc HD at 100 kHz

Low differential output referred noise: 12 nV/√Hz

High input impedance: 11  $M\Omega$

Fixed gain of 2

No external gain components required

Low output-referred offset voltage: 1.1 mV maximum

Low input bias current: 3.5 µA maximum

Wide supply range

5 V to 26 V

Can produce differential output signals in excess of 40 V p-p High speed

38 MHz, -3 dB bandwidth at 0.2 V p-p differential output Fast settling time

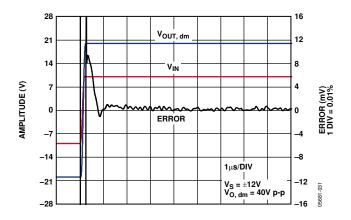

200 ns to 0.01% for 12 V step on  $\pm 5$  V supplies

Disable feature

Available in space-saving, thermally enhanced packages

8-lead, 3 mm × 3 mm LFCSP

8-lead SOIC

Low supply current:  $I_s = 10 \text{ mA on } \pm 12 \text{ V supplies}$

#### **APPLICATIONS**

**Medical instruments**

High voltage data acquisition systems Industrial instrumentation Spectrum analysis ATE

#### **GENERAL DESCRIPTION**

The ADA4922-1 is a differential driver for 16-bit to 18-bit analog-to-digital converters (ADCs) that have differential input ranges up to  $\pm 20$  V. Configured as an easy-to-use, single-ended-to-differential amplifier, the ADA4922-1 requires no external components to drive ADCs. The ADA4922-1 provides essential benefits such as low distortion and high SNR that are required for driving ADCs with resolutions up to 18 bits.

With a wide supply voltage range (5 V to 26 V), high input impedance, and fixed differential gain of 2, the ADA4922-1 is designed to drive ADCs found to in a variety of applications, including industrial instrumentation.

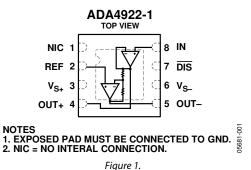

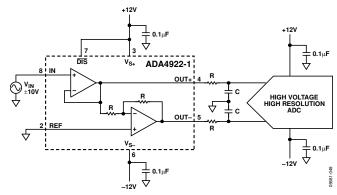

#### FUNCTIONAL BLOCK DIAGRAM

The ADA4922-1 is manufactured on Analog Devices, Inc., proprietary, second-generation XFCB process that enables the amplifier to achieve excellent noise and distortion performance on high supply voltages.

The ADA4922-1 is available in an 8-lead 3 mm  $\times$  3 mm LFCSP as well as an 8-lead SOIC package. Both packages are equipped with an exposed paddle for more efficient heat transfer. The ADA4922-1 is rated to work over the extended industrial temperature range,  $-40^{\circ}$ C to  $+85^{\circ}$ C.

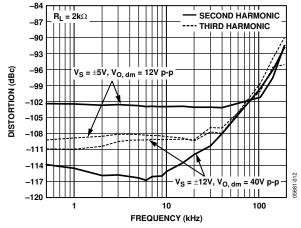

Figure 2. Harmonic Distortion for Various Power Supplies

Trademarks and registered trademarks are the property of their respective owners.

# ADA4922-1\* PRODUCT PAGE QUICK LINKS

Last Content Update: 02/23/2017

# COMPARABLE PARTS 🖵

View a parametric search of comparable parts.

# **EVALUATION KITS**

Universal Evaluation Board for Single Differential Amplifiers

# **DOCUMENTATION**

#### **Data Sheet**

ADA4922-1: High Voltage, Differential 18-Bit ADC Driver Data Sheet

#### **User Guides**

UG-474: Evaluation Board for Differential Amplifiers Offered in 8-Lead SOIC Packages

## TOOLS AND SIMULATIONS •

ADA4922-1 SPICE Macro Model

# REFERENCE MATERIALS 🖳

#### **Product Selection Guide**

- · Amplifiers for Video Distribution

- High Speed Amplifiers Selection Table

#### **Tutorials**

• MT-218: Multiple Feedback Band-Pass Design Example

# DESIGN RESOURCES 🖵

- · ADA4922-1 Material Declaration

- PCN-PDN Information

- · Quality And Reliability

- · Symbols and Footprints

## DISCUSSIONS 🖳

View all ADA4922-1 EngineerZone Discussions.

## SAMPLE AND BUY 🖳

Visit the product page to see pricing options.

# **TECHNICAL SUPPORT**

Submit a technical question or find your regional support number.

## DOCUMENT FEEDBACK $\Box$

Submit feedback for this data sheet.

# **TABLE OF CONTENTS**

| Features                                    | 1   |

|---------------------------------------------|-----|

| Applications                                | 1   |

| General Description                         | 1   |

| Functional Block Diagram                    | 1   |

| Revision History                            | . 2 |

| Specifications                              | 3   |

| Absolute Maximum Ratings                    | 5   |

| Thermal Resistance                          | 5   |

| Maximum Power Dissipation                   | 5   |

| ESD Caution                                 | 5   |

| Pin Configuration and Function Descriptions | 6   |

| Typical Performance Characteristics         | . 7 |

| Theory of Operation14                          |

|------------------------------------------------|

| Applications Information                       |

| ADA4922-1 Differential Output Noise Model 16   |

| Using the REF Pin                              |

| Internal Feedback Network Power Dissipation 17 |

| Disable Feature                                |

| Driving a Differential Input ADC17             |

| Printed Circuit Board Layout Considerations    |

| Outline Dimensions                             |

| Ordering Guide19                               |

#### **REVISION HISTORY**

#### 5/2016—Rev. 0 to Rev. A

| Change CP-8-2 to CP-8-13   | Throughout |

|----------------------------|------------|

| Changes to Figure 1        | 1          |

| Changes to Figure 4        |            |

| Updated Outline Dimensions |            |

| Changes to Ordering Guide  |            |

10/2005—Revision 0: Initial Version

# **SPECIFICATIONS**

$V_S=\pm 12~V,\, T_A=25^{\circ}C,\, R_L=1~k\Omega,\, \overline{DIS}=high,\, C_L=3~pF,\, unless~otherwise~noted.$

Table 1.

| Parameter                                | Test Conditions/Comments                                                          | Min    | Тур        | Max  | Unit   |

|------------------------------------------|-----------------------------------------------------------------------------------|--------|------------|------|--------|

| DYNAMIC PERFORMANCE                      |                                                                                   |        |            |      |        |

| –3 dB Bandwidth                          | $G = +2$ , $V_0 = 0.2 \text{ V p-p}$ , differential                               | 34     | 38         |      | MHz    |

|                                          | $G = +2$ , $V_0 = 40$ V p-p, differential                                         | 6.5    | 7.2        |      | MHz    |

| Overdrive Recovery Time                  | $V_{S+} + 0.5 \text{ V to } V_{S-} - 0.5 \text{ V}$ ; +recovery/-recovery         |        | 180/330    |      | ns     |

| Slew Rate                                | $V_{O, dm} = 2 V step$                                                            |        | 260        |      | V/µs   |

|                                          | $V_{O, dm} = 40 \text{ V step}$                                                   |        | 730        |      | V/µs   |

| Settling Time to 0.01%                   | $V_{O, dm} = 40 \text{ V step}$                                                   |        | 580        |      | ns     |

| NOISE/DISTORTION PERFORMANCE             |                                                                                   |        |            |      |        |

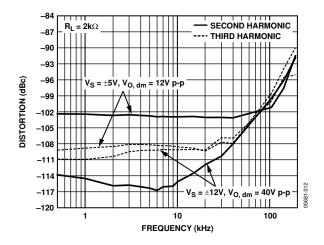

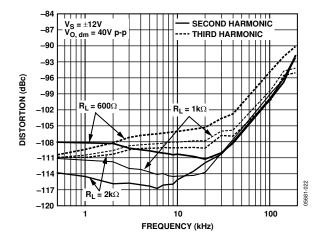

| Harmonic Distortion                      | $f_C = 5 \text{ kHz}, V_O = 40 \text{ V p-p}, R_L = 2 \text{ k}\Omega, HD2/HD3$   |        | -116/-109  |      | dBc    |

|                                          | $f_C = 100 \text{ kHz}, V_O = 40 \text{ V p-p}, R_L = 2 \text{ k}\Omega, HD2/HD3$ |        | -99/-100   |      | dBc    |

| Differential Output Voltage Noise        | f = 100 kHz                                                                       |        | 12         |      | nV/√H: |

| Input Current Noise                      | f = 100 kHz                                                                       |        | 1.4        |      | pA/√H  |

| DC PERFORMANCE                           |                                                                                   |        |            |      | -      |

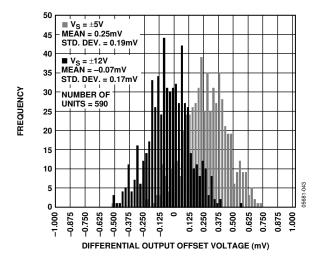

| Differential Output Offset Voltage       |                                                                                   |        | 0.35       | 1.1  | mV     |

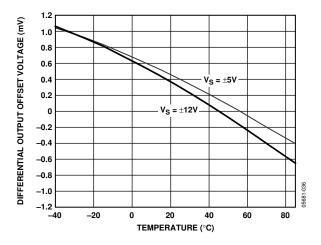

| Differential Output Offset Voltage Drift |                                                                                   |        | 14         |      | μV/°C  |

| Input Bias Current                       |                                                                                   |        | 1.8        | 3.5  | μA     |

| Gain                                     |                                                                                   |        | 2          |      | V/V    |

| Gain Error                               |                                                                                   |        | -0.05      |      | %      |

| Gain Error Drift                         |                                                                                   |        | 0.0002     |      | %/°C   |

| INPUT CHARACTERISTICS                    |                                                                                   |        |            |      |        |

| Input Resistance                         |                                                                                   |        | 11         |      | ΜΩ     |

| Input Capacitance                        |                                                                                   |        | 1          |      | рF     |

| Input Voltage Range                      |                                                                                   |        | ±10.7      |      | V      |

| OUTPUT CHARACTERISTICS                   |                                                                                   |        |            |      |        |

| Output Voltage Swing                     | Each single-ended output, $R_L = 1 \text{ k}\Omega$                               | ±10.65 | ±10.7      |      | V      |

| DC Output Current                        |                                                                                   |        | 40         |      | mA     |

| Capacitive Load Drive                    | 30% overshoot                                                                     |        | 20         |      | рF     |

| POWER SUPPLY                             |                                                                                   |        |            |      |        |

| Operating Range                          |                                                                                   | 5      |            | 26   | V      |

| Quiescent Current                        |                                                                                   |        | 9.4        | 10.1 | mA     |

| Quiescent Current (Disabled)             |                                                                                   |        | 1.5        | 2.0  | mA     |

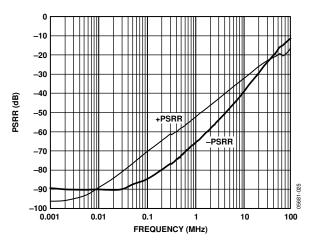

| Power Supply Rejection Ratio (PSRR)      |                                                                                   |        |            |      |        |

| –PSRR                                    |                                                                                   |        | -89        | -80  | dB     |

| +PSRR                                    |                                                                                   |        | <b>-91</b> | -83  | dB     |

| DISABLE                                  |                                                                                   |        |            |      |        |

| DIS Input Voltage Threshold              | Disabled                                                                          |        | ≤ −11      |      | V      |

| , 3                                      | Enabled                                                                           |        | ≥ -9       |      | V      |

| Turn-Off Time                            |                                                                                   |        | 160        |      | μs     |

| Turn-On Time                             |                                                                                   |        | 78         |      | ns     |

| DIS Bias Current                         |                                                                                   |        | -          |      |        |

| Enabled                                  | $\overline{\rm DIS} = -9  \rm V$                                                  |        | 114        |      | μΑ     |

| Disabled                                 | $\frac{DIS}{DIS} = -11 \text{ V}$                                                 |        | -125       |      | μΑ     |

| הואמטוכע                                 | עוט = – נוט – – נוט                                                               |        | -123       |      | μΛ     |

$V_S=\pm 5$  V,  $T_A=25$ °C,  $R_L=1$  k $\Omega$ ,  $\overline{DIS}=$  high,  $C_L=3$  pF, unless otherwise noted.

Table 2.

| Parameter                                | Test Conditions/Comments                                                          | Min   | Тур               | Max | Unit   |

|------------------------------------------|-----------------------------------------------------------------------------------|-------|-------------------|-----|--------|

| DYNAMIC PERFORMANCE                      |                                                                                   |       |                   |     |        |

| –3 dB Bandwidth                          | $G = +2$ , $V_0 = 0.2 \text{ V p-p}$ , differential                               | 36    | 40.5              |     | MHz    |

|                                          | $G = +2$ , $V_0 = 12 \text{ V p-p}$ , differential                                | 6.5   | 13.5              |     | MHz    |

| Overdrive Recovery Time                  | +Recovery/–Recovery                                                               |       | 200/670           |     | ns     |

| Slew Rate                                | $V_{O, dm} = 2 V step$                                                            |       | 220               |     | V/µs   |

|                                          | $V_{O, dm} = 12 V step$                                                           |       | 350               |     | V/µs   |

| Settling Time to 0.01%                   | $V_{O,dm} = 12 V step$                                                            |       | 200               |     | ns     |

| NOISE/DISTORTION PERFORMANCE             |                                                                                   |       |                   |     |        |

| Harmonic Distortion                      | $f_C = 5 \text{ kHz}, V_O = 12 \text{ V p-p}, R_L = 2 \text{ k}\Omega, HD2/HD3$   |       | -102/-108         |     | dBc    |

|                                          | $f_C = 100 \text{ kHz}, V_O = 12 \text{ V p-p}, R_L = 2 \text{ k}\Omega, HD2/HD3$ |       | -101/-98          |     | dBc    |

| Differential Output Voltage Noise        | f = 100 kHz                                                                       |       | 12                |     | nV/√Hz |

| Input Current Noise                      | f = 100 kHz                                                                       |       | 1.4               |     | pA/√Hz |

| DC PERFORMANCE                           |                                                                                   |       |                   |     |        |

| Differential Output Offset Voltage       |                                                                                   |       | 0.4               | 1.2 | mV     |

| Differential Output Offset Voltage Drift |                                                                                   |       | 12                |     | μV/°C  |

| Input Bias Current                       |                                                                                   |       | 2.0               | 3.5 | μΑ     |

| Gain                                     |                                                                                   |       | 2                 |     | V/V    |

| Gain Error                               |                                                                                   |       | -0.05             |     | %      |

| Gain Error Drift                         |                                                                                   |       | 0.0002            |     | %/°C   |

| INPUT CHARACTERISTICS                    |                                                                                   |       |                   |     |        |

| Input Resistance                         |                                                                                   |       | 11                |     | ΜΩ     |

| Input Capacitance                        |                                                                                   |       | 1                 |     | рF     |

| Input Voltage Range                      |                                                                                   |       | ±3.6              |     | V      |

| OUTPUT CHARACTERISTICS                   |                                                                                   |       |                   |     |        |

| Output Voltage Swing                     | Each single-ended output, $R_L = 1 \text{ k}\Omega$                               | ±3.55 | ±3.6              |     | V      |

| DC Output Current                        |                                                                                   |       | 40                |     | mA     |

| Capacitive Load Drive                    | 30% overshoot                                                                     |       | 20                |     | рF     |

| POWER SUPPLY                             |                                                                                   |       |                   |     | -      |

| Operating Range                          |                                                                                   | 5     |                   | 26  | V      |

| Quiescent Current                        |                                                                                   |       | 7.0               | 7.6 | mA     |

| Quiescent Current (Disabled)             |                                                                                   |       | 0.7               | 1.6 | mA     |

| Power Supply Rejection Ratio (PSRR)      |                                                                                   |       |                   |     |        |

| -PSRR                                    |                                                                                   |       | <b>-93</b>        | -82 | dB     |

| +PSRR                                    |                                                                                   |       | <b>–91</b>        | -83 | dB     |

| DISABLE                                  |                                                                                   |       |                   |     |        |

| DIS Input Voltage                        | Disabled                                                                          |       | ≤ -4              |     | V      |

| . 5                                      | Enabled                                                                           |       | ≥ -2              |     | V      |

| Turn-Off Time                            |                                                                                   |       | _ <b>_</b><br>160 |     | μs     |

| Turn-On Time                             |                                                                                   |       | 78                |     | ns     |

| DIS Bias Current                         |                                                                                   |       |                   |     |        |

| Enabled                                  | $\overline{DIS} = -2 \text{ V}$                                                   |       | 41                |     | μΑ     |

| Disabled                                 | $\frac{\text{DIS} - 2\text{V}}{\text{DIS} = -4\text{V}}$                          |       | 49                |     | μΑ     |

## **ABSOLUTE MAXIMUM RATINGS**

Table 3.

| Parameter                           | Rating          |

|-------------------------------------|-----------------|

| Supply Voltage                      | 26 V            |

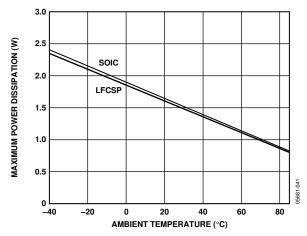

| Power Dissipation                   | See Figure 3    |

| Storage Temperature Range           | −65°C to +125°C |

| Operating Temperature Range         | −40°C to +85°C  |

| Lead Temperature (Soldering 10 sec) | 300°C           |

| Junction Temperature                | 150°C           |

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

#### THERMAL RESISTANCE

$\theta_{JA}$  is specified for the worst-case conditions, that is,  $\theta_{JA}$  is specified for a device soldered in the circuit board with its exposed paddle soldered to a pad on the PCB surface that is thermally connected to a copper plane, with zero airflow.

**Table 4. Thermal Resistance**

| Package Type                          | <b>Ө</b> ЈА | θ,ς | Unit |

|---------------------------------------|-------------|-----|------|

| 8-Lead SOIC with EP on 4-Layer Board  | 79          | 25  | °C/W |

| 8-Lead LFCSP with EP on 4-Layer Board | 81          | 17  | °C/W |

#### **MAXIMUM POWER DISSIPATION**

The maximum safe power dissipation in the ADA4922-1 package is limited by the associated rise in junction temperature (T<sub>J</sub>) on the die. At approximately 150°C, which is the glass transition temperature, the plastic changes its properties. Even temporarily exceeding this temperature limit can change the stresses that the package exerts on the die, permanently shifting the parametric performance of the ADA4922-1. Exceeding a junction temperature of 150°C for an extended period can result in changes in the silicon devices potentially causing failure.

The power dissipated in the package ( $P_D$ ) is the sum of the quiescent power dissipation and the power dissipated in the package due to the load drive for all outputs. The quiescent power is the voltage between the supply pins ( $V_S$ ) times the quiescent current ( $I_S$ ). The power dissipated due to the load drive depends upon the particular application. For each output, the power due to load drive is calculated by multiplying the load current by the associated voltage drop across the device. The power dissipated due to all of the loads is equal to the sum of the power dissipation due to each individual load. RMS voltages and currents must be used in these calculations.

Airflow increases heat dissipation, effectively reducing  $\theta_{JA}$ . In addition, more metal directly in contact with the package leads from metal traces, through holes, ground, and power planes reduces the  $\theta_{JA}$ . The exposed paddle on the underside of the package must be soldered to a pad on the PCB surface that is thermally connected to a copper plane to achieve the specified  $\theta_{JA}$ .

Figure 3 shows the maximum safe power dissipation in the packages vs. the ambient temperature for the 8-lead SOIC (79°C/W) and for the 8-lead LFCSP (81°C/W) on a JEDEC standard 4-layer board, each with its underside paddle soldered to a pad that is thermally connected to a PCB plane.  $\theta_{JA}$  values are approximations.

Figure 3. Maximum Power Dissipation vs. Temperature for a 4-Layer Board

#### **ESD CAUTION**

ESD (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

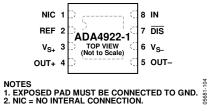

# PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Figure 4. Pin Configuration

**Table 5. Pin Function Descriptions**

| Pin No. | Mnemonic | Description                                     |

|---------|----------|-------------------------------------------------|

| 1       | NIC      | No Internal Connection                          |

| 2       | REF      | Reference Voltage for Single-Ended Input Signal |

| 3       | $V_{S+}$ | Positive Power Supply                           |

| 4       | OUT+     | Noninverting Side of Differential Output        |

| 5       | OUT-     | Inverting Side of Differential Output           |

| 6       | $V_{S-}$ | Negative Power Supply                           |

| 7       | DIS      | Disable                                         |

| 8       | IN       | Single-Ended Signal Input                       |

# TYPICAL PERFORMANCE CHARACTERISTICS

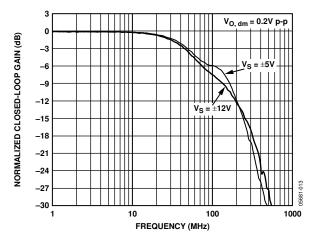

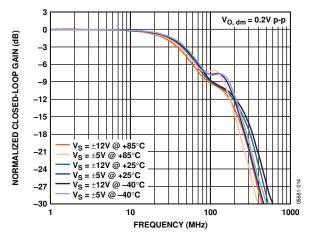

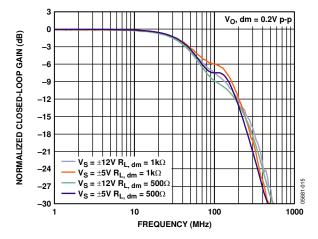

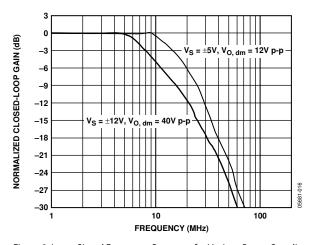

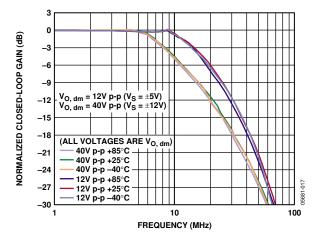

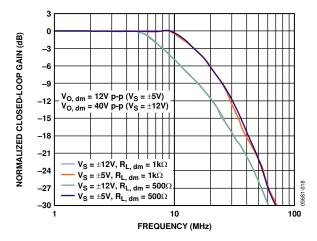

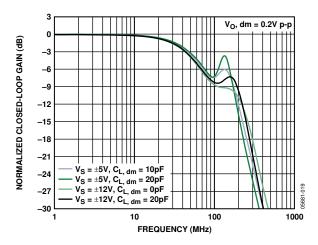

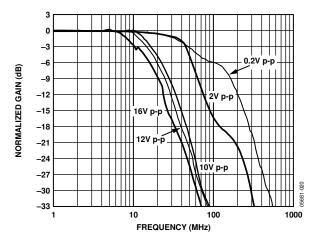

Unless otherwise noted,  $V_S = \pm 12 \text{ V}$ ,  $R_{L, dm} = 1 \text{ k}\Omega$ , REF = 0 V,  $\overline{DIS} = \text{high}$ ,  $T_A = 25^{\circ}\text{C}$ .

Figure 5. Small Signal Frequency Response for Various Power Supplies

Figure 6. Small Signal Frequency Response for Various Temperatures and Supplies

Figure 7. Small Signal Frequency Response for Various Resistive Loads and Supplies

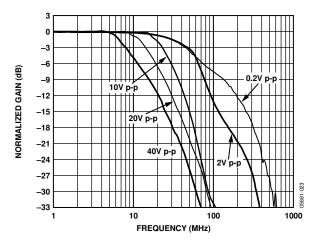

Figure 8. Large Signal Frequency Response for Various Power Supplies

Figure 9. Large Signal Frequency Response at Various Temperatures and Supplies

Figure 10. Large Signal Frequency Response for Various Resistive Loads and Supplies

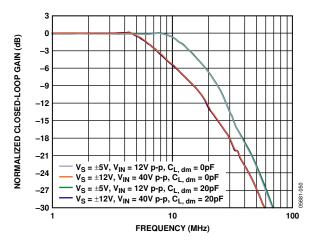

Figure 11. Small Signal Frequency Response for Various Capacitive Loads

Figure 12. Frequency Response for Various Output Amplitudes,  $V_S = \pm 5 V$

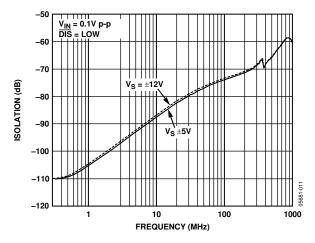

Figure 13. Isolation vs. Frequency—Disabled

Figure 14. Large Signal Frequency Response for Various Capacitive Loads

Figure 15. Frequency Response for Various Output Amplitudes,  $V_S = \pm 12 \text{ V}$

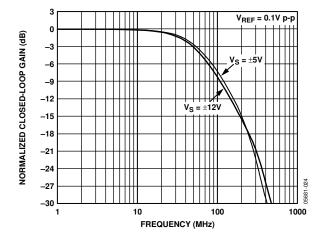

Figure 16. REF Small Signal Frequency Response for Various Power Supplies

Figure 17. Harmonic Distortion for Various Power Supplies

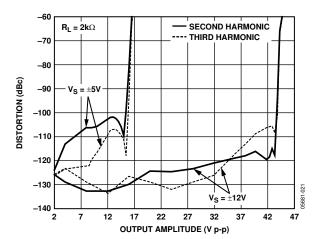

Figure 18. Harmonic Distortion vs. Output Amplitude and Supply Voltage (f=10 kHz)

Figure 19. PSRR vs. Frequency

Figure 20. Harmonic Distortion for Various Loads

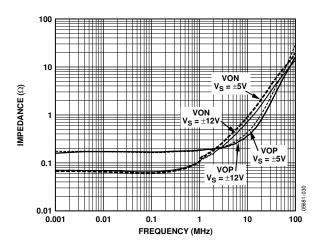

Figure 21. Single-Ended Output Impedance vs. Frequency and Supplies

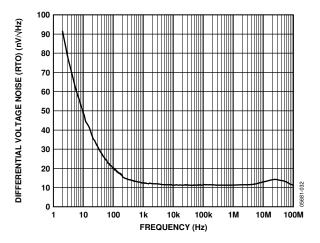

Figure 22. Differential Output Noise vs. Frequency

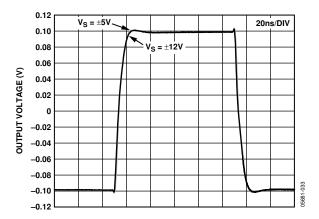

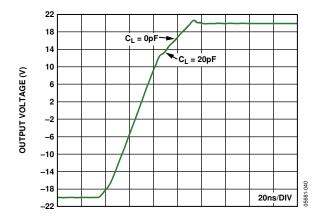

Figure 23. Small Signal Transient Response for Various Power Supplies

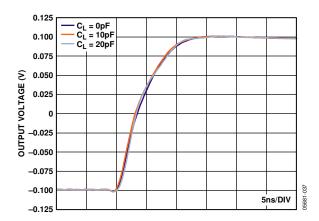

Figure 24. Small Signal Transient Response for Various Capacitive Loads

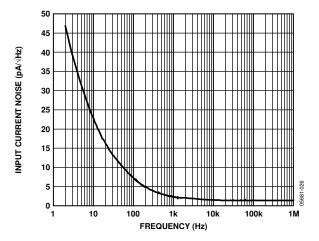

Figure 25. Input Current Noise vs. Frequency

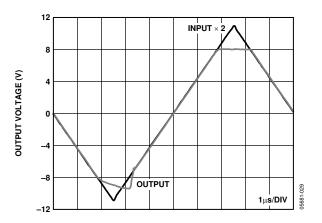

Figure 26. Large Signal Transient Response for Various Power Supplies

Figure 27. Large Signal Transient Response for Various Capacitive Loads

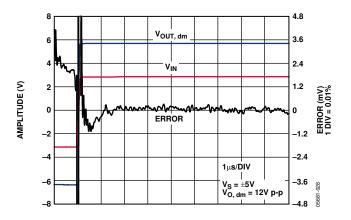

Figure 28. Settling Time,  $V_S = \pm 5 V$

Figure 29. Input Overdrive Recovery,  $V_S = \pm 5 V$

Figure 30. Differential Output Offset Voltage vs. Temperature

Figure 31. Settling Time,  $V_S = \pm 12 V$

Figure 32. Input Overdrive Recovery,  $V_S = \pm 12 V$

Figure 33. Differential Output Offset Voltage Distribution

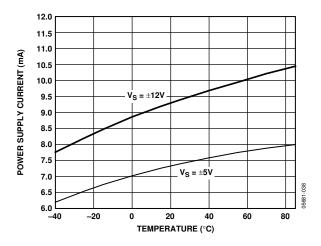

Figure 34. Power Supply Current vs. Temperature

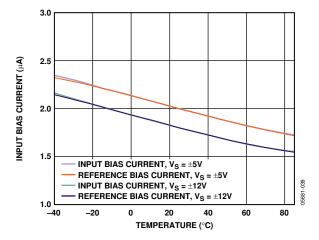

Figure 35. Input Bias Current vs. Temperature

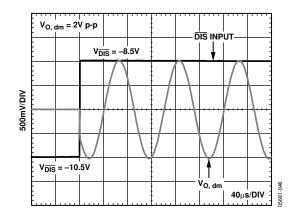

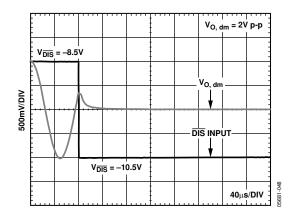

Figure 36. Disable Turn-On Time

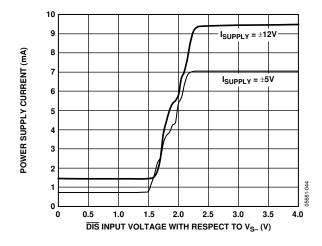

Figure 37. Power Supply Current vs. Disable Input Voltage

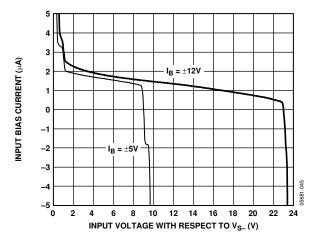

Figure 38. Input Bias Current vs. Input Voltage

Figure 39. Disable Turn-Off Time

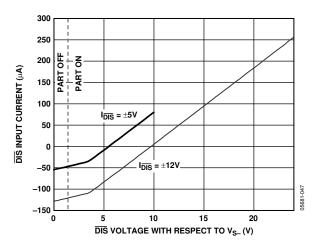

Figure 40. Disable Current vs. Disable Voltage

## THEORY OF OPERATION

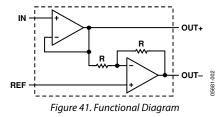

The ADA4922-1 is dual amplifier that has been optimized to drive a differential ADC from a single-ended input source with a minimum number of external components (see Figure 41).

The differential output voltage is defined as

$$V_{O,dm} = V_{OUT+} - V_{OUT-} \tag{1}$$

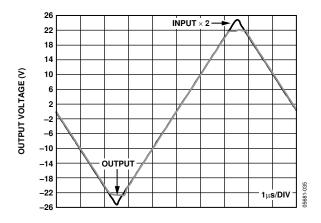

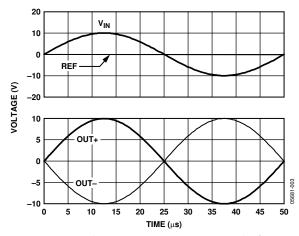

Each amplifier in Figure 41 is identical, and the value of Resistor R is set at 600  $\Omega$ , yielding an optimal trade-off between output differential noise, internal power dissipation, and overall system linearity. For basic operation, the REF input is tied to the midswing level of the input signal, which is often midsupply. The input signal (referenced to REF) produces a differential output signal with an overall gain of +2. Figure 42 shows typical operation on  $\pm 12$  V supplies with the source referenced to 0 V and the REF pin tied to 0 V.

Figure 42. Typical Input/Output Response—Centered Reference

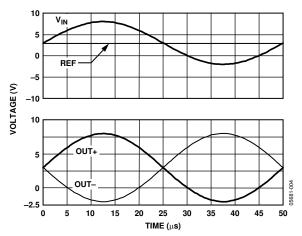

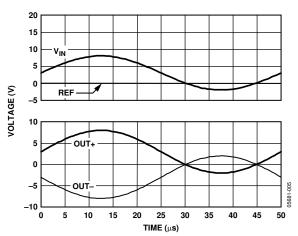

If an application uses an input midswing voltage other than midsupply, the REF pin needs to be offset to the input midswing level to obtain outputs that do not exhibit a differential offset (see Figure 43). If the voltage applied to the REF pin is different from the midswing level of the input signal, a dc offset is created between outputs  $V_{\rm OUT^+}$  and  $V_{\rm OUT^-}$ . Figure 44 illustrates this condition when the input signal is referenced to a positive level, and the REF pin is connected to 0 V.

Figure 43. Typical Input/Output Response—Equal Input/Reference

Figure 44. Typical Input/Output Response—Unequal Input/Reference

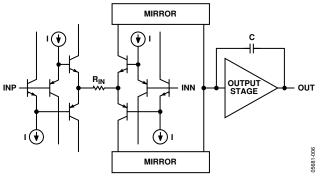

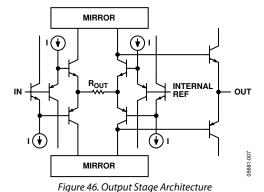

A more detailed view of the amplifier is shown in Figure 45. Each amplifier is a 2-stage design that uses an input H-Bridge followed by a rail-to-rail output stage (see Figure 46).

Figure 45. Internal Amplifier Architecture

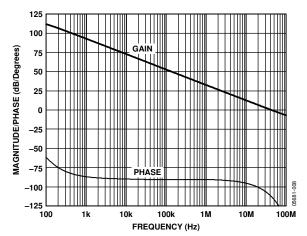

Figure 47 illustrates the open-loop gain and phase relationships of each amplifier in the ADA4922-1.

Figure 47. Amplifier Gain/Phase Relationship

The architecture used in the ADA4922-1 results in excellent SNR and distortion performance when compared to other differential amplifiers.

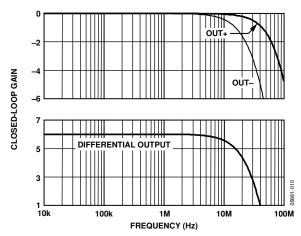

One of the more subtle points of operation arises when the two amplifiers are used to generate the differential outputs. Because the differential outputs are derived from a follower amplifier and an inverting amplifier, they have different noise gains and, therefore, different closed-loop bandwidths. For frequencies up to 1 MHz, the bandwidth difference between outputs causes little difference in the overall differential output performance. However, because the bandwidth is the sum of both amplifiers, the 3 dB point of the inverting amplifier defines the overall differential 3 dB corner (see Figure 48).

Figure 48. Closed-Loop AC Gain (Differential Outputs)

Small delay and gain errors exist between the two outputs because the inverting output is derived from the noninverting output through an inverting amplifier. The gain error is due to imperfect matching of the inverting amplifier gain and feedback resistors, as well as differences in the transfer functions of the two amplifiers, as illustrated in Figure 48. The delay error is due to the delay through the inverting amplifier relative to the noninverting amplifier output. The delay produces a reduction in differential gain because the two outputs are not exactly 180° out of phase. Both of these errors combine to produce an overall gain error because the outputs are completely balanced. This error is very small at the frequencies involved in most ADA4922-1 applications.

## APPLICATIONS INFORMATION

The ADA4922-1 is a fixed-gain, single-ended-to-differential voltage amplifier, optimized for driving high resolution ADCs in high voltage applications. There are no gain adjustments available to the user.

#### **ADA4922-1 DIFFERENTIAL OUTPUT NOISE MODEL**

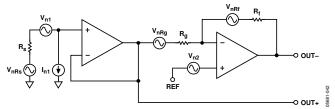

The principal noise sources in a typical ADA4922-1 application circuit are shown in Figure 49.

Figure 49. ADA4922-1 Differential Output Noise Model

Using the traditional approach, a noise source is applied in series with one of the inputs of each op amp to model input-referred voltage noise. The input current noise that matters the most is present at the input pin. The output voltage noise due to this noise current depends on the source resistance feeding the input, as well as the downstream gain in the amplifier. Resistor noise is modeled by placing a noise voltage source in series with a noiseless resistor.  $R_{\rm f}$  and  $R_{\rm g}$  are both 600  $\Omega$  and therefore have the same noise voltage density.

At room temperature,

$$V_{nRg} = V_{nRf} = \sqrt{4 \text{ kT} (600 \Omega)} \approx 3.2 \text{ nV} / \sqrt{\text{Hz}}$$

(2)

The noise at OUT+ is due to the input-referred current and voltage noise sources of the noninverting amplifier and the noise of the source resistance, all reflected to the output with a noise gain of 1, and is equal to:

Voltage Noise @ OUT+:

$$V_{n1} + R_S(I_{n1}) + V_{nRs}$$

(3)

where  $R_S$  is the source resistance feeding the input, and  $V_{nRS}$  is the source resistance noise.

The noise at OUT- originates from a number of sources:

Voltage Noise @ OUT- due to

$$V_{nl}$$

:  $V_{nl} \left( \frac{-R_f}{R_g} \right) = -V_{nl}$  (4)

Voltage Noise @ OUT- due to

$$I_{n1}$$

:  $R_{S}(I_{n1})\left(\frac{-R_{f}}{R_{g}}\right) = -R_{S}(I_{n1})$  (5)

Voltage Noise @ OUT- due to Rs:

$$V_{nRs} \left( \frac{-R_f}{R_g} \right) = -V_{nRs}$$

(6)

Voltage Noise @ OUT- due to

$$V_{nRg}$$

:  $V_{nRg} \left( \frac{-R_f}{R_g} \right) = -V_{nRg}$  (7)

Voltage Noise @ OUT – due to

$$V_{nRf}$$

:  $V_{nRF}$  (8)

Voltage Noise @ OUT- due to

$$V_{n2}$$

:  $V_{n2} \left( 1 + \frac{R_f}{R_g} \right) = 2V_{n2}$  (9)

When looking at OUT– by itself, the contributing noise sources are uncorrelated, and therefore, the total output noise is calculated as the root-sum-square (rss) of the individual contributors. When looking at the differential output noise, the noise contributors are uncorrelated except for three,  $V_{\rm nl},\,R_{\rm S}(I_{\rm nl}),$  and  $V_{\rm nRs},$  which are common noise sources for both outputs. It can be seen from the previous results that the output noise due to  $V_{\rm nl},\,R_{\rm S}(I_{\rm nl}),$  and  $V_{\rm nRs}$  each appear at OUT+ with a gain of +1 and at OUT– with a gain of –1. This produces a gain of 2 for each of these three sources at the differential output.

The total differential output noise density is calculated as

$V_{on,dm} =$

$$\sqrt{(2(V_n + R_s(1.4 \text{ pA}/\sqrt{\text{Hz}}) + V_{nRs}))^2 + 2(3.2 \text{ nV}/\sqrt{\text{Hz}})^2 + 4V_n^2}$$

(10)

where  $V_{n1} = V_{n2} \equiv V_n = 3.9 \text{ nV/}\sqrt{\text{Hz}}$ ; the input referred voltage noise of each amplifier is the same.

The output noise due to the amplifier alone is calculated by setting  $R_S$  and  $V_{nRs}$  equal to zero. In this case:

$$V_{on, dm} = 12 \text{ nV/}\sqrt{\text{Hz}} \tag{11}$$

Clearly, the output noise is not balanced between the outputs, but this is not an issue in most applications.

#### **USING THE REF PIN**

The REF pin sets the output baseline in the inverting path and is used as a reference for the input signal. In most applications, the REF pin is set to the input signal midswing level, which in many cases is also midsupply. For bipolar signals and power supplies, REF is generally set to ground. In single-supply applications, setting REF to the input signal midswing level provides optimal output dynamic range performance with minimum differential offset. Note that the REF input only affects the inverting signal path, or OUT—.

Most applications require a differential output signal with the same dc common-mode level on each output. It is possible for the signal measured across OUT+ and OUT- to have a common-mode voltage that is of the desired level but has different dc levels at both outputs. Typically, this situation is avoided, because it wastes the output dynamic range of the amplifier.

Defining  $V_{\rm IN}$  as the voltage applied to the input pin, the equations that govern the two signal paths are given in Equation 12 and Equation 13.

$$V_{OUT+} = +V_{IN} \tag{12}$$

$$V_{OUT-} = -V_{IN} + 2(REF) (13)$$

When the REF voltage is set to the midswing level of the input signal, the two output signals fall directly on top of each other with minimal offset. Setting the REF voltage elsewhere results in an offset between the two outputs. This effect is illustrated in the Theory of Operation section.

The best use of the REF pin can be further illustrated by considering a single-supply example that uses a 10 V dc power supply and has an input signal that varies between 2 V and 7 V. This is a case where the midswing level of the input signal is not at midsupply but is at 4.5 V. By setting the REF input to 4.5 V and neglecting offsets, Equation 12 and Equation 13 are used to calculate the results. When the input signal is at its midpoint of 4.5 V, V<sub>OUT+</sub> is at 4.5 V, as is V<sub>OUT-</sub>. This can be considered as a type of baseline state where the differential output voltage is zero. When the input increases to 7 V,  $V_{\text{OUT+}}$  tracks the input to 7 V and V<sub>OUT</sub> decreases to 2 V. This can be viewed as a positive peak signal where the differential output voltage equals 5 V. When the input signal decreases to 2 V, V<sub>OUT+</sub> again tracks to 2 V, and V<sub>OUT</sub> increases to 7 V. This can be viewed as a negative peak signal where the differential output voltage equals -5 V. The resulting differential output voltage is 10 V p-p.

The previous discussion exposes how the single-ended-to-differential gain of 2 is achieved.

# INTERNAL FEEDBACK NETWORK POWER DISSIPATION

While traditional op amps do not have on-chip feedback elements, the ADA4922-1 contains two on-chip 600  $\Omega$  resistors that comprise an internal feedback loop. The power dissipated in these resistors must be included in the overall power dissipation calculations for the device. Under certain circumstances, the power dissipated in these resistors could be considerably more than the quiescent current of the device. For example, on  $\pm 12~V$  supplies with the REF pin tied to ground and OUT– at 9 V dc, each 600  $\Omega$  resistor carries 15 mA and dissipates 135 mW. This is a significant amount of power and must therefore be included in the overall device power dissipation calculations. For ac signals, rms analysis is required.

#### **DISABLE FEATURE**

The ADA4922-1 includes a disable feature that can be asserted to minimize power consumption in a device that is not needed at a particular time. When asserted, the disable feature does not place the device output in a high impedance or three-state condition. The disable feature is asserted by applying a control voltage to the  $\overline{\rm DIS}$  pin and is active low. See the Specifications section for the high and low level voltage specifications.

#### **DRIVING A DIFFERENTIAL INPUT ADC**

The ADA4922-1 provides the single-ended-to-differential conversion that is required to drive most high resolution ADCs. Figure 50 shows how the ADA4922-1 simplifies ADC driving.

Figure 50. Driving a Differential Input ADC

For example, consider the case where the input signal bandwidth is 100 kHz and R = 41.2  $\Omega$  and C = 3.9 nF, as is shown in Figure 50, to form a single-pole filter with -3 dB bandwidth of approximately 1 MHz. The ADA4922-1 output noise (with zero source resistance) integrated over this bandwidth appears at the ADC input and is calculated as

$$V_{n, ADC, dm}(rms) = \left(12 \,\text{nV}/\sqrt{\text{Hz}}\right) \sqrt{\left(\frac{\pi}{2}\right) \left(1 \,\text{MHz}\right)} = 15 \,\mu\text{V rms} \qquad (14)$$

The rms value of a 20 V p-p signal at the ADC input is 7 V rms, yielding a SNR of 113 dB at the ADC input.

# PRINTED CIRCUIT BOARD LAYOUT CONSIDERATIONS

Although the ADA4922-1 is used in many applications involving frequencies that are well below 1 MHz, some general high speed layout practices must be adhered to because it is a high speed amplifier. Controlled impedance transmission lines are not required for low frequency signals, provided the signal rise times are longer than approximately 5 times the electrical delay of the interconnections. For reference, typical 50  $\Omega$  transmission lines on FR-4 material exhibit approximately

140 ps/in delay on outer layers and 180 ps/in for inner layers. Most connections between the ADA4922-1 and the ADC can be kept very short.

Place broadband power supply decoupling networks as close as possible to the supply pins. Small surface-mount ceramic capacitors are recommended for these networks, and tantalum capacitors are recommended for bulk supply decoupling.

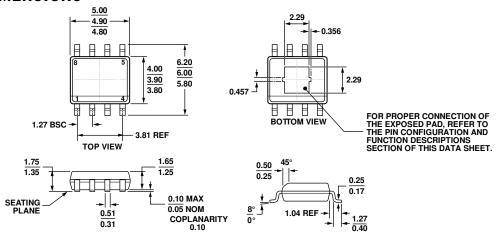

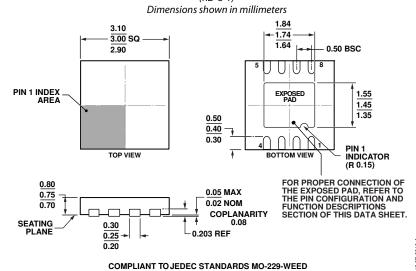

# **OUTLINE DIMENSIONS**

#### COMPLIANT TO JEDEC STANDARDS MS-012-A A

Figure 51. 8-Lead Standard Small Outline Package with Exposed Pad [SOIC\_N\_EP] Narrow Body (RD-8-1)

Figure 52. 8-Lead Lead Frame Chip Scale Package [LFCSP] 3 mm × 3 mm Body and 0.75 mm Package Height (CP-8-13) Dimensions shown in millimeters

#### **ORDERING GUIDE**

| Model <sup>1</sup> | Temperature Range | Package Description                                                | Package<br>Option | Branding |

|--------------------|-------------------|--------------------------------------------------------------------|-------------------|----------|

| ADA4922-1ARDZ      | −40°C to +85°C    | 8-Lead Standard Small Outline Package with Exposed Pad [SOIC_N_EP] | RD-8-1            |          |

| ADA4922-1ARDZ-RL   | −40°C to +85°C    | 8-Lead Standard Small Outline Package with Exposed Pad [SOIC_N_EP] | RD-8-1            |          |

| ADA4922-1ACPZ-R2   | -40°C to +85°C    | 8-Lead Lead Frame Chip Scale Package [LFCSP]                       | CP-8-13           | HUB      |

| ADA4922-1ACPZ-RL7  | -40°C to +85°C    | 8-Lead Lead Frame Chip Scale Package [LFCSP]                       | CP-8-13           | HUB      |

| ADA4922-1ACP-EBZ   |                   | Evaluation Board                                                   |                   |          |

<sup>&</sup>lt;sup>1</sup> Z = RoHS-Compliant Part.