Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

## SigmaDSP Digital Audio Processor

## **Data Sheet**

## ADAU1452/ADAU1451/ADAU1450

#### **FEATURES**

**Qualified for automotive applications**

Fully programmable audio DSP for enhanced sound processing Features SigmaStudio, a proprietary graphical programming tool for the development of custom signal flows

Up to 294.912 MHz, 32-bit SigmaDSP core at 1.2 V

Up to 6144 SIMD instructions per sample at 48 kHz

Up to 40 kWords of parameter/data RAM

Up to 800 ms digital audio delay pool at 48 kHz

Audio I/O and routing

4 serial input ports, 4 serial output ports

48-channel, 32-bit digital I/O up to a sample rate of 192 kHz Flexible configuration for TDM, I<sup>2</sup>S, left and right justified

formats, and PCM

Up to 8 stereo ASRCs from 1:8 up to 7.75:1 ratio and 139 dB DNR

Stereo S/PDIF input and output (not on the ADAU1450)

Four PDM microphone input channels

Multichannel, byte addressable TDM serial ports

Clock oscillator for generating master clock from crystal

Integer PLL and flexible clock generators

Integrated die temperature sensor

I<sup>2</sup>C and SPI control interfaces (both slave and master)

Standalone operation

**Self boot from serial EEPROM**

6-channel, 10-bit SAR auxiliary control ADC

14 multipurpose pins for digital controls and outputs

On-chip regulator for generating 1.2 V from 3.3 V supply

72-lead, 10 mm  $\times$  10 mm LFCSP package with 5.3 mm

exposed pad

Temperature range: -40°C to +105°C

#### **APPLICATIONS**

**Automotive audio processing**

Head units

**Navigation systems**

Rear seat entertainment systems

DSP amplifiers (sound system amplifiers)

Commercial and professional audio processing

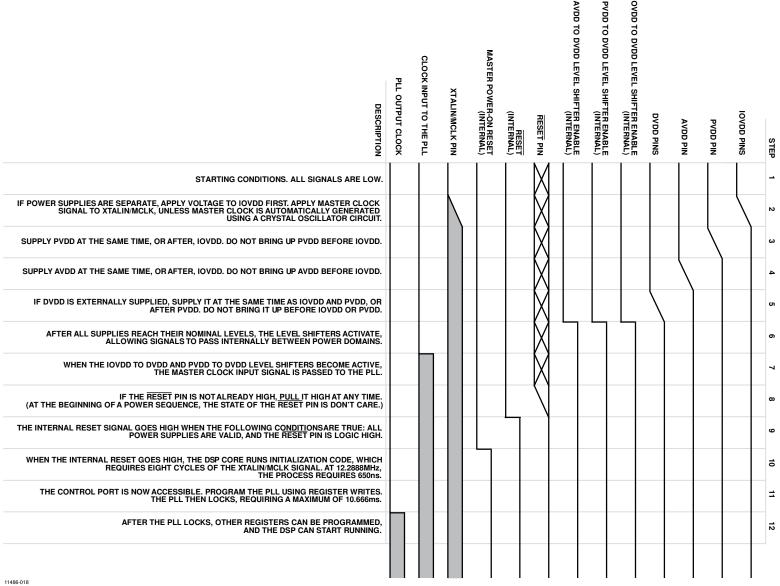

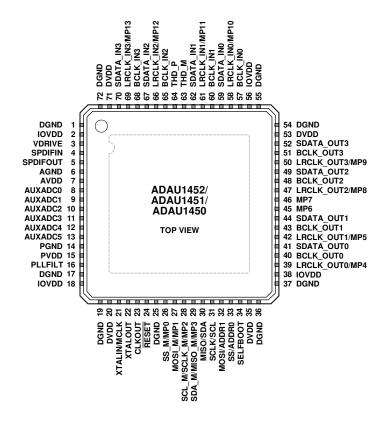

#### FUNCTIONAL BLOCK DIAGRAM—ADAU1452/ADAU1451

Figure 1.

## **Data Sheet**

## ADAU1452/ADAU1451/ADAU1450

## **TABLE OF CONTENTS**

| Features                                                 | 1  |

|----------------------------------------------------------|----|

| Applications                                             | 1  |

| Functional Block Diagram—ADAU1452/ADAU1451               | 1  |

| Revision History                                         | 3  |

| General Description                                      | 4  |

| Differences Between the ADAU1452, ADAU1451, and ADAU1450 | 4  |

| Functional Block Diagram—ADAU1450                        | 5  |

| Specifications                                           | 6  |

| Electrical Characteristics                               | 8  |

| Timing Specifications                                    | 9  |

| Absolute Maximum Ratings                                 | 17 |

| Thermal Characteristics                                  | 17 |

| Maximum Power Dissipation                                | 17 |

| ESD Caution                                              | 17 |

| Pin Configuration and Function Descriptions              | 18 |

| Theory of Operation                                      | 22 |

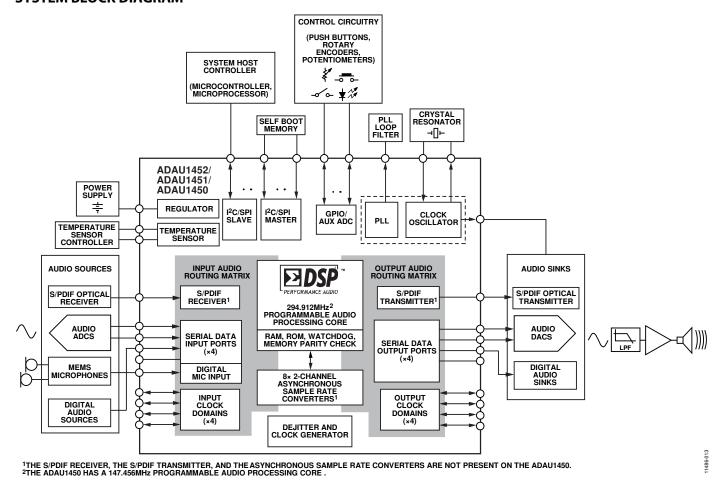

| System Block Diagram                                     | 22 |

| Overview                                                 | 22 |

| Initialization                                           | 24 |

| Master Clock, PLL, and Clock Generators                  | 27 |

| Power Supplies, Voltage Regulator, and Hardware Reset    | 32 |

| Temperature Sensor Diode                                 | 33 |

| Slave Control Ports                                      | 34 |

| Master Control Ports                                     | 40 |

| Self Boot                                                | 41 |

| Audio Signal Routing                                     | 43 |

| Serial Data Input/Output                                 | 53 |

| Flexible TDM Interface                                   | 64 |

| Asynchronous Sample Rate Converters                      | 69 |

| S/PDIF Interface                                         | 70 |

| Digital PDM Microphone Interface                         | 72 |

| Multipurpose Pins                                        | 73 |

| Auxiliary ADC76                                          |

|----------------------------------------------------------|

| SigmaDSP Core76                                          |

| Software Features                                        |

| Pin Drive Strength, Slew Rate, and Pull Configuration 81 |

| Global RAM and Control Register Map83                    |

| Random Access Memory                                     |

| Control Registers84                                      |

| Control Register Details                                 |

| PLL Configuration Registers94                            |

| Clock Generator Registers                                |

| Power Reduction Registers                                |

| Audio Signal Routing Registers105                        |

| Serial Port Configuration Registers111                   |

| Flexible TDM Interface Registers                         |

| DSP Core Control Registers118                            |

| Debug and Reliability Registers123                       |

| DSP Program Execution Registers                          |

| Multipurpose Pin Configuration Registers135              |

| ASRC Status and Control Registers140                     |

| Auxiliary ADC Registers143                               |

| S/PDIF Interface Registers                               |

| Hardware Interfacing Registers157                        |

| Soft Reset Register175                                   |

| Applications Information                                 |

| PCB Design Considerations176                             |

| Typical Applications Block Diagram177                    |

| Example PCB Layout                                       |

| PCB Manufacturing Guidelines179                          |

| Outline Dimensions                                       |

| Ordering Guide180                                        |

| Automotive Products 180                                  |

## **Data Sheet**

## ADAU1452/ADAU1451/ADAU1450

### **REVISION HISTORY**

| 7/14—Rev. B to Rev. C                                       |

|-------------------------------------------------------------|

| Changes to SCL_M/SCLK_M/MP2 Pin Description,                |

| Table 23                                                    |

| Change to PLL Lock Register Section96                       |

| Changes to Ordering Guide180                                |

| 5/14—Rev. A to Rev. B                                       |

| Reorganized Layout                                          |

| Added ADAU1452 and ADAU1451 Universal                       |

| Changes to Features Section                                 |

| Moved Revision History Section                              |

| Changes to General Description Section4                     |

| Added Differences Between the ADAU1452, ADAU1451, and       |

| ADAU1450 Section and Table 1, Renumbered Sequentially4      |

| Added Functional Block Diagram—ADAU1450 Section and         |

| Figure 2, Renumbered Sequentially5                          |

| Changes to Table 26                                         |

| Changes to Table 3                                          |

| Changes to Table 6                                          |

| Changes to Maximum Power Dissipation Section, Table 19,     |

| and Table 2017                                              |

| Added Table 21 and Table 2217                               |

| Changes to Figure 12 and Table 2318                         |

| Changes to Overview Section                                 |

| Change to Clocking Overview Section and Power-Up            |

| Sequence Section24                                          |

| Changes to Setting the Master Clock and PLL Mode Section 27 |

| Changes to Example PLL Settings Section and Table 2528      |

| Changed PLL Loop Filter Section to PLL Filter Section29     |

| Changes to PLL Filter Section, Figure 17 Caption, and       |

| Table 26                                                    |

| Changes to Clock Generators Section                     | 30  |

|---------------------------------------------------------|-----|

| Changes to Master Clock Output Section                  | 31  |

| Changes to I <sup>2</sup> C Slave Port Section          | 35  |

| Changes to Audio Signal Routing Section                 | 43  |

| Changes to Serial Audio Inputs to DSP Core Section      | 44  |

| Changes to Asynchronous Sample Rate Converter Input     |     |

| Routing Section                                         | 49  |

| Change to Serial Input Ports Section                    | 61  |

| Changes to Asynchronous Sample Rate Converters Section  | ı68 |

| Changes to S/PDIF Interface Section and S/PDIF Receiver |     |

| Section                                                 | 69  |

| Changes to Auxiliary Output Mode Section                | 70  |

| Change to Digital PDM Microphone Interface Section      | 71  |

| Changes to SigmaDSP Core Section                        | 76  |

| Changes to Soft Reset Function Section                  | 81  |

| Changes to Random Access Memory Section                 |     |

| Added Table 62 and Table 63                             | 83  |

| Changes to Table 84                                     | 109 |

| Changed PLL Loop Filter Section to PLL Filter Section   | 176 |

| Change to EOS/ESD Protection Section                    | 177 |

| Change to PCB Manufacturing Guidelines Section          |     |

| Changes to Ordering Guide                               | 180 |

|                                                         |     |

| 1/14—Rev O to Rev A                                     |     |

Changed S/PDIF Transceiver and Receiver Maximum Audio Sample Rate from 192 kHz to 96 kHz; Table 9 and Table 10......9

### 10/13—Revision 0: Initial Version

### **GENERAL DESCRIPTION**

The ADAU1452/ADAU1451/ADAU1450 are automotive qualified audio processors that far exceed the digital signal processing capabilities of earlier SigmaDSP® devices. The restructured hardware architecture is optimized for efficient audio processing. The audio processing algorithms are realized in sample-by-sample and block-by-block paradigms that can both be executed simultaneously in a signal processing flow created using the graphical programming tool, SigmaStudio™. The restructured digital signal processor (DSP) core architecture enables some types of audio processing algorithms to be executed using significantly fewer instructions than were required on previous SigmaDSP generations, leading to vastly improved code efficiency.

The 1.2 V, 32-bit DSP core can run at frequencies of up to 294.912 MHz and execute up to 6144 instructions per sample at the standard sample rate of 48 kHz. However, in addition to industry standard rates, a wide range of sample rates are available. The integer PLL and flexible clock generator hardware can generate up to 15 audio sample rates simultaneously. These clock generators, along with the on board asynchronous sample rate converters (ASRCs) and a flexible hardware audio routing matrix, make the ADAU1452/ADAU1451/ADAU1450 ideal audio hubs that greatly simplify the design of complex multirate audio systems.

The ADAU1452/ADAU1451/ADAU1450 interface with a wide range of ADCs, DACs, digital audio devices, amplifiers, and control circuitry, due to their highly configurable serial ports, S/PDIF interfaces (on the ADAU1452 and ADAU1451), and multipurpose input/output pins. They can also directly interface with PDM output MEMS microphones, thanks to integrated decimation filters specifically designed for that purpose.

Independent slave and master I<sup>2</sup>C/SPI control ports allow the ADAU1452/ADAU1451/ADAU1450 not only to be programmed and configured by an external master device, but also to act as masters that can program and configure external slave devices directly. This flexibility, combined with self boot functionality, enables the design of standalone systems that do not require any external input to operate.

The power efficient DSP core executes full programs while consuming only a few hundred milliwatts (mW) of power and can run at a maximum program load while consuming less than a watt, even in worst case temperatures exceeding 100°C. This relatively low power consumption and small footprint make the ADAU1452/ADAU1451/ADAU1450 ideal replacements for large, general-purpose DSPs that consume more power at the same processing load.

## DIFFERENCES BETWEEN THE ADAU1452, ADAU1451, AND ADAU1450

The three variants of this device are differentiated by memory, DSP core frequency, availability of S/PDIF interfaces, and ASRC configuration. A detailed summary of the differences is listed in Table 1.

Because the ADAU1450 does not contain an S/PDIF receiver or transmitter, the SPDIFIN and SPDIFOUT pins are nonfunctional. Also, the settings of any registers related to the S/PDIF input or output in the ADAU1450 do not have any effect on the operation of the device.

Likewise, because the ADAU1450 does not contain ASRCs, the settings of any registers related to the ASRCs in the ADAU1450 do not have any effect on the operation of the device.

**Table 1. Product Selection Table**

| Device<br>Number | Data Memory<br>(kWords) | Program Memory (kWords) | DSP Core<br>Frequency | S/PDIF Input and<br>Output | ASRC Configuration                          |  |  |  |  |

|------------------|-------------------------|-------------------------|-----------------------|----------------------------|---------------------------------------------|--|--|--|--|

| ADAU1452         | 40                      | 8                       | 294.912 MHz           | Available                  | 16 channels (8 rates × 2 channels per rate) |  |  |  |  |

| ADAU1451         | 16                      | 8                       | 294.912 MHz           | Available                  | 16 channels (8 rates × 2 channels per rate) |  |  |  |  |

| ADAU1450         | 8                       | 8                       | 147.456 MHz           | Not available              | No ASRCs included                           |  |  |  |  |

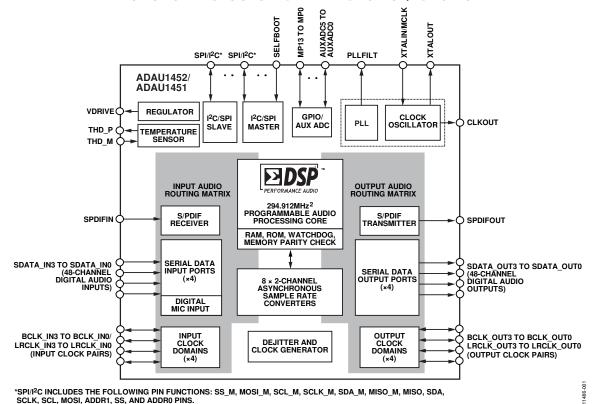

## FUNCTIONAL BLOCK DIAGRAM—ADAU1450

\*SPI/I<sup>2</sup>C INCLUDES THE FOLLOWING PIN FUNCTIONS: SS\_M, MOSI\_M, SCL\_M, SCLK\_M, SDA\_M, MISO\_M, MISO, SDA, SCLK, SCL, MOSI, ADDR1, SS, AND ADDR0 PINS.

Figure 2.

## **SPECIFICATIONS**

$AVDD = 3.3~V \pm 10\%, DVDD = 1.2~V \pm 5\%, PVDD = 3.3~V \pm 10\%, IOVDD = 1.8~V - 10\% \ to \ 3.3~V + 10\%, T_A = 25^{\circ}C, master clock input = 12.288~MHz, core clock (f_{CORE}) = 294.912~MHz, I/O pins set to low drive setting, unless otherwise noted.$

Table 2.

| Parameter                               | Min  | Тур  | Max    | Unit | Test Conditions/Comments                                                                                                         |

|-----------------------------------------|------|------|--------|------|----------------------------------------------------------------------------------------------------------------------------------|

| POWER                                   |      |      |        |      |                                                                                                                                  |

| Supply Voltage                          |      |      |        |      |                                                                                                                                  |

| Analog Voltage (AVDD)                   | 2.97 | 3.3  | 3.63   | V    | Supply for analog circuitry, including auxiliary ADC                                                                             |

| Digital Voltage (DVDD)                  | 1.14 | 1.2  | 1.26   | V    | Supply for digital circuitry, including the DSP core, ASRCs, and signal routing                                                  |

| PLL Voltage (PVDD)                      | 2.97 | 3.3  | 3.63   | V    | Supply for phase-locked loop (PLL) circuitry                                                                                     |

| I/O Supply Voltage (IOVDD)              | 1.71 | 3.3  | 3.63   | V    | Supply for input/output circuitry, including pads and level shifters                                                             |

| Supply Current                          |      |      |        |      |                                                                                                                                  |

| Analog Current (AVDD)                   | 1.5  | 1.73 | 2      | mA   |                                                                                                                                  |

| Idle State                              | 0    | 5    | 40     | μΑ   | Power applied, chip not programmed                                                                                               |

| Reset State                             | 1.9  | 6.5  | 40     | μΑ   | Power applied, RESET held low                                                                                                    |

| PLL Current (PVDD)                      | 9.5  | 10   | 13     | mA   | 12.288 MHz MCLK with default PLL settings                                                                                        |

| Idle State                              | 0    | 7.3  | 40     | μΑ   | Power applied, PLL not configured                                                                                                |

| Reset State                             | 3.9  | 8.5  | 40     | μA   | Power applied, RESET held low                                                                                                    |

| I/O Current (IOVDD)                     |      |      |        | 1    | Dependent on the number of active serial ports, clock pins, and                                                                  |

| , , , , , , , , , , , , , , , , , , , , |      |      |        |      | characteristics of external loads                                                                                                |

| Operation State                         |      | 53   |        | mA   | IOVDD = 3.3 V; all serial ports are clock masters                                                                                |

|                                         |      | 22   |        | mA   | IOVDD = 1.8 V; all serial ports are clock masters                                                                                |

| Power-Down State                        |      | 0.3  | 2.5    | mA   | IOVDD = 1.8 V - 10% to 3.3 V + 10%                                                                                               |

| Digital Current (DVDD)                  |      |      |        |      |                                                                                                                                  |

| Operation State, ADAU1452               |      |      |        |      |                                                                                                                                  |

| Maximum Program                         |      | 350  | 415    | mA   |                                                                                                                                  |

| Typical Program                         |      | 100  |        | mA   | Test program includes 16-channel I/O, 10-band EQ per channel, all ASRCs active                                                   |

| Minimal Program                         |      | 85   |        | mA   | Test program includes 2-channel I/O, 10-band EQ per channel                                                                      |

| Operation State, ADAU1451               |      |      |        |      |                                                                                                                                  |

| Maximum Program                         |      | 350  | 415    | mA   |                                                                                                                                  |

| Typical Program                         |      | 100  |        | mA   | Test program includes 16-channel I/O, 10-band EQ per channel, all ASRCs active                                                   |

| Minimal Program                         |      | 85   |        | mA   | Test program includes 2-channel I/O, 10-band EQ per channel                                                                      |

| Operation State, ADAU1450               |      |      |        |      |                                                                                                                                  |

| Maximum Program                         |      | 125  | 250    | mA   | f <sub>CORE</sub> = 147.456 MHz                                                                                                  |

| Typical Program                         |      | 65   |        | mA   | Test program includes 16-channel I/O, 10-band EQ per channel, $f_{CORE} = 147.456 \text{ MHz}$                                   |

| Minimal Program                         |      | 55   |        | mA   | Test program includes 2-channel I/O, 10-band EQ per channel, $f_{CORE} = 147.456$ MHz                                            |

| Idle State                              |      | 20   | 95     | mA   | Power applied, DSP not enabled                                                                                                   |

| Reset State                             |      | 20   | 95     | mA   | Power applied, RESET held low                                                                                                    |

| ASYNCHRONOUS SAMPLE RATE CONVERTERS     |      |      |        |      |                                                                                                                                  |

| Dynamic Range                           |      | 139  |        | dB   | A-weighted, 20 Hz to 20 kHz                                                                                                      |

| I/O Sample Rate                         | 6    |      | 192    | kHz  |                                                                                                                                  |

| I/O Sample Rate Ratio                   | 1:8  |      | 7.75:1 |      |                                                                                                                                  |

| THD + N                                 |      |      | -120   | dB   |                                                                                                                                  |

| CRYSTAL OSCILLATOR                      |      |      | -      |      |                                                                                                                                  |

| Transconductance                        | 8.3  | 10.6 | 13.4   | mS   |                                                                                                                                  |

| REGULATOR                               |      |      |        | 1    |                                                                                                                                  |

| DVDD Voltage                            | 1.14 | 1.2  |        | V    | Regulator maintains typical output voltage up to a maximum 800 mA load; IOVDD = $1.8 \text{ V} - 10\%$ to $3.3 \text{ V} + 10\%$ |

$AVDD = 3.3~V \pm 10\%, DVDD = 1.2~V \pm 5\%, PVDD = 3.3~V \pm 10\%, IOVDD = 1.8~V - 10\% \ to \ 3.3~V + 10\%, T_A = -40^{\circ}C \ to \ +105^{\circ}C, master clock input = 12.288~MHz, core clock (<math>f_{CORE}$ ) = 294.912 MHz, I/O pins set to low drive setting, unless otherwise noted.

Table 3.

| Parameter                           | Min  | Тур  | Max    | Unit | Test Conditions/Comments                                                                                         |

|-------------------------------------|------|------|--------|------|------------------------------------------------------------------------------------------------------------------|

| POWER                               |      |      |        |      |                                                                                                                  |

| Supply Voltage                      |      |      |        |      |                                                                                                                  |

| Analog Voltage (AVDD)               | 2.97 | 3.3  | 3.63   | ٧    | Supply for analog circuitry, including auxiliary ADC                                                             |

| Digital Voltage (DVDD)              | 1.14 | 1.2  | 1.26   | V    | Supply for digital circuitry, including the DSP core, ASRCs, and signal routing                                  |

| PLL Voltage (PVDD)                  | 2.97 | 3.3  | 3.63   | V    | Supply for PLL circuitry                                                                                         |

| IOVDD Voltage (IOVDD)               | 1.71 | 3.3  | 3.63   | V    | Supply for input/output circuitry, including pads and level shifters                                             |

| Supply Current                      |      |      |        |      |                                                                                                                  |

| Analog Current (AVDD)               | 1.44 | 1.72 | 2      | mA   |                                                                                                                  |

| Idle State                          | 0    | 6.3  | 40     | μΑ   |                                                                                                                  |

| Reset State                         | 0.26 | 7.1  | 40     | μA   |                                                                                                                  |

| PLL Current (PVDD)                  | 6    | 10.9 | 15     | mA   | 12.288 MHz master clock; default PLL settings                                                                    |

| Idle State                          | 0    | 7.8  | 40     | μΑ   | Power applied, PLL not configured                                                                                |

| Reset State                         | 1.2  | 9.3  | 40     | μA   | Power applied, RESET held low                                                                                    |

| I/O Current (IOVDD)                 |      |      |        |      | Dependent on the number of active serial ports, clock pins, and                                                  |

| .,                                  |      |      |        |      | characteristics of external loads                                                                                |

| Operation State                     |      | 47   |        | mA   | IOVDD = 3.3 V; all serial ports are clock masters                                                                |

| •                                   |      | 15   |        | mA   | IOVDD = 1.8 V; all serial ports are clock masters                                                                |

| Power-Down State                    |      | 1.3  | 2.2    | mA   | IOVDD = 1.8 V – 10% to 3.3 V + 10%                                                                               |

| Digital Current (DVDD)              |      |      |        |      |                                                                                                                  |

| Operation State, ADAU1452           |      |      |        |      |                                                                                                                  |

| Maximum Program                     |      | 500  | 690    | mA   |                                                                                                                  |

| Typical Program                     |      | 200  |        | mA   | Test program includes 16-channel I/O, 10-band EQ per channel, all ASRCs active                                   |

| Minimal Program                     |      | 160  |        | mA   | Test program includes 2-channel I/O, 10-band EQ per channel                                                      |

| Operation State, ADAU1451           |      |      |        |      | , , , , ,                                                                                                        |

| Maximum Program                     |      | 500  | 690    | mA   |                                                                                                                  |

| Typical Program                     |      | 200  |        | mA   | Test program includes 16-channel I/O, 10-band EQ per channel, all ASRCs active                                   |

| Minimal Program                     |      | 160  |        | mA   | Test program includes 2-channel I/O, 10-band EQ per channel                                                      |

| Operation State, ADAU1450           |      |      |        |      |                                                                                                                  |

| Maximum Program                     |      | 270  | 635    | mA   | f <sub>CORE</sub> = 147.456 MHz                                                                                  |

| Typical Program                     |      | 110  |        | mA   | Test program includes 16-channel I/O, 10-band EQ per channel, f <sub>CORE</sub> = 147.456 MHz                    |

| Minimal Program                     |      | 90   |        | mA   | Test program includes 2-channel I/O, 10-band EQ per channel, $f_{CORE} = 147.456$ MHz                            |

| Idle State                          |      | 315  | 635    | mA   |                                                                                                                  |

| Reset State                         |      | 315  | 635    | mA   |                                                                                                                  |

| ASYNCHRONOUS SAMPLE RATE CONVERTERS |      |      |        |      |                                                                                                                  |

| Dynamic Range                       |      | 139  |        | dB   | A-weighted, 20 Hz to 20 kHz                                                                                      |

| I/O Sample Rate                     | 6    |      | 192    | kHz  |                                                                                                                  |

| I/O Sample Rate Ratio               | 1:8  |      | 7.75:1 |      |                                                                                                                  |

| THD + N                             |      |      | -120   | dB   |                                                                                                                  |

| CRYSTAL OSCILLATOR                  |      |      |        |      |                                                                                                                  |

| Transconductance                    | 8.1  | 10.6 | 14.6   | mS   |                                                                                                                  |

| REGULATOR                           |      |      |        | -    |                                                                                                                  |

| DVDD Voltage                        | 1.14 | 1.2  |        | V    | Regulator maintains typical output voltage up to a maximum 800 m. load; $IOVDD = 1.8 V - 10\%$ to $3.3 V + 10\%$ |

### **ELECTRICAL CHARACTERISTICS**

## Digital Input/Output

Table 4.

| Parameter                                 | Min  | Тур | Max  | Unit | Test Conditions/Comments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-------------------------------------------|------|-----|------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DIGITAL INPUT                             |      |     |      |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Input Voltage                             |      |     |      |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| IOVDD = 3.3 V                             |      |     |      |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| High Level (V <sub>IH</sub> )¹            | 1.71 |     | 3.3  | V    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Low Level (V <sub>IL</sub> ) <sup>1</sup> | 0    |     | 1.71 | V    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| IOVDD = 1.8 V                             |      |     |      |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| High Level (V <sub>IH</sub> )¹            | 0.92 |     | 1.8  | V    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Low Level (V <sub>IL</sub> ) <sup>1</sup> | 0.92 |     | 0.89 | ľ    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Input Leakage                             | 0    |     | 0.09 | l v  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| High Level (I <sub>H</sub> )              | -2   |     | . 2  |      | Digital input pine with pull up recietor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| nign Level (I⊪)                           |      |     | +2   | μΑ   | Digital input pins with pull-up resistor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                           | 2    |     | 12   | μΑ   | Digital input pins with pull-down resistor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                           | -2   |     | +2   | μΑ   | Digital input pins with no pull resistor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                           | 0    |     | 8    | μΑ   | MCLK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                           | 80   |     | 120  | μΑ   | SPDIFIN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Low Level (I <sub>IL</sub> ) at 0 V       | -12  |     | -2   | μΑ   | Digital input pins with pull-up resistor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                           | -2   |     | +2   | μΑ   | Digital input pins with pull-down resistor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                           | -2   |     | +2   | μΑ   | Digital input pins with no pull resistor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

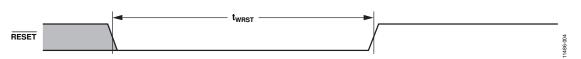

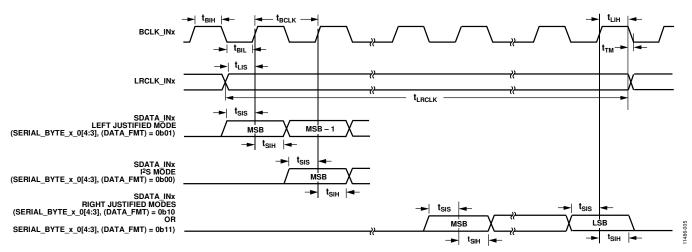

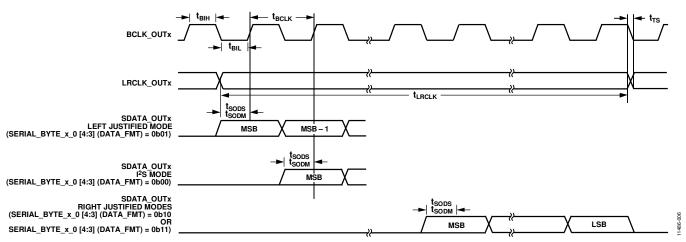

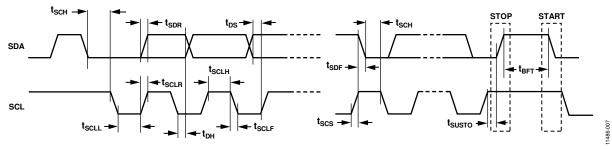

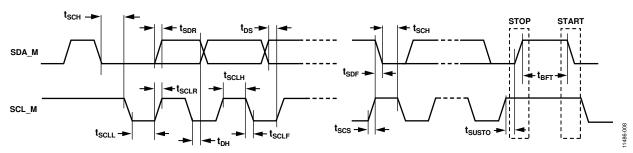

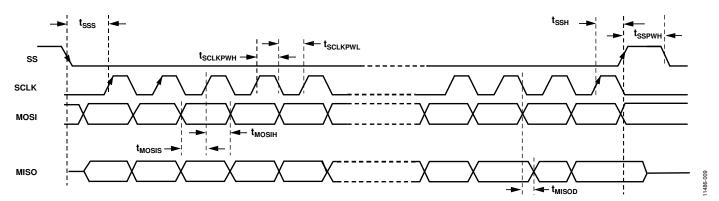

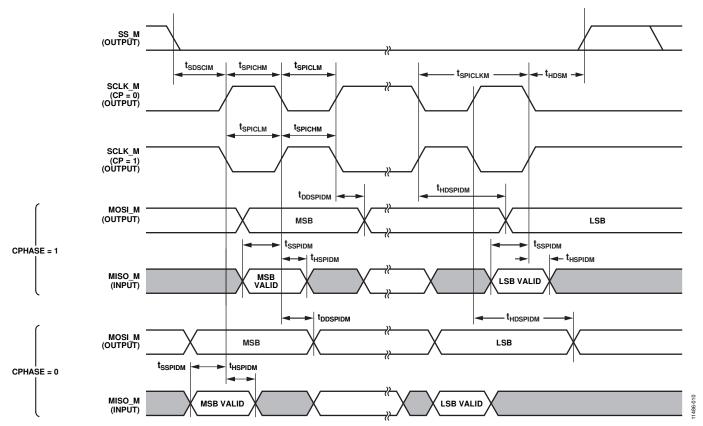

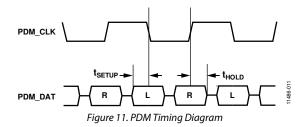

|                                           | -8   |     | 0    | μΑ   | MCLK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |